Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 8-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f1840-i-sn |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 7.12 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- Stack Overflow Reset (STKOVF)

- Stack Underflow Reset (STKUNF)

- MCLR Reset (RMCLR)

The PCON register bits are shown in Register 7-2.

### 7.13 Register Definitions: Power Control

### REGISTER 7-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | U-0 | U-0 | R/W/HC-1/q  | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|-----|-------------|------------|------------|------------|

| STKOVF     | STKUNF     | _   |     | RMCLR       | RI         | POR        | BOR        |

| bit 7      |            |     |     | · · · · · · |            | •          | bit 0      |

| Legend:                     |                      |                                                       |

|-----------------------------|----------------------|-------------------------------------------------------|

| HC = Bit is cleared by hard | dware                | HS = Bit is set by hardware                           |

| R = Readable bit            | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged        | x = Bit is unknown   | -m/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set            | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | STKOVF: Stack Overflow Flag bit                                                                                                   |

|---------|-----------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = A Stack Overflow occurred                                                                                                     |

|         | 0 = A Stack Overflow has not occurred or set to '0' by firmware                                                                   |

| bit 6   | STKUNF: Stack Underflow Flag bit                                                                                                  |

|         | 1 = A Stack Underflow occurred                                                                                                    |

|         | 0 = A Stack Underflow has not occurred or set to '0' by firmware                                                                  |

| bit 5-4 | Unimplemented: Read as '0'                                                                                                        |

| bit 3   | RMCLR: MCLR Reset Flag bit                                                                                                        |

|         | 1 = A MCLR Reset has not occurred or set to '1' by firmware                                                                       |

|         | 0 = A MCLR Reset has occurred (set to '0' in hardware when a MCLR Reset occurs)                                                   |

| bit 2   | RI: RESET Instruction Flag bit                                                                                                    |

|         | 1 = A RESET instruction has not been executed or set to '1' by firmware                                                           |

|         | 0 = A RESET instruction has been executed (set to '0' in hardware upon executing a RESET instruction)                             |

| bit 1   | POR: Power-on Reset Status bit                                                                                                    |

|         | 1 = No Power-on Reset occurred                                                                                                    |

|         | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                                             |

| bit 0   | BOR: Brown-out Reset Status bit                                                                                                   |

|         | 1 = No Brown-out Reset occurred                                                                                                   |

|         | <ul> <li>0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset<br/>occurs)</li> </ul> |

|         |                                                                                                                                   |

| R/W-0/0          | R/W-0/0                                                           | R/W-0/0                          | R/W-0/0         | R/W-0/0         | R/W-0/0          | R/W-0/0 | R/W-0/0     |  |  |  |

|------------------|-------------------------------------------------------------------|----------------------------------|-----------------|-----------------|------------------|---------|-------------|--|--|--|

| TMR1GIE          | ADIE                                                              | RCIE                             | TXIE            | SSP1IE          | CCP1IE           | TMR2IE  | TMR1IE      |  |  |  |

| bit 7            |                                                                   |                                  |                 |                 |                  |         | bit (       |  |  |  |

| Legend:          |                                                                   |                                  |                 |                 |                  |         |             |  |  |  |

| R = Readable     | bit                                                               | W = Writable                     | bit             | U = Unimpler    | nented bit, read | as '0'  |             |  |  |  |

| u = Bit is unch  |                                                                   | x = Bit is unkr                  |                 | •               | at POR and BO    |         | ther Resets |  |  |  |

| '1' = Bit is set | •                                                                 | '0' = Bit is clea                | ared            |                 |                  |         |             |  |  |  |

|                  |                                                                   |                                  |                 |                 |                  |         |             |  |  |  |

| bit 7            |                                                                   | mer1 Gate Inte                   |                 |                 |                  |         |             |  |  |  |

|                  |                                                                   | he Timer1 Gate<br>the Timer1 Gat |                 |                 |                  |         |             |  |  |  |

| bit 6            |                                                                   | j-to-Digital Con                 | •               | •               | e bit            |         |             |  |  |  |

|                  |                                                                   | he ADC interru                   |                 |                 |                  |         |             |  |  |  |

|                  |                                                                   | the ADC interru                  | •               |                 |                  |         |             |  |  |  |

| bit 5            |                                                                   | T Receive Inter                  | •               | it              |                  |         |             |  |  |  |

|                  |                                                                   | he USART rec<br>the USART rec    |                 |                 |                  |         |             |  |  |  |

| bit 4            |                                                                   | Transmit Inter                   |                 |                 |                  |         |             |  |  |  |

|                  |                                                                   | he USART trar                    | •               |                 |                  |         |             |  |  |  |

|                  | 0 = Disables                                                      | the USART tra                    | nsmit interrup  | t               |                  |         |             |  |  |  |

| bit 3            | -                                                                 | chronous Seria                   |                 | ) Interrupt Ena | ble bit          |         |             |  |  |  |

|                  | 1 = Enables the MSSP interrupt<br>0 = Disables the MSSP interrupt |                                  |                 |                 |                  |         |             |  |  |  |

| bit 2            |                                                                   | P1 Interrupt En                  | •               |                 |                  |         |             |  |  |  |

|                  |                                                                   | 1 = Enables the CCP1 interrupt   |                 |                 |                  |         |             |  |  |  |

|                  | 0 = Disables the CCP1 interrupt                                   |                                  |                 |                 |                  |         |             |  |  |  |

| bit 1            | TMR2IE: TM                                                        | R2 to PR2 Mate                   | ch Interrupt Er | nable bit       |                  |         |             |  |  |  |

|                  |                                                                   | he Timer2 to P                   |                 |                 |                  |         |             |  |  |  |

| 1.11.0           |                                                                   | the Timer2 to F                  |                 | •               |                  |         |             |  |  |  |

| bit 0            |                                                                   | er1 Overflow Ir                  |                 |                 |                  |         |             |  |  |  |

|                  |                                                                   | he Timer1 over<br>the Timer1 ove |                 |                 |                  |         |             |  |  |  |

|                  |                                                                   |                                  |                 |                 |                  |         |             |  |  |  |

|                  | PEIE of the IN                                                    |                                  |                 |                 |                  |         |             |  |  |  |

| set              | t to enable any p                                                 | peripheral inter                 | rupt.           |                 |                  |         |             |  |  |  |

## REGISTER 8-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| Name   | Bit 7  | Bit 6 | Bit 5     | Bit 4 | Bit 3     | Bit 2 | Bit 1    | Bit 0  | Register<br>on Page |

|--------|--------|-------|-----------|-------|-----------|-------|----------|--------|---------------------|

| OSCCON | SPLLEN |       | IRCF<3:0> |       |           | —     | SCS<1:0> |        | 53                  |

| STATUS | —      | _     | —         | TO    | PD        | Z     | DC       | С      | 15                  |

| WDTCON | —      | _     |           | ١     | WDTPS<4:0 | >     |          | SWDTEN | 83                  |

#### TABLE 10-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2   | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|------------|---------|---------|---------------------|

| CONFIG1 | 13:8 | _       | _       | FCMEN    | IESO     | CLKOUTEN | BOREN<1:0> |         | —       | 22                  |

| CONFIGT | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | =<1:0>   | FOSC<2:0>  |         |         | 33                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

## 11.0 DATA EEPROM AND FLASH PROGRAM MEMORY CONTROL

The data EEPROM and Flash program memory are readable and writable during normal operation (full VDD range). These memories are not directly mapped in the register file space. Instead, they are indirectly addressed through the Special Function Registers (SFRs). There are six SFRs used to access these memories:

- EECON1

- EECON2

- EEDATL

- EEDATH

- EEADRL

- EEADRH

When interfacing the data memory block, EEDATL holds the 8-bit data for read/write, and EEADRL holds the address of the EEDATL location being accessed. These devices have 256 bytes of data EEPROM with an address range from 0h to 0FFh.

When accessing the program memory block, the EEDATH:EEDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the EEADRL and EEADRH registers form a 2-byte word that holds the 15-bit address of the program memory location being read.

The EEPROM data memory allows byte read and write. An EEPROM byte write automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

Depending on the setting of the Flash Program Memory Self Write Enable bits WRT<1:0> of the Configuration Words, the device may or may not be able to write certain blocks of the program memory. However, reads from the program memory are always allowed.

When the device is code-protected, the device programmer can no longer access data or program memory. When code-protected, the CPU may continue to read and write the data EEPROM memory and Flash program memory.

#### 11.1 EEADRL and EEADRH Registers

The EEADRH:EEADRL register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 32K words of program memory.

When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADRL register. When selecting a EEPROM address value, only the LSB of the address is written to the EEADRL register.

#### 11.1.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for EE memory accesses.

Control bit EEPGD determines if the access will be a program or data memory access. When clear, any subsequent operations will operate on the EEPROM memory. When set, any subsequent operations will operate on the program memory. On Reset, EEPROM is selected by default.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

Interrupt flag bit EEIF of the PIR2 register is set when write is complete. It must be cleared in the software.

Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence. To enable writes, a specific pattern must be written to EECON2.

### 13.6 Register Definitions: Interrupt-on-Change Control

#### **REGISTER 13-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER**

| U-0                                   | U-0                                     | R/W-0/0        | R/W-0/0 | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|---------------------------------------|-----------------------------------------|----------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|

| _                                     | —                                       | IOCAP5         | IOCAP4  | IOCAP3                                                | IOCAP2  | IOCAP1  | IOCAP0  |  |  |

| bit 7                                 |                                         | •              | •       | •                                                     |         |         | bit 0   |  |  |

|                                       |                                         |                |         |                                                       |         |         |         |  |  |

| Legend:                               |                                         |                |         |                                                       |         |         |         |  |  |

| R = Readable b                        | it                                      | W = Writable b | oit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| u = Bit is uncha                      | u = Bit is unchanged x = Bit is unknown |                |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

| '1' = Bit is set '0' = Bit is cleared |                                         |                |         |                                                       |         |         |         |  |  |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 IOCAP<5:0>: Interrupt-on-Change PORTA Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

|       |     |         |         |         |         |         |         |

|       |     |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0

bit 5-0

- **IOCAN<5:0>:** Interrupt-on-Change PORTA Negative Edge Enable bits 1 = Interrupt-on-Change enabled on the pin for a negative going edge. Associated Status bit and interrupt

- flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

| U-0   | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|------------|------------|------------|------------|------------|------------|

| —     | —   | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| bit 7 |     |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-6 Unimplemented: Read as '0'

IOCAF<5:0>: Interrupt-on-Change PORTA Flag bits

- 1 = An enabled change was detected on the associated pin.

- Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

- 0 = No change was detected, or the user cleared the detected change.

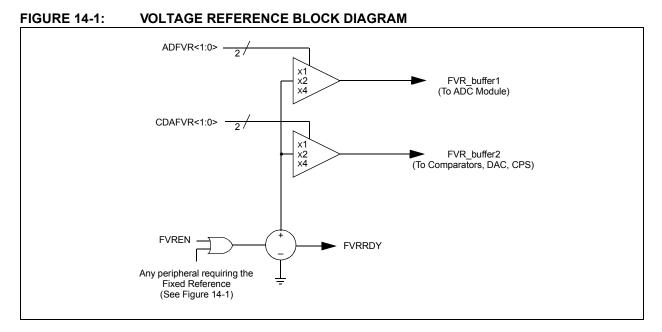

## 14.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- · ADC input channel

- · ADC positive reference

- · Comparator positive input

- Digital-to-Analog Converter (DAC)

- Capacitive Sensing (CPS) module

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

### 14.1 Independent Gain Amplifiers

The output of the FVR supplied to the ADC, Comparators, DAC and CPS module is routed through two independent programmable gain amplifiers. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 16.0** "**Analog-to-Digital Converter** (**ADC**) **Module**" for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the Comparators, DAC, and CPS module. Reference Section 17.0 "Digital-to-Analog Converter (DAC) Module", Section 19.0 "Comparator Module" and Section 17.0 "Digital-to-Analog Converter (DAC) Module" for additional information.

### 14.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set. See **Section 30.0 "Electrical Specifications"** for the minimum delay requirement.

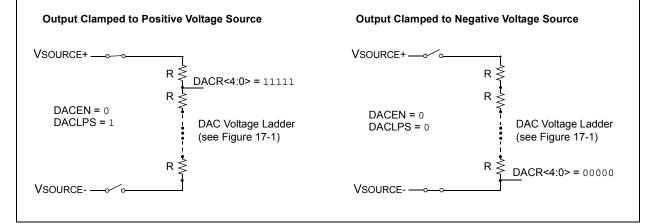

## 17.4 Low-Power Voltage State

In order for the DAC module to consume the least amount of power, one of the two voltage reference input sources to the resistor ladder must be disconnected. Either the positive voltage source, (VSOURCE+), or the negative voltage source, (VSOURCE-) can be disabled.

The negative voltage source is disabled by setting the DACLPS bit in the DACCON0 register. Clearing the DACLPS bit in the DACCON0 register disables the positive voltage source.

#### 17.4.1 OUTPUT CLAMPED TO POSITIVE VOLTAGE SOURCE

The DAC output voltage can be set to VSOURCE+ with the least amount of power consumption by performing the following:

- · Clearing the DACEN bit in the DACCON0 register.

- · Setting the DACLPS bit in the DACCON0 register.

- Configuring the DACPSS bits to the proper positive source.

- Configuring the DACR<4:0> bits to '11111' in the DACCON1 register.

This is also the method used to output the voltage level from the FVR to an output pin. See **Section 17.5 "Operation During Sleep"** for more information.

Reference Figure 17-3 for output clamping examples.

## 17.4.2 OUTPUT CLAMPED TO NEGATIVE VOLTAGE SOURCE

The DAC output voltage can be set to VSOURCE- with the least amount of power consumption by performing the following:

- · Clearing the DACEN bit in the DACCON0 register.

- Clearing the DACLPS bit in the DACCON0 register.

- Configuring the DACR<4:0> bits to '00000' in the DACCON1 register.

This allows the comparator to detect a zero-crossing while not consuming additional current through the DAC module.

Reference Figure 17-3 for output clamping examples.

#### FIGURE 17-3: OUTPUT VOLTAGE CLAMPING EXAMPLES

#### 17.5 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DACCON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

## 17.6 Effects of a Reset

A device Reset affects the following:

- DAC is disabled.

- DAC output voltage is removed from the DACOUT pin.

- The DACR<4:0> range select bits are cleared.

#### 24.3.2 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP1 module for standard PWM operation:

- 1. Disable the CCP1 pin output driver by setting the associated TRIS bit.

- 2. Load the PR2 register with the PWM period value.

- Configure the CCP1 module for the PWM mode by loading the CCP1CON register with the appropriate values.

- Load the CCPR1L register and the DC1B1 bits of the CCP1CON register, with the PWM duty cycle value.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register. See Note below.

- Configure the T2CKPS bits of the T2CON register with the Timer prescale value.

- Enable the Timer by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until the Timer overflows and the TMR2IF bit of the PIR1 register is set. See Note below.

- Enable the CCP1 pin output driver by clearing the associated TRIS bit.

- **Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

#### 24.3.3 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 24-1.

#### EQUATION 24-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$ (TMR2 Prescale Value)

Note 1: Tosc = 1/Fosc

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from CCPR1L into CCPR1H.

Note: The Timer postscaler (see Section 22.1 "Timer2 Operation") is not used in the determination of the PWM frequency.

#### 24.3.4 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to multiple registers: CCPR1L register and DC1B<1:0> bits of the CCP1CON register. The CCPR1L contains the eight MSbs and the DC1B<1:0> bits of the CCP1CON register contain the two LSbs. CCPR1L and DC1B<1:0> bits of the CCP1CON register can be written to at any time. The duty cycle value is not latched into CCPR1H until after the period completes (i.e., a match between PR2 and TMR2 registers occurs). While using the PWM, the CCPR1H register is read-only.

Equation 24-2 is used to calculate the PWM pulse width.

Equation 24-3 is used to calculate the PWM duty cycle ratio.

## EQUATION 24-2: PULSE WIDTH

$$Pulse Width = (CCPR1L:CCP1CON < 5:4>) \bullet$$

TOSC • (TMR2 Prescale Value)

## EQUATION 24-3: DUTY CYCLE RATIO

$Duty Cycle Ratio = \frac{(CCPR1L:CCP1CON < 5:4>)}{4(PR2 + 1)}$

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (Fosc), or 2 bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPR1H and 2-bit latch, then the CCP1 pin is cleared (see Figure 24-4).

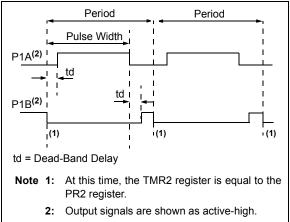

### 24.4.1 HALF-BRIDGE MODE

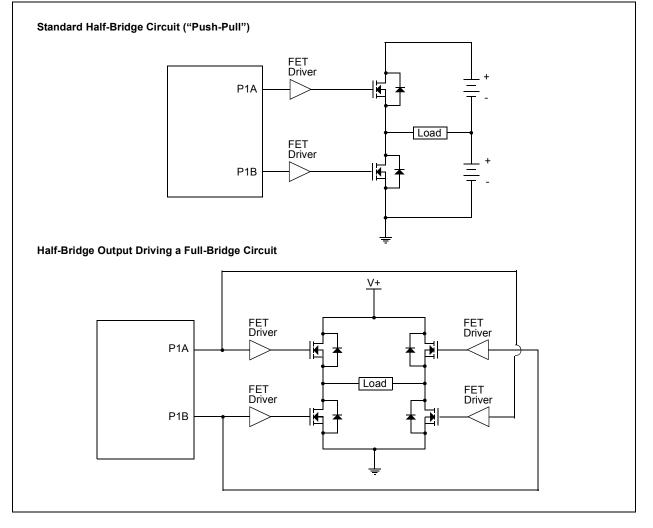

In Half-Bridge mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the CCP1/P1A pin, while the complementary PWM output signal is output on the P1B pin (see Figure 24-9). This mode can be used for Half-Bridge applications, as shown in Figure 24-9, or for Full-Bridge applications, where four power switches are being modulated with two PWM signals.

In Half-Bridge mode, the programmable dead-band delay can be used to prevent shoot-through current in Half-Bridge power devices. The value of the P1DC<6:0> bits of the PWM1CON register sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 24.4.4 "Programmable Dead-Band Delay Mode"** for more details of the dead-band delay operations. Since the P1A and P1B outputs are multiplexed with the PORT data latches, the associated TRIS bits must be cleared to configure P1A and P1B as outputs.

### FIGURE 24-9: EXAMPLE OF HALF-BRIDGE APPLICATIONS

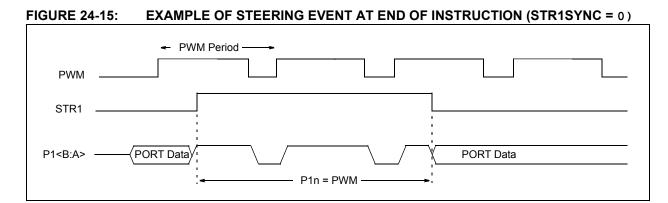

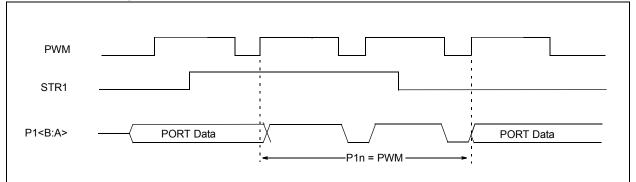

FIGURE 24-16: EXAMPLE OF STEERING EVENT AT BEGINNING OF INSTRUCTION (STR1SYNC = 1)

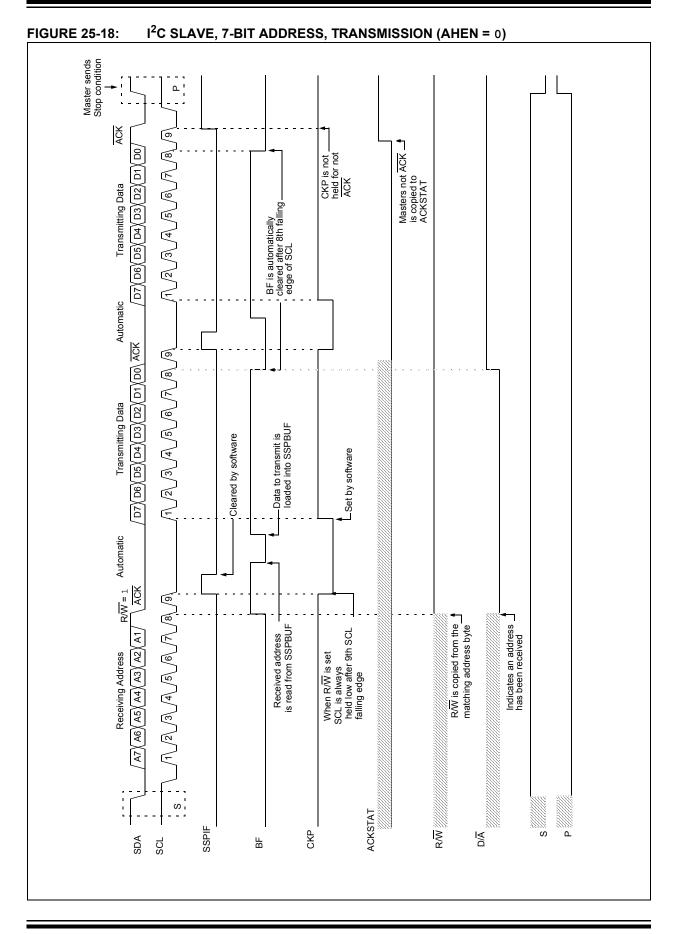

#### 25.4.9 ACKNOWLEDGE SEQUENCE

The 9th SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicated to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSP1CON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the  $\overrightarrow{ACK}$  value sent back to the transmitter. The ACKDT bit of the SSP1CON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSP1CON3 register are clear.

There are certain conditions where an  $\overline{ACK}$  will not be sent by the slave. If the BF bit of the SSP1STAT register or the SSP1OV bit of the SSP1CON1 register are set when a byte is received.

When the module is addressed, after the 8th falling edge of SCL on the bus, the ACKTIM bit of the SSP1CON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

## 25.5 I<sup>2</sup>C SLAVE MODE OPERATION

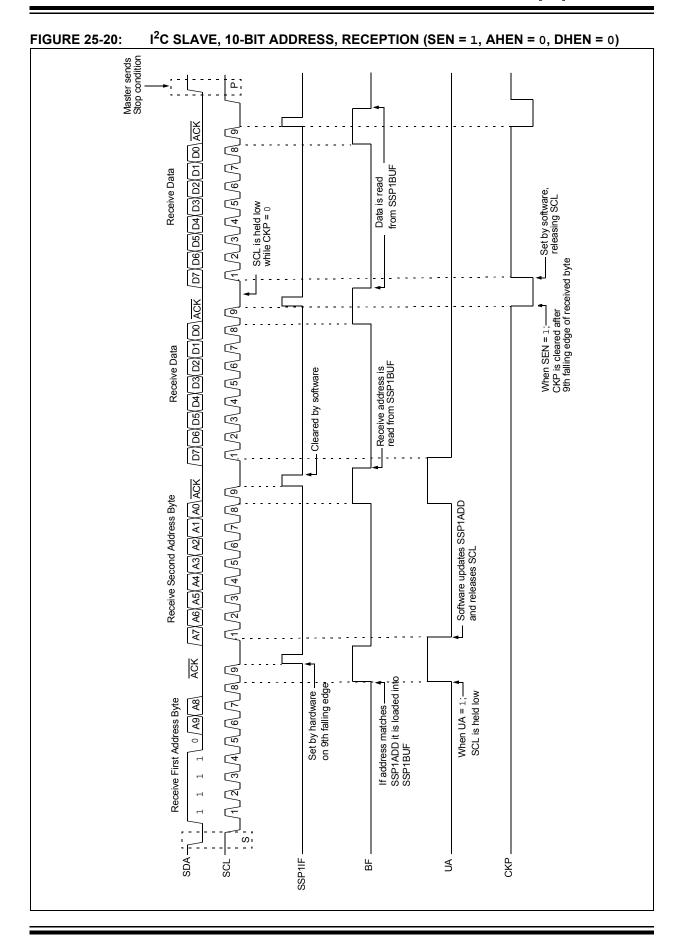

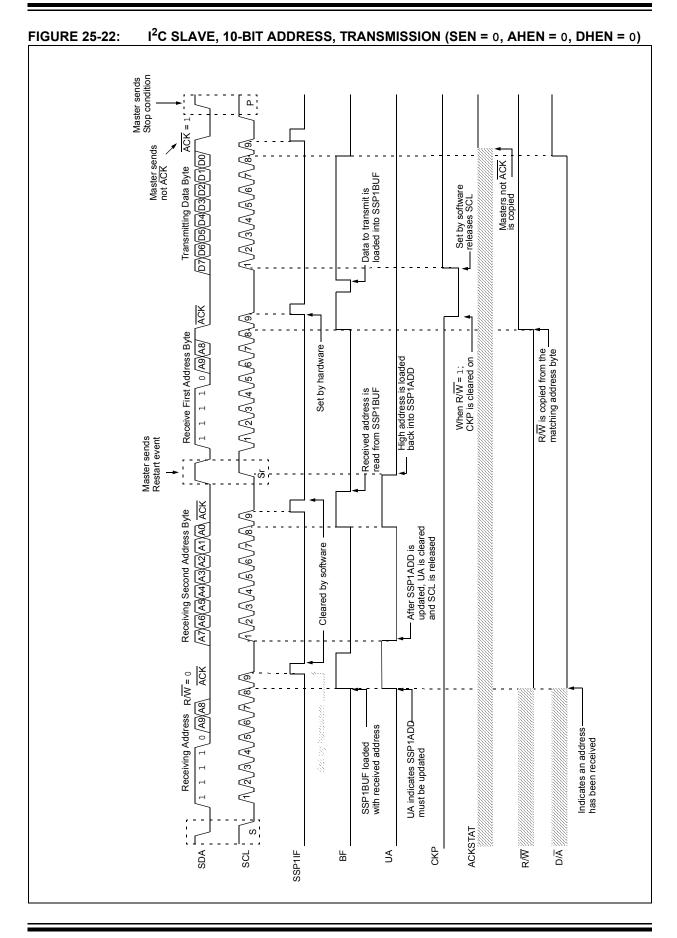

The MSSP1 Slave mode operates in one of four modes selected in the SSP1M bits of SSP1CON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSP1IF additionally getting set upon detection of a Start, Restart, or Stop condition.

#### 25.5.1 SLAVE MODE ADDRESSES

The SSP1ADD register (Register 25-6) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSP1BUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSP Mask register (Register 25-5) affects the address matching process. See **Section 25.5.9** "SSP1 Mask Register" for more information.

25.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

25.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb's of the 10-bit address and stored in bits 2 and 1 of the SSP1ADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSP1ADD with the low address. The low address byte is clocked in and all 8 bits are compared to the low address value in SSP1ADD. Even if there is not an address match; SSP1IF and UA are set, and SCL is held low until SSP1ADD is updated to receive a high byte again. When SSP1ADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the  $R/\overline{W}$  bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                          |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', then a<br>NOP is executed instead, making it a<br>2-cycle instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                    |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                 |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                    |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<6:3> $\rightarrow$ PC<14:11>                                                                                                                         |  |  |  |

| Status Affected: | None                                                                                                                                                                                    |  |  |  |

| Description:     | GOTO is an unconditional branch. The<br>11-bit immediate value is loaded into<br>PC bits <10:0>. The upper bits of PC<br>are loaded from PCLATH<4:3>. GOTO<br>is a 2-cycle instruction. |  |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                          |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                              |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                              |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                      |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', a NOP is<br>executed instead, making it a 2-cycle<br>instruction. |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                                                                                                                                                                                                                                     |  |  |  |

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                           |

|------------------|--------------------------------------------------------------------------------------------------------------------|

| Operands:        | $0 \leq k \leq 255$                                                                                                |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                       |

| Status Affected: | Z                                                                                                                  |

| Description:     | The contents of the W register are<br>OR'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |

| INCF             | Increment f                                                                                                                                                               |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                                 |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                       |  |  |  |

| Status Affected: | Z                                                                                                                                                                         |  |  |  |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'. |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                      |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                 |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                            |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |

| Status Affected: | Z                                                                                                                                                                          |  |  |  |

| Description:     | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |  |  |  |

#### 30.9 High Temperature Operation

This section outlines the specifications for the following devices operating in the high temperature range between  $-40^{\circ}$ C and  $150^{\circ}$ C.<sup>(2)</sup>

• PIC12F1840<sup>(4)</sup>

When the value of any parameter is identical for both the 125°C Extended and the 150°C High Temp. temperature ranges, then that value will be found in the standard specification tables shown earlier in this chapter, under the fields listed for the 125°C Extended temperature range. If the value of any parameter is unique to the 150°C High Temp. temperature range, then it will be listed here, in this section of the data sheet.

If a Silicon Errata exists for the product and it lists a modification to the 125°C Extended temperature range value, one that is also shared at the 150°C High Temp. temperature range, then that modified value will apply to both temperature ranges.

- Note 1: Writes are <u>not allowed</u> for Flash program memory above 125°C.

- 2: AEC-Q100 reliability testing for devices intended to operate at 150°C is 1,000 hours. Any design in which the total operating time from 125°C to 150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- **3:** The temperature range indicator in the catalog part number and device marking is "H" for -40°C to 150°C.

Example: PIC12F1840T-H/SN indicates the device is shipped in a Tape and Reel configuration, in the SOIC package, and is rated for operation from -40°C to 150°C.

- 4: The low voltage version of this device, PIC12LF1840, is not released for operation above +125°C.

- Errata Sheet DS80538 lists various mask revisions. 150°C operation applies only to revisions A5 and later.

- 6: The Capacitive Sensing module (CPS) should not be used in high temperature devices. Function and its parametrics are not warranted.

- Only SOIC (SN) and DFN (MF) packages will be offered, not PDIP or UQFN.

#### TABLE 30-18: ABSOLUTE MAXIMUM RATINGS

| Parameter                      | Condition | Value           |  |  |

|--------------------------------|-----------|-----------------|--|--|

| Max. Current: VDD              | Source    | 15 mA           |  |  |

| Max. Current: Vss              | Sink      | 15 mA           |  |  |

| Max. Current: Pin              | Source    | 5 mA            |  |  |

| Max. Current: Pin              | Sink      | 5 mA            |  |  |

| Max. Storage Temperature       | —         | -65°C to 155°C  |  |  |

| Max. Junction Temperature      | _         | +155°C          |  |  |

| Ambient Temperature under Bias | —         | -40°C to +150°C |  |  |

**Note:** Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

#### TABLE 30-19: DC CHARACTERISTICS FOR PIC12F1840-H (High Temp.)

| PIC12F1840   |         |                                            | Standard Operating Conditions: (unless otherwise stated)<br>Operating Temperature: $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |      |      |       |                                                                 |

|--------------|---------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------------------------------------------------------|

| Param<br>No. | Sym.    | Characteristics                            | Min.                                                                                                                                            | Тур. | Max. | Units | Condition                                                       |

| D001         | Vdd     | Supply Voltage                             | 2.5                                                                                                                                             |      | 5.5  | V     | Fosc ≤ 32 MHz <b>(Note 2)</b>                                   |

| D002*        | Vdr     | RAM Data Retention Voltage <sup>(1)</sup>  | 2.1                                                                                                                                             | _    | 5.5  | V     | Device in Sleep mode                                            |

| D003         | VADFVR  | Fixed Voltage Reference<br>Voltage for ADC | -10                                                                                                                                             | _    | 8    | %     | 1.024V, VDD ≥ 2.5V<br>2.048V, VDD ≥ 2.5V<br>4.096V, VDD ≥ 4.75V |

| D003A        | VCDAFVR | Fixed Voltage Reference<br>Voltage for ADC | -13                                                                                                                                             | _    | 9    | %     | 1.024V, VDD ≥ 2.5V<br>2.048V, VDD ≥ 2.5V<br>4.096V, VDD ≥ 4.75V |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

2: PLL required for 32 MHz operation.