Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

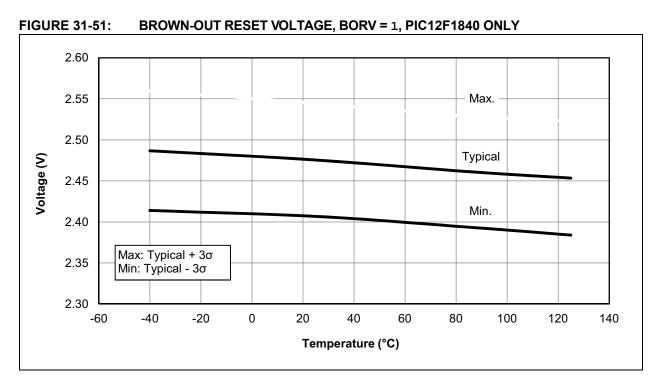

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-VDFN Exposed Pad                                                         |

| Supplier Device Package    | 8-DFN (3x3)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f1840t-i-mf |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

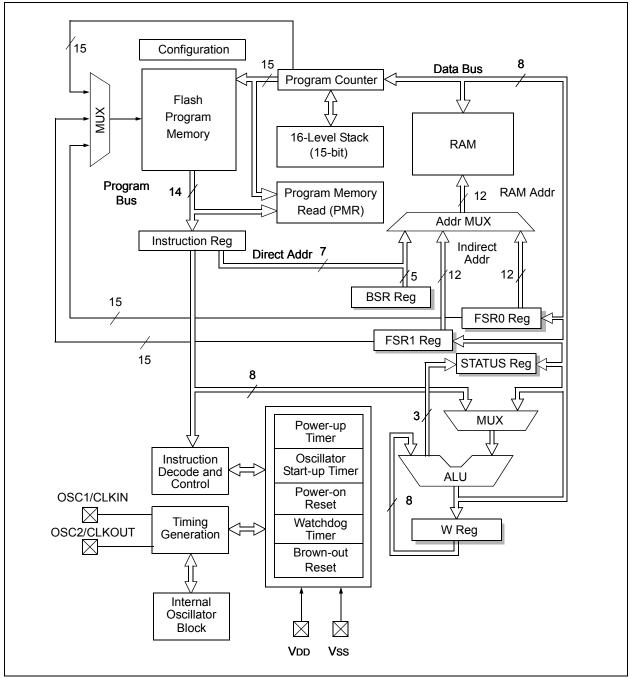

# 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- · 16-level Stack with Overflow and Underflow

- · File Select Registers

- Instruction Set

#### FIGURE 2-1: CORE BLOCK DIAGRAM

## **REGISTER 4-1:** CONFIG1: CONFIGURATION WORD 1 (CONTINUED)

- bit 4-3 WDTE<1:0>: Watchdog Timer Enable bit

- 11 = WDT enabled

- 10 = WDT enabled while running and disabled in Sleep

- 01 = WDT controlled by the SWDTEN bit in the WDTCON register

- 00 = WDT disabled

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = ECH: External Clock, High-Power mode (4-20 MHz): device clock supplied to CLKIN pin

- 110 = ECM: External Clock, Medium-Power mode (0.5-4 MHz): device clock supplied to CLKIN pin

- 101 = ECL: External Clock, Low-Power mode (0-0.5 MHz): device clock supplied to CLKIN pin

- 100 = INTOSC oscillator: I/O function on CLKIN pin

- 011 = EXTRC oscillator: External RC circuit connected to CLKIN pin

- 010 = HS oscillator: High-speed crystal/resonator connected between OSC1 and OSC2 pins

- 001 = XT oscillator: Crystal/resonator connected between OSC1 and OSC2 pins

- 000 = LP oscillator: Low-power crystal connected between OSC1 and OSC2 pins

- **Note 1:** Enabling Brown-out Reset does not automatically enable Power-up Timer.

- 2: The entire data EEPROM will be erased when the code protection is turned off during an erase.

- 3: The entire program memory will be erased when the code protection is turned off.

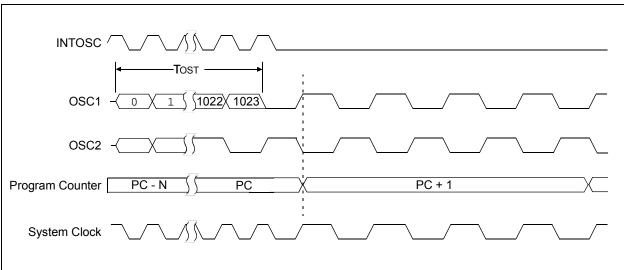

# 5.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

| Note: | Executing a SLEEP instruction will abort    |

|-------|---------------------------------------------|

|       | the oscillator start-up time and will cause |

|       | the OSTS bit of the OSCSTAT register to     |

|       | remain clear.                               |

# 5.4.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Words) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Words configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- Wake-up from Sleep.

| Switch From Switch To |                                                                               | Frequency                                       | Oscillator Delay                 |  |  |

|-----------------------|-------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------|--|--|

| Sleep/POR             | LFINTOSC <sup>(1)</sup><br>MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup> | 31 kHz<br>31.25 kHz-500 kHz<br>31.25 kHz-16 MHz | Oscillator Warm-up Delay (Twarm) |  |  |

| Sleep/POR             | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 2 cycles                         |  |  |

| LFINTOSC              | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 1 cycle of each                  |  |  |

| Sleep/POR             | Timer1 Oscillator<br>LP, XT, HS <sup>(1)</sup>                                | 32 kHz-20 MHz 1024 Clock Cycles (OST)           |                                  |  |  |

| Any clock source      | MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup>                            | 31.25 kHz-500 kHz<br>31.25 kHz-16 MHz           | 2 μs (approx.)                   |  |  |

| Any clock source      | LFINTOSC <sup>(1)</sup>                                                       | 31 kHz                                          | 1 cycle of each                  |  |  |

| Any clock source      | Timer1 Oscillator                                                             | 32 kHz                                          | 1024 Clock Cycles (OST)          |  |  |

| PLL inactive          | PLL active                                                                    | 16-32 MHz                                       | 2 ms (approx.)                   |  |  |

Note 1: PLL inactive.

#### 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

# 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or the internal oscillator.

#### FIGURE 5-8: TWO-SPEED START-UP

# 11.2 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). When variables in one section change frequently, while variables in another section do not change, it is possible to exceed the total number of write cycles to the EEPROM without exceeding the total number of write cycles to a single byte. Refer to **Section 30.0 "Electrical Specifications**". If this is the case, then a refresh of the array must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

#### 11.2.1 READING THE DATA EEPROM MEMORY

To read a data memory location, the user must write the address to the EEADRL register, clear the EEPGD and CFGS control bits of the EECON1 register, and then set control bit RD. The data is available at the very next cycle, in the EEDATL register; therefore, it can be read in the next instruction. EEDATL will hold this value until another read or until it is written to by the user (during a write operation).

#### EXAMPLE 11-1: DATA EEPROM READ

| BANKSEL | EEADRL   |       | i                      |

|---------|----------|-------|------------------------|

| MOVLW   | DATA_EE_ | _ADDR | ;                      |

| MOVWF   | EEADRL   |       | ;Data Memory           |

|         |          |       | ;Address to read       |

| BCF     | EECON1,  | CFGS  | ;Deselect Config space |

| BCF     | EECON1,  | EEPGI | ;Point to DATA memory  |

| BSF     | EECON1,  | RD    | ;EE Read               |

| MOVF    | EEDATL,  | W     | ;W = EEDATL            |

|         |          |       |                        |

Note: Data EEPROM can be read regardless of the setting of the CPD bit.

# 11.2.2 WRITING TO THE DATA EEPROM MEMORY

To write an EEPROM data location, the user must first write the address to the EEADRL register and the data to the EEDATL register. Then the user must follow a specific sequence to initiate the write for each byte.

The write will not initiate if the above sequence is not followed exactly (write 55h to EECON2, write AAh to EECON2, then set the WR bit) for each byte. Interrupts should be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

# 11.2.3 PROTECTION AGAINST SPURIOUS WRITE

There are conditions when the user may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, WREN is cleared. Also, the Power-up Timer (64 ms duration) prevents EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during:

- Brown-out

- · Power Glitch

- Software Malfunction

#### 11.2.4 DATA EEPROM OPERATION DURING CODE-PROTECT

Data memory can be code-protected by programming the  $\overline{CPD}$  bit in the Configuration Words to '0'.

When the data memory is code-protected, only the CPU is able to read and write data to the data EEPROM. It is recommended to code-protect the program memory when code-protecting data memory. This prevents anyone from replacing your program with a program that will access the contents of the data EEPROM.

# 12.2 PORTA Registers

#### 12.2.1 DATA REGISTER

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 12-3). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA3, which is input only and its TRIS bit will always read as '1'. Example 12-1 shows how to initialize PORTA.

Reading the PORTA register (Register 12-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

## 12.2.2 DIRECTION CONTROL

The TRISA register (Register 12-3) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

# 12.2.3 ANSELA REGISTER

The ANSELA register (Register 12-5) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELA register must be initialized     |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | to configure an analog channel as a digital |  |  |  |  |  |

|       | input. Pins configured as analog inputs     |  |  |  |  |  |

|       | will read '0'.                              |  |  |  |  |  |

## EXAMPLE 12-1: INITIALIZING PORTA

| BANKSEL | PORTA       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTA       | ;Init PORTA            |

| BANKSEL | LATA        | ;Data Latch            |

| CLRF    | LATA        | ;                      |

| BANKSEL | ANSELA      | ;                      |

| CLRF    | ANSELA      | ;digital I/O           |

| BANKSEL | TRISA       | ;                      |

| MOVLW   | B'00111000' | ;Set RA<5:3> as inputs |

| MOVWF   | TRISA       | ;and set RA<2:0> as    |

|         |             | ;outputs               |

|         |             |                        |

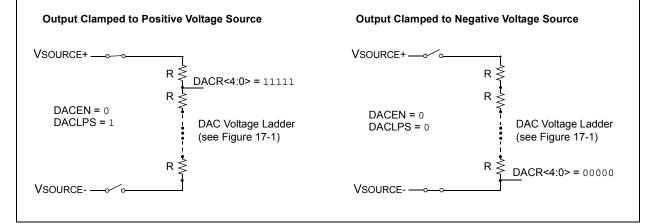

# 17.4 Low-Power Voltage State

In order for the DAC module to consume the least amount of power, one of the two voltage reference input sources to the resistor ladder must be disconnected. Either the positive voltage source, (VSOURCE+), or the negative voltage source, (VSOURCE-) can be disabled.

The negative voltage source is disabled by setting the DACLPS bit in the DACCON0 register. Clearing the DACLPS bit in the DACCON0 register disables the positive voltage source.

#### 17.4.1 OUTPUT CLAMPED TO POSITIVE VOLTAGE SOURCE

The DAC output voltage can be set to VSOURCE+ with the least amount of power consumption by performing the following:

- · Clearing the DACEN bit in the DACCON0 register.

- · Setting the DACLPS bit in the DACCON0 register.

- Configuring the DACPSS bits to the proper positive source.

- Configuring the DACR<4:0> bits to '11111' in the DACCON1 register.

This is also the method used to output the voltage level from the FVR to an output pin. See **Section 17.5 "Operation During Sleep"** for more information.

Reference Figure 17-3 for output clamping examples.

# 17.4.2 OUTPUT CLAMPED TO NEGATIVE VOLTAGE SOURCE

The DAC output voltage can be set to VSOURCE- with the least amount of power consumption by performing the following:

- · Clearing the DACEN bit in the DACCON0 register.

- Clearing the DACLPS bit in the DACCON0 register.

- Configuring the DACR<4:0> bits to '00000' in the DACCON1 register.

This allows the comparator to detect a zero-crossing while not consuming additional current through the DAC module.

Reference Figure 17-3 for output clamping examples.

## FIGURE 17-3: OUTPUT VOLTAGE CLAMPING EXAMPLES

## 17.5 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DACCON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

# 17.6 Effects of a Reset

A device Reset affects the following:

- DAC is disabled.

- DAC output voltage is removed from the DACOUT pin.

- The DACR<4:0> range select bits are cleared.

# 18.0 SR LATCH

The module consists of a single SR latch with multiple Set and Reset inputs as well as separate latch outputs. The SR latch module includes the following features:

- Programmable input selection

- SR latch output is available externally

- Separate Q and  $\overline{Q}$  outputs

- · Firmware Set and Reset

The SR latch can be used in a variety of analog applications, including oscillator circuits, one-shot circuit, hysteretic controllers, and analog timing applications.

# 18.1 Latch Operation

The latch is a Set-Reset Latch that does not depend on a clock source. Each of the Set and Reset inputs are active-high. The latch can be set or reset by:

- Software control (SRPS and SRPR bits)

- Comparator C1 output (sync\_C1OUT)

- SRI pin

- Programmable clock (SRCLK)

The SRPS and the SRPR bits of the SRCON0 register may be used to set or reset the SR latch, respectively. The latch is Reset-dominant. Therefore, if both Set and Reset inputs are high, the latch will go to the Reset state. Both the SRPS and SRPR bits are self resetting which means that a single write to either of the bits is all that is necessary to complete a latch Set or Reset operation.

The output from Comparator C1 can be used as the Set or Reset inputs of the SR latch. The output of the comparator can be synchronized to the Timer1 clock source. See Section 19.0 "Comparator Module" and Section 21.0 "Timer1 Module with Gate Control" for more information.

An external source on the SRI pin can be used as the Set or Reset inputs of the SR latch.

An internal clock source is available that can periodically set or reset the SR latch. The SRCLK<2:0> bits in the SRCON0 register are used to select the clock source period. The SRSCKE and SRRCKE bits of the SRCON1 register enable the clock source to set or reset the SR latch, respectively.

# 18.2 Latch Output

The SRQEN and SRNQEN bits of the SRCON0 register control the Q and  $\overline{Q}$  latch outputs. Both of the SR latch outputs may be directly output to an I/O pin at the same time.

The applicable TRIS bit of the corresponding port must be cleared to enable the port pin output driver.

# 18.3 Effects of a Reset

Upon any device Reset, the SR latch output is not initialized to a known state. The user's firmware is responsible for initializing the latch output before enabling the output pins.

# 21.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# 21.4 Timer1 Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to using Timer1. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

# 21.5 Timer1 Operation in Asynchronous Counter Mode

If the control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 21.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to asynchronous operation, it is possible to                                                              |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

|       | skip an increment. When switching from<br>asynchronous to synchronous operation,<br>it is possible to produce an additional<br>increment. |

## 21.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

# 21.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

## 21.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 21-3 for timing details.

# TABLE 21-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

#### 21.6.2 TIMER1 GATE SOURCE SELECTION

Timer1 gate source selections are shown in Table 21-4. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

## TABLE 21-4: TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                        |

|-------|---------------------------------------------------------------------------|

| 00    | Timer1 Gate Pin                                                           |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)                   |

| 10    | Comparator 1 Output sync_C1OUT<br>(optionally Timer1 synchronized output) |

| 11    | Reserved                                                                  |

#### 21.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 21.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 21.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for Timer1 gate control. The Comparator 1 output (sync\_C1OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 19.4.1 "Comparator Output Synchronization"**.

#### 21.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 21-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

**Note:** Enabling Toggle mode at the same time as changing the gate polarity may result in indeterminate operation.

#### 21.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single-pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 21-5 for timing details.

If the Single-Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 21-6 for timing details.

## 21.6.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

## 21.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

| Name    | Bit 7                                                                       | Bit 6   | Bit 5  | Bit 4  | Bit 3          | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-----------------------------------------------------------------------------|---------|--------|--------|----------------|--------|--------|--------|---------------------|

| ANSELA  |                                                                             | _       | _      | ANSA4  | —              | ANSA2  | ANSA1  | ANSA0  | 103                 |

| CCP1CON | P1M                                                                         | <1:0>   | DC1B   | <1:0>  |                | CCP1N  | 1<3:0> |        | 189                 |

| INTCON  | GIE                                                                         | PEIE    | TMR0IE | INTE   | IOCIE          | TMR0IF | INTF   | IOCIF  | 72                  |

| PIE1    | TMR1GIE                                                                     | ADIE    | RCIE   | TXIE   | SSP1IE         | CCP1IE | TMR2IE | TMR1IE | 73                  |

| PIR1    | TMR1GIF                                                                     | ADIF    | RCIF   | TXIF   | SSP1IF         | CCP1IF | TMR2IF | TMR1IF | 75                  |

| TMR1H   | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |         |        |        |                | 150*   |        |        |                     |

| TMR1L   | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |         |        |        | 150*           |        |        |        |                     |

| TRISA   |                                                                             | _       | TRISA5 | TRISA4 | TRISA3         | TRISA2 | TRISA1 | TRISA0 | 102                 |

| T1CON   | TMR1C                                                                       | :S<1:0> | T1CKP  | S<1:0> | T10SCEN        | T1SYNC | -      | TMR10N | 154                 |

| T1GCON  | TMR1GE                                                                      | T1GPOL  | T1GTM  | T1GSPM | T1GGO/<br>DONE | T1GVAL | T1GS   | S<1:0> | 155                 |

## TABLE 21-5: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

\* Page provides register information.

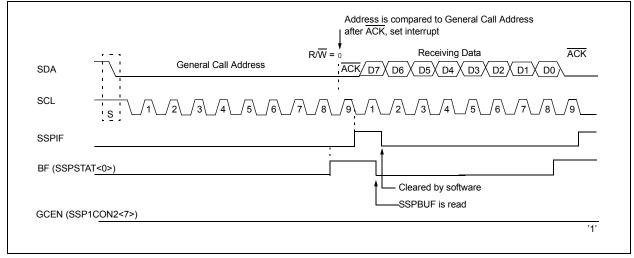

#### 25.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the  $I^2C$  protocol, defined as address 0x00. When the GCEN bit of the SSP1CON2 register is set, the slave module will automatically ACK the reception of this address regardless of the value stored in SSP1ADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave software can read SSP1BUF and respond. Figure 25-24 shows a General Call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSP1CON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the 8th falling edge of SCL. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

## FIGURE 25-24: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE

#### 25.5.9 SSP1 MASK REGISTER

An SSP1 Mask (SSP1MSK) register (Register 25-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSP1SR register during an address comparison operation. A zero ('0') bit in the SSP1MSK register has the effect of making the corresponding bit of the received address a "don't care."

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP1 operation until written with a mask value.

The SSP1 Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSP1 mask has no effect during the reception of the first (high) byte of the address.

#### 26.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 26-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 26.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RX/DT I/O pin as an input.

**Note 1:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

# 26.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 26.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

| Note: | If the receive FIFO is overrun, no additional characters will be received until the overrun condition is cleared. See <b>Section 26.1.2.5</b> |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|       | "Receive Overrun Error" for more information on overrun errors.                                                                               |

|       |                                                                                                                                               |

## 26.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- RCIE, Interrupt Enable bit of the PIE1 register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RCIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

## 26.4.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TXSTA register. The Break character transmission is then initiated by a write to the TXREG. The value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TXSTA register indicates when the transmit operation is active or idle, just as it does during normal transmission. See Figure 26-9 for the timing of the Break character sequence.

#### 26.4.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### Write to TXREG Dummy Write **BRG** Output (Shift Clock) TX (pin) Start bit bit 0 bit 1 Stop bit Break TXIF bit (Transmit Interrupt Flag) TRMT bit (Transmit Shift Empty Flag) SENDB Sampled Here Auto Cleared SENDB (send Break control bit)

SEND BREAK CHARACTER SEQUENCE

#### 26.4.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCSTA register and the Received data as indicated by RCREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when;

- RCIF bit is set

- · FERR bit is set

- RCREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 26.4.3** "**Auto-Wake-up on Break**". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDCON register before placing the EUSART in Sleep mode.

FIGURE 26-9:

| MOVIW            | Move INDFn to W                                                                                                                                                                                                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVIW ++FSRn<br>[ <i>label</i> ] MOVIWFSRn<br>[ <i>label</i> ] MOVIW FSRn++<br>[ <i>label</i> ] MOVIW FSRn<br>[ <i>label</i> ] MOVIW k[FSRn]                                                                                                                                                                                                        |

| Operands:        | n ∈ [0,1]<br>mm ∈ [00,01, 10, 11]<br>-32 ≤ k ≤ 31                                                                                                                                                                                                                                                                                                                    |

| Operation:       | $\begin{split} &\text{INDFn} \rightarrow W \\ &\text{Effective address is determined by} \\ &\text{FSR + 1 (preincrement)} \\ &\text{FSR - 1 (predecrement)} \\ &\text{FSR + k (relative offset)} \\ &\text{After the Move, the FSR value will be either:} \\ &\text{FSR + 1 (all increments)} \\ &\text{FSR - 1 (all decrements)} \\ &\text{Unchanged} \end{split}$ |

| Status Affected: | Z                                                                                                                                                                                                                                                                                                                                                                    |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

Note: The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

| Syntax:          | [ <i>label</i> ]MOVLB k                                              |

|------------------|----------------------------------------------------------------------|

| Operands:        | $0 \leq k \leq 15$                                                   |

| Operation:       | $k \rightarrow BSR$                                                  |

| Status Affected: | None                                                                 |

| Description:     | The 5-bit literal 'k' is loaded into the Bank Select Register (BSR). |

| MOVLP            | Move literal to PCLATH                                                                         |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ]MOVLP k                                                                        |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 127$                                                                              |  |  |  |  |  |  |

| Operation:       | $k \rightarrow PCLATH$                                                                         |  |  |  |  |  |  |

| Status Affected: | None                                                                                           |  |  |  |  |  |  |

| Description:     | The 7-bit literal 'k' is loaded into the PCLATH register.                                      |  |  |  |  |  |  |

| MOVLW            | Move literal to W                                                                              |  |  |  |  |  |  |

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                       |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                            |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                            |  |  |  |  |  |  |

| Status Affected: | None                                                                                           |  |  |  |  |  |  |

| Description:     | The 8-bit literal 'k' is loaded into W reg-<br>ister. The "don't cares" will assemble as '0's. |  |  |  |  |  |  |

| Words:           | 1                                                                                              |  |  |  |  |  |  |

| Cycles:          | 1                                                                                              |  |  |  |  |  |  |

| Example:         | MOVLW 0x5A                                                                                     |  |  |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                                  |  |  |  |  |  |  |

| MOVWF            | Move W to f                                                                                    |  |  |  |  |  |  |

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                       |  |  |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                                                                            |  |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                                                                          |  |  |  |  |  |  |

| Status Affected: | None                                                                                           |  |  |  |  |  |  |

| Description:     | Move data from W register to register 'f'.                                                     |  |  |  |  |  |  |

| Words:           | 1                                                                                              |  |  |  |  |  |  |

| Cycles:          | 1                                                                                              |  |  |  |  |  |  |

MOVWF OPTION\_REG Before Instruction OPTION\_REG = 0xFF W = 0x4F After Instruction OPTION\_REG = 0x4F W = 0x4F

Example:

| SWAPF            | Swap Nibbles in f                                                                                                                                                                 |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                                 |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                 |  |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                           |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                              |  |  |  |  |  |

| Description:     | The upper and lower nibbles of regis-<br>ter 'f' are exchanged. If 'd' is '0', the<br>result is placed in the W register. If 'd'<br>is '1', the result is placed in register 'f'. |  |  |  |  |  |

| XORLW            | Exclusive OR literal with W                                                                                         |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                            |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                 |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                       |  |  |  |  |  |

| Status Affected: | Z                                                                                                                   |  |  |  |  |  |

| Description:     | The contents of the W register are<br>XOR'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |  |

| TRIS             | Load TRIS Register with W                                                                                                                            |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] TRIS f                                                                                                                                     |  |  |  |  |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                    |  |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register 'f'                                                                                                                  |  |  |  |  |

| Status Affected: | None                                                                                                                                                 |  |  |  |  |

| Description:     | Move data from W register to TRIS<br>register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. |  |  |  |  |

| XORWF                                                                                                                                                                                   | Exclusive OR W with f                                             |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                                                                                                                                                                 | [label] XORWF f,d                                                 |  |  |  |  |  |  |

| Operands:                                                                                                                                                                               | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$ |  |  |  |  |  |  |

| Operation:                                                                                                                                                                              | (W) .XOR. (f) $\rightarrow$ (destination)                         |  |  |  |  |  |  |

| Status Affected:                                                                                                                                                                        | Z                                                                 |  |  |  |  |  |  |

| Description: Exclusive OR the contents of the<br>register with register 'f'. If 'd' is '0'<br>result is stored in the W register.<br>is '1', the result is stored back in r<br>ter 'f'. |                                                                   |  |  |  |  |  |  |

## TABLE 30-2: OSCILLATOR PARAMETERS

| Param<br>No. | Sym.     | Characteristic                               | Freq.<br>Tolerance | Min. | Тур† | Max. | Units | Conditions                                                            |  |

|--------------|----------|----------------------------------------------|--------------------|------|------|------|-------|-----------------------------------------------------------------------|--|

| OS08         | HFosc    | Internal Calibrated HFINTOSC                 | ±2%                |      | 16.0 |      | MHz   | $0^{\circ}C \leq TA \leq \text{+}60^{\circ}C,  V\text{DD} \geq 2.5V$  |  |

|              |          | Frequency (Note 1)                           | ±3%                | _    | 16.0 | _    | MHz   | $60^{\circ}C \le TA \le +85^{\circ}C, VDD \ge 2.5V$                   |  |

|              |          |                                              | ±5%                | _    | 16.0 | _    | MHz   | $-40^\circ C \le T_A \le +125^\circ C$                                |  |

| OS08A MFosc  |          | Internal Calibrated MFINTOSC                 | ±2%                | _    | 500  | _    | MHz   | $0^{\circ}C \leq T_A \leq \text{+}60^{\circ}C,  V\text{DD} \geq 2.5V$ |  |

|              |          | Frequency (Note 1)                           | ±3%                |      | 500  | _    | kHz   | $60^{\circ}C \le TA \le +85^{\circ}C, VDD \ge 2.5V$                   |  |

|              |          |                                              | ±5%                | _    | 500  | _    | kHz   | $-40^\circ C \le T_A \le +125^\circ C$                                |  |

| OS09         | LFosc    | Internal LFINTOSC Frequency                  | _                  |      | 31   |      | kHz   | (Note 2)                                                              |  |

| OS10*        | TIOSC ST | HFINTOSC<br>Wake-up from Sleep Start-up Time |                    | _    | 5    | 8    | μS    |                                                                       |  |

|              |          | MFINTOSC<br>Wake-up from Sleep Start-up Time | _                  | _    | 20   | 30   | μS    |                                                                       |  |

Standard Operating Conditions (unless otherwise stated)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1 μF and 0.01 μF values in parallel are recommended.

2: See Figure 31-64 and Figure 31-65, LFINTOSC Frequency Characteristics over VDD and Temperature.

#### TABLE 30-3:PLL CLOCK TIMING SPECIFICATIONS (VDD = 2.7V TO 5.5V)

| Param<br>No. | Sym.                | Characteristic                | Min.   | Тур† | Max.   | Units | Conditions |

|--------------|---------------------|-------------------------------|--------|------|--------|-------|------------|

| F10          | Fosc                | Oscillator Frequency Range    | 4      | _    | 8      | MHz   |            |

| F11          | Fsys                | On-Chip VCO System Frequency  | 16     | —    | 32     | MHz   |            |

| F12          | TRC                 | PLL Start-up Time (Lock Time) | _      | _    | 2      | ms    |            |

| F13*         | $\Delta \text{CLK}$ | CLKOUT Stability (Jitter)     | -0.25% | —    | +0.25% | %     |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

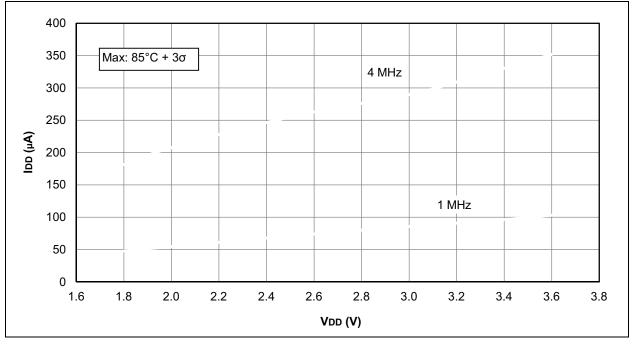

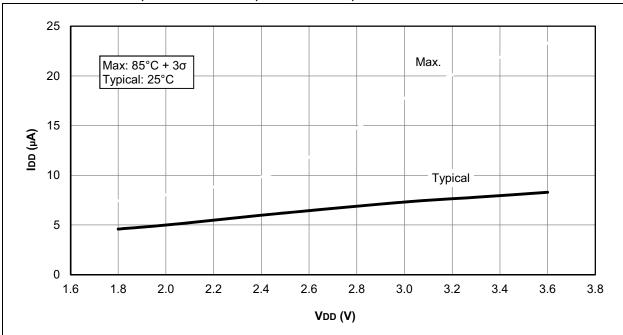

FIGURE 31-11: IDD TYPICAL, EXTERNAL CLOCK (ECM), MEDIUM-POWER MODE, PIC12LF1840 ONLY

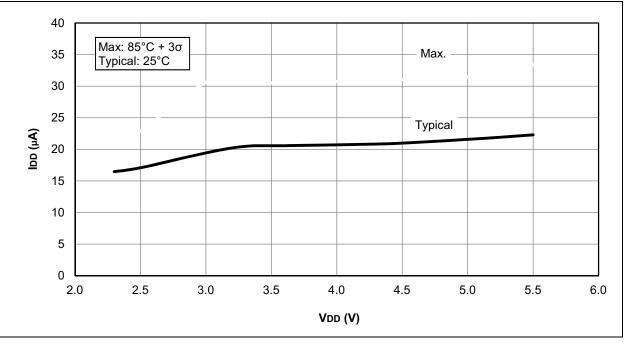

FIGURE 31-12: IDD MAXIMUM, EXTERNAL CLOCK (ECM), MEDIUM-POWER MODE, PIC12LF1840 ONLY