Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

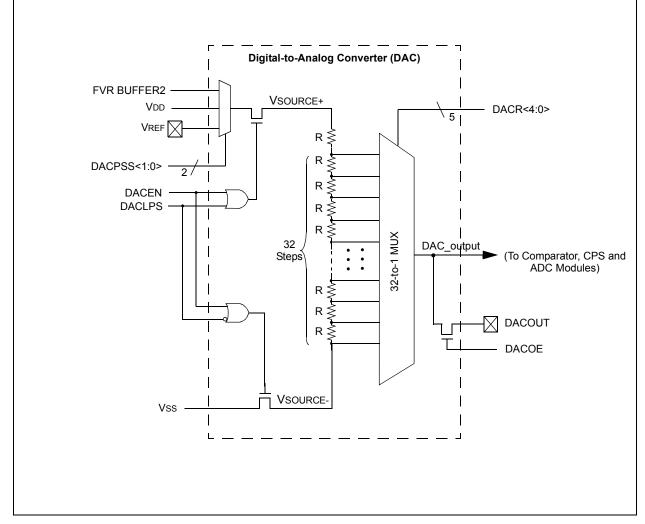

| Data Converters            | A/D 4x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-UDFN Exposed Pad                                                         |

| Supplier Device Package    | 8-UDFN (3x3)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f1840t-i-rf |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.2.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- the arithmetic status of the ALU

- · the Reset status

**REGISTER 3-1:**

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

STATUS: STATUS REGISTER

#### 3.3 Register Definitions: Status

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 29.0 "Instruction Set Summary").

Note 1: The <u>C and DC</u> bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction.

| U-0                                                                                                                                                      | U-0                                                                                                                                                    | U-0                                                                                      | R-1/q | R-1/q          | R/W-0/u          | R/W-0/u           | R/W-0/u          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------|----------------|------------------|-------------------|------------------|

|                                                                                                                                                          | —                                                                                                                                                      |                                                                                          | TO    | PD             | Z                | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7                                                                                                                                                    |                                                                                                                                                        |                                                                                          |       |                |                  |                   | bit 0            |

| Legend:                                                                                                                                                  |                                                                                                                                                        |                                                                                          |       |                |                  |                   |                  |

| R = Readable                                                                                                                                             | bit                                                                                                                                                    | W = Writable I                                                                           | bit   | U = Unimpler   | mented bit, read | as '0'            |                  |

| u = Bit is uncha                                                                                                                                         | anged                                                                                                                                                  | x = Bit is unkn                                                                          | own   | -n/n = Value a | at POR and BOI   | R/Value at all o  | ther Resets      |

| '1' = Bit is set                                                                                                                                         |                                                                                                                                                        | '0' = Bit is clea                                                                        | ared  | q = Value de   | pends on condit  | ion               |                  |

|                                                                                                                                                          |                                                                                                                                                        |                                                                                          |       |                |                  |                   |                  |

| bit 7-5                                                                                                                                                  | Unimplemen                                                                                                                                             | ted: Read as '                                                                           | )'    |                |                  |                   |                  |

| bit 4                                                                                                                                                    | TO: Time-Out                                                                                                                                           | bit                                                                                      |       |                |                  |                   |                  |

|                                                                                                                                                          | 1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time-out occurred                                                             |                                                                                          |       |                |                  |                   |                  |

| bit 3                                                                                                                                                    | PD: Power-Down bit                                                                                                                                     |                                                                                          |       |                |                  |                   |                  |

|                                                                                                                                                          | 1 = After power-up or by the CLRWDT instruction<br>0 = By execution of the SLEEP instruction                                                           |                                                                                          |       |                |                  |                   |                  |

| bit 2                                                                                                                                                    | Z: Zero bit                                                                                                                                            |                                                                                          |       |                |                  |                   |                  |

|                                                                                                                                                          | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul> |                                                                                          |       |                |                  |                   |                  |

| bit 1                                                                                                                                                    | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                              |                                                                                          |       |                |                  |                   |                  |

| <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul> |                                                                                                                                                        |                                                                                          |       |                |                  |                   |                  |

| bit 0                                                                                                                                                    | C: Carry/Borr                                                                                                                                          | Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup> |       |                |                  |                   |                  |

**Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand.

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

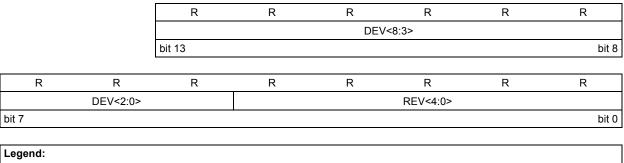

#### 4.6 Device ID and Revision ID

The memory location 8006h is where the Device ID and Revision ID are stored. The upper nine bits hold the Device ID. The lower five bits hold the Revision ID. See **Section 11.5 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

#### REGISTER 4-3: DEVID: DEVICE ID REGISTER

R = Readable bit

'1' = Bit is set '0' = Bit is cleared

#### bit 13-5 **DEV<8:0>:** Device ID bits

| Device      | DEVID<13:0> Values |          |  |  |

|-------------|--------------------|----------|--|--|

| Device      | DEV<8:0>           | REV<4:0> |  |  |

| PIC12F1840  | 011 011 100        | x xxxx   |  |  |

| PIC12LF1840 | 011 011 110        | x xxxx   |  |  |

#### bit 4-0 **REV<4:0>:** Revision ID bits

These bits are used to identify the revision (see Table under DEV<8:0> above).

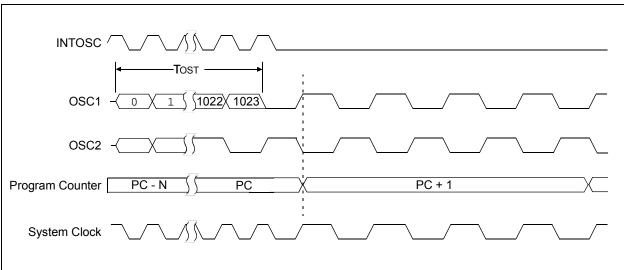

#### 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

#### 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or the internal oscillator.

#### FIGURE 5-8: TWO-SPEED START-UP

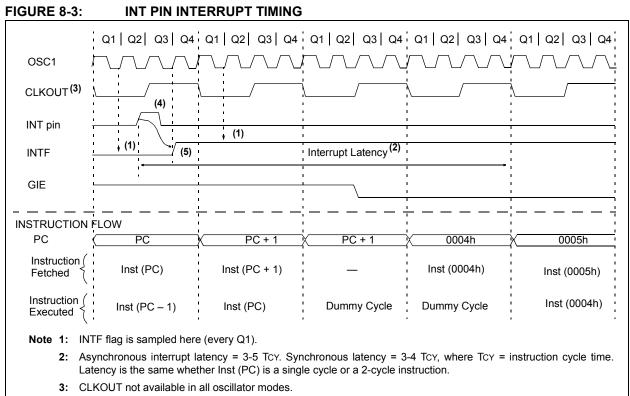

4: For minimum width of INT pulse, refer to AC specifications in Section 30.0 "Electrical Specifications".

5: INTF is enabled to be set any time during the Q4-Q1 cycles.

### 11.4 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

- 8. Repeat steps 6 and 7 as many times as required to reprogram the erased row.

#### 11.5 User ID, Device ID and Configuration Word Access

Instead of accessing program memory or EEPROM data memory, the User ID's, Device ID/Revision ID and Configuration Words can be accessed when CFGS = 1 in the EECON1 register. This is the region that would be pointed to by PC<15> = 1, but not all addresses are accessible. Different access may exist for reads and writes. Refer to Table 11-2.

When read access is initiated on an address outside the parameters listed in Table 11-2, the EEDATH:EEDATL register pair is cleared.

| Address     | Function                    | Read Access | Write Access |

|-------------|-----------------------------|-------------|--------------|

| 8000h-8003h | User IDs                    | Yes         | Yes          |

| 8006h       | Device ID/Revision ID       | Yes         | No           |

| 8007h-8008h | Configuration Words 1 and 2 | Yes         | No           |

#### TABLE 11-2: USER ID, DEVICE ID AND CONFIGURATION WORD ACCESS (CFGS = 1)

#### EXAMPLE 11-3: CONFIGURATION WORD AND DEVICE ID ACCESS

| *<br>*<br>* | PROG_ADD                               |                                                          | 1 word of program memory at the memory address:<br>Dh-08h) data will be returned in the variables;<br>LO |

|-------------|----------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|             | BANKSEL<br>MOVLW<br>MOVWF<br>CLRF      | EEADRL<br>PROG_ADDR_LO<br>EEADRL<br>EEADRH               | ;<br>; Store LSB of address                                                                              |

|             | BSF<br>BCF<br>BSF<br>NOP<br>NOP<br>BSF | EECON1, CFGS<br>INTCON, GIE<br>EECON1, RD<br>INTCON, GIE | 5 1                                                                                                      |

|             | MOVF<br>MOVWF<br>MOVF<br>MOVWF         | PROG_DATA_LO<br>EEDATH,W                                 | <pre>; Get LSB of word ; Store in user location ; Get MSB of word ; Store in user location</pre>         |

## 11.6 Write Verify

Depending on the application, good programming practice may dictate that the value written to the data EEPROM or program memory should be verified (see Example 11-6) to the desired value to be written. Example 11-6 shows how to verify a write to EEPROM.

#### EXAMPLE 11-6: EEPROM WRITE VERIFY

| BANKSEI | L EEDATL  |   | ;                    |

|---------|-----------|---|----------------------|

| MOVF    | EEDATL, W | I | ;EEDATL not changed  |

|         |           |   | ;from previous write |

| BSF     | EECON1, R | D | ;YES, Read the       |

|         |           |   | ;value written       |

| XORWF   | EEDATL, W | ſ | ;                    |

| BTFSS   | STATUS, Z |   | ;Is data the same    |

| GOTO    | WRITE_ERR | - | ;No, handle error    |

| :       |           |   | ;Yes, continue       |

|         |           |   |                      |

| Peripheral | Conditions                                                  | Description                                                        |

|------------|-------------------------------------------------------------|--------------------------------------------------------------------|

| HFINTOSC   | FOSC<2:0> = 100 and<br>IRCF<3:0> = 000x                     | INTOSC is active and device is not in Sleep.                       |

|            | BOREN<1:0> = 11                                             | BOR always enabled.                                                |

| BOR        | BOREN<1:0> = 10 and BORFS = 1                               | BOR disabled in Sleep mode, BOR Fast Start enabled.                |

|            | BOREN<1:0> = 01 and BORFS = 1                               | BOR under software control, BOR Fast Start enabled.                |

| LDO        | All PIC12F1840 devices, when<br>VREGPM = 1 and not in Sleep | The device runs off of the low-power regulator when in Sleep mode. |

### TABLE 14-1: PERIPHERALS REQUIRING THE FIXED VOLTAGE REFERENCE (FVR)

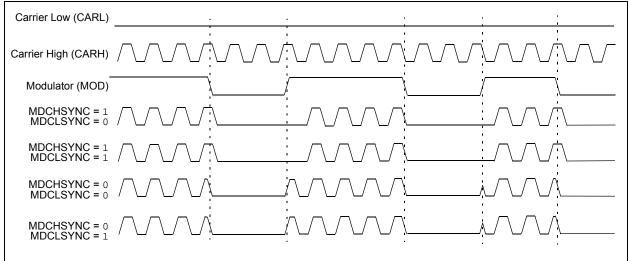

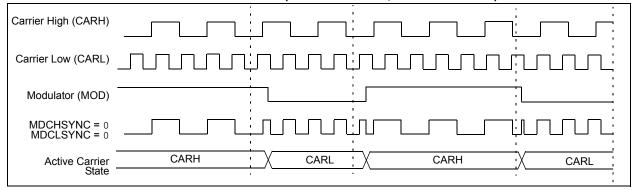

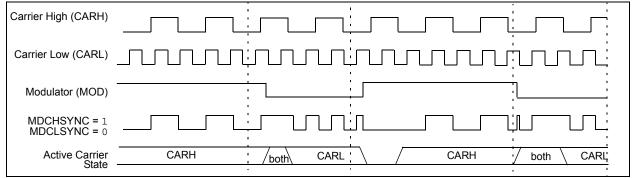

#### FIGURE 23-2: ON OFF KEYING (OOK) SYNCHRONIZATION

#### EXAMPLE 23-1: NO SYNCHRONIZATION (MDSHSYNC = 0, MDCLSYNC = 0)

#### FIGURE 23-3: CARRIER HIGH SYNCHRONIZATION (MDSHSYNC = 1, MDCLSYNC = 0)

### 23.5 Carrier Source Polarity Select

The signal provided from any selected input source for the carrier high and carrier low signals can be inverted. Inverting the signal for the carrier high source is enabled by setting the MDCHPOL bit of the MDCARH register. Inverting the signal for the carrier low source is enabled by setting the MDCLPOL bit of the MDCARL register.

#### 23.6 Carrier Source Pin Disable

Some peripherals assert control over their corresponding output pin when they are enabled. For example, when the CCP1 module is enabled, the output of CCP1 is connected to the CCP1 pin.

This default connection to a pin can be disabled by setting the MDCHODIS bit in the MDCARH register for the carrier high source and the MDCLODIS bit in the MDCARL register for the carrier low source.

#### 23.7 Programmable Modulator Data

The MDBIT of the MDCON register can be selected as the source for the modulator signal. This gives the user the ability to program the value used for modulation.

#### 23.8 Modulator Source Pin Disable

The modulator source default connection to a pin can be disabled by setting the MDMSODIS bit in the MDSRC register.

### 23.9 Modulated Output Polarity

The modulated output signal provided on the MDOUT pin can also be inverted. Inverting the modulated output signal is enabled by setting the MDOPOL bit of the MDCON register.

### 23.10 Slew Rate Control

The slew rate limitation on the output port pin can be disabled. The slew rate limitation can be removed by clearing the MDSLR bit in the MDCON register.

#### 23.11 Operation in Sleep Mode

The DSM module is not affected by Sleep mode. The DSM can still operate during Sleep, if the Carrier and Modulator input sources are also still operable during Sleep.

#### 23.12 Effects of a Reset

Upon any device Reset, the DSM module is disabled. The user's firmware is responsible for initializing the module before enabling the output. The registers are reset to their default values.

| R-0/0            | R-1/1                                                                                                                                                                 | U-0                                                                                                                 | R/W-0/0        | R/W-0/0          | U-0              | R/W-0/0          | R/W-0/0     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------|------------------|-------------|

| ABDOVF           | RCIDL                                                                                                                                                                 | —                                                                                                                   | SCKP           | BRG16            | —                | WUE              | ABDEN       |

| bit 7            |                                                                                                                                                                       |                                                                                                                     |                |                  |                  |                  | bit 0       |

|                  |                                                                                                                                                                       |                                                                                                                     |                |                  |                  |                  |             |

| Legend:          |                                                                                                                                                                       |                                                                                                                     |                |                  |                  |                  |             |

| R = Readable     | e bit                                                                                                                                                                 | W = Writable                                                                                                        | bit            | U = Unimplei     | mented bit, read | as '0'           |             |

| u = Bit is uncl  | -                                                                                                                                                                     | x = Bit is unk                                                                                                      |                | -n/n = Value     | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |                                                                                                                                                                       | '0' = Bit is cle                                                                                                    | ared           |                  |                  |                  |             |

|                  |                                                                                                                                                                       |                                                                                                                     |                |                  |                  |                  |             |

| bit 7            |                                                                                                                                                                       | to-Baud Deteo                                                                                                       | t Overflow bit |                  |                  |                  |             |

|                  | Asynchronous                                                                                                                                                          | <u>s moae</u> :<br>d timer overflo                                                                                  | wed            |                  |                  |                  |             |

|                  |                                                                                                                                                                       | d timer did not                                                                                                     |                |                  |                  |                  |             |

|                  | Synchronous                                                                                                                                                           |                                                                                                                     |                |                  |                  |                  |             |

|                  | Don't care                                                                                                                                                            |                                                                                                                     |                |                  |                  |                  |             |

| bit 6            | RCIDL: Rece                                                                                                                                                           | ive Idle Flag b                                                                                                     | it             |                  |                  |                  |             |

|                  | Asynchronou:                                                                                                                                                          |                                                                                                                     |                |                  |                  |                  |             |

|                  | 1 = Receiver                                                                                                                                                          |                                                                                                                     |                |                  |                  |                  |             |

|                  | 0 = Start bit n<br>Synchronous                                                                                                                                        |                                                                                                                     | ed and the re  | ceiver is receiv | /ing             |                  |             |

|                  | Don't care                                                                                                                                                            | <u>moue</u> .                                                                                                       |                |                  |                  |                  |             |

| bit 5            | Unimplemen                                                                                                                                                            | ted: Read as                                                                                                        | 0'             |                  |                  |                  |             |

| bit 4            | SCKP: Synch                                                                                                                                                           | SCKP: Synchronous Clock Polarity Select bit                                                                         |                |                  |                  |                  |             |

|                  | Asynchronou:                                                                                                                                                          | Asynchronous mode:                                                                                                  |                |                  |                  |                  |             |

|                  |                                                                                                                                                                       | 1 = Transmit inverted data to the TX/CK pin<br>0 = Transmit non-inverted data to the TX/CK pin                      |                |                  |                  |                  |             |

|                  |                                                                                                                                                                       | Synchronous mode:                                                                                                   |                |                  |                  |                  |             |

|                  |                                                                                                                                                                       | 1 = Data is clocked on rising edge of the clock                                                                     |                |                  |                  |                  |             |

| bit 3            |                                                                                                                                                                       | <ul> <li>0 = Data is clocked on falling edge of the clock</li> <li>BRG16: 16-bit Baud Rate Generator bit</li> </ul> |                |                  |                  |                  |             |

| DIL 3            |                                                                                                                                                                       | ud Rate Gene                                                                                                        |                |                  |                  |                  |             |

|                  |                                                                                                                                                                       | d Rate General                                                                                                      |                |                  |                  |                  |             |

| bit 2            | Unimplemen                                                                                                                                                            | ted: Read as                                                                                                        | 0'             |                  |                  |                  |             |

| bit 1            | WUE: Wake-                                                                                                                                                            | up Enable bit                                                                                                       |                |                  |                  |                  |             |

|                  | Asynchronou                                                                                                                                                           | s mode:                                                                                                             |                |                  |                  |                  |             |

|                  | <ul> <li>1 = Receiver is waiting for a falling edge. No character will be received, byte RCIF will be set. WUE will automatically clear after RCIF is set.</li> </ul> |                                                                                                                     |                |                  |                  | l be set. WUE    |             |

|                  | 0 = Receiver is operating normally                                                                                                                                    |                                                                                                                     |                |                  |                  |                  |             |

|                  | Synchronous                                                                                                                                                           | <u>mode</u> :                                                                                                       |                |                  |                  |                  |             |

| 1                | Don't care                                                                                                                                                            |                                                                                                                     | <b>_</b>       |                  |                  |                  |             |

| bit 0            |                                                                                                                                                                       | -Baud Detect                                                                                                        | Enable bit     |                  |                  |                  |             |

|                  | Asynchronou                                                                                                                                                           |                                                                                                                     |                |                  |                  |                  |             |

|                  | 1 = Auto-Baud Detect mode is enabled (clears when auto-baud is complete)                                                                                              |                                                                                                                     |                |                  |                  |                  |             |

|                  | 0 = Auto-Baud Detect mode is disabled<br><u>Synchronous mode</u> :                                                                                                    |                                                                                                                     |                |                  |                  |                  |             |

|                  | Don't care                                                                                                                                                            |                                                                                                                     |                |                  |                  |                  |             |

|                  |                                                                                                                                                                       |                                                                                                                     |                |                  |                  |                  |             |

### REGISTER 26-3: BAUDCON: BAUD RATE CONTROL REGISTER

| LSLF                                                                                                             | Logical Left Shift                                                                                                                       | MOVF             | Move f                                                                                                                                                                                                                                                                            |  |

|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:                                                                                                          | [ <i>label</i> ]LSLF f{,d}                                                                                                               | Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                         |  |

| Operands:                                                                                                        | $0 \le f \le 127$<br>d $\in$ [0,1]                                                                                                       | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                 |  |

| Operation:                                                                                                       | $(f < 7 >) \rightarrow C$                                                                                                                | Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                          |  |

|                                                                                                                  | $(f < 6:0 >) \rightarrow dest < 7:1 >$                                                                                                   | Status Affected: | Z                                                                                                                                                                                                                                                                                 |  |

| $0 \rightarrow \text{dest}<0>$<br>Status Affected: C, Z<br>Description: The contents of register 'f' are shifted |                                                                                                                                          | Description:     | The contents of register f is moved to<br>a destination dependent upon the<br>status of d. If $d = 0$ , destination is W<br>register. If $d = 1$ , the destination is file<br>register f itself. $d = 1$ is useful to test a<br>file register since status flag Z is<br>affected. |  |

|                                                                                                                  | A '0' is shifted into the LSb. If 'd' is '0',<br>the result is placed in W. If 'd' is '1', the<br>result is stored back in register 'f'. |                  |                                                                                                                                                                                                                                                                                   |  |

|                                                                                                                  | C                                                                                                                                        | Words:           | 1                                                                                                                                                                                                                                                                                 |  |

|                                                                                                                  |                                                                                                                                          | Cycles:          | 1                                                                                                                                                                                                                                                                                 |  |

|                                                                                                                  |                                                                                                                                          | Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                       |  |

| LSRF                                                                                                             | Logical Right Shift                                                                                                                      |                  | After Instruction<br>W = value in FSR register                                                                                                                                                                                                                                    |  |

| Syntax:                                                                                                          | [ <i>label</i> ]LSRF f{,d}                                                                                                               |                  | Z = 1                                                                                                                                                                                                                                                                             |  |

| Syntax:          | [ <i>label</i> ]LSRF f{,d}                                                                                                                                                                                                           |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                    |

| Operation:       | $\begin{array}{l} 0 \rightarrow dest < 7 > \\ (f < 7:1 >) \rightarrow dest < 6:0 >, \\ (f < 0 >) \rightarrow C, \end{array}$                                                                                                         |

| Status Affected: | C, Z                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. A '0' is shifted into the MSb. If 'd' is<br>'0', the result is placed in W. If 'd' is '1',<br>the result is stored back in register 'f'. |

|                  |                                                                                                                                                                                                                                      |

► C 0→ register f

| ΜΟνωι      | Move W to INDFn                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:    | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                                                                                                                                                          |

| Operands:  | $\begin{array}{l} n \in [0,1] \\ mm \in [00,01,10,11] \\ \textbf{-32} \leq k \leq 31 \end{array}$                                                                                                                                                                                                                                                                                                                                                      |

| Operation: | $\label{eq:states} \begin{array}{l} W \rightarrow INDFn \\ Effective \ address \ is \ determined \ by \\ \bullet \ FSR + 1 \ (preincrement) \\ \bullet \ FSR + 1 \ (predecrement) \\ \bullet \ FSR + k \ (relative \ offset) \\ After \ the \ Move, \ the \ FSR \ value \ will \ be \\ either: \\ \bullet \ FSR + 1 \ (all \ increments) \\ \bullet \ FSR + 1 \ (all \ increments) \\ \bullet \ FSR - 1 \ (all \ decrements) \\ Unchanged \end{array}$ |

Status Affected:

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

None

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

| OPTION           | Load OPTION_REG Register with W                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] OPTION                                                                                            |

| Operands:        | None                                                                                                      |

| Operation:       | $(W) \rightarrow OPTION\_REG$                                                                             |

| Status Affected: | None                                                                                                      |

| Description:     | Move data from W register to<br>OPTION_REG register.                                                      |

| Words:           | 1                                                                                                         |

| Cycles:          | 1                                                                                                         |

| Example:         | OPTION                                                                                                    |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION_REG = 0x4F<br>W = 0x4F |

| RESET            | Software Reset                                                                   |

|------------------|----------------------------------------------------------------------------------|

| Syntax:          | [label] RESET                                                                    |

| Operands:        | None                                                                             |

| Operation:       | Execute a device Reset. Resets the $\overline{RI}$ flag of the PCON register.    |

| Status Affected: | None                                                                             |

| Description:     | This instruction provides a way to<br>execute a hardware Reset by soft-<br>ware. |

### 30.7 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| 2. Tpp3                               |                                       |     |                |  |  |

|---------------------------------------|---------------------------------------|-----|----------------|--|--|

| т                                     |                                       |     |                |  |  |

| F                                     | Frequency                             | Т   | Time           |  |  |

| Lowerc                                | case letters (pp) and their meanings: |     |                |  |  |

| рр                                    |                                       |     |                |  |  |

| сс                                    | CCP1                                  | OSC | OSC1           |  |  |

| ck                                    | CLKOUT                                | rd  | RD             |  |  |

| cs                                    | CS                                    | rw  | RD or WR       |  |  |

| di                                    | SDIx                                  | sc  | SCKx           |  |  |

| do                                    | SDO                                   | SS  | SS             |  |  |

| dt                                    | Data in                               | tO  | TOCKI          |  |  |

| io                                    | I/O PORT                              | t1  | T1CKI          |  |  |

| mc                                    | MCLR                                  | wr  | WR             |  |  |

| Uppercase letters and their meanings: |                                       |     |                |  |  |

| S                                     |                                       |     |                |  |  |

| F                                     | Fall                                  | Р   | Period         |  |  |

| н                                     | High                                  | R   | Rise           |  |  |

| I                                     | Invalid (High-impedance)              | V   | Valid          |  |  |

| L                                     | Low                                   | Z   | High-impedance |  |  |

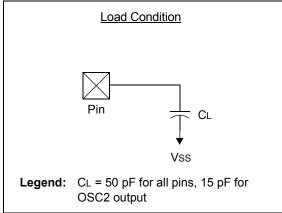

#### FIGURE 30-5: LOAD CONDITIONS

#### TABLE 30-19: DC CHARACTERISTICS FOR PIC12F1840-H (High Temp.)

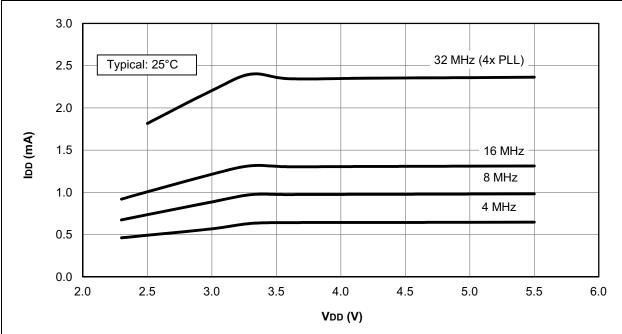

| PIC12F1840   |         |                                            | Standard Operating Conditions: (unless otherwise stated)<br>Operating Temperature: $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |      |      |       |                                                                 |

|--------------|---------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------------------------------------------------------|

| Param<br>No. | Sym.    | Characteristics                            | Min.                                                                                                                                            | Тур. | Max. | Units | Condition                                                       |

| D001         | Vdd     | Supply Voltage                             | 2.5                                                                                                                                             |      | 5.5  | V     | Fosc ≤ 32 MHz <b>(Note 2)</b>                                   |

| D002*        | Vdr     | RAM Data Retention Voltage <sup>(1)</sup>  | 2.1                                                                                                                                             | _    | 5.5  | V     | Device in Sleep mode                                            |

| D003         | VADFVR  | Fixed Voltage Reference<br>Voltage for ADC | -10                                                                                                                                             | _    | 8    | %     | 1.024V, VDD ≥ 2.5V<br>2.048V, VDD ≥ 2.5V<br>4.096V, VDD ≥ 4.75V |

| D003A        | VCDAFVR | Fixed Voltage Reference<br>Voltage for ADC | -13                                                                                                                                             | _    | 9    | %     | 1.024V, VDD ≥ 2.5V<br>2.048V, VDD ≥ 2.5V<br>4.096V, VDD ≥ 4.75V |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

2: PLL required for 32 MHz operation.

## 33.0 PACKAGING INFORMATION

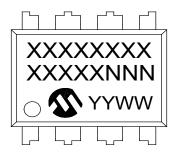

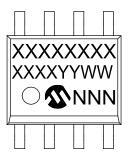

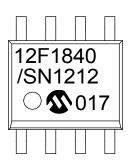

### 33.1 Package Marking Information

8-Lead PDIP (300 mil)

8-Lead SOIC (3.90 mm)

Example 12F1840 /P017 12I2

Example

| Legend: | XXX<br>Y<br>YY<br>WW<br>NNN<br>(e3)<br>*                                                                                                                                                                      | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC <sup>®</sup> designator(e3))<br>can be found on the outer packaging for this package. |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|         | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

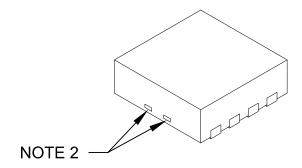

### 8-Lead Plastic Dual Flat, No Lead Package (MF) - 3x3x0.9mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |             |          |      |  |  |  |

|------------------------|-------------|-------------|----------|------|--|--|--|

| Dimensior              | MIN         | NOM         | MAX      |      |  |  |  |

| Number of Pins         | N           |             | 8        |      |  |  |  |

| Pitch                  | е           |             | 0.65 BSC |      |  |  |  |

| Overall Height         | A           | 0.80        | 0.90     | 1.00 |  |  |  |

| Standoff               | A1          | 0.00        | 0.02     | 0.05 |  |  |  |

| Contact Thickness      | A3          | 0.20 REF    |          |      |  |  |  |

| Overall Length         | D           | 3.00 BSC    |          |      |  |  |  |

| Exposed Pad Width      | E2          | 1.34 - 1.60 |          |      |  |  |  |

| Overall Width          | E           | 3.00 BSC    |          |      |  |  |  |

| Exposed Pad Length     | D2          | 1.60        | -        | 2.40 |  |  |  |

| Contact Width          | b           | 0.25        | 0.30     | 0.35 |  |  |  |

| Contact Length         | L           | 0.20        | 0.30     | 0.55 |  |  |  |

| Contact-to-Exposed Pad | ĸ           | 0.20        | -        | -    |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package may have one or more exposed tie bars at ends.

3. Package is saw singulated

4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-062C Sheet 2 of 2