Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 8-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f1840t-i-sn |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

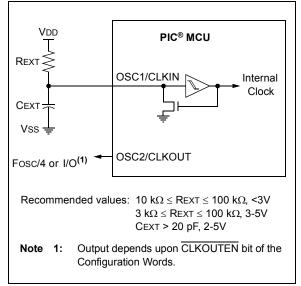

#### FIGURE 5-6: EXTERNAL RC MODES

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- threshold voltage variation

- component tolerances

- packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

#### 5.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to the internal oscillator during run-time. See Section 5.3 "Clock Switching"for more information.

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators and a dedicated Phase-Lock Loop, HFPLL that can produce one of three internal system clock sources.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz. The HFINTOSC source is generated from the 500 kHz MFINTOSC source and the dedicated Phase-Lock Loop, HFPLL. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- 2. The **MFINTOSC** (Medium-Frequency Internal Oscillator) is factory calibrated and operates at 500 kHz. The frequency of the MFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- 3. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

## 5.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Words

- Timer1 32 kHz crystal oscillator

- Internal Oscillator Block (INTOSC)

#### 5.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by value of the FOSC<2:0> bits in the Configuration Words.

- When the SCS bits of the OSCCON register = 01, the system clock source is the Timer1 oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

| Note: | Any automatic clock switch, which may     |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|

|       | occur from Two-Speed Start-up or          |  |  |  |  |  |

|       | Fail-Safe Clock Monitor, does not update  |  |  |  |  |  |

|       | the SCS bits of the OSCCON register. The  |  |  |  |  |  |

|       | user can monitor the OSTS bit of the      |  |  |  |  |  |

|       | OSCSTAT register to determine the current |  |  |  |  |  |

|       | system clock source.                      |  |  |  |  |  |

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 5-1.

#### 5.3.2 OSCILLATOR START-UP TIMER STATUS (OSTS) BIT

The Oscillator Start-up Timer Status (OSTS) bit of the OSCSTAT register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes. The OST does not reflect the status of the Timer1 oscillator.

### 5.3.3 TIMER1 OSCILLATOR

The Timer1 oscillator is a separate crystal oscillator associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the T1OSO and T1OSI device pins.

The Timer1 oscillator is enabled using the T1OSCEN control bit in the T1CON register. See **Section 21.0 "Timer1 Module with Gate Control"** for more information about the Timer1 peripheral.

#### 5.3.4 TIMER1 OSCILLATOR READY (T1OSCR) BIT

The user must ensure that the Timer1 oscillator is ready to be used before it is selected as a system clock source. The Timer1 Oscillator Ready (T1OSCR) bit of the OSCSTAT register indicates whether the Timer1 oscillator is ready to be used. After the T1OSCR bit is set, the SCS bits can be configured to select the Timer1 oscillator.

## 7.12 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- Stack Overflow Reset (STKOVF)

- Stack Underflow Reset (STKUNF)

- MCLR Reset (RMCLR)

The PCON register bits are shown in Register 7-2.

### 7.13 Register Definitions: Power Control

### REGISTER 7-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | U-0 | U-0 | R/W/HC-1/q  | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|-----|-------------|------------|------------|------------|

| STKOVF     | STKUNF     | _   |     | RMCLR       | RI         | POR        | BOR        |

| bit 7      |            |     |     | · · · · · · |            | •          | bit 0      |

| Legend:                     |                      |                                                       |  |  |  |  |  |

|-----------------------------|----------------------|-------------------------------------------------------|--|--|--|--|--|

| HC = Bit is cleared by hard | dware                | HS = Bit is set by hardware                           |  |  |  |  |  |

| R = Readable bit            | W = Writable bit     | U = Unimplemented bit, read as '0'                    |  |  |  |  |  |

| u = Bit is unchanged        | x = Bit is unknown   | -m/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |  |

| '1' = Bit is set            | '0' = Bit is cleared | q = Value depends on condition                        |  |  |  |  |  |

| bit 7   | STKOVF: Stack Overflow Flag bit                                                                                                   |

|---------|-----------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = A Stack Overflow occurred                                                                                                     |

|         | 0 = A Stack Overflow has not occurred or set to '0' by firmware                                                                   |

| bit 6   | STKUNF: Stack Underflow Flag bit                                                                                                  |

|         | 1 = A Stack Underflow occurred                                                                                                    |

|         | 0 = A Stack Underflow has not occurred or set to '0' by firmware                                                                  |

| bit 5-4 | Unimplemented: Read as '0'                                                                                                        |

| bit 3   | RMCLR: MCLR Reset Flag bit                                                                                                        |

|         | 1 = A MCLR Reset has not occurred or set to '1' by firmware                                                                       |

|         | 0 = A MCLR Reset has occurred (set to '0' in hardware when a MCLR Reset occurs)                                                   |

| bit 2   | RI: RESET Instruction Flag bit                                                                                                    |

|         | 1 = A RESET instruction has not been executed or set to '1' by firmware                                                           |

|         | 0 = A RESET instruction has been executed (set to '0' in hardware upon executing a RESET instruction)                             |

| bit 1   | POR: Power-on Reset Status bit                                                                                                    |

|         | 1 = No Power-on Reset occurred                                                                                                    |

|         | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                                             |

| bit 0   | BOR: Brown-out Reset Status bit                                                                                                   |

|         | 1 = No Brown-out Reset occurred                                                                                                   |

|         | <ul> <li>0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset<br/>occurs)</li> </ul> |

|         |                                                                                                                                   |

## 8.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to the Section 9.0 "Power-Down Mode (Sleep)" for more details.

### 8.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the INTCON register. The INTEDG bit of the OPTION\_REG register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

### 8.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the shadow registers:

- W register

- STATUS register (except for TO and PD)

- BSR register

- FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding shadow register should be modified and the value will be restored when exiting the ISR. The shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

## 12.0 I/O PORTS

In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

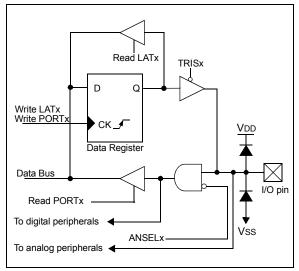

The port has three registers for its operation. These registers are:

- · TRISA register (data direction register)

- PORTA register (reads the levels on the pins of the device)

- LATA register (output latch)

PORTA has the following additional registers. They are:

- ANSELA (analog select)

- WPUA (weak pull-up)

The Data Latch (LATA register) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATA register has the same affect as a write to the corresponding PORTA register. A read of the LATA register reads of the values held in the I/O PORT latches, while a read of the PORTA register reads the actual I/O pin value.

The port has analog functions and has an ANSELA. register which can disable the digital input and save power. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 12-1.

#### FIGURE 12-1: GENERIC I/O PORT OPERATION

## 12.1 Alternate Pin Function

The Alternate Pin Function Control (APFCON) register is used to steer specific peripheral input and output functions between different pins. The APFCON register is shown in Register 12-1. For this device family, the following functions can be moved between different pins.

- RX/DT

- TX/CK

- SDO

- SS (Slave Select)

- T1G

- P1B

- CCP1/P1A

These bits have no effect on the values of any TRIS register. PORT and TRIS overrides will be routed to the correct pin. The unselected pin will be unaffected.

| <b>REGISTER</b> 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6-2: ADC | ON1: ADC CC      | NTROL RE | GISTER 1       |                 |                |              |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|----------------|-----------------|----------------|--------------|--|

| R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0/0  | R/W-0/0          | R/W-0/0  | U-0            | U-0             | R/W-0/0        | R/W-0/0      |  |

| ADFM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | ADCS<2:0>        |          | — — ADPREF<1:0 |                 |                |              |  |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                  |          |                |                 |                | bit 0        |  |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |                  |          |                |                 |                |              |  |

| R = Readable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit      | W = Writable     | bit      | U = Unimpler   | mented bit, rea | d as '0'       |              |  |

| u = Bit is unch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nanged   | x = Bit is unkr  | nown     | -n/n = Value a | at POR and BC   | R/Value at all | other Resets |  |

| '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | '0' = Bit is cle | ared     |                |                 |                |              |  |

| <ul> <li>bit 7 ADFM: ADC Result Format Select bit <ol> <li>Right justified. Six Most Significant bits of ADRESH are set to '0' when the conversion loaded.</li> <li>Left justified. Six Least Significant bits of ADRESL are set to '0' when the conversion loaded.</li> </ol> </li> <li>bit 6-4 ADCS&lt;2:0&gt;: ADC Conversion Clock Select bits <ol> <li>FRC (clock supplied from a dedicated RC oscillator)</li> <li>FOSC/64</li> <li>FOSC/16</li> <li>FRC (clock supplied from a dedicated RC oscillator)</li> <li>FRC (clock supplied from a dedicated RC oscillator)</li> <li>FRC (clock supplied from a dedicated RC oscillator)</li> </ol> </li> </ul> |          |                  |          |                |                 |                |              |  |

| bit 3-2<br>bit 1-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |                  |          |                |                 |                |              |  |

**Note 1:** When selecting the FVR or the VREF+ pin as the source of the positive reference, be aware that a minimum voltage specification exists. See **Section 30.0 "Electrical Specifications"** for details.

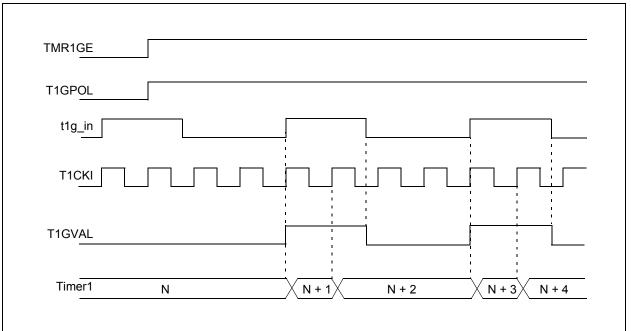

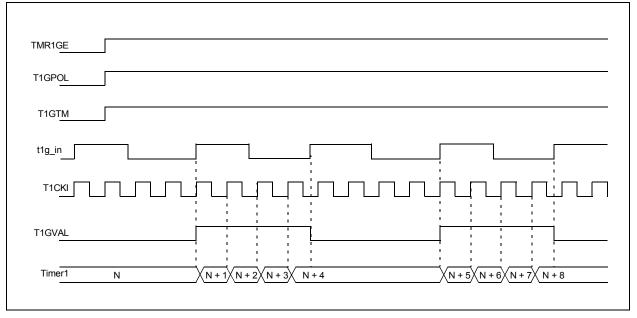

### FIGURE 21-4: TIMER1 GATE TOGGLE MODE

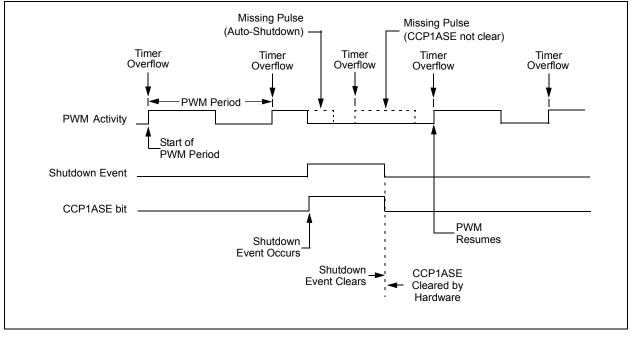

### 24.4.3 AUTO-RESTART MODE

The Enhanced PWM can be configured to automatically restart the PWM signal once the autoshutdown condition has been removed. Auto-restart is enabled by setting the P1RSEN bit in the PWM1CON register.

If auto-restart is enabled, the CCP1ASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the CCP1ASE bit will be cleared via hardware and normal operation will resume.

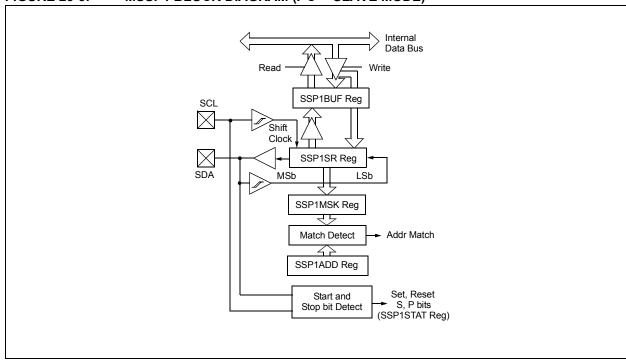

#### 25.5.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSP1CON3 register enables additional clock stretching and interrupt generation after the 8th falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSP1IF interrupt is set.

Figure 25-19 displays a standard waveform of a 7-bit Address Slave Transmission with AHEN enabled.

- 1. Bus starts Idle.

- Master sends Start condition; the S bit of SSP1STAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the 8th falling edge of the SCL line the CKP bit is cleared and SSP1IF interrupt is generated.

- 4. Slave software clears SSP1IF.

- 5. Slave software reads ACKTIM bit of SSP1CON3 register, and  $R/\overline{W}$  and  $D/\overline{A}$  of the SSP1STAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSP1BUF register clearing the BF bit.

- 7. Slave software decides from this information if it wishes to ACK or not ACK and sets the ACKDT bit of the SSP1CON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCL.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- 10. Slave hardware automatically clears the CKP bit and sets SSP1IF after the ACK if the R/W bit is set.

- 11. Slave software clears SSP1IF.

- 12. Slave loads value to transmit to the master into SSP1BUF setting the BF bit.

Note:  $\frac{\text{SSP1BUF}}{\text{ACK.}}$  cannot be loaded until after the

13. Slave sets the CKP bit, releasing the clock.

- 14. Master clocks out the data from the slave and sends an ACK value on the 9th SCL pulse.

- 15. Slave hardware copies the  $\overline{ACK}$  value into the ACKSTAT bit of the SSP1CON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not ACK the slave releases the bus, allowing the master to send a Stop and end the communication.

**Note:** Master must send a not ACK on the last byte to ensure that the slave releases the SCL line to receive a Stop.

#### REGISTER 25-2: SSP1CON1: SSP1 CONTROL REGISTER 1

| R/C/HS-0/0                         | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0/0                                                                                                                                                           | R/W-0/0                                                                                                                                                                                              | R/W-0/0                                                                                                                                       | R/W-0/0                                             | R/W-0/0                                                                                 | R/W-0/0                            |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------|

| WCOL                               | SSP10V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SSP1EN                                                                                                                                                            | CKP                                                                                                                                                                                                  |                                                                                                                                               | SSP1                                                | M<3:0>                                                                                  |                                    |

| bit 7                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                   |                                                                                                                                                                                                      |                                                                                                                                               |                                                     |                                                                                         | bit (                              |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                   |                                                                                                                                                                                                      |                                                                                                                                               |                                                     |                                                                                         |                                    |

| Legend:                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                   |                                                                                                                                                                                                      |                                                                                                                                               |                                                     |                                                                                         |                                    |

| R = Readable bit                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | W = Writable bit                                                                                                                                                  |                                                                                                                                                                                                      | U = Unimplemer                                                                                                                                | nted bit, read as '0                                | )'                                                                                      |                                    |

| u = Bit is unchan                  | ged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | x = Bit is unknow                                                                                                                                                 | vn                                                                                                                                                                                                   | -n/n = Value at F                                                                                                                             | OR and BOR/Val                                      | lue at all other Rese                                                                   | ets                                |

| '1' = Bit is set                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | '0' = Bit is cleare                                                                                                                                               | d                                                                                                                                                                                                    | HS = Bit is set by                                                                                                                            | y hardware                                          | C = User cleared                                                                        | 1                                  |

| bit 7                              | Master mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                   | ster was attempt                                                                                                                                                                                     | ed while the I <sup>2</sup> C co                                                                                                              | nditions were not                                   | valid for a transmis                                                                    | sion to be starte                  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •                                                                                                                                                                 | en while it is still ti                                                                                                                                                                              | ansmitting the previo                                                                                                                         | ous word (must be                                   | cleared in software)                                                                    |                                    |

| bit 6                              | In SPI mode:<br>1 = A new byte<br>is lost. Over<br>data, to avor<br>initiated by<br>0 = No overflow<br>In I <sup>2</sup> C mode:<br>1 = A byte is re                                                                                                                                                                                                                                                                                                                                                                                   | rflow can only occu<br>bid setting overflow,<br>writing to the SSP1<br>w<br>eccived while the s<br>st be cleared in so                                            | e SSP1BUF regi<br>Ir in Slave mode.<br>In Master mode<br>IBUF register (m<br>SSP1BUF regist                                                                                                          | In Slave mode, the<br>, the overflow bit is i<br>ust be cleared in so                                                                         | user must read th<br>not set since each<br>ftware). | case of overflow, the<br>e SSP1BUF, even if<br>new reception (and<br>SSP1OV is a "don't | only transmitting transmission) is |

| bit 5                              | <ul> <li>SSP1EN: Synchronous Serial Port Enable bit</li> <li>In both modes, when enabled, these pins must be properly configured as input or output In SPI mode:</li> <li>1 = Enables serial port and configures SCK, SDO, SDI and SS as the source of the serial port pins<sup>(2)</sup></li> <li>0 = Disables serial port and configures these pins as I/O port pins In I<sup>2</sup>C mode:</li> <li>1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins<sup>(3)</sup></li> </ul> |                                                                                                                                                                   |                                                                                                                                                                                                      |                                                                                                                                               |                                                     |                                                                                         |                                    |

| bit 4                              | <ul> <li>Disables serial port and configures these pins as I/O port pins</li> <li>CKP: Clock Polarity Select bit <ul> <li>In SPI mode:</li> </ul> </li> <li>1 = Idle state for clock is a high level</li> <li>0 = Idle state for clock is a low level <ul> <li>In I<sup>2</sup>C Slave mode:</li> <li>SCL release control</li> <li>1 = Enable clock</li> <li>0 = Holds clock low (clock stretch). (Used to ensure data setup time.)</li> <li>In I<sup>2</sup>C Master mode:</li> <li>Unused in this mode</li> </ul> </li> </ul>        |                                                                                                                                                                   |                                                                                                                                                                                                      |                                                                                                                                               |                                                     |                                                                                         |                                    |

| bit 3-0                            | 1111 = I <sup>2</sup> C Slave<br>1110 = I <sup>2</sup> C Slave<br>1101 = Reserved<br>1001 = Reserved<br>1001 = SPI Mastr<br>1001 = Reserved<br>1001 = Reserved<br>1000 = I <sup>2</sup> C Slave<br>0110 = I <sup>2</sup> C Slave<br>0101 = SPI Slave<br>0101 = SPI Slave<br>0101 = SPI Mastr<br>0001 = SPI Mastr<br>0001 = SPI Mastr                                                                                                                                                                                                   | e mode, 7-bit addres<br>are controlled Mass<br>er mode, clock = Fr<br>er mode, clock = Fo<br>e mode, clock = clock<br>e mode, 10-bit addres<br>mode, 7-bit addres | ess with Start and<br>ss with Start and<br>ter mode (slave i<br>osc/(4 * (SSPAD<br>osc / (4 * (SSPAI<br>ess<br>ss<br>K pin, <u>SS</u> pin co<br>K pin, SS pin co<br>MR2 output/2<br>osc/64<br>osc/16 | d Stop bit interrupts e<br>Stop bit interrupts e<br>dle)<br>D+1)) <sup>(5)</sup><br>DD+1)) <sup>(4)</sup><br>ntrol disabled, <del>SS</del> ca | nabled                                              | bin                                                                                     |                                    |

| regi<br>2: Who<br>3: Who<br>4: SSF | laster mode, the ov<br>ster.<br>en enabled, these p<br>en enabled, the SD<br>P1ADD values of 0,<br>P1ADD value of '0' is                                                                                                                                                                                                                                                                                                                                                                                                               | pins must be prop<br>0A and SCL pins n<br>, 1 or 2 are not suj                                                                                                    | erly configured a<br>nust be configur<br>oported for I <sup>2</sup> C r                                                                                                                              | as input or output.<br>ed as inputs.<br>node.                                                                                                 | ansmission) is ini                                  | itiated by writing to                                                                   | the SSP1BUF                        |

5: SSP1ADD value of '0' is not supported. Use SSP1M = 0000 instead.

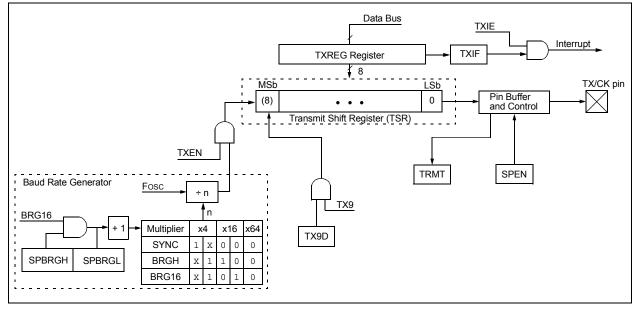

## 26.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- · Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- · Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- · 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 26-1 and Figure 26-2.

#### FIGURE 26-1: EUSART TRANSMIT BLOCK DIAGRAM

|        |                | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                  |            |                             |                |            |                             |                |                  |                             |  |

|--------|----------------|-------------------------------|-----------------------------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------------|-----------------------------|--|

| BAUD   | Fos            | c = 8.000                     | ) MHz                       | Fosc = 4.000 MHz |            |                             | Foso           | : = 3.686  | 4 MHz                       | Fos            | Fosc = 1.000 MHz |                             |  |

| RATE   | Actual<br>Rate | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 300    | _              | _                             | —                           | _                |            | _                           |                |            | _                           | 300            | 0.16             | 207                         |  |

| 1200   | —              | —                             | —                           | 1202             | 0.16       | 207                         | 1200           | 0.00       | 191                         | 1202           | 0.16             | 51                          |  |

| 2400   | 2404           | 0.16                          | 207                         | 2404             | 0.16       | 103                         | 2400           | 0.00       | 95                          | 2404           | 0.16             | 25                          |  |

| 9600   | 9615           | 0.16                          | 51                          | 9615             | 0.16       | 25                          | 9600           | 0.00       | 23                          | _              | _                | _                           |  |

| 10417  | 10417          | 0.00                          | 47                          | 10417            | 0.00       | 23                          | 10473          | 0.53       | 21                          | 10417          | 0.00             | 5                           |  |

| 19.2k  | 19231          | 0.16                          | 25                          | 19.23k           | 0.16       | 12                          | 19.2k          | 0.00       | 11                          | _              | _                | _                           |  |

| 57.6k  | 55556          | -3.55                         | 8                           | —                | _          | _                           | 57.60k         | 0.00       | 3                           | —              | _                | _                           |  |

| 115.2k | —              | _                             | —                           | —                | _          | —                           | 115.2k         | 0.00       | 1                           | _              | _                | —                           |  |

## TABLE 26-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                   |            |                             |                   |            |                             |                    |            |                             |

|--------|----------------|-------------------------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD   | Foso           | : = 32.00                     | 0 MHz                       | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0          | 0.00                          | 6666                        | 300.0             | -0.01      | 4166                        | 300.0             | 0.00       | 3839                        | 300.0              | 0.00       | 2303                        |

| 1200   | 1200           | -0.02                         | 3332                        | 1200              | -0.03      | 1041                        | 1200              | 0.00       | 959                         | 1200               | 0.00       | 575                         |

| 2400   | 2401           | -0.04                         | 832                         | 2399              | -0.03      | 520                         | 2400              | 0.00       | 479                         | 2400               | 0.00       | 287                         |

| 9600   | 9615           | 0.16                          | 207                         | 9615              | 0.16       | 129                         | 9600              | 0.00       | 119                         | 9600               | 0.00       | 71                          |

| 10417  | 10417          | 0.00                          | 191                         | 10417             | 0.00       | 119                         | 10378             | -0.37      | 110                         | 10473              | 0.53       | 65                          |

| 19.2k  | 19.23k         | 0.16                          | 103                         | 19.23k            | 0.16       | 64                          | 19.20k            | 0.00       | 59                          | 19.20k             | 0.00       | 35                          |

| 57.6k  | 57.14k         | -0.79                         | 34                          | 56.818            | -1.36      | 21                          | 57.60k            | 0.00       | 19                          | 57.60k             | 0.00       | 11                          |

| 115.2k | 117.6k         | 2.12                          | 16                          | 113.636           | -1.36      | 10                          | 115.2k            | 0.00       | 9                           | 115.2k             | 0.00       | 5                           |

|        |                | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                  |            |                             |                |            |                             |                  |            |                             |

|--------|----------------|-------------------------------|-----------------------------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fos            | c = 8.000                     | ) MHz                       | Fosc = 4.000 MHz |            |                             | Foso           | : = 3.686  | 4 MHz                       | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 299.9          | -0.02                         | 1666                        | 300.1            | 0.04       | 832                         | 300.0          | 0.00       | 767                         | 300.5            | 0.16       | 207                         |

| 1200   | 1199           | -0.08                         | 416                         | 1202             | 0.16       | 207                         | 1200           | 0.00       | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404           | 0.16                          | 207                         | 2404             | 0.16       | 103                         | 2400           | 0.00       | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615           | 0.16                          | 51                          | 9615             | 0.16       | 25                          | 9600           | 0.00       | 23                          | _                | _          | _                           |

| 10417  | 10417          | 0.00                          | 47                          | 10417            | 0.00       | 23                          | 10473          | 0.53       | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19.23k         | 0.16                          | 25                          | 19.23k           | 0.16       | 12                          | 19.20k         | 0.00       | 11                          | —                | _          | _                           |

| 57.6k  | 55556          | -3.55                         | 8                           | —                | —          | _                           | 57.60k         | 0.00       | 3                           | —                | _          | _                           |

| 115.2k | _              | _                             | _                           | —                | _          | _                           | 115.2k         | 0.00       | 1                           | _                | _          | _                           |

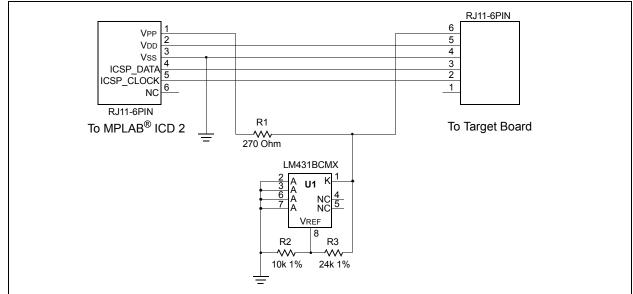

## 28.0 IN-CIRCUIT SERIAL PROGRAMMING™ (ICSP™)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, user IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP<sup>TM</sup> refer to the "PIC16F/LF1847/PIC12F/LF1840 Memory Programming Specification", (DS41439).

## 28.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

Some programmers produce VPP greater than VIHH (9.0V), an external circuit is required to limit the VPP voltage. See Figure 28-1 for example circuit.

### FIGURE 28-1: VPP LIMITER EXAMPLE CIRCUIT

| Mnen    | nonic, | Description                   |               |        | 14-Bit | Opcode | e        | Status   | N     |

|---------|--------|-------------------------------|---------------|--------|--------|--------|----------|----------|-------|

| Ореі    | rands  | Description                   | Cycles        | MSb    |        |        | LSb      | Affected | Notes |

|         |        | BYTE-ORIENTED FILE R          | EGISTER OPE   | RATIO  | NS     |        |          |          |       |

| ADDWF   | f, d   | Add W and f                   | 1             | 00     | 0111   | dfff   | ffff     | C, DC, Z | 2     |

| ADDWFC  | f, d   | Add with Carry W and f        | 1             | 11     | 1101   | dfff   | ffff     | C, DC, Z | 2     |

| ANDWF   | f, d   | AND W with f                  | 1             | 00     | 0101   | dfff   | ffff     | Z        | 2     |

| ASRF    | f, d   | Arithmetic Right Shift        | 1             | 11     | 0111   | dfff   | ffff     | C, Z     | 2     |

| LSLF    | f, d   | Logical Left Shift            | 1             | 11     | 0101   | dfff   | ffff     | C, Z     | 2     |

| LSRF    | f, d   | Logical Right Shift           | 1             | 11     | 0110   | dfff   | ffff     | C, Z     | 2     |

| CLRF    | f      | Clear f                       | 1             | 00     | 0001   | lfff   | ffff     | Z        | 2     |

| CLRW    | _      | Clear W                       | 1             | 00     | 0001   | 0000   | 00xx     | Z        |       |

| COMF    | f, d   | Complement f                  | 1             | 00     | 1001   | dfff   | ffff     | Z        | 2     |

| DECF    | f, d   | Decrement f                   | 1             | 00     | 0011   | dfff   | ffff     | Z        | 2     |

| INCF    | f, d   | Increment f                   | 1             | 00     | 1010   | dfff   | ffff     | Z        | 2     |

| IORWF   | f, d   | Inclusive OR W with f         | 1             | 00     | 0100   | dfff   | ffff     | Z        | 2     |

| MOVF    | f, d   | Move f                        | 1             | 00     | 1000   | dfff   | ffff     | Z        | 2     |

| MOVWF   | f      | Move W to f                   | 1             | 00     | 0000   | 1fff   | ffff     |          | 2     |

| RLF     | f, d   | Rotate Left f through Carry   | 1             | 00     | 1101   | dfff   | ffff     | С        | 2     |

| RRF     | f, d   | Rotate Right f through Carry  | 1             | 00     | 1100   | dfff   | ffff     | С        | 2     |

| SUBWF   | f, d   | Subtract W from f             | 1             | 00     | 0010   | dfff   | ffff     | C, DC, Z | 2     |

| SUBWFB  | f. d   | Subtract with Borrow W from f | 1             | 11     |        | dfff   |          | C, DC, Z | 2     |

| SWAPF   | f, d   | Swap nibbles in f             | 1             | 00     |        | dfff   |          | -, -,    | 2     |

| XORWF   | f, d   | Exclusive OR W with f         | 1             | 00     |        | dfff   |          | Z        | 2     |

|         |        | BYTE ORIENTED S               | SKIP OPERATIO | ONS    |        |        |          |          |       |

| DECFSZ  | f, d   | Decrement f, Skip if 0        | 1(2)          | 00     | 1011   | dfff   | ffff     |          | 1, 2  |

| INCFSZ  | f, d   | Increment f, Skip if 0        | 1(2)          | 00     | 1111   | dfff   | ffff     |          | 1, 2  |

|         |        | BIT-ORIENTED FILE RE          |               | RATION | IS     |        |          | I        |       |

| BCF     | f, b   | Bit Clear f                   | 1             | 01     | 00bb   | bfff   | ffff     |          | 2     |

| BSF     | f, b   | Bit Set f                     | 1             | 01     | 01bb   | bfff   | ffff     |          | 2     |

|         |        | BIT-ORIENTED SI               |               | NS     |        | •      |          | L        |       |

| BTFSC   | f, b   | Bit Test f, Skip if Clear     | 1 (2)         | 01     | 10bb   | bfff   | ffff     |          | 1, 2  |

| BTFSS   | f, b   | Bit Test f, Skip if Set       | 1 (2)         | 01     | 11bb   | bfff   | ffff     |          | 1, 2  |

| LITERAL |        |                               |               | 1      |        |        |          | r        | 1     |

| ADDLW   | k      | Add literal and W             | 1             | 11     | 1110   | kkkk   |          | C, DC, Z |       |

| ANDLW   | k      | AND literal with W            | 1             | 11     |        | kkkk   |          | Z        |       |

| IORLW   | k      | Inclusive OR literal with W   | 1             | 11     | 1000   | kkkk   |          | Z        |       |

| MOVLB   | k      | Move literal to BSR           | 1             | 00     | 0000   | 001k   | kkkk     |          |       |

| MOVLP   | k      | Move literal to PCLATH        | 1             | 11     | 0001   | 1kkk   | kkkk     |          |       |

| MOVLW   | k      | Move literal to W             | 1             | 11     | 0000   | kkkk   | kkkk     |          |       |

| SUBLW   | k      | Subtract W from literal       | 1             | 11     | 1100   | kkkk   | kkkk     | C, DC, Z |       |

| XORLW   | k      | Exclusive OR literal with W   | 1             | 11     | 1010   | kkkk   | 1-1-1-1- | Z        | 1     |

## TABLE 29-3: PIC12(L)F1840 INSTRUCTION SET

**Note 1:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

| CALL             | Call Subroutine                                                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                   |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                      |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<6:3>) $\rightarrow$ PC<14:11>                                                                                                                                          |

| Status Affected: | None                                                                                                                                                                                                                                      |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The 11-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle instruc-<br>tion. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                                                                      |

| Operands:        | None                                                                                                                                                                                |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT} \\ 0 \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}} \\ 1 \rightarrow \overline{\text{PD}} \end{array}$ |

| Status Affected: | TO, PD                                                                                                                                                                              |

| Description:     | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits $\overline{\text{TO}}$ and $\overline{\text{PD}}$<br>are set.            |

| CALLW            | Subroutine Call With W                                                                                                                                                                                                |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] CALLW                                                                                                                                                                                                       |  |  |  |

| Operands:        | None                                                                                                                                                                                                                  |  |  |  |

| Operation:       | (PC) +1 $\rightarrow$ TOS,<br>(W) $\rightarrow$ PC<7:0>,<br>(PCLATH<6:0>) $\rightarrow$ PC<14:8>                                                                                                                      |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                  |  |  |  |

| Description:     | Subroutine call with W. First, the return address (PC + 1) is pushed onto the return stack. Then, the contents of W is loaded into PC<7:0>, and the contents of PCLATH into PC<14:8>. CALLW is a 2-cycle instruction. |  |  |  |

| COMF             | Complement f                                                                                                                                                  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                     |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                             |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                    |  |  |  |  |

| Status Affected: | Z                                                                                                                                                             |  |  |  |  |

| Description:     | The contents of register 'f' are com-<br>plemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |

| CLRF             | Clear f                                                               |  |  |  |  |

|------------------|-----------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] CLRF f                                                        |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                                                   |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |  |  |  |  |

| Status Affected: | Z                                                                     |  |  |  |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |  |  |  |  |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

| DECF             | Decrement f                                                                                                                              |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] DECF f,d                                                                                                                       |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                              |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                      |  |  |  |

| Status Affected: | Z                                                                                                                                        |  |  |  |

| Description:     | Decrement register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |

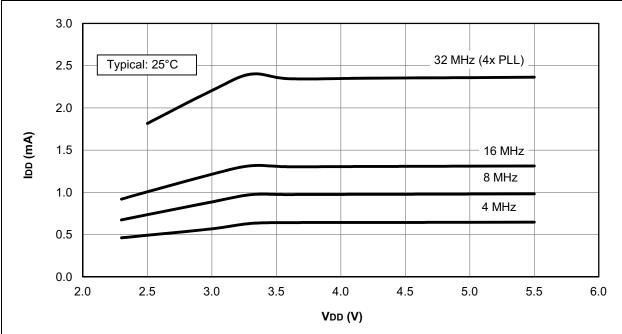

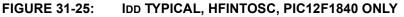

## 30.2 DC Characteristics: Supply Current (IDD) (Continued)

| PIC12LF                                                                                                                                                                                                  | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |         |           |         |                                 |            |                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------|---------|---------------------------------|------------|-------------------------------------------------|

| PIC12F1840Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                                                                                                                                                                                         |         |           |         | C for industrial                |            |                                                 |

| Param                                                                                                                                                                                                    | Device                                                                                                                                                                                  | Device  | Min. Typ† | Max. Un | Units                           | Conditions |                                                 |

| No.                                                                                                                                                                                                      | Characteristics                                                                                                                                                                         | WIIII.  | ואני      |         | Units                           | VDD        | Note                                            |