#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-VDFN Exposed Pad                                                         |

| Supplier Device Package    | 8-DFN (3x3)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lf1840-e-mf |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

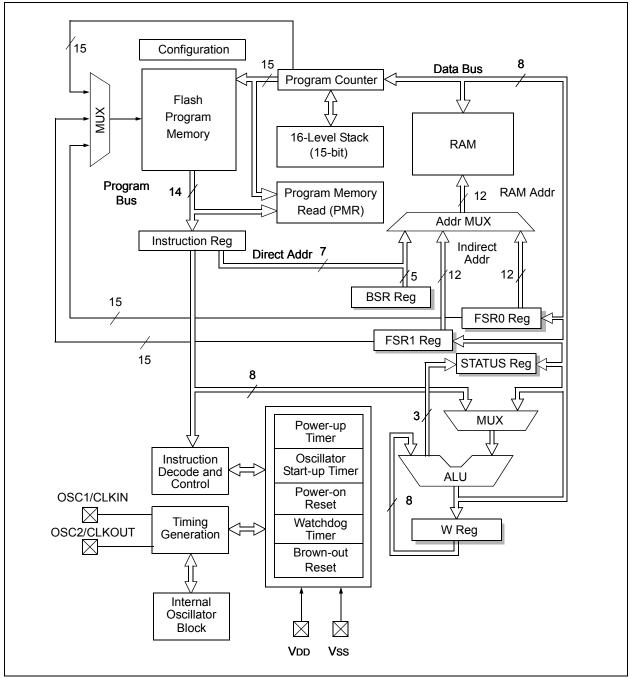

## 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- · 16-level Stack with Overflow and Underflow

- · File Select Registers

- Instruction Set

#### FIGURE 2-1: CORE BLOCK DIAGRAM

## 3.4 PCL and PCLATH

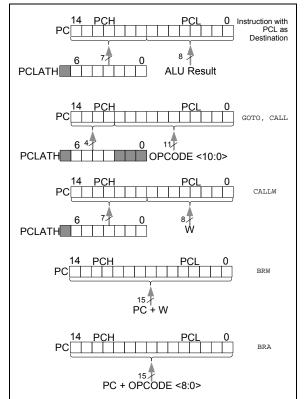

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 3-3 shows the five situations for the loading of the PC.

FIGURE 3-3: LOADING OF PC IN DIFFERENT SITUATIONS

#### 3.4.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register.

#### 3.4.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

#### 3.4.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

#### 3.4.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 +, the signed value of the operand of the BRA instruction.

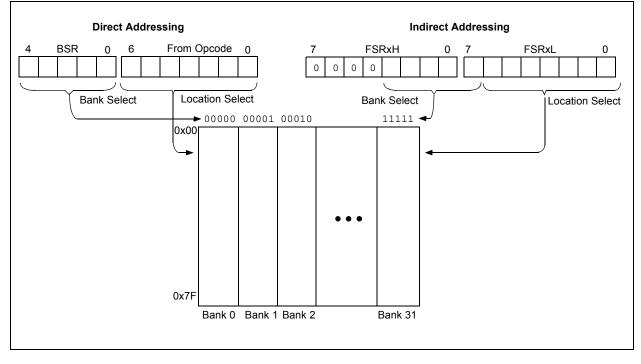

#### 3.6.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

#### FIGURE 3-9: TRADITIONAL DATA MEMORY MAP

#### 5.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

| Note: | Executing a SLEEP instruction will abort    |

|-------|---------------------------------------------|

|       | the oscillator start-up time and will cause |

|       | the OSTS bit of the OSCSTAT register to     |

|       | remain clear.                               |

## 5.4.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Words) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Words configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- Wake-up from Sleep.

| Switch From      | Switch To                                                                     | Frequency                                       | Oscillator Delay                 |

|------------------|-------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------|

| Sleep/POR        | LFINTOSC <sup>(1)</sup><br>MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup> | 31 kHz<br>31.25 kHz-500 kHz<br>31.25 kHz-16 MHz | Oscillator Warm-up Delay (Twarm) |

| Sleep/POR        | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 2 cycles                         |

| LFINTOSC         | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 1 cycle of each                  |

| Sleep/POR        | Timer1 Oscillator<br>LP, XT, HS <sup>(1)</sup>                                | 32 kHz-20 MHz                                   | 1024 Clock Cycles (OST)          |

| Any clock source | MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup>                            | 31.25 kHz-500 kHz<br>31.25 kHz-16 MHz           | 2 μs (approx.)                   |

| Any clock source | LFINTOSC <sup>(1)</sup>                                                       | 31 kHz                                          | 1 cycle of each                  |

| Any clock source | Timer1 Oscillator                                                             | 32 kHz                                          | 1024 Clock Cycles (OST)          |

| PLL inactive     | PLL active                                                                    | 16-32 MHz                                       | 2 ms (approx.)                   |

Note 1: PLL inactive.

#### 11.4 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

- 8. Repeat steps 6 and 7 as many times as required to reprogram the erased row.

#### 11.5 User ID, Device ID and Configuration Word Access

Instead of accessing program memory or EEPROM data memory, the User ID's, Device ID/Revision ID and Configuration Words can be accessed when CFGS = 1 in the EECON1 register. This is the region that would be pointed to by PC<15> = 1, but not all addresses are accessible. Different access may exist for reads and writes. Refer to Table 11-2.

When read access is initiated on an address outside the parameters listed in Table 11-2, the EEDATH:EEDATL register pair is cleared.

| Address     | Address Function            |     | Write Access |

|-------------|-----------------------------|-----|--------------|

| 8000h-8003h | User IDs                    | Yes | Yes          |

| 8006h       | Device ID/Revision ID       | Yes | No           |

| 8007h-8008h | Configuration Words 1 and 2 | Yes | No           |

#### TABLE 11-2: USER ID, DEVICE ID AND CONFIGURATION WORD ACCESS (CFGS = 1)

#### EXAMPLE 11-3: CONFIGURATION WORD AND DEVICE ID ACCESS

| *<br>*<br>* | This code block will read 1 word of program memory at the memory address:<br>PROG_ADDR_LO (must be 00h-08h) data will be returned in the variables;<br>PROG_DATA_HI, PROG_DATA_LO |                                                          |                                                                                                  |  |  |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

|             | BANKSEL<br>MOVLW<br>MOVWF<br>CLRF                                                                                                                                                 | EEADRL<br>PROG_ADDR_LO<br>EEADRL<br>EEADRH               | ;<br>; Store LSB of address                                                                      |  |  |  |  |  |

|             | BSF<br>BCF<br>BSF<br>NOP<br>NOP<br>BSF                                                                                                                                            | EECON1, CFGS<br>INTCON, GIE<br>EECON1, RD<br>INTCON, GIE | 5 1                                                                                              |  |  |  |  |  |

|             | MOVF<br>MOVWF<br>MOVF<br>MOVWF                                                                                                                                                    | PROG_DATA_LO<br>EEDATH,W                                 | <pre>; Get LSB of word ; Store in user location ; Get MSB of word ; Store in user location</pre> |  |  |  |  |  |

| U-0                                     | U-0 | R/W-1/1           | R/W-1/1 | R/W-1/1                                               | R/W-1/1          | R/W-1/1 | R/W-1/1 |  |

|-----------------------------------------|-----|-------------------|---------|-------------------------------------------------------|------------------|---------|---------|--|

| _                                       | _   | WPUA5             | WPUA4   | WPUA3                                                 | WPUA2            | WPUA1   | WPUA0   |  |

| bit 7                                   |     |                   |         |                                                       |                  |         | bit 0   |  |

|                                         |     |                   |         |                                                       |                  |         |         |  |

| Legend:                                 |     |                   |         |                                                       |                  |         |         |  |

| R = Readable bit                        |     | W = Writable      | bit     | U = Unimpler                                          | mented bit, read | as '0'  |         |  |

| u = Bit is unchanged x = Bit is unknown |     |                   | nown    | -n/n = Value at POR and BOR/Value at all other Resets |                  |         |         |  |

| '1' = Bit is set                        |     | '0' = Bit is clea | ared    |                                                       |                  |         |         |  |

#### REGISTER 12-6: WPUA: WEAK PULL-UP PORTA REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0 WPUA<5:0>: Weak Pull-up Register bits<sup>(1, 2)</sup> 1 = Pull-up enabled 0 = Pull-up disabled

**Note 1:** Global WPUEN bit of the OPTION register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|------------|---------|--------|--------|--------|--------|---------|---------|---------|---------------------|

| ANSELA     | —       |        | —      | ANSA4  |        | ANSA2   | ANSA1   | ANSA0   | 103                 |

| APFCON     | RXDTSEL | SDOSEL | SSSEL  |        | T1GSEL | TXCKSEL | P1BSEL  | CCP1SEL | 99                  |

| LATA       | —       | _      | LATA5  | LATA4  | _      | LATA2   | LATA1   | LATA0   | 103                 |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA    |         | PS<2:0> |         | 145                 |

| PORTA      | —       | _      | RA5    | RA4    | RA3    | RA2     | RA1     | RA0     | 102                 |

| TRISA      | —       | _      | TRISA5 | TRISA4 | TRISA3 | TRISA2  | TRISA1  | TRISA0  | 102                 |

| WPUA       | _       |        | WPUA5  | WPUA4  | WPUA3  | WPUA2   | WPUA1   | WPUA0   | 104                 |

#### TABLE 12-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

#### TABLE 12-3: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits   | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2   | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|--------|---------|---------|----------|----------|----------|------------|-----------|---------|---------------------|

|         | 13:8   |         | —       | FCMEN    | IESO     | CLKOUTEN | BOREN<1:0> |           | CPD     | 22                  |

| CONFIG1 | 7:0 CI |         | MCLRE   | PWRTE    | WDTE     | E<1:0>   |            | FOSC<2:0> |         | 33                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

#### 16.2 ADC Operation

#### 16.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 16.2.6 "ADC Conver-     |

|       | sion Procedure".                         |

#### 16.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- · Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 16.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

#### 16.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC oscillator source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 16.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCPx/ECCPX module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

#### TABLE 16-2: SPECIAL EVENT TRIGGER

| Device        | ECCP1 |

|---------------|-------|

| PIC12(L)F1840 | ECCP1 |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 24.0 "Capture/Compare/PWM Modules" for more information.

## 16.3 Register Definitions: ADC Control

### REGISTER 16-1: ADCON0: ADC CONTROL REGISTER 0

| U-0            | R/W-0/0                                                                   | R/W-0/0                                                                                               | R/W-0/0                                                   | R/W-0/0         | R/W-0/0         | R/W-0/0           | R/W-0/0      |

|----------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------|-----------------|-------------------|--------------|

| _              |                                                                           |                                                                                                       | CHS<4:0>                                                  |                 |                 | GO/DONE           | ADON         |

| bit 7          |                                                                           |                                                                                                       |                                                           |                 |                 |                   | bit 0        |

|                |                                                                           |                                                                                                       |                                                           |                 |                 |                   |              |

| Legend:        |                                                                           |                                                                                                       |                                                           |                 |                 |                   |              |

| R = Reada      | ble bit                                                                   | W = Writable                                                                                          | bit                                                       | U = Unimpler    | mented bit, rea | id as '0'         |              |

| u = Bit is u   | nchanged                                                                  | x = Bit is unkr                                                                                       | nown                                                      | -n/n = Value a  | at POR and BO   | OR/Value at all o | other Resets |

| '1' = Bit is s | set                                                                       | '0' = Bit is cle                                                                                      | ared                                                      |                 |                 |                   |              |

| bit 7          | Unimplomo                                                                 | nted: Read as '                                                                                       | 0'                                                        |                 |                 |                   |              |

| bit 6-2        | -                                                                         | Analog Channel                                                                                        |                                                           |                 |                 |                   |              |

|                | 11111 = FV<br>11110 = DA<br>11101 = Tei<br>11100 = Re<br>•<br>•<br>•<br>• | R (Fixed Voltage<br>C_output <sup>(1)</sup><br>mperature Indica<br>served. No char<br>served. No char | e Reference) E<br>ator <sup>(3)</sup> .<br>nnel connected | J.              | 2)              |                   |              |

|                | $00011 = AN \\ 00010 = AN \\ 00001 = AN \\ 00000 = AN $                   | 12<br>11<br>10                                                                                        |                                                           |                 |                 |                   |              |

| bit 1          | 1 = ADC co<br>This bit i                                                  | ADC Conversion<br>nversion cycle ir<br>is automatically<br>nversion comple                            | n progress. Se<br>cleared by har                          | dware when th   |                 |                   | eted.        |

| bit 0          | <b>ADON:</b> ADO<br>1 = ADC is e                                          | C Enable bit                                                                                          |                                                           | -               |                 |                   |              |

| 2:             | See Section 17.<br>See Section 14.<br>See Section 15.                     | 0 "Fixed Voltag                                                                                       | e Reference (                                             | (FVR)" for more | e information.  | nformation.       |              |

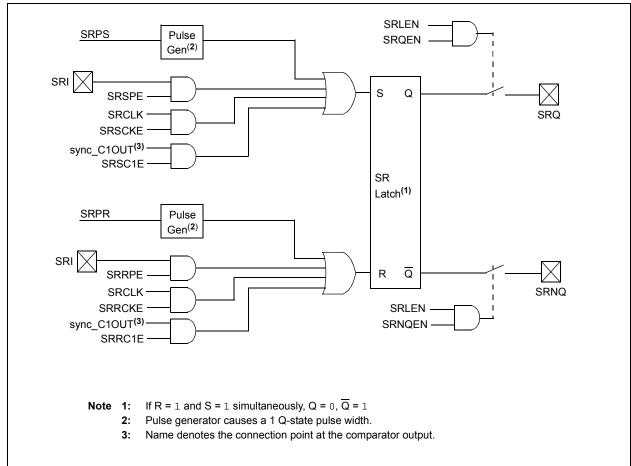

| FIGURE 18-1: | SR LATCH SIMPLIFIED BLOCK DIAGRAM |

|--------------|-----------------------------------|

|              |                                   |

| TABLE 18-1: SRCLK FF | REQUENCY TABLE |

|----------------------|----------------|

|----------------------|----------------|

| SRCLK | Divider | Fosc = 32 MHz | Fosc = 20 MHz | Fosc = 16 MHz | Fosc = 4 MHz | Fosc = 1 MHz |

|-------|---------|---------------|---------------|---------------|--------------|--------------|

| 111   | 512     | 62.5 kHz      | 39.0 kHz      | 31.3 kHz      | 7.81 kHz     | 1.95 kHz     |

| 110   | 256     | 125 kHz       | 78.1 kHz      | 62.5 kHz      | 15.6 kHz     | 3.90 kHz     |

| 101   | 128     | 250 kHz       | 156 kHz       | 125 kHz       | 31.25 kHz    | 7.81 kHz     |

| 100   | 64      | 500 kHz       | 313 kHz       | 250 kHz       | 62.5 kHz     | 15.6 kHz     |

| 011   | 32      | 1 MHz         | 625 kHz       | 500 kHz       | 125 kHz      | 31.3 kHz     |

| 010   | 16      | 2 MHz         | 1.25 MHz      | 1 MHz         | 250 kHz      | 62.5 kHz     |

| 001   | 8       | 4 MHz         | 2.5 MHz       | 2 MHz         | 500 kHz      | 125 kHz      |

| 000   | 4       | 8 MHz         | 5 MHz         | 4 MHz         | 1 MHz        | 250 kHz      |

#### **19.3 Comparator Hysteresis**

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the C1HYS bit of the CM1CON0 register.

See **Section 30.0 "Electrical Specifications"** for more information.

#### 19.4 Timer1 Gate Operation

The output resulting from a comparator operation can be used as a source for gate control of Timer1. See **Section 21.6 "Timer1 Gate"** for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

#### 19.4.1 COMPARATOR OUTPUT SYNCHRONIZATION

The output from comparator C1 can be synchronized with Timer1 by setting the C1SYNC bit of the CM1CON0 register.

Once enabled, the comparator output is latched on the falling edge of the Timer1 source clock. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figure 19-2) and the Timer1 Block Diagram (Figure 21-1) for more information.

#### **19.5** Comparator Interrupt

An interrupt can be generated upon a change in the output value of the comparator for each comparator, a rising edge detector and a Falling edge detector are present.

When either edge detector is triggered and its associated enable bit is set (C1INTP and/or C1INTN bits of the CM1CON1 register), the Corresponding Interrupt Flag bit (C1IF bit of the PIR2 register) will be set.

To enable the interrupt, you must set the following bits:

- C1ON, C1POL and C1SP bits of the CM1CON0 register

- C1IE bit of the PIE2 register

- C1INTP bit of the CM1CON1 register (for a rising edge detection)

- C1INTN bit of the CM1CON1 register (for a falling edge detection)

- PEIE and GIE bits of the INTCON register

The associated interrupt flag bit, C1IF bit of the PIR2 register, must be cleared in software. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

| Note: | Although a comparator is disabled, an      |

|-------|--------------------------------------------|

|       | interrupt can be generated by changing     |

|       | the output polarity with the C1POL bit of  |

|       | the CM1CON0 register, or by switching      |

|       | the comparator on or off with the C1ON bit |

|       | of the CM1CON0 register.                   |

## 19.6 Comparator Positive Input Selection

Configuring the C1PCH<1:0> bits of the CM1CON1 register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- · C1IN+ analog pin

- DAC\_output

- FVR Buffer2

- Vss (Ground)

See Section 14.0 "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section 17.0 "Digital-to-Analog Converter (DAC) Module" for more information on the DAC input signal.

Any time the comparator is disabled (C1ON = 0), all comparator inputs are disabled.

# 19.7 Comparator Negative Input Selection

The C1NCH bit of the CM1CON1 register directs one of two analog pins to the comparator inverting input.

**Note:** To use C1IN+ and C1INx- pins as analog input, the appropriate bits must be set in the ANSEL register and the corresponding TRIS bits must also be set to disable the output drivers.

#### **19.8 Comparator Response Time**

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in **Section 30.0 "Electrical Specifications"** for more details.

#### 19.9 Interaction with ECCP Logic

The C1 comparator can be used as a general purpose comparator. The output can be brought out to the C1OUT pin. When the ECCP auto-shutdown is active it can use the comparator signal. If auto-restart is also enabled, the comparator can be configured as a closed loop analog feedback to the ECCP, thereby, creating an analog controlled PWM.

| Note: | When the comparator module is first         |

|-------|---------------------------------------------|

|       | initialized the output state is unknown.    |

|       | Upon initialization, the user should verify |

|       | the output state of the comparator prior to |

|       | relying on the result, primarily when using |

|       | the result in connection with other         |

|       | peripheral features, such as the ECCP       |

|       | Auto-Shutdown mode.                         |

#### 19.10 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 19-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

| R/W-0/0                                                                                                                                                                                                         | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0/0                                                        | R/W-0/0 | U-0             | U-0                | U-0               | R/W-0/0 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------|-----------------|--------------------|-------------------|---------|

| C1INTP                                                                                                                                                                                                          | C1INTN                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C1PCH                                                          | l<1:0>  | _               | _                  | _                 | C1NCH   |

| bit 7                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                |         |                 |                    |                   | bit 0   |

|                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                |         |                 |                    |                   |         |

| Legend:                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                |         |                 |                    |                   |         |

| R = Readable b                                                                                                                                                                                                  | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W = Writable bit                                               |         | U = Unimpleme   | ented bit, read as | ʻ0'               |         |

| u = Bit is uncha                                                                                                                                                                                                | inged                                                                                                                                                                                                                                                                                                                                                                                                                                                   | x = Bit is unknow                                              | wn      | -n/n = Value at | POR and BOR/V      | alue at all other | Resets  |

| '1' = Bit is set                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | '0' = Bit is cleare                                            | ed      |                 |                    |                   |         |

| bit 6                                                                                                                                                                                                           | <ul> <li>1 = The C1IF interrupt flag will be set upon a positive going edge of the C1OUT bit</li> <li>0 = No interrupt flag will be set on a positive going edge of the C1OUT bit</li> <li>C1INTN: Comparator Interrupt on Negative Going Edge Enable bits</li> <li>1 = The C1IF interrupt flag will be set upon a negative going edge of the C1OUT bit</li> <li>0 = No interrupt flag will be set on a negative going edge of the C1OUT bit</li> </ul> |                                                                |         |                 |                    |                   |         |

| bit 5-4 <b>C1PCH&lt;1:0&gt;:</b> Comparator Positive Input Channel Select bits<br>10 = C1VP connects to FVR Voltage Reference<br>01 = C1VP connects to DAC Voltage Reference<br>00 = C1VP connects to C1IN+ pin |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                |         |                 |                    |                   |         |

| bit 3-1                                                                                                                                                                                                         | Unimplemente                                                                                                                                                                                                                                                                                                                                                                                                                                            | ed: Read as '0'                                                |         |                 |                    |                   |         |

| bit 0                                                                                                                                                                                                           | 1 = C1VN co                                                                                                                                                                                                                                                                                                                                                                                                                                             | parator Negative I<br>ponnects to C1IN1-<br>ponnects to C1IN0- | pin     | elect bit       |                    |                   |         |

#### REGISTER 19-2: CM1CON1: COMPARATOR C1 CONTROL REGISTER 1

#### REGISTER 19-3: CMOUT: COMPARATOR OUTPUT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0/0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

| _     | _   | —   | —   | —   | _   | —   | MC1OUT |

| bit 7 |     |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-1 Unimplemented: Read as '0'

bit 0 MC10UT: Mirror Copy of C10UT bit

#### TABLE 19-3: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELA  | _      | -      | —      | ANSA4  | —      | ANSA2  | ANSA1  | ANSA0  | 103                 |

| CM1CON0 | C1ON   | C10UT  | C10E   | C1POL  | _      | C1SP   | C1HYS  | C1SYNC | 141                 |

| CM1CON1 | C1INTP | C1INTN | C1PCI  | H<1:0> | _      | —      | _      | C1NCH  | 142                 |

| CMOUT   | _      | —      | —      | —      | —      | —      | _      | MC1OUT | 142                 |

| INTCON  | GIE    | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 72                  |

| PIE2    | OSFIE  | —      | C1IE   | EEIE   | BCL1IE | —      | -      | —      | 74                  |

| PIR2    | OSFIF  | _      | C1IF   | EEIF   | BCL1IF | —      | _      | —      | 76                  |

| TRISA   | —      |        | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 102                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the comparator module.

| R/W-x/u                                                             | R/W-x/u                                                                                                                  | R/W-x/u                                                                                                                                                                         | U-0          | R/W-x/u            | R/W-x/u                       | R/W-x/u        | R/W-x/u              |  |  |  |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------|-------------------------------|----------------|----------------------|--|--|--|

| MDCLODIS                                                            | MDCLPOL                                                                                                                  | MDCLSYNC                                                                                                                                                                        |              |                    | MDCI                          | _<3:0>         |                      |  |  |  |

| bit 7                                                               |                                                                                                                          |                                                                                                                                                                                 |              |                    |                               |                | bit C                |  |  |  |

|                                                                     |                                                                                                                          |                                                                                                                                                                                 |              |                    |                               |                |                      |  |  |  |

| Legend:                                                             |                                                                                                                          |                                                                                                                                                                                 |              |                    |                               |                |                      |  |  |  |

| R = Readable                                                        | bit                                                                                                                      | W = Writable I                                                                                                                                                                  | oit          | •                  | nented bit, read              |                |                      |  |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR |                                                                                                                          |                                                                                                                                                                                 |              |                    | R/Value at all o              | other Resets   |                      |  |  |  |

| '1' = Bit is set                                                    |                                                                                                                          | '0' = Bit is clea                                                                                                                                                               | ared         |                    |                               |                |                      |  |  |  |

|                                                                     |                                                                                                                          |                                                                                                                                                                                 |              |                    |                               |                |                      |  |  |  |

| bit 7                                                               |                                                                                                                          | Modulator Low                                                                                                                                                                   |              | •                  |                               | POS of the MD( | CADL register        |  |  |  |

|                                                                     | is disable                                                                                                               | • •                                                                                                                                                                             | periprierar  | output pin (selec  |                               |                | JARL register        |  |  |  |

|                                                                     | 0 = Output s                                                                                                             | ignal driving the                                                                                                                                                               | peripheral   | output pin (selec  | ted by MDCL<3                 | 3:0> of the MD | CARL register        |  |  |  |

|                                                                     | is enable                                                                                                                |                                                                                                                                                                                 |              |                    |                               |                |                      |  |  |  |

| bit 6                                                               |                                                                                                                          | DL: Modulator Low Carrier Polarity Select bit                                                                                                                                   |              |                    |                               |                |                      |  |  |  |

|                                                                     | <ul> <li>1 = Selected low carrier signal is inverted</li> <li>0 = Selected low carrier signal is not inverted</li> </ul> |                                                                                                                                                                                 |              |                    |                               |                |                      |  |  |  |

| bit 5                                                               |                                                                                                                          | 0                                                                                                                                                                               |              |                    | ahle hit                      |                |                      |  |  |  |

| bit 5                                                               |                                                                                                                          | <b>MDCLSYNC:</b> Modulator Low Carrier Synchronization Enable bit<br>1 = Modulator waits for a falling edge on the low time carrier signal before allowing a switch to the high |              |                    |                               |                |                      |  |  |  |

|                                                                     | time carr                                                                                                                | rier                                                                                                                                                                            |              |                    | ·                             | Ū.             | literi te tire riig. |  |  |  |

|                                                                     | 0 = Modulate                                                                                                             | or Output is not                                                                                                                                                                | synchronize  | ed to the low time | e carrier signal <sup>(</sup> | 1)             |                      |  |  |  |

| bit 4                                                               | •                                                                                                                        | nted: Read as 'o                                                                                                                                                                |              |                    |                               |                |                      |  |  |  |

| bit 3-0                                                             |                                                                                                                          |                                                                                                                                                                                 |              | r Selection bits   | 1)                            |                |                      |  |  |  |

|                                                                     | 1111 = Res                                                                                                               | erved. No char                                                                                                                                                                  | inel connect | ted.               |                               |                |                      |  |  |  |

|                                                                     | •                                                                                                                        |                                                                                                                                                                                 |              |                    |                               |                |                      |  |  |  |

|                                                                     | •                                                                                                                        |                                                                                                                                                                                 |              |                    |                               |                |                      |  |  |  |

|                                                                     | 0101 = Reserved. No channel connected.                                                                                   |                                                                                                                                                                                 |              |                    |                               |                |                      |  |  |  |

|                                                                     |                                                                                                                          | P1 output (PWM                                                                                                                                                                  | •            | • •                |                               |                |                      |  |  |  |

|                                                                     |                                                                                                                          | erence Clock me                                                                                                                                                                 | 0            |                    |                               |                |                      |  |  |  |

|                                                                     | $0.010 = R_{}$                                                                                                           | erved No char                                                                                                                                                                   | inel connect | hed                |                               |                |                      |  |  |  |

|                                                                     | 0010 = Res<br>0001 = MD(                                                                                                 | erved. No char<br>CIN1 port pin                                                                                                                                                 | inel connect | ted.               |                               |                |                      |  |  |  |

#### REGISTER 23-4: MDCARL: MODULATION LOW CARRIER CONTROL REGISTER

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

| TABLE 23-1: SUMMARY OF REGISTERS ASSOCIATED WITH DATA SIGNAL MODULATOR MO |

|---------------------------------------------------------------------------|

|---------------------------------------------------------------------------|

| Name   | Bit 7    | Bit 6   | Bit 5    | Bit 4  | Bit 3     | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|--------|----------|---------|----------|--------|-----------|-------|-------|-------|---------------------|

| MDCARH | MDCHODIS | MDCHPOL | MDCHSYNC | —      | MDCH<3:0> |       |       |       | 169                 |

| MDCARL | MDCLODIS | MDCLPOL | MDCLSYNC | _      | MDCL<3:0> |       |       |       | 170                 |

| MDCON  | MDEN     | MDOE    | MDSLR    | MDOPOL | MDOUT     | _     | —     | MDBIT | 167                 |

| MDSRC  | MDMSODIS | —       | —        |        | MDMS<3:0> |       |       | 168   |                     |

Legend: — = unimplemented, read as '0'. Shaded cells are not used in the Data Signal Modulator mode.

| R/W-0/0                                                                                                                                                      | R/W-0/0                                                                                                                      | R/W-0/0          | R/W-0/0    | R/W-0/0            | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------|------------|--------------------|------------------|----------------|--------------|

| P1RSEN                                                                                                                                                       |                                                                                                                              |                  |            | P1DC<6:0>          |                  |                |              |

| bit 7                                                                                                                                                        |                                                                                                                              |                  |            |                    |                  |                | bit 0        |

|                                                                                                                                                              |                                                                                                                              |                  |            |                    |                  |                |              |

| Legend:                                                                                                                                                      |                                                                                                                              |                  |            |                    |                  |                |              |

| R = Readab                                                                                                                                                   | ole bit                                                                                                                      | W = Writable     | bit        | U = Unimpler       | nented bit, read | d as '0'       |              |

| u = Bit is unchanged x = Bit is unkno                                                                                                                        |                                                                                                                              |                  | nown       | -n/n = Value a     | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is se                                                                                                                                              | et                                                                                                                           | '0' = Bit is cle | ared       |                    |                  |                |              |

|                                                                                                                                                              |                                                                                                                              |                  |            |                    |                  |                |              |

| bit 7                                                                                                                                                        | P1RSEN: P                                                                                                                    | WM Restart Ena   | able bit   |                    |                  |                |              |

|                                                                                                                                                              | 1 = Upon auto-shutdown, the CCP1ASE bit clears automatically once the shutdown event<br>away; the PWM restarts automatically |                  |            |                    |                  |                |              |

|                                                                                                                                                              | 0 = Upon a                                                                                                                   | uto-shutdown, C  | CP1ASE mus | st be cleared in a | software to res  | tart the PWM   |              |

| bit 6-0                                                                                                                                                      | bit 6-0 P1DC<6:0>: PWM Delay Count bits                                                                                      |                  |            |                    |                  |                |              |

| P1DC1 = Number of Fosc/4 (4 * Tosc) cycles between the scheduled time when a PWM signa<br>should transition active and the actual time it transitions active |                                                                                                                              |                  |            |                    |                  |                | a PWM signal |

|                                                                                                                                                              | N                                                                                                                            | :                |            |                    |                  |                |              |

#### REGISTER 24-3: PWM1CON: ENHANCED PWM CONTROL REGISTER

**Note 1:** Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the Oscillator mode or Fail-Safe mode is enabled.

## **REGISTER 24-4: PSTR1CON: PWM STEERING CONTROL REGISTER<sup>(1)</sup>**

| U-0   | U-0 | U-0 | R/W-0/0  | R/W-0/0  | R/W-0/0  | R/W-0/0 | R/W-1/1 |

|-------|-----|-----|----------|----------|----------|---------|---------|

| —     | —   | —   | STR1SYNC | Reserved | Reserved | STR1B   | STR1A   |

| bit 7 |     |     |          |          |          |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | STR1SYNC: Steering Sync bit                                                                                                                                            |

|         | <ul> <li>1 = Output steering update occurs on next PWM period</li> <li>0 = Output steering update occurs at the beginning of the instruction cycle boundary</li> </ul> |

| bit 3-2 | Reserved: Read as '0'. Maintain these bits clear.                                                                                                                      |

| bit 1   | STR1B: Steering Enable bit B                                                                                                                                           |

|         | 1 = P1B pin has the PWM waveform with polarity control from CCP1M<1:0>                                                                                                 |

|         | 0 = P1B pin is assigned to port pin                                                                                                                                    |

| bit 0   | STR1A: Steering Enable bit A                                                                                                                                           |

|         | 1 = P1A pin has the PWM waveform with polarity control from CCP1M<1:0>                                                                                                 |

|         | 0 = P1A pin is assigned to port pin                                                                                                                                    |

|         |                                                                                                                                                                        |

Note 1: The PWM Steering mode is available only when the CCP1CON register bits CCP1M<3:2> = 11 and P1M<1:0> = 00.

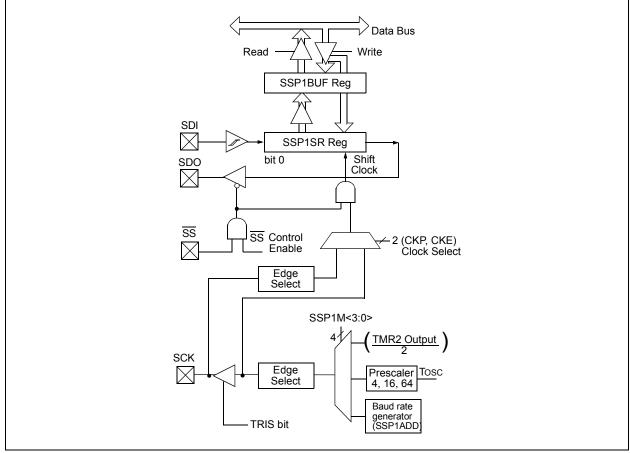

## 25.0 MASTER SYNCHRONOUS SERIAL PORT MODULE

#### 25.1 Master SSP (MSSP1) Module Overview

The Master Synchronous Serial Port (MSSP1) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP1 module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

Figure 25-1 is a block diagram of the SPI interface module.

#### 27.5 Timer Resources

To measure the change in frequency of the capacitive sensing oscillator, a fixed time base is required. For the period of the fixed time base, the capacitive sensing oscillator is used to clock either Timer0 or Timer1. The frequency of the capacitive sensing oscillator is equal to the number of counts in the timer divided by the period of the fixed time base.

#### 27.6 Fixed Time Base

To measure the frequency of the capacitive sensing oscillator, a fixed time base is required. Any timer resource or software loop can be used to establish the fixed time base. It is up to the end user to determine the method in which the fixed time base is generated.

| Note: | The fixed time base can not be generated  |

|-------|-------------------------------------------|

|       | by the timer resource that the capacitive |

|       | sensing oscillator is clocking.           |

#### 27.6.1 TIMER0

To select Timer0 as the timer resource for the CPS module:

- Set the T0XCS bit of the CPSCON0 register.

- Clear the TMR0CS bit of the OPTION\_REG register.

When Timer0 is chosen as the timer resource, the capacitive sensing oscillator will be the clock source for Timer0. Refer to **Section 20.0 "Timer0 Module"** for additional information.

#### 27.6.2 TIMER1

To select Timer1 as the timer resource for the CPS module, set the TMR1CS<1:0> of the T1CON register to '11'. When Timer1 is chosen as the timer resource, the capacitive sensing oscillator will be the clock source for Timer1. Because the Timer1 module has a gate control, developing a time base for the frequency measurement can be simplified by using the Timer0 overflow flag.

It is recommend that the Timer0 overflow flag, in conjunction with the Toggle mode of the Timer1 Gate, be used to develop the fixed time base required by the software portion of the CPS module. Refer to **Section 21.6 "Timer1 Gate**" for additional information.

TABLE 27-2: TIMER1 ENABLE FUNCTION

| TMR10N | TMR1GE | Timer1 Operation       |

|--------|--------|------------------------|

| 0      | 0      | Off                    |

| 0      | 1      | Off                    |

| 1      | 0      | On                     |

| 1      | 1      | Count Enabled by input |

#### 27.7 Software Control

The software portion of the CPS module is required to determine the change in frequency of the capacitive sensing oscillator. This is accomplished by the following:

- Setting a fixed time base to acquire counts on Timer0 or Timer1.

- Establishing the nominal frequency for the capacitive sensing oscillator.

- Establishing the reduced frequency for the capacitive sensing oscillator due to an additional capacitive load.

- Set the frequency threshold.

#### 27.7.1 NOMINAL FREQUENCY (NO CAPACITIVE LOAD)

To determine the nominal frequency of the capacitive sensing oscillator:

- Remove any extra capacitive load on the selected CPSx pin.

- At the start of the fixed time base, clear the timer resource.

- At the end of the fixed time base save the value in the timer resource.

The value of the timer resource is the number of oscillations of the capacitive sensing oscillator for the given time base. The frequency of the capacitive sensing oscillator is equal to the number of counts on in the timer, divided by the period of the fixed time base.

#### 27.7.2 REDUCED FREQUENCY (ADDITIONAL CAPACITIVE LOAD)

The extra capacitive load will cause the frequency of the capacitive sensing oscillator to decrease. To determine the reduced frequency of the capacitive sensing oscillator:

- Add a typical capacitive load on the selected CPSx pin.

- Use the same fixed time base as the nominal frequency measurement.

- At the start of the fixed time base, clear the timer resource.

- At the end of the fixed time base, save the value in the timer resource.

The value of the timer resource is the number of oscillations of the capacitive sensing oscillator with an additional capacitive load. The frequency of the capacitive sensing oscillator is equal to the number of counts on in the timer, divided by the period of the fixed time base. This frequency should be less than the value obtained during the nominal frequency measurement.

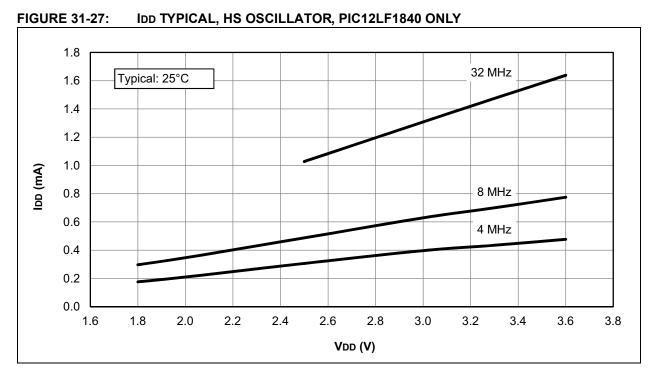

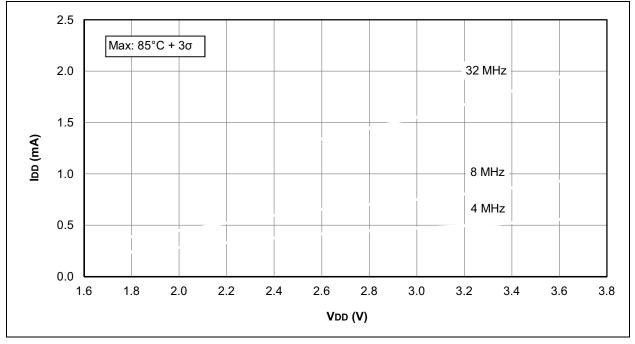

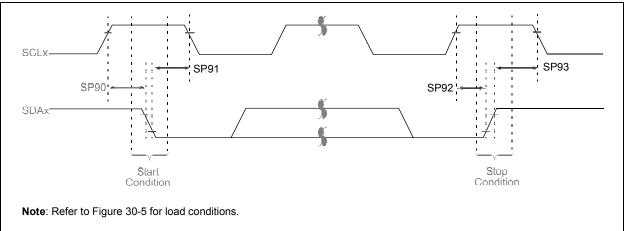

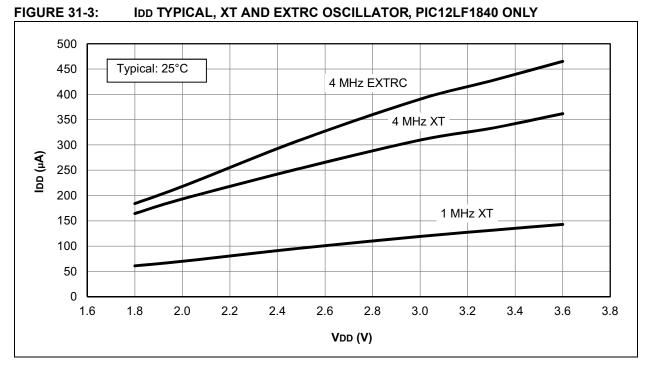

#### 30.2 DC Characteristics: Supply Current (IDD) (Continued)

| PIC12LF1840 |                                    | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq Ta \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq Ta \leq +125^\circ C \mbox{ for extended} \end{array} $ |                        |            |           |                                                               |                                            |  |  |

|-------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|-----------|---------------------------------------------------------------|--------------------------------------------|--|--|