Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 8-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lf1840-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                                                        | Function | Input<br>Type | Output<br>Type | Description                           |

|-------------------------------------------------------------------------------------------------------------|----------|---------------|----------------|---------------------------------------|

| RA4/AN3/CPS3/OSC2/                                                                                          | RA4      | TTL           | CMOS           | General purpose I/O.                  |

| CLKOUT/T1OSO/C1IN1-/CLKR/<br>SDO <sup>(1)</sup> /CK <sup>(1)</sup> /TX <sup>(1)</sup> /P1B <sup>(1)</sup> / | AN3      | AN            | _              | ADC Channel 3 input.                  |

| T1G/MDCIN2                                                                                                  | · CPS3   | AN            |                | Capacitive sensing input 3.           |

|                                                                                                             | OSC2     | _             | XTAL           | Crystal/Resonator (LP, XT, HS modes). |

|                                                                                                             | CLKOUT   | _             | CMOS           | Fosc/4 output.                        |

|                                                                                                             | T10S0    | XTAL          | XTAL           | Timer1 oscillator connection.         |

|                                                                                                             | C1IN1-   | AN            | —              | Comparator C1 negative input.         |

|                                                                                                             | CLKR     | _             | CMOS           | Clock Reference output.               |

|                                                                                                             | SDO      | _             | CMOS           | SPI data output.                      |

|                                                                                                             | СК       | ST            | CMOS           | USART synchronous clock.              |

|                                                                                                             | TX       | _             | CMOS           | USART asynchronous transmit.          |

|                                                                                                             | P1B      | _             | CMOS           | PWM output.                           |

|                                                                                                             | T1G      | ST            | —              | Timer1 Gate input.                    |

|                                                                                                             | MDCIN2   | ST            | _              | Modulator Carrier Input 2.            |

| RA5/CLKIN/OSC1/T1OSI/                                                                                       | RA5      | TTL           | CMOS           | General purpose I/O.                  |

| T1CKI/SRNQ/P1A <sup>(1)</sup> /CCP1 <sup>(1)</sup> /<br>DT <sup>(1)</sup> /RX <sup>(1)</sup>                | CLKIN    | CMOS          | _              | External clock input (EC mode).       |

| DIV/RAV                                                                                                     | OSC1     | XTAL          | —              | Crystal/Resonator (LP, XT, HS modes). |

|                                                                                                             | T10SI    | XTAL          | XTAL           | Timer1 oscillator connection.         |

|                                                                                                             | T1CKI    | ST            | _              | Timer1 clock input.                   |

|                                                                                                             | SRNQ     |               | CMOS           | SR Latch inverting output.            |

|                                                                                                             | P1A      |               | CMOS           | PWM output.                           |

|                                                                                                             | CCP1     | ST            | CMOS           | Capture/Compare/PWM 1.                |

|                                                                                                             | DT       | ST            | CMOS           | USART synchronous data.               |

|                                                                                                             | RX       | ST            | —              | USART asynchronous input.             |

| VDD                                                                                                         | Vdd      | Power         | —              | Positive supply.                      |

| Vss                                                                                                         | Vss      | Power         | —              | Ground reference.                     |

TABLE 1-2:

PIC12(L)F1840 PINOUT DESCRIPTION (CONTINUED)

Legend:AN = Analog input or output<br/>TTL = TTL compatible inputCMOS = CMOS compatible input or output<br/>ST = Schmitt Trigger input with CMOS levelsOD = Open DrainHV = High VoltageXTAL = CrystalLevels

Note 1: Alternate pin function selected with the APFCON (Register 12-1) register.

### 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The High directive will set bit<7> if a label points to a location in program memory.

EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants                   |

|-----------------------------|

| RETLW DATA0 ;Index0 data    |

| RETLW DATA1 ;Index1 data    |

| RETLW DATA2                 |

| RETLW DATA3                 |

| my_function                 |

| ; LOTS OF CODE              |

| MOVLW LOW constants         |

| MOVWF FSR1L                 |

| MOVLW HIGH constants        |

| MOVWF FSR1H                 |

| MOVIW 0[FSR1]               |

| ;THE PROGRAM MEMORY IS IN W |

## 3.2 Data Memory Organization

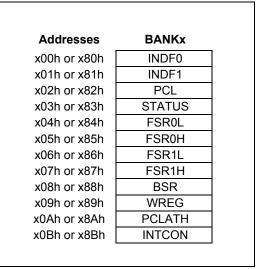

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-2):

- 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.6 "Indirect Addressing"** for more information.

## 3.2.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-5.

## 9.2 Low-Power Sleep Mode

The PIC12F1840 device contains an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode. The PIC12F1840 allows the user to optimize the operating current in Sleep, depending on the application requirements.

A Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register. With this bit set, the LDO and reference circuitry are placed in a low-power state when the device is in Sleep.

## 9.2.1 SLEEP CURRENT VS. WAKE-UP TIME

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

#### 9.2.2 PERIPHERAL USAGE IN SLEEP

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The LDO will remain in the normal power mode when those peripherals are enabled. The Low-Power Sleep mode is intended for use with these peripherals:

- Brown-Out Reset (BOR)

- Watchdog Timer (WDT)

- · External interrupt pin/Interrupt-on-change pins

- Timer1 (with external clock source)

- Comparator

- · ECCP (Capture mode)

Note: The PIC12LF1840 does not have a configurable Low-Power Sleep mode. PIC12LF1840 is an unregulated device and is always in the lowest power state when in Sleep, with no wake-up time penalty. This device has a lower maximum VDD and I/O voltage than the PIC12F1840. See Section 30.0 "Electrical Specifications" for more information.

## 10.6 Register Definitions: Watchdog Control

|               |                                                              | R/W-0/0                                                                                                 | R/W-1/1       | R/W-0/0          | R/W-1/1        | R/W-1/1         | R/W-0/0      |  |  |  |  |

|---------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------|------------------|----------------|-----------------|--------------|--|--|--|--|

| _             | —                                                            |                                                                                                         |               | WDTPS<4:0>       |                |                 | SWDTEN       |  |  |  |  |

| it 7          | ·                                                            | •                                                                                                       |               |                  |                |                 | bit (        |  |  |  |  |

|               |                                                              |                                                                                                         |               |                  |                |                 |              |  |  |  |  |

| egend:        |                                                              |                                                                                                         |               |                  |                |                 |              |  |  |  |  |

| = Readabl     | le bit                                                       | W = Writable                                                                                            | bit           | U = Unimpleme    | ented bit, rea | d as '0'        |              |  |  |  |  |

| = Bit is und  | changed                                                      | x = Bit is unkr                                                                                         | nown          | -m/n = Value at  | POR and B      | OR/Value at all | other Resets |  |  |  |  |

| ' = Bit is se | et                                                           | '0' = Bit is clea                                                                                       | ared          |                  |                |                 |              |  |  |  |  |

| it 7-6        | Unimpleme                                                    | nted: Read as '                                                                                         | 0'            |                  |                |                 |              |  |  |  |  |

| it 5-1        | -                                                            | >: Watchdog Ti                                                                                          |               | elect bits       |                |                 |              |  |  |  |  |

|               |                                                              | Prescale Rate                                                                                           |               |                  |                |                 |              |  |  |  |  |

|               |                                                              | eserved. Result                                                                                         | s in minimum  | interval (1:32)  |                |                 |              |  |  |  |  |

|               | •                                                            |                                                                                                         |               | 1101101 (1102)   |                |                 |              |  |  |  |  |

|               | •                                                            |                                                                                                         |               |                  |                |                 |              |  |  |  |  |

|               | •                                                            |                                                                                                         |               |                  |                |                 |              |  |  |  |  |

|               | 10011 = Reserved. Results in minimum interval (1:32)         |                                                                                                         |               |                  |                |                 |              |  |  |  |  |

|               | 10010 = 1:8388608 (2 <sup>23</sup> ) (Interval 256s nominal) |                                                                                                         |               |                  |                |                 |              |  |  |  |  |

|               | 10001 = 1:4194304 (2 <sup>22</sup> ) (Interval 128s nominal) |                                                                                                         |               |                  |                |                 |              |  |  |  |  |

|               | 10000 = 1:2097152 (2 <sup>21</sup> ) (Interval 64s nominal)  |                                                                                                         |               |                  |                |                 |              |  |  |  |  |

|               | 01111 = 1:1048576 (2 <sup>20</sup> ) (Interval 32s nominal)  |                                                                                                         |               |                  |                |                 |              |  |  |  |  |

|               | 01110 = 1:                                                   | 01110 = $1:524288 (2^{19})$ (Interval 16s nominal)<br>01101 = $1:262144 (2^{18})$ (Interval 8s nominal) |               |                  |                |                 |              |  |  |  |  |

|               |                                                              | 262144 (2 <sup>13</sup> ) (In<br>131072 (2 <sup>17</sup> ) (In                                          |               |                  |                |                 |              |  |  |  |  |

|               |                                                              | 65536 (Interval                                                                                         |               |                  |                |                 |              |  |  |  |  |

|               |                                                              |                                                                                                         |               |                  |                |                 |              |  |  |  |  |

|               |                                                              | 01010 = 1:32768 (Interval 1s nominal)<br>01001 = 1:16384 (Interval 512 ms nominal)                      |               |                  |                |                 |              |  |  |  |  |

|               | 01000 = 1:8192 (Interval 256 ms nominal)                     |                                                                                                         |               |                  |                |                 |              |  |  |  |  |

|               |                                                              | 4096 (Interval 1                                                                                        |               |                  |                |                 |              |  |  |  |  |

|               |                                                              | 2048 (Interval 6                                                                                        |               | ·                |                |                 |              |  |  |  |  |

|               |                                                              | 1024 (Interval 3)                                                                                       |               |                  |                |                 |              |  |  |  |  |

|               |                                                              | 512 (Interval 16<br>256 (Interval 8 r                                                                   |               |                  |                |                 |              |  |  |  |  |

|               |                                                              |                                                                                                         |               |                  |                |                 |              |  |  |  |  |

|               |                                                              | 00010 = 1:128 (Interval 4 ms nominal)<br>00001 = 1:64 (Interval 2 ms nominal)                           |               |                  |                |                 |              |  |  |  |  |

|               |                                                              | 32 (Interval 1 m                                                                                        |               |                  |                |                 |              |  |  |  |  |

| it O          | SWDTEN: S                                                    | oftware Enable/                                                                                         | Disable for V | Vatchdog Timer b | it             |                 |              |  |  |  |  |

|               | <u>If WDTE&lt;1:0</u>                                        | )> = <u>00</u> :                                                                                        |               | C                |                |                 |              |  |  |  |  |

|               | This bit is ig                                               | nored.                                                                                                  |               |                  |                |                 |              |  |  |  |  |

|               | If WDTE<1:0                                                  |                                                                                                         |               |                  |                |                 |              |  |  |  |  |

|               | 1 = WDT is                                                   |                                                                                                         |               |                  |                |                 |              |  |  |  |  |

|               | 0 = WDT is                                                   |                                                                                                         |               |                  |                |                 |              |  |  |  |  |

|               | If WDTE<1:(                                                  |                                                                                                         |               |                  |                |                 |              |  |  |  |  |

|               | This bit is ig                                               | nored.                                                                                                  |               |                  |                |                 |              |  |  |  |  |

## REGISTER 10-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

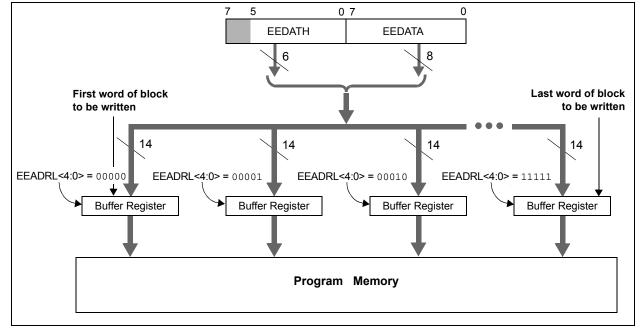

After the "BSF EECON1, WR" instruction, the processor requires two cycles to set up the write operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2 ms, only during the cycle in which the write takes place (i.e., the last word of the block write). This is not Sleep mode as the clocks and peripherals will

continue to run. The processor does not stall when LWLO = 1, loading the write latches. After the write cycle, the processor will resume operation with the third instruction after the EECON1 WRITE instruction.

#### EXAMPLE 11-4: ERASING ONE ROW OF PROGRAM MEMORY

| ; | ; This row erase routine assumes the following: |             |                  |     |                                                          |  |  |  |

|---|-------------------------------------------------|-------------|------------------|-----|----------------------------------------------------------|--|--|--|

| ; | 1. A                                            | valid addre | ess within the e | era | se block is loaded in ADDRH:ADDRL                        |  |  |  |

| ; | 2. AI                                           | DRH and ADD | ORL are located  | in  | shared data memory 0x70 - 0x7F                           |  |  |  |

|   |                                                 |             |                  |     |                                                          |  |  |  |

|   |                                                 | BCF         | INTCON,GIE       | ;   | Disable ints so required sequences will execute properly |  |  |  |

|   |                                                 | BANKSEL     | EEADRL           |     |                                                          |  |  |  |

|   |                                                 | MOVF        | ADDRL,W          | ;   | Load lower 8 bits of erase address boundary              |  |  |  |

|   |                                                 | MOVWF       | EEADRL           |     |                                                          |  |  |  |

|   |                                                 | MOVF        | ADDRH,W          | ;   | Load upper 6 bits of erase address boundary              |  |  |  |

|   |                                                 | MOVWF       | EEADRH           |     |                                                          |  |  |  |

|   |                                                 | BSF         | EECON1,EEPGD     | ;   | Point to program memory                                  |  |  |  |

|   |                                                 | BCF         | EECON1,CFGS      | ;   | Not configuration space                                  |  |  |  |

|   |                                                 | BSF         | EECON1, FREE     | ;   | Specify an erase operation                               |  |  |  |

|   |                                                 | BSF         | EECON1,WREN      | ;   | Enable writes                                            |  |  |  |

|   |                                                 |             |                  |     |                                                          |  |  |  |

|   |                                                 | MOVLW       | 55h              |     | Start of required sequence to initiate erase             |  |  |  |

|   |                                                 | MOVWF       | EECON2           | ;   | Write 55h                                                |  |  |  |

|   |                                                 | MOVLW       | 0AAh             | ;   |                                                          |  |  |  |

|   | Required<br>Sequence                            | MOVWF       | EECON2           |     | Write AAh                                                |  |  |  |

|   | luir<br>uer                                     | BSF         | EECON1,WR        |     | Set WR bit to begin erase                                |  |  |  |

|   | seq.                                            | NOP         |                  |     | Any instructions here are ignored as processor           |  |  |  |

|   | щω                                              |             |                  |     | halts to begin erase sequence                            |  |  |  |

|   |                                                 | NOP         |                  | ;   | Processor will stop here and wait for erase complete.    |  |  |  |

|   |                                                 |             |                  |     |                                                          |  |  |  |

|   | L                                               |             |                  | ;   | after erase processor continues with 3rd instruction     |  |  |  |

|   |                                                 | BCF         | EECON1,WREN      | ;   | Disable writes                                           |  |  |  |

|   |                                                 | BSF         | INTCON,GIE       | ;   | Enable interrupts                                        |  |  |  |

|   |                                                 |             |                  |     |                                                          |  |  |  |

| R/W-0/0          | R/W-0/0                                                                                                                        | R/W-0/0                                                                                                                            | R/W/HC-0/0      | R/W-x/q             | R/W-0/0              | R/S/HC-0/0       | R/S/HC-0/0        |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------|----------------------|------------------|-------------------|--|--|--|

| EEPGD            | CFGS                                                                                                                           | LWLO                                                                                                                               | FREE            | WRERR               | WREN                 | WR               | RD                |  |  |  |

| bit 7            |                                                                                                                                |                                                                                                                                    |                 |                     |                      |                  | bit C             |  |  |  |

|                  |                                                                                                                                |                                                                                                                                    |                 |                     |                      |                  |                   |  |  |  |

| Legend:          |                                                                                                                                |                                                                                                                                    |                 |                     |                      |                  |                   |  |  |  |

| R = Readable     | bit                                                                                                                            | W = Writable                                                                                                                       | bit             | U = Unimpler        | mented bit, read     | d as '0'         |                   |  |  |  |

| S = Bit can on   | ly be set                                                                                                                      | x = Bit is unk                                                                                                                     | nown            | -n/n = Value        | at POR and BC        | R/Value at all o | ther Resets       |  |  |  |

| '1' = Bit is set |                                                                                                                                | '0' = Bit is cle                                                                                                                   | ared            | HC = Bit is cl      | eared by hardw       | vare             |                   |  |  |  |

|                  |                                                                                                                                |                                                                                                                                    |                 |                     |                      |                  |                   |  |  |  |

| bit 7            |                                                                                                                                | sh Program/Da                                                                                                                      |                 | -                   | bit                  |                  |                   |  |  |  |

|                  |                                                                                                                                | s program spa<br>s data EEPRO                                                                                                      |                 | ory                 |                      |                  |                   |  |  |  |

| bit 6            |                                                                                                                                | Program/Data                                                                                                                       | •               | Configuration       | Soloct bit           |                  |                   |  |  |  |

| DILO             |                                                                                                                                | s Configuration                                                                                                                    |                 |                     |                      |                  |                   |  |  |  |

|                  |                                                                                                                                | s Flash Progra                                                                                                                     |                 |                     | •                    |                  |                   |  |  |  |

| bit 5            | LWLO: Load                                                                                                                     | Write Latches                                                                                                                      | Only bit        | -                   |                      |                  |                   |  |  |  |

|                  | <u>If CFGS = 1 (</u>                                                                                                           | (Configuration                                                                                                                     | space) OR CFO   | <u>GS = 0_and E</u> | <u>EPGD = 1 (pro</u> | ogram Flash):    |                   |  |  |  |

|                  |                                                                                                                                |                                                                                                                                    | mand does no    | ot initiate a w     | rite; only the p     | program memor    | y latches are     |  |  |  |

|                  |                                                                                                                                | ated.                                                                                                                              |                 | alua fram EE        |                      | into ano avo as  | o voo om diatabaa |  |  |  |

|                  |                                                                                                                                |                                                                                                                                    |                 |                     | program memo         | into program m   | emory latches     |  |  |  |

|                  |                                                                                                                                |                                                                                                                                    |                 |                     | p. eg. a             |                  |                   |  |  |  |

|                  |                                                                                                                                | and EEPGD =                                                                                                                        |                 |                     |                      |                  |                   |  |  |  |

|                  | •                                                                                                                              |                                                                                                                                    |                 | initiates a writ    | e to the data El     | EPROM.           |                   |  |  |  |

| bit 4            | •                                                                                                                              | FREE: Program Flash Erase Enable bit<br>f CFGS = 1 (Configuration space) <b>OR</b> <u>CFGS = 0 and EEPGD = 1 (program Flash)</u> : |                 |                     |                      |                  |                   |  |  |  |

|                  | _                                                                                                                              |                                                                                                                                    |                 | _                   |                      | ed by hardware   | after comple-     |  |  |  |

|                  |                                                                                                                                | of erase).                                                                                                                         | operation on t  |                     | orninana (cicar      |                  | and compic-       |  |  |  |

|                  | 0 = Perf                                                                                                                       | forms a write o                                                                                                                    | peration on the | next WR com         | nmand.               |                  |                   |  |  |  |

|                  | If FEPGD = (                                                                                                                   | and CFGS =                                                                                                                         | 0. (Accessing   | data EEPROI         | M)                   |                  |                   |  |  |  |

|                  |                                                                                                                                |                                                                                                                                    |                 |                     |                      | and a write cyc  | le.               |  |  |  |

| bit 3            | WRERR: EE                                                                                                                      | PROM Error FI                                                                                                                      | ag bit          |                     | -                    |                  |                   |  |  |  |

|                  | 1 = Condition                                                                                                                  | n indicates an                                                                                                                     | improper prog   | ram or erase        | sequence atte        | mpt or termina   | tion (bit is set  |  |  |  |

|                  | automatically on any set attempt (write '1') of the WR bit).<br>0 = The program or erase operation completed normally.         |                                                                                                                                    |                 |                     |                      |                  |                   |  |  |  |

| 1.11.0           |                                                                                                                                |                                                                                                                                    |                 | leted normally      | /.                   |                  |                   |  |  |  |

| bit 2            | -                                                                                                                              | ram/Erase Ena                                                                                                                      |                 |                     |                      |                  |                   |  |  |  |

|                  | <ul> <li>1 = Allows program/erase cycles</li> <li>0 = Inhibits programming/erasing of program Flash and data EEPROM</li> </ul> |                                                                                                                                    |                 |                     |                      |                  |                   |  |  |  |

| bit 1            | WR: Write Co                                                                                                                   |                                                                                                                                    | song of progre  |                     |                      |                  |                   |  |  |  |

|                  |                                                                                                                                |                                                                                                                                    | h or data EEP   | ROM program         | /erase operatio      | on.              |                   |  |  |  |

|                  |                                                                                                                                |                                                                                                                                    |                 |                     |                      | operation is co  | mplete.           |  |  |  |

|                  |                                                                                                                                | bit can only be                                                                                                                    |                 |                     |                      |                  |                   |  |  |  |

|                  | -                                                                                                                              | -                                                                                                                                  | on to the Flash | or data EEPR        | OM is complete       | e and inactive.  |                   |  |  |  |

| L 11 A           | RD: Read Co                                                                                                                    |                                                                                                                                    |                 |                     |                      |                  |                   |  |  |  |

| bit 0            |                                                                                                                                |                                                                                                                                    | ob or data T    |                     | Dood takes           |                  | in placed in      |  |  |  |

| bit 0            | 1 = Initiates                                                                                                                  |                                                                                                                                    |                 |                     |                      | one cycle. RD    | is cleared in     |  |  |  |

## REGISTER 11-5: EECON1: EEPROM CONTROL 1 REGISTER

## 15.3 Temperature Output

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to **Section 16.0** "Analog-to-Digital Converter (ADC) Module" for detailed information.

| Note: | Every time the ADC MUX is changed to              |

|-------|---------------------------------------------------|

|       | the temperature indicator output selection        |

|       | (CHS bit in the ADCCON0 register), wait           |

|       | 500 $\mu$ sec for the sampling capacitor to fully |

|       | charge before sampling the temperature            |

|       | indicator output.                                 |

#### 15.3.1 ADC ACQUISITION TIME

To ensure accurate temperature measurements, the user must wait at least 200 usec after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200 usec between sequential conversions of the temperature indicator output.

| TABLE 15-2: | SUMMARY OF REGISTERS ASSOCIATED WITH THE TEMPERATURE INDICATOR |

|-------------|----------------------------------------------------------------|

|-------------|----------------------------------------------------------------|

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|--------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFV | R<1:0> | ADFVF | R<1:0> | 111                 |

**Legend:** Shaded cells are unused by the temperature indicator module.

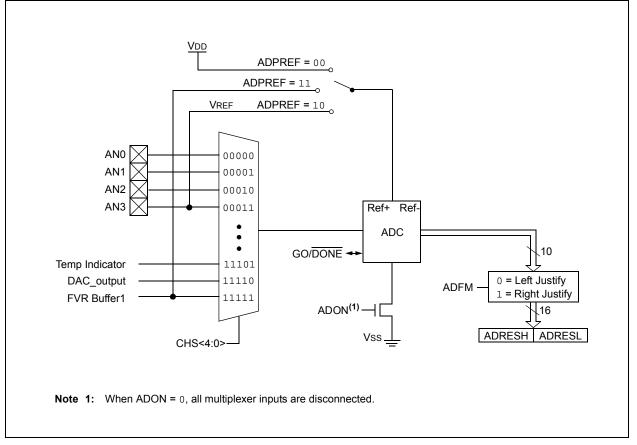

## 16.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 16-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

## FIGURE 16-1: ADC BLOCK DIAGRAM

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

## 20.2 Register Definitions: Option Register

## REGISTER 20-1: OPTION\_REG: OPTION REGISTER

| R/W-1/1          | R/W-1/1                                                                             | R/W-1/1                                                                                              | R/W-1/1    | R/W-1/1       | R/W-1/1          | R/W-1/1          | R/W-1/1      |  |  |  |

|------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------|---------------|------------------|------------------|--------------|--|--|--|

| WPUEN            | INTEDG                                                                              | TMR0CS                                                                                               | TMR0SE     | PSA           |                  | PS<2:0>          |              |  |  |  |

| bit 7            |                                                                                     |                                                                                                      |            |               |                  |                  | bit 0        |  |  |  |

| Legend:          |                                                                                     |                                                                                                      |            |               |                  |                  |              |  |  |  |

| R = Readable     | bit V                                                                               | / = Writable                                                                                         | bit        | U = Unimpler  | mented bit, read | d as '0'         |              |  |  |  |

| u = Bit is unch  | nanged x                                                                            | = Bit is unkr                                                                                        | nown       | •             |                  | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is set | -                                                                                   | )' = Bit is cle                                                                                      | ared       |               |                  |                  |              |  |  |  |

|                  |                                                                                     |                                                                                                      |            |               |                  |                  |              |  |  |  |

| bit 7            | WPUEN: Weak                                                                         | Pull-Up Ena                                                                                          | ble bit    |               |                  |                  |              |  |  |  |

|                  | 1 = All weak pul                                                                    |                                                                                                      | · · ·      | •             | ,                |                  |              |  |  |  |

|                  | 0 = Weak pull-u                                                                     | -                                                                                                    | -          | al WPUA latch | values           |                  |              |  |  |  |

| bit 6            | INTEDG: Interru                                                                     |                                                                                                      |            |               |                  |                  |              |  |  |  |

|                  | 1 = Interrupt on rising edge of INT pin<br>0 = Interrupt on falling edge of INT pin |                                                                                                      |            |               |                  |                  |              |  |  |  |

| bit 5            | TMR0CS: Time                                                                        | • •                                                                                                  | •          |               |                  |                  |              |  |  |  |

|                  | 1 = Transition on TOCKI pin                                                         |                                                                                                      |            |               |                  |                  |              |  |  |  |

|                  | 0 = Internal instruction cycle clock (Fosc/4)                                       |                                                                                                      |            |               |                  |                  |              |  |  |  |

| bit 4            | TMR0SE: Timer                                                                       |                                                                                                      | •          |               |                  |                  |              |  |  |  |

|                  |                                                                                     | t on high-to-low transition on T0CKI pin<br>t on low-to-high transition on T0CKI pin                 |            |               |                  |                  |              |  |  |  |

| bit 3            | <b>PSA:</b> Prescaler                                                               | •                                                                                                    |            | TUCKI pin     |                  |                  |              |  |  |  |

|                  |                                                                                     | •                                                                                                    |            | ) module      |                  |                  |              |  |  |  |

|                  |                                                                                     | L = Prescaler is not assigned to the Timer0 module<br>D = Prescaler is assigned to the Timer0 module |            |               |                  |                  |              |  |  |  |

| bit 2-0          | PS<2:0>: Presc                                                                      | aler Rate Se                                                                                         | elect bits |               |                  |                  |              |  |  |  |

|                  | Bit Val                                                                             | ue Timer0                                                                                            | Rate       |               |                  |                  |              |  |  |  |

|                  | 000                                                                                 | 1:2                                                                                                  |            |               |                  |                  |              |  |  |  |

|                  | 001<br>010                                                                          |                                                                                                      |            |               |                  |                  |              |  |  |  |

|                  | 010                                                                                 | 1:1                                                                                                  | 6          |               |                  |                  |              |  |  |  |

|                  | 100<br>101                                                                          |                                                                                                      |            |               |                  |                  |              |  |  |  |

|                  | 101                                                                                 |                                                                                                      |            |               |                  |                  |              |  |  |  |

|                  | 111                                                                                 | 1:2                                                                                                  | 56         |               |                  |                  |              |  |  |  |

|                  |                                                                                     |                                                                                                      |            |               |                  |                  |              |  |  |  |

| ABLE 20-1:       | SUMMARY                                                                             | DE REGIST                                                                                            | ERS ASSO   |               | H TIMER0         |                  |              |  |  |  |

#### TABLE 20-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

| Name       | Bit 7                  | Bit 6  | Bit 5                            | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Register<br>on Page |

|------------|------------------------|--------|----------------------------------|--------|--------|---------|--------|--------|---------------------|

| CPSCON0    | CPSON                  | CPSRM  |                                  | _      | CPSRN  | IG<1:0> | CPSOUT | T0XCS  | 282                 |

| INTCON     | GIE                    | PEIE   | TMR0IE                           | INTE   | IOCIE  | TMR0IF  | INTF   | IOCIF  | 72                  |

| OPTION_REG | WPUEN                  | INTEDG | INTEDG TMR0CS TMR0SE PSA PS<2:0> |        |        |         |        |        | 145                 |

| TMR0       | Timer0 Module Register |        |                                  |        |        |         |        |        | 143*                |

| TRISA      | _                      | _      | TRISA5                           | TRISA4 | TRISA3 | TRISA2  | TRISA1 | TRISA0 | 102                 |

**Legend:** — = Unimplemented locations, read as '0'. Shaded cells are not used by the Timer0 module.

\* Page provides register information.

## 21.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

## 21.4 Timer1 Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to using Timer1. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

## 21.5 Timer1 Operation in Asynchronous Counter Mode

If the control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 21.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to asynchronous operation, it is possible to                                                              |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

|       | skip an increment. When switching from<br>asynchronous to synchronous operation,<br>it is possible to produce an additional<br>increment. |

### 21.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

## 21.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

### 21.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 21-3 for timing details.

## TABLE 21-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |  |  |

|------------|--------|-----|------------------|--|--|

| $\uparrow$ | 0      | 0   | Counts           |  |  |

| $\uparrow$ | 0      | 1   | Holds Count      |  |  |

| $\uparrow$ | 1      | 0   | Holds Count      |  |  |

| $\uparrow$ | 1      | 1   | Counts           |  |  |

#### 21.6.2 TIMER1 GATE SOURCE SELECTION

Timer1 gate source selections are shown in Table 21-4. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

### TABLE 21-4: TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                        |  |  |

|-------|---------------------------------------------------------------------------|--|--|

| 00    | Timer1 Gate Pin                                                           |  |  |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)                   |  |  |

| 10    | Comparator 1 Output sync_C1OUT<br>(optionally Timer1 synchronized output) |  |  |

| 11    | Reserved                                                                  |  |  |

## 22.0 TIMER2 MODULE

The Timer2 module incorporates the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match with PR2, respectively

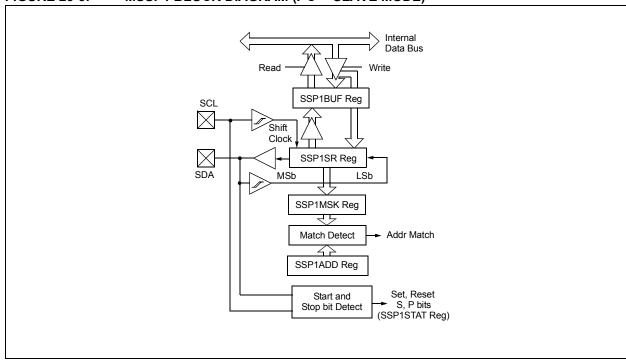

- Optional use as the shift clock for the MSSP1

modules

See Figure 22-1 for a block diagram of Timer2.

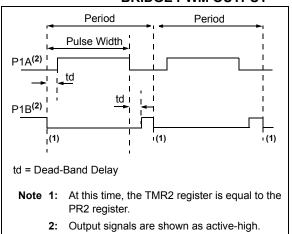

## 24.4.4 PROGRAMMABLE DEAD-BAND DELAY MODE

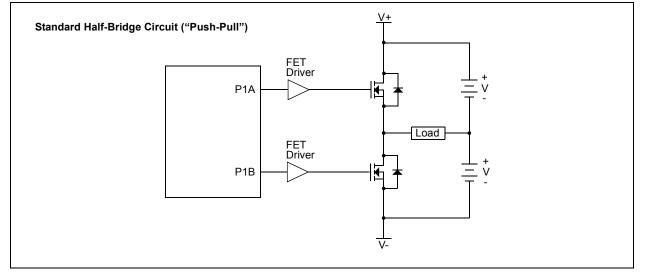

In half-bridge applications where all power switches are modulated at the PWM frequency, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on, and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shoot-through current*) will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shootthrough current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In Half-Bridge mode, a digitally programmable deadband delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 24-12 for illustration. The lower seven bits of the associated PWM1CON register (Register 24-3) sets the delay period in terms of microcontroller instruction cycles (Tcy or 4 Tosc).

#### FIGURE 24-12: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

## FIGURE 24-13: EXAMPLE OF HALF-BRIDGE APPLICATIONS

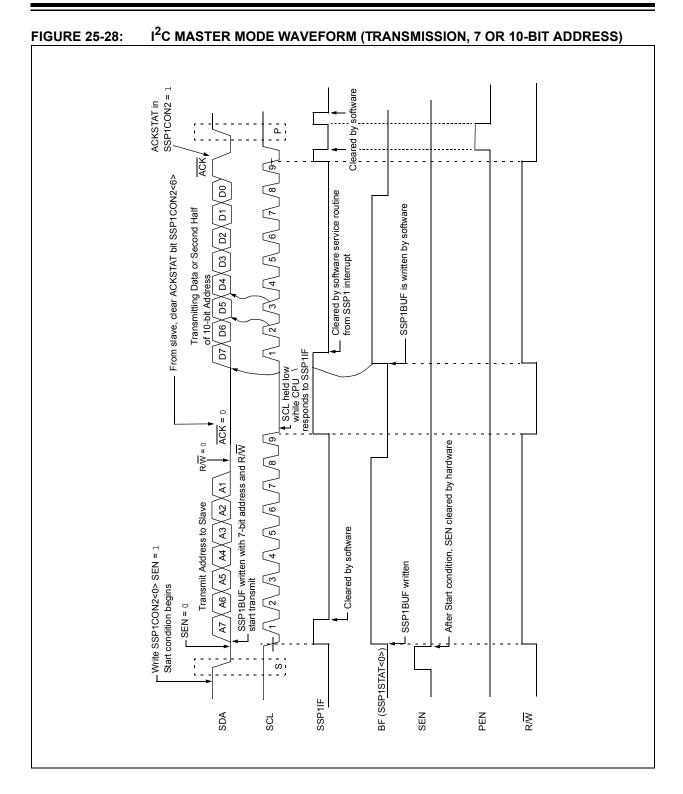

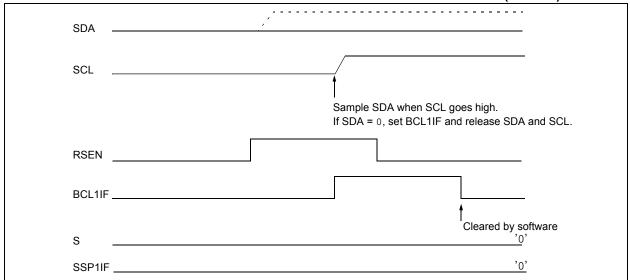

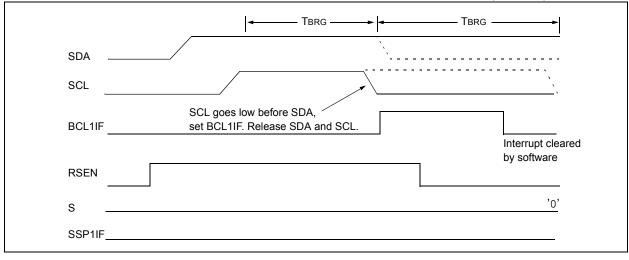

## 25.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level (Case 1).

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1' (Case 2).

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSP1ADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 25-36). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 25-37.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

### FIGURE 25-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### FIGURE 25-37: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

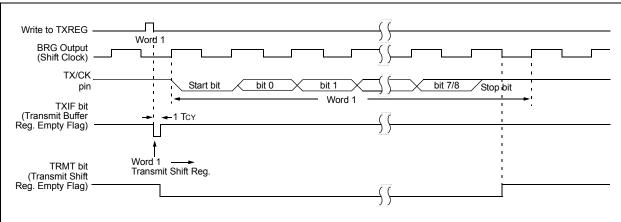

### 26.1.1.5 TSR Status

The TRMT bit of the TXSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

#### 26.1.1.6 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXSTA register is set, the EUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXSTA register is the ninth, and Most Significant, data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 26.1.2.7** "Address **Detection**" for more information on the address mode.

- 26.1.1.7 Asynchronous Transmission Set-up:

- 1. Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 26.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 4. Set SCKP bit if inverted transmit is desired.

- 5. Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 8. Load 8-bit data into the TXREG register. This will start the transmission.

#### FIGURE 26-3: ASYNCHRONOUS TRANSMISSION

#### TABLE 30-5: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET PARAMETERS

| Param<br>No. | Sym.   | Characteristic                                           | Min.         | Тур†         | Max.         | Units  | Conditions                                        |

|--------------|--------|----------------------------------------------------------|--------------|--------------|--------------|--------|---------------------------------------------------|

| 30           | TMCL   | MCLR Pulse Width (low)                                   | 2            | _            | _            | μS     |                                                   |

| 31           | TWDTLP | Low-Power Watchdog Timer<br>Time-out Period              | 10           | 16           | 27           | ms     | V <sub>DD</sub> = 3.3V-5V,<br>1:16 Prescaler used |

| 32           | Tost   | Oscillator Start-up Timer Period (Note 1)                | _            | 1024         | _            | Tosc   |                                                   |

| 33*          | TPWRT  | Power-up Timer Period, $\overline{PWRTE} = 0$            | 40           | 65           | 140          | ms     |                                                   |

| 34*          | Tioz   | I/O high-impedance from MCLR Low or Watchdog Timer Reset | _            | —            | 2.0          | μS     |                                                   |

| 35           | VBOR   | Brown-out Reset Voltage (Note 2)                         | 2.55         | 2.70         | 2.85         | V      | BORV = 0, PIC12(L)F1840                           |

|              |        |                                                          | 2.35<br>1.80 | 2.45<br>1.90 | 2.58<br>2.00 | V<br>V | BORV = 1, PIC12F1840<br>PIC12LF1840               |

| 37*          | VHYST  | Brown-out Reset Hysteresis                               | 0            | 25           | 75           | mV     | -40°C to +85°C                                    |

| 38*          | TBORDC | Brown-out Reset DC Response<br>Time                      | 1            | 3            | 35           | μS     | $VDD \leq VBOR$                                   |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance t only and are not tested.

Note 1: By design, the Oscillator Start-up Timer (OST) counts the first 1024 cycles, independent of frequency.

2: To ensure these voltage tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1  $\mu\text{F}$  and 0.01  $\mu\text{F}$  values in parallel are recommended.

| TABLE 30-14: | SPI MODE | REQUIREMENTS |

|--------------|----------|--------------|

|--------------|----------|--------------|

| Param<br>No. | Symbol                | Characteristic                                               |                           | Min.        | Тур† | Max. | Units | Conditions |

|--------------|-----------------------|--------------------------------------------------------------|---------------------------|-------------|------|------|-------|------------|

| SP70*        | TssL2scH,<br>TssL2scL | $\overline{SS}$ ↓ to SCK↓ or SCK↑ input                      | 2.25 TCY                  |             | —    | ns   |       |            |

| SP71*        | TscH                  | SCK input high time (Slave mod                               | e)                        | Tcy + 20    | _    | _    | ns    |            |

| SP72*        | TscL                  | SCK input low time (Slave mode                               | )                         | Tcy + 20    | _    | _    | ns    |            |

| SP73*        | TDIV2scH,<br>TDIV2scL | Setup time of SDI data input to S                            | 100                       |             | —    | ns   |       |            |

| SP74*        | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SO                            | DI data input to SCK edge |             |      | —    | ns    |            |

| SP75*        | TDOR                  | SDO data output rise time                                    | 3.0-5.5V                  | _           | 10   | 25   | ns    |            |

|              |                       |                                                              | 1.8-5.5V                  | —           | 25   | 50   | ns    |            |

| SP76*        | TDOF                  | SDO data output fall time                                    |                           | _           | 10   | 25   | ns    |            |

| SP77*        | TssH2doZ              | SS↑ to SDO output high-impedance                             |                           | 10          |      | 50   | ns    |            |

| SP78*        | TscR                  | SCK output rise time                                         | 3.0-5.5V                  | _           | 10   | 25   | ns    |            |

|              |                       | (Master mode)                                                | 1.8-5.5V                  | _           | 25   | 50   | ns    |            |

| SP79*        | TscF                  | SCK output fall time (Master mo                              | de)                       | _           | 10   | 25   | ns    |            |

| SP80*        | TscH2doV,             | , , , , , , , , , , , , , , , , , , , ,                      |                           | _           |      | 50   | ns    |            |

|              | TscL2doV              |                                                              |                           | —           | _    | 145  | ns    |            |

| SP81*        | TDOV2scH,<br>TDOV2scL | SDO data output setup to SCK edge                            |                           | Тсу         |      | —    | ns    |            |

| SP82*        | TssL2doV              | SDO data output valid after $\overline{\text{SS}}\downarrow$ | edge                      | —           | _    | 50   | ns    |            |

| SP83*        | TscH2ssH,<br>TscL2ssH |                                                              |                           | 1.5Tcy + 40 |      | —    | ns    |            |