Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 8-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lf1840-i-p |

# 3.3.5 CORE FUNCTION REGISTERS SUMMARY

The Core Function registers listed in Table 3-5 can be addressed from any Bank.

TABLE 3-5: CORE FUNCTION REGISTERS SUMMARY

| Addr                                                                                                                      | Name   | Bit 7                                                    | Bit 6                        | Bit 5         | Bit 4        | Bit 3       | Bit 2         | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on all other Resets |

|---------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------|------------------------------|---------------|--------------|-------------|---------------|--------|-----------|----------------------|---------------------------|

| Bank 0-31                                                                                                                 |        |                                                          |                              |               |              |             |               |        |           |                      | 1                         |

| x00h or x80h INDF0 Addressing this location uses contents of FSR0H/FSR0L to address data memory (not a physical register) |        |                                                          |                              |               |              |             |               |        | xxxx xxxx | uuuu uuuu            |                           |

| x01h or<br>x81h                                                                                                           | INDF1  |                                                          | this location ical register) |               | nts of FSR1H | /FSR1L to a | ddress data r | memory |           | xxxx xxxx            | uuuu uuuu                 |

| x02h or<br>x82h                                                                                                           | PCL    | Program Co                                               | ounter (PC)                  | Least Signifi | cant Byte    |             |               |        |           | 0000 0000            | 0000 0000                 |

| x03h or<br>x83h                                                                                                           | STATUS | _                                                        | -                            | -             | TO           | PD          | Z             | DC     | С         | 1 1000               | q quuu                    |

| x04h or<br>x84h                                                                                                           |        |                                                          |                              |               |              |             |               |        |           | 0000 0000            | uuuu uuuu                 |

| x05h or<br>x85h                                                                                                           | FSR0H  | Indirect Dat                                             | ta Memory A                  | ddress 0 Hiç  | gh Pointer   |             |               |        |           | 0000 0000            | 0000 0000                 |

| x06h or<br>x86h                                                                                                           | FSR1L  | Indirect Dat                                             | ta Memory A                  | ddress 1 Lo   | w Pointer    |             |               |        |           | 0000 0000            | uuuu uuuu                 |

| x07h or<br>x87h                                                                                                           | FSR1H  | Indirect Dat                                             | ta Memory A                  | ddress 1 Hiç  | gh Pointer   |             |               |        |           | 0000 0000            | 0000 0000                 |

| x08h or<br>x88h                                                                                                           | BSR    | _                                                        | ı                            | ı             | BSR4         | BSR3        | BSR2          | BSR1   | BSR0      | 0 0000               | 0 0000                    |

| x09h or<br>x89h                                                                                                           | WREG   | Working Register                                         |                              |               |              |             |               |        |           | 0000 0000            | uuuu uuuu                 |

| x0Ahor<br>x8Ah                                                                                                            | PCLATH | Write Buffer for the upper 7 bits of the Program Counter |                              |               |              |             |               |        | -000 0000 | -000 0000            |                           |

| x0Bhor<br>x8Bh                                                                                                            | INTCON | GIE                                                      | PEIE                         | TMR0IE        | INTE         | IOCIE       | TMR0IF        | INTF   | IOCIF     | 0000 0000            | 0000 0000                 |

$\textbf{Legend:} \qquad x = \text{unknown}, \\ u = \text{unchanged}, \\ q = \text{value depends on condition}, \\ - = \text{unimplemented}, \\ \text{read as '0'}, \\ r = \text{reserved}.$

Shaded locations are unimplemented, read as '0'.

# 5.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

## 5.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 5-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Two-Speed Start-up mode, which minimizes latency between external oscillator start-up and code execution.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, EC or RC modes) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources.

The oscillator module can be configured in one of eight clock modes.

- ECL External Clock Low-Power mode (0 MHz to 0.5 MHz)

- ECM External Clock Medium-Power mode (0.5 MHz to 4 MHz)

- ECH External Clock High-Power mode (4 MHz to 32 MHz)

- 4. LP 32 kHz Low-Power Crystal mode.

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (up to 4 MHz)

- HS High Gain Crystal or Ceramic Resonator mode (4 MHz to 20 MHz)

- 7. RC External Resistor-Capacitor (RC).

- 8. INTOSC Internal oscillator (31 kHz to 32 MHz).

Clock Source modes are selected by the FOSC<2:0> bits in the Configuration Words. The FOSC bits determine the type of oscillator that will be used when the device is first powered.

The EC clock mode relies on an external logic level signal as the device clock source. The LP, XT, and HS clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The RC clock mode requires an external resistor and capacitor to set the oscillator frequency.

The INTOSC internal oscillator block produces low, medium, and high-frequency clock sources, designated LFINTOSC, MFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 5-1). A wide selection of device clock frequencies may be derived from these three clock sources.

#### 5.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory calibrated 16 MHz internal clock source. The frequency of the HFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of multiple frequencies derived from the HFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See Section 5.2.2.7 "Internal Oscillator Clock Switch Timing" for more information.

The HFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'.

A fast start-up oscillator allows internal circuits to power up and stabilize before switching to HFINTOSC.

The High-Frequency Internal Oscillator Ready bit (HFIOFR) of the OSCSTAT register indicates when the HFINTOSC is running.

The High-Frequency Internal Oscillator Status Locked bit (HFIOFL) of the OSCSTAT register indicates when the HFINTOSC is running within 2% of its final value.

The High-Frequency Internal Oscillator Stable bit (HFIOFS) of the OSCSTAT register indicates when the HFINTOSC is running within 0.5% of its final value.

### 5.2.2.2 MFINTOSC

The Medium-Frequency Internal Oscillator (MFINTOSC) is a factory calibrated 500 kHz internal clock source. The frequency of the MFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the MFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of nine frequencies derived from the MFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See Section 5.2.2.7 "Internal Oscillator Clock Switch Timing" for more information.

The MFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

The Medium Frequency Internal Oscillator Ready bit (MFIOFR) of the OSCSTAT register indicates when the MFINTOSC is running.

# 5.2.2.3 Internal Oscillator Frequency Adjustment

The 500 kHz internal oscillator is factory calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 5-3). Since the HFINTOSC and MFINTOSC clock sources are derived from the 500 kHz internal oscillator a change in the OSCTUNE register value will apply to both.

The default value of the OSCTUNE register is '0'. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

#### 5.2.2.4 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a multiplexer (see Figure 5-1). Select 31 kHz, via software, using the IRCF<3:0> bits of the OSCCON register. See Section 5.2.2.7 "Internal Oscillator Clock Switch Timing" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<3:0> bits of the OSCCON register = 000) as the system clock source (SCS bits of the OSCCON register = 1x), or when any of the following are enabled:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired LF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

Peripherals that use the LFINTOSC are:

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor (FSCM)

The Low-Frequency Internal Oscillator Ready bit (LFIOFR) of the OSCSTAT register indicates when the LFINTOSC is running.

#### 5.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Words. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, EC, Timer1 Oscillator and RC).

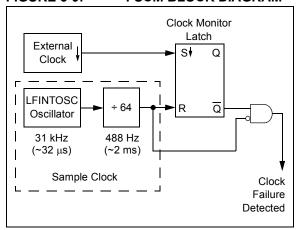

FIGURE 5-9: FSCM BLOCK DIAGRAM

#### 5.5.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 5-9. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

### 5.5.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<3:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

#### 5.5.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the SCS bits of the OSCCON register. When the SCS bits are changed, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared after successfully switching to the external clock source. The OSFIF bit should be cleared prior to switching to the external clock source. If the Fail-Safe condition still exists, the OSFIF flag will again become set by hardware.

### 5.5.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Note:

Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the Status bits in the OSCSTAT register to verify the oscillator start-up and that the system clock switchover has successfully completed.

### TABLE 6-1: SUMMARY OF REGISTERS ASSOCIATED WITH REFERENCE CLOCK SOURCES

| Name    | Bit 7  | Bit 6  | Bit 5   | Bit 4       | Bit 3 | Bit 2 | Bit 1        | Bit 0 | Register on Page |

|---------|--------|--------|---------|-------------|-------|-------|--------------|-------|------------------|

| CLKRCON | CLKREN | CLKROE | CLKRSLR | CLKRDC<1:0> |       | (     | CLKRDIV<2:0> |       | 57               |

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used by reference clock sources.

#### TABLE 6-2: SUMMARY OF CONFIGURATION WORD WITH REFERENCE CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4            | Bit 11/3 | Bit 10/2   | Bit 9/1 | Bit 8/0 | Register on Page |

|---------|------|---------|---------|----------|---------------------|----------|------------|---------|---------|------------------|

| CONFIG1 | 13:8 | 1       |         | FCMEN    | IESO                | CLKOUTEN | BOREN<1:0> |         | CPD     | 33               |

| CONFIGI | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> FOSC<2:0> |          | •          | 33      |         |                  |

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used by reference clock sources.

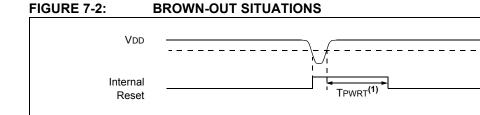

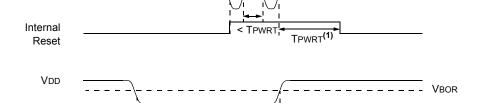

Note 1: TPWRT delay only if PWRTE bit is programmed to '0'.

## 7.3 Register Definitions: BOR Control

VDD

Internal Reset

### REGISTER 7-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | R/W-0/u | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|---------|-----|-----|-----|-----|-----|--------|

| SBOREN  | BORFS   | _   | _   | _   | _   | _   | BORRDY |

| bit 7   |         |     |     |     |     |     | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Value depends on condition

bit 7 SBOREN: Software Brown-out Reset Enable bit

If BOREN <1:0> in Configuration Words ≠ 01:

SBOREN is read/write, but has no effect on the BOR.

If BOREN <1:0> in Configuration Words = 01:

1 = BOR Enabled

0 = BOR Disabled

bit 6 **BORFS:** Brown-out Reset Fast Start bit<sup>(1)</sup>

If BOREN<1:0> = 11 (Always on) or BOREN<1:0> = 00 (Always off)

BORFS is Read/Write, but has no effect.

If BOREN <1:0> = 10 (Disabled in Sleep) or BOREN<1:0> = 01 (Under software control):

1 = Band gap is forced on always (covers sleep/wake-up/operating cases)

0 = Band gap operates normally, and may turn off

bit 5-1 **Unimplemented:** Read as '0'

bit 0 BORRDY: Brown-out Reset Circuit Ready Status bit

1 = The Brown-out Reset circuit is active

0 = The Brown-out Reset circuit is inactive

Note 1: BOREN<1:0> bits are located in Configuration Words.

## 9.3 Register Definitions: Voltage Regulator Control

# REGISTER 9-1: VREGCON: VOLTAGE REGULATOR CONTROL REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-1/1  |

|-------|-----|-----|-----|-----|-----|---------|----------|

| _     | _   | _   | _   | _   | _   | VREGPM  | Reserved |

| bit 7 |     |     |     |     |     |         | bit 0    |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-2 **Unimplemented:** Read as '0'

bit 1 **VREGPM:** Voltage Regulator Power Mode Selection bit

1 = Low-Power Sleep mode enabled in Sleep<sup>(2)</sup>

Draws lowest current in Sleep, slower wake-up

0 = Normal-Power mode enabled in Sleep<sup>(2)</sup>

Draws higher current in Sleep, faster wake-up

bit 0 Reserved: Read as '1'. Maintain this bit set.

**Note 1:** PIC12F1840 only.

2: See Section 30.0 "Electrical Specifications".

TABLE 9-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

| Name                   | Bit 7   | Bit 6 | Bit 5  | Bit 4  | Bit 3     | Bit 2  | Bit 1  | Bit 0    | Register on Page |

|------------------------|---------|-------|--------|--------|-----------|--------|--------|----------|------------------|

| INTCON                 | GIE     | PEIE  | TMR0IE | INTE   | IOCIE     | TMR0IF | INTF   | IOCIF    | 72               |

| IOCAF                  | _       | _     | IOCAF5 | IOCAF4 | IOCAF3    | IOCAF2 | IOCAF1 | IOCAF0   | 107              |

| IOCAN                  | _       | _     | IOCAN5 | IOCAN4 | IOCAN3    | IOCAN2 | IOCAN1 | IOCAN0   | 107              |

| IOCAP                  | _       | _     | IOCAP5 | IOCAP4 | IOCAP3    | IOCAP2 | IOCAP1 | IOCAP0   | 107              |

| PIE1                   | TMR1GIE | ADIE  | RCIE   | TXIE   | SSP1IE    | CCP1IE | TMR2IE | TMR1IE   | 73               |

| PIE2                   | OSFIE   | _     | C1IE   | EEIE   | BCL1IE    | _      | _      | _        | 74               |

| PIR1                   | TMR1GIF | ADIF  | RCIF   | TXIF   | SSP1IF    | CCP1IF | TMR2IF | TMR1IF   | 75               |

| PIR2                   | OSFIF   | _     | C1IF   | EEIF   | BCL1IF    | _      | _      | _        | 76               |

| STATUS                 | _       | _     | _      | TO     | PD        | Z      | DC     | С        | 15               |

| VREGCON <sup>(1)</sup> | 1       | 1     | _      | 1      | 1         | _      | VREGPM | Reserved | 80               |

| WDTCON                 | _       | _     |        | 1      | NDTPS<4:0 | >      |        | SWDTEN   | 83               |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used in Power-Down mode.

Note 1: PIC12F1840 only.

## 10.6 Register Definitions: Watchdog Control

#### REGISTER 10-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-1/1 | R/W-0/0    | R/W-1/1 | R/W-1/1 | R/W-0/0 |

|-------|-----|---------|---------|------------|---------|---------|---------|

| _     | _   |         |         | WDTPS<4:0> | >       |         | SWDTEN  |

| bit 7 |     |         |         |            |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -m/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 Unimplemented: Read as '0'

bit 5-1 WDTPS<4:0>: Watchdog Timer Period Select bits

Bit Value = Prescale Rate

11111 = Reserved. Results in minimum interval (1:32)

11111 = Reserved. Results in minimum interval (1:32)

:

10011 = Reserved. Results in minimum interval (1:32)

$10010 = 1:8388608 (2^{23}) (Interval 256s nominal)$   $10001 = 1:4194304 (2^{22}) (Interval 128s nominal)$   $10000 = 1:2097152 (2^{21}) (Interval 64s nominal)$   $01111 = 1:1048576 (2^{20}) (Interval 32s nominal)$  $01110 = 1:524288 (2^{19}) (Interval 16s nominal)$

$01101 = 1:262144 (2^{18}) (Interval 8s nominal)$  $01100 = 1:131072 (2^{17}) (Interval 4s nominal)$

01011 = 1:65536 (Interval 2s nominal) (Reset value)

01010 = 1:32768 (Interval 1s nominal) 01001 = 1:16384 (Interval 512 ms nominal) 01000 = 1:8192 (Interval 256 ms nominal)

00111 = 1:4096 (Interval 128 ms nominal) 00110 = 1:2048 (Interval 64 ms nominal)

00101 = 1:1024 (Interval 32 ms nominal) 00100 = 1:512 (Interval 16 ms nominal)

00011 = 1:256 (Interval 8 ms nominal) 00010 = 1:128 (Interval 4 ms nominal)

00001 = 1:64 (Interval 2 ms nominal) 00000 = 1:32 (Interval 1 ms nominal)

bit 0 **SWDTEN:** Software Enable/Disable for Watchdog Timer bit

If WDTE<1:0> = 00: This bit is ignored. If WDTE<1:0> = 01: 1 = WDT is turned on 0 = WDT is turned off If WDTE<1:0> = 1x:

This bit is ignored.

#### **EXAMPLE 11-2: DATA EEPROM WRITE**

```

BANKSEL EEADRL

MOVLW

DATA_EE_ADDR

;

MOVWF

EEADRL

;Data Memory Address to write

MOVLW

DATA_EE_DATA

MOVWF

EEDATL

;Data Memory Value to write

BCF

EECON1, CFGS

;Deselect Configuration space

EECON1, EEPGD ; Point to DATA memory

BCF

EECON1, WREN

;Enable writes

BSF

BCF

INTCON, GIE

;Disable INTs.

MOVLW

55h

MOVWF

EECON2

;Write 55h

MOVLW

0AAh

MOVWF

EECON2

;Write AAh

BSF

EECON1, WR

;Set WR bit to begin write

INTCON, GIE

BSF

;Enable Interrupts

EECON1, WREN

BCF

;Disable writes

BTFSC

EECON1, WR

;Wait for write to complete

GOTO

;Done

```

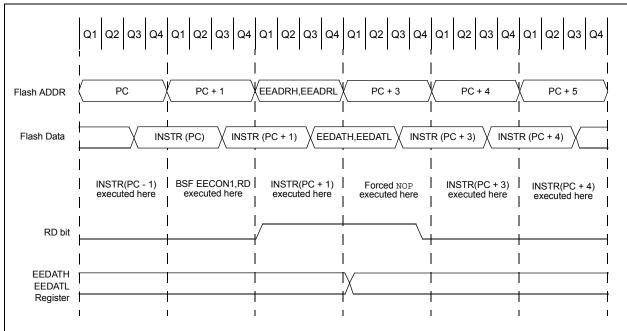

### FIGURE 11-1: FLASH PROGRAM MEMORY READ CYCLE EXECUTION

TABLE 13-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

| Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register on Page |

|--------|-------|-------|--------|--------|--------|--------|--------|--------|------------------|

| ANSELA | _     | _     | _      | ANSA4  | _      | ANSA2  | ANSA1  | ANSA0  | 103              |

| INTCON | GIE   | PEIE  | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 72               |

| IOCAF  | _     | _     | IOCAF5 | IOCAF4 | IOCAF3 | IOCAF2 | IOCAF1 | IOCAF0 | 107              |

| IOCAN  | _     | _     | IOCAN5 | IOCAN4 | IOCAN3 | IOCAN2 | IOCAN1 | IOCAN0 | 107              |

| IOCAP  | _     | _     | IOCAP5 | IOCAP4 | IOCAP3 | IOCAP2 | IOCAP1 | IOCAP0 | 107              |

| TRISA  | _     | _     | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 102              |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

# 17.0 DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- · External VREF pins

- VDD supply voltage

- · FVR Buffer2

The output of the DAC can be configured to supply a reference voltage to the following:

- · Comparator positive input

- · ADC input channel

- · DACOUT pin

- · Capacitive Sensing (CPS) module

The Digital-to-Analog Converter (DAC) can be enabled by setting the DACEN bit of the DACCON0 register.

# 17.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACR<4:0> bits of the DACCON1 register.

The DAC output voltage is determined by the following equations:

#### **EQUATION 17-1: DAC OUTPUT VOLTAGE**

## IF DACEN = 1

$$VOUT = \left( (VSOURCE + - VSOURCE -) \times \frac{DACR[4:0]}{2^5} \right) + VSOURCE - VSOUR$$

### IF DACEN = 0 & DACLPS = 1 & DACR[4:0] = 11111

VOUT = VSOURCE +

## IF DACEN = 0 & DACLPS = 0 & DACR[4:0] = 00000

Vout = Vsource -

VSOURCE+ = VDD, VREF, or FVR BUFFER 2

Vsource - Vss

## 17.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in Section 30.0 "Electrical Specifications".

# 17.3 DAC Voltage Reference Output

The DAC can be output to the DACOUT pin by setting the DACOE bit of the DACCON0 register to '1'. Selecting the DAC reference voltage for output on the DACOUT pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DACOUT pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to DACOUT. Figure 17-2 shows an example buffering technique.

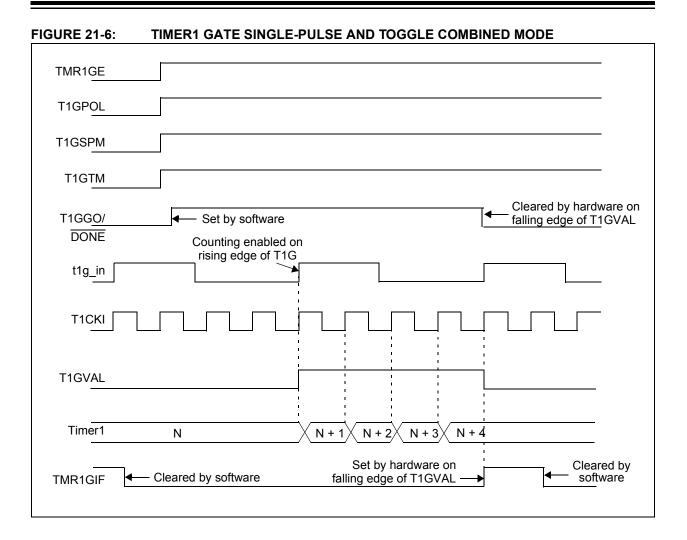

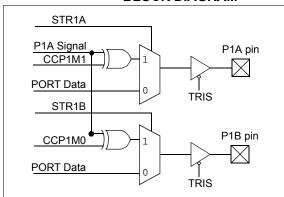

#### 24.4.5 PWM STEERING MODE

In Single Output mode, PWM steering allows any of the PWM pins to be the modulated signal. Additionally, the same PWM signal can be simultaneously available on multiple pins.

Once the Single Output mode is selected (CCP1M<3:2> = 11 and P1M<1:0> = 00 of the CCP1CON register), the user firmware can bring out the same PWM signal to one or two output pins by setting the appropriate STR1 bits of the PSTR1CON register, as shown in Table 24-8.

**Note:** The associated TRIS bits must be set to output ('0') to enable the pin output driver in order to see the PWM signal on the pin.

While the PWM Steering mode is active, the CCP1M<1:0> bits of the CCP1CON register determine the polarity of the output pins.

The PWM auto-shutdown operation also applies to PWM Steering mode as described in **Section 24.4.2** "**Enhanced PWM Auto-Shutdown Mode**". An auto-shutdown event will only affect pins that have PWM outputs enabled.

# FIGURE 24-14: SIMPLIFIED STEERING BLOCK DIAGRAM

- Note 1: Port outputs are configured as shown when the CCP1CON register bits P1M<1:0> = 00 and CCP1M<3:2> = 11.

- 2: Single PWM output requires setting at least one of the STR1 bits.

### 24.4.5.1 Steering Synchronization

The STR1SYNC bit of the PSTR1CON register gives the user two selections of when the steering event will happen. When the STR1SYNC bit is '0', the steering event will happen at the end of the instruction that writes to the PSTR1CON register. In this case, the output signal at the output pins may be an incomplete PWM waveform. This operation is useful when the user firmware needs to immediately remove a PWM signal from the pin.

When the STR1SYNC bit is '1', the effective steering update will happen at the beginning of the next PWM period. In this case, steering on/off the PWM output will always produce a complete PWM waveform.

Figures 24-15 and 24-16 illustrate the timing diagrams of the PWM steering depending on the STR1SYNC setting.

#### 24.4.6 START-UP CONSIDERATIONS

When any PWM mode is used, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins.

The CCP1M<1:0> bits of the CCP1CON register allow the user to choose whether the PWM output signals are active-high or active-low for each of the PWM output pins (P1A and P1B). The PWM output polarities must be selected before the PWM pin output drivers are enabled. Changing the polarity configuration while the PWM pin output drivers are enable is not recommended since it may result in damage to the application circuits.

The P1A and P1B output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pin output drivers at the same time as the Enhanced PWM modes may cause damage to the application circuit. The Enhanced PWM modes must be enabled in the proper Output mode and complete a full PWM cycle before enabling the PWM pin output drivers. The completion of a full PWM cycle is indicated by the TMR2IF bit of the PIR1 register being set as the second PWM period begins.

Note: When the microcontroller is released from Reset, all of the I/O pins are in the high-impedance state. The external circuits must keep the power switch devices in the Off state until the microcontroller drives the I/O pins with the proper signal levels or activates the PWM output(s).

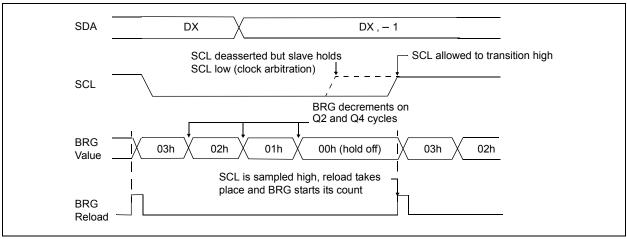

#### 25.6.2 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, releases the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSP1ADD<7:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 25-25).

FIGURE 25-25: BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

#### 25.6.3 WCOL STATUS FLAG

If the user writes the SSP1BUF when a Start, Restart, Stop, Receive or Transmit sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur). Any time the WCOL bit is set it indicates that an action on SSP1BUF was attempted while the module was not idle.

Note: Because queuing of events is not allowed, writing to the lower 5 bits of SSP1CON2 is disabled until the Start condition is complete.

# FIGURE 26-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

# FIGURE 26-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

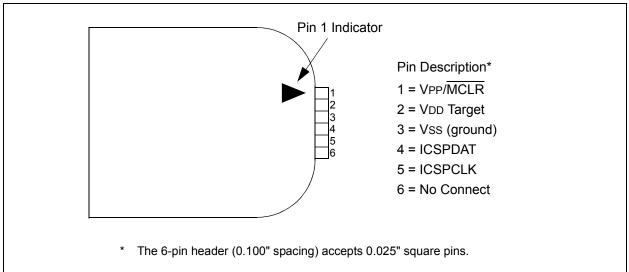

Another connector often found in use with the PICkit™ programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 28-3.

FIGURE 28-3: PICkit™ PROGRAMMER STYLE CONNECTOR INTERFACE

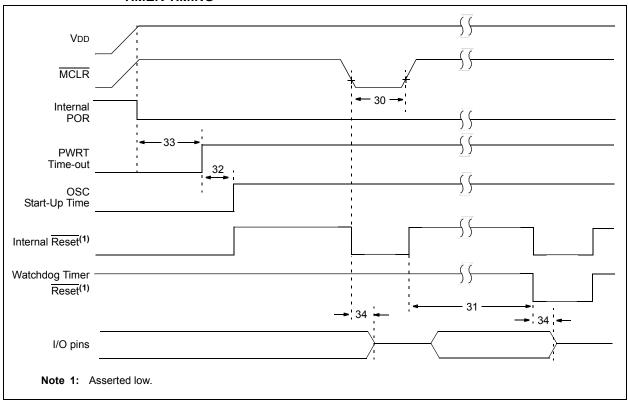

FIGURE 30-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

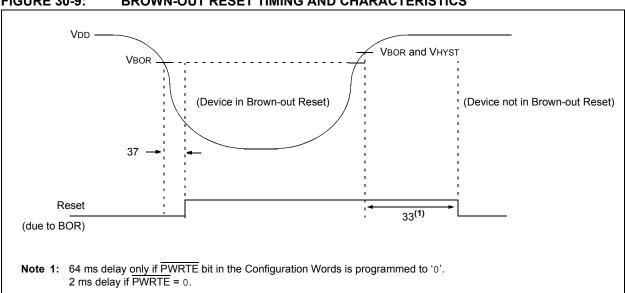

FIGURE 30-9: BROWN-OUT RESET TIMING AND CHARACTERISTICS

FIGURE 31-17: IDD TYPICAL, EXTERNAL CLOCK (ECH), HIGH-POWER MODE, PIC12F1840 ONLY

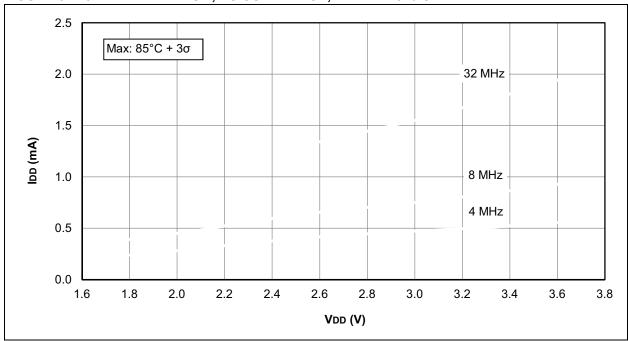

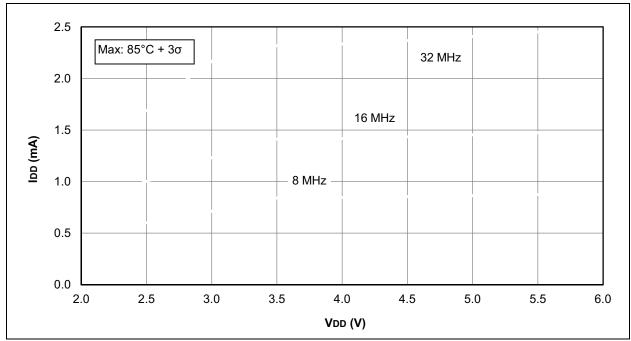

FIGURE 31-18: IDD MAXIMUM, EXTERNAL CLOCK (ECH), HIGH-POWER MODE, PIC12F1840 ONLY

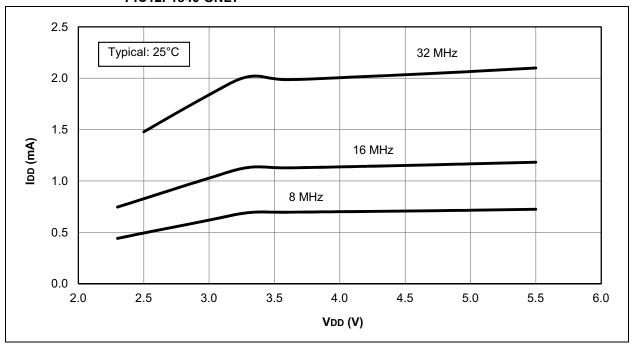

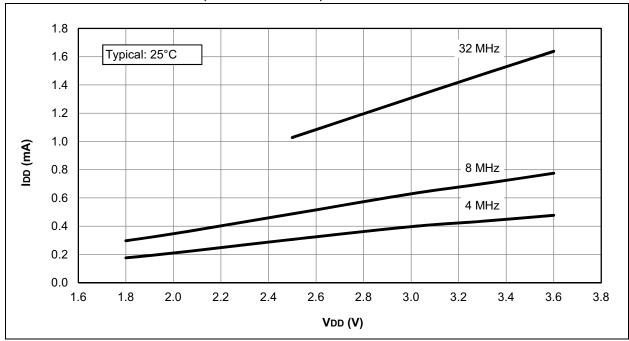

FIGURE 31-27: IDD TYPICAL, HS OSCILLATOR, PIC12LF1840 ONLY

FIGURE 31-28: IDD MAXIMUM, HS OSCILLATOR, PIC12LF1840 ONLY