Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 5                                                                           |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 8-VDFN Exposed Pad                                                          |

| Supplier Device Package    | 8-DFN (3x3)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lf1840t-i-mf |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                                                           | 6   |

|-------|---------------------------------------------------------------------------|-----|

| 2.0   | Enhanced Mid-range CPU                                                    | 10  |

| 3.0   | Memory Organization                                                       |     |

| 4.0   | Device Configuration                                                      |     |

| 5.0   | Oscillator Module (with Fail-Safe Clock Monitor)                          |     |

| 6.0   | Reference Clock Module                                                    |     |

| 7.0   | Resets                                                                    | 59  |

| 8.0   | Interrupts                                                                |     |

| 9.0   | Power-Down Mode (Sleep)                                                   |     |

| 10.0  | Watchdog Timer (WDT)                                                      |     |

| 11.0  | Data EEPROM and Flash Program Memory Control                              |     |

| 12.0  | I/O Ports                                                                 |     |

| 13.0  | Interrupt-on-Change                                                       | 105 |

| 14.0  | Fixed Voltage Reference (FVR)                                             | 109 |

| 15.0  | Temperature Indicator Module                                              | 112 |

| 16.0  | Analog-to-Digital Converter (ADC) Module                                  | 114 |

| 17.0  | Digital-to-Analog Converter (DAC) Module                                  | 127 |

| 18.0  | SR Latch                                                                  | 131 |

| 19.0  | Comparator Module                                                         | 135 |

|       | Timer0 Module                                                             |     |

| 21.0  | Timer1 Module with Gate Control                                           |     |

| 22.0  | Timer2 Module                                                             | 157 |

| 23.0  | Data Signal Modulator                                                     | 161 |

| 24.0  | Capture/Compare/PWM Modules                                               | 171 |

| 25.0  | Master Synchronous Serial Port Module                                     | 192 |

|       | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) |     |

| 27.0  | Capacitive Sensing (CPS) Module                                           |     |

| 28.0  | In-Circuit Serial Programming™ (ICSP™)                                    |     |

| 29.0  | Instruction Set Summary                                                   |     |

| 30.0  | Electrical Specifications                                                 |     |

| 31.0  | DC and AC Characteristics Graphs and Charts                               |     |

| 32.0  | Development Support                                                       |     |

| 33.0  | Packaging Information                                                     |     |

| Appe  | endix A: Data Sheet Revision History                                      | 393 |

| Appe  | endix B: Migrating From Other PIC® Devices                                | 393 |

|       | Microchip Web Site                                                        |     |

|       | omer Change Notification Service                                          |     |

|       | omer Support                                                              |     |

| Produ | uct Identification System                                                 |     |

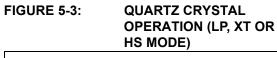

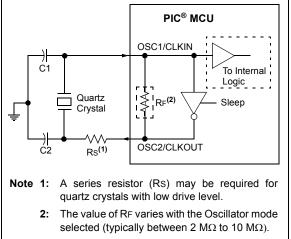

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

#### FIGURE 5-4:

#### CERAMIC RESONATOR OPERATION (XT OR HS MODE)

### 5.2.1.3 Oscillator Start-up Timer (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended, unless either FSCM or Two-Speed Start-Up are enabled. In this case, code will continue to execute at the selected INTOSC frequency while the OST is counting. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-up mode can be selected (see Section 5.4 "Two-Speed Clock Start-up Mode").

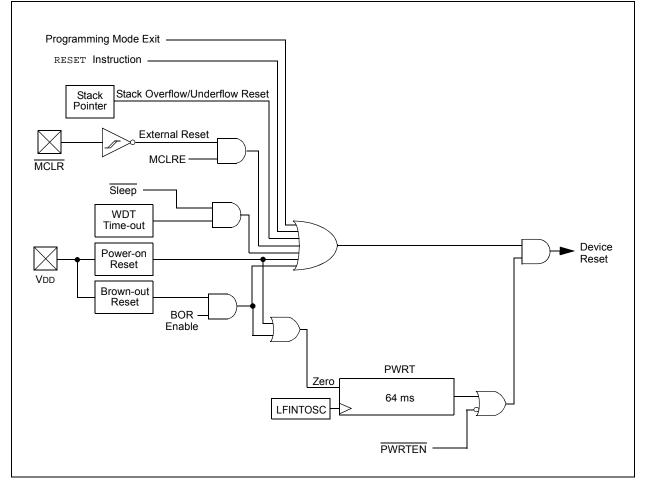

### 7.0 RESETS

There are multiple ways to reset this device:

- Power-On Reset (POR)

- Brown-Out Reset (BOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- · Stack Overflow

- Stack Underflow

- Programming mode exit

To allow VDD to stabilize, an optional power-up timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 7-1.

#### FIGURE 7-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|--------|--------|--------|-------|-------|-----------|-------|-------|--------|---------------------|

| BORCON | SBOREN | BORFS  | _     | _     | —         | _     |       | BORRDY | 61                  |

| PCON   | STKOVF | STKUNF | _     | _     | RMCLR     | RI    | POR   | BOR    | 65                  |

| STATUS |        | _      | _     | TO    | PD        | Z     | DC    | С      | 15                  |

| WDTCON | _      | _      |       | V     | VDTPS<4:0 | >     |       | SWDTEN | 83                  |

#### TABLE 7-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

Legend: — = unimplemented, read as '0'. Shaded cells are not used by Resets.

| R/W-0/0        | ) U-0                 | R/W-0/0                      | R/W-0/0         | R/W-0/0      | U-0              | U-0              | U-0         |

|----------------|-----------------------|------------------------------|-----------------|--------------|------------------|------------------|-------------|

| OSFIF          |                       | C1IF                         | EEIF            | BCL1IF       |                  | —                | —           |

| bit 7          |                       | ·                            |                 |              | ·                |                  | bit 0       |

|                |                       |                              |                 |              |                  |                  |             |

| Legend:        |                       |                              |                 |              |                  |                  |             |

| R = Reada      | ble bit               | W = Writable                 | bit             | U = Unimplei | mented bit, read | as '0'           |             |

| u = Bit is u   | nchanged              | x = Bit is unkr              | nown            | -n/n = Value | at POR and BOI   | R/Value at all o | ther Resets |

| '1' = Bit is s | set                   | '0' = Bit is clea            | ared            |              |                  |                  |             |

|                |                       |                              |                 |              |                  |                  |             |

| bit 7          |                       | llator Fail Interru          | upt Flag bit    |              |                  |                  |             |

|                | 1 = Interrupt         |                              |                 |              |                  |                  |             |

| <b>h</b> it 0  | •                     | is not pending               | o'              |              |                  |                  |             |

| bit 6          | -                     | nted: Read as '              |                 |              |                  |                  |             |

| bit 5          |                       | arator C1 Interru            | ipt Flag bit    |              |                  |                  |             |

|                | 1 = Interrupt         | is pending<br>is not pending |                 |              |                  |                  |             |

| bit 4          | •                     |                              | lation Interru  | nt Elog hit  |                  |                  |             |

| DIL 4          | 1 = Interrupt         | OM Write Comp                |                 | pt Flag bit  |                  |                  |             |

|                |                       | is not pending               |                 |              |                  |                  |             |

| bit 3          | •                     | SP Bus Collisio              | n Interrupt Fla | aa bit       |                  |                  |             |

|                | 1 = Interrupt         |                              |                 |              |                  |                  |             |

|                |                       | is not pending               |                 |              |                  |                  |             |

| bit 2-0        | Unimpleme             | nted: Read as '              | 0'              |              |                  |                  |             |

|                |                       |                              |                 |              |                  |                  |             |

| Note:          | Interrupt flag bits a | are set when an              | interrupt       |              |                  |                  |             |

|                | condition occurs,     |                              |                 |              |                  |                  |             |

|                | its corresponding     | 0                            |                 |              |                  |                  |             |

#### REGISTER 8-5: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| Note: | Interrupt flag bits are set when an interrupt   |

|-------|-------------------------------------------------|

|       | condition occurs, regardless of the state of    |

|       | its corresponding enable bit or the Global      |

|       | Enable bit, GIE, of the INTCON register.        |

|       | User software should ensure the                 |

|       | appropriate interrupt flag bits are clear prior |

|       | to enabling an interrupt.                       |

#### TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|------------|---------|--------|--------|--------|--------|--------|---------|--------|---------------------|

| INTCON     | GIE     | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF    | IOCIF  | 72                  |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA    |        | PS<2:0> |        | 145                 |

| PIE1       | TMR1GIE | ADIE   | RCIE   | TXIE   | SSP1IE | CCP1IE | TMR2IE  | TMR1IE | 73                  |

| PIE2       | OSFIE   | _      | C1IE   | EEIE   | BCL1IE | _      | _       | _      | 74                  |

| PIR1       | TMR1GIF | ADIF   | RCIF   | TXIF   | SSP1IF | CCP1IF | TMR2IF  | TMR1IF | 75                  |

| PIR2       | OSFIF   |        | C1IF   | EEIF   | BCL1IF |        |         |        | 76                  |

Legend: — = unimplemented locations read as '0'. Shaded cells are not used by Interrupts.

### 9.2 Low-Power Sleep Mode

The PIC12F1840 device contains an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode. The PIC12F1840 allows the user to optimize the operating current in Sleep, depending on the application requirements.

A Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register. With this bit set, the LDO and reference circuitry are placed in a low-power state when the device is in Sleep.

## 9.2.1 SLEEP CURRENT VS. WAKE-UP TIME

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

#### 9.2.2 PERIPHERAL USAGE IN SLEEP

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The LDO will remain in the normal power mode when those peripherals are enabled. The Low-Power Sleep mode is intended for use with these peripherals:

- Brown-Out Reset (BOR)

- Watchdog Timer (WDT)

- · External interrupt pin/Interrupt-on-change pins

- Timer1 (with external clock source)

- Comparator

- · ECCP (Capture mode)

Note: The PIC12LF1840 does not have a configurable Low-Power Sleep mode. PIC12LF1840 is an unregulated device and is always in the lowest power state when in Sleep, with no wake-up time penalty. This device has a lower maximum VDD and I/O voltage than the PIC12F1840. See Section 30.0 "Electrical Specifications" for more information.

## 20.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A software programmable prescaler is available for exclusive use with Timer0. The prescaler is enabled by clearing the PSA bit of the OPTION\_REG register.

| Note: | The Watchdog Timer (WDT) uses its own |

|-------|---------------------------------------|

|       | independent prescaler.                |

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION\_REG register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be disabled by setting the PSA bit of the OPTION\_REG register.

The prescaler is not readable or writable. All instructions writing to the TMR0 register will clear the prescaler.

#### 20.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The TMR0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The TMR0IF bit can only be cleared in software. The Timer0 interrupt enable is the TMR0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|

|       | processor from Sleep since the timer is |  |  |  |  |

|       | frozen during Sleep.                    |  |  |  |  |

#### 20.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 30.0 "Electrical Specifications"**.

### 20.1.6 OPERATION DURING SLEEP

Timer0 cannot operate while the processor is in Sleep mode. The contents of the TMR0 register will remain unchanged while the processor is in Sleep mode.

| R/W-x/u          | R/W-x/u                    | R/W-x/u                                                               | U-0                       | R/W-x/u            | R/W-x/u                       | R/W-x/u          | R/W-x/u         |  |

|------------------|----------------------------|-----------------------------------------------------------------------|---------------------------|--------------------|-------------------------------|------------------|-----------------|--|

| MDCLODIS         | MDCLPOL                    | MDCLSYNC                                                              | _                         |                    | MDCI                          | _<3:0>           |                 |  |

| bit 7            |                            |                                                                       |                           |                    |                               |                  | bit (           |  |

|                  |                            |                                                                       |                           |                    |                               |                  |                 |  |

| Legend:          |                            |                                                                       |                           |                    |                               |                  |                 |  |

| R = Readable I   |                            | W = Writable b                                                        |                           | •                  | nented bit, read              |                  |                 |  |

| u = Bit is uncha | anged                      | x = Bit is unkno                                                      | own                       | -n/n = Value a     | at POR and BO                 | R/Value at all c | other Resets    |  |

| '1' = Bit is set |                            | '0' = Bit is clea                                                     | red                       |                    |                               |                  |                 |  |

| bit 7            | MDCLODIS:                  | Modulator Low                                                         | Carrier Out               | out Disable bit    |                               |                  |                 |  |

|                  | 1 = Output s<br>is disable | ignal driving the<br>ed                                               | peripheral o              | output pin (selec  | ted by MDCL<3                 | 3:0> of the MD0  | CARL register   |  |

|                  | 0 = Output s<br>is enable  | ignal driving the                                                     | peripheral o              | output pin (selec  | ted by MDCL<3                 | 3:0> of the MD0  | CARL register   |  |

| bit 6            | MDCLPOL:                   | Modulator Low C                                                       | arrier Polar              | ity Select bit     |                               |                  |                 |  |

|                  |                            | l low carrier sign<br>l low carrier sign                              |                           |                    |                               |                  |                 |  |

| bit 5            | MDCLSYNC                   | Modulator Low                                                         | Carrier Syr               | hchronization En   | able bit                      |                  |                 |  |

|                  | 1 = Modulato<br>time carr  | or waits for a falli<br>ier                                           | ng edge on                | the low time carr  | ier signal befor              | e allowing a sw  | itch to the hig |  |

|                  | 0 = Modulate               | or Output is not a                                                    | synchronize               | d to the low time  | e carrier signal <sup>(</sup> | 1)               |                 |  |

| bit 4            | Unimplemented: Read as '0' |                                                                       |                           |                    |                               |                  |                 |  |

| bit 3-0          | MDCL<3:0>                  | Modulator Data                                                        | High Carrie               | r Selection bits ( | 1)                            |                  |                 |  |

|                  | 1111 = Res                 | erved. No chan                                                        | nel connect               | ed.                |                               |                  |                 |  |

|                  | •                          |                                                                       |                           |                    |                               |                  |                 |  |

|                  | •                          |                                                                       |                           |                    |                               |                  |                 |  |

|                  | 0100 = CCF<br>0011 = Refe  | erved. No chan<br>21 output (PWM<br>erence Clock mo<br>erved. No chan | Output mod<br>dule signal | de only)           |                               |                  |                 |  |

#### REGISTER 23-4: MDCARL: MODULATION LOW CARRIER CONTROL REGISTER

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

| TABLE 23-1: SUMMARY OF REGISTERS ASSOCIATED WITH DATA SIGNAL MODULATOR MO |

|---------------------------------------------------------------------------|

|---------------------------------------------------------------------------|

| Name   | Bit 7    | Bit 6   | Bit 5    | Bit 4  | Bit 3 | Bit 2 | Bit 1  | Bit 0 | Register<br>on Page |

|--------|----------|---------|----------|--------|-------|-------|--------|-------|---------------------|

| MDCARH | MDCHODIS | MDCHPOL | MDCHSYNC | —      |       | MDCF  | <3:0>  |       | 169                 |

| MDCARL | MDCLODIS | MDCLPOL | MDCLSYNC | _      |       | MDCL  | <3:0>  |       | 170                 |

| MDCON  | MDEN     | MDOE    | MDSLR    | MDOPOL | MDOUT | _     | —      | MDBIT | 167                 |

| MDSRC  | MDMSODIS | —       | —        |        |       | MDMS  | 6<3:0> |       | 168                 |

Legend: — = unimplemented, read as '0'. Shaded cells are not used in the Data Signal Modulator mode.

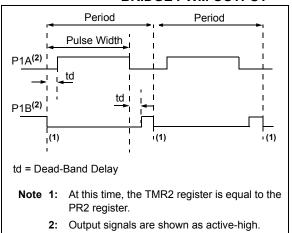

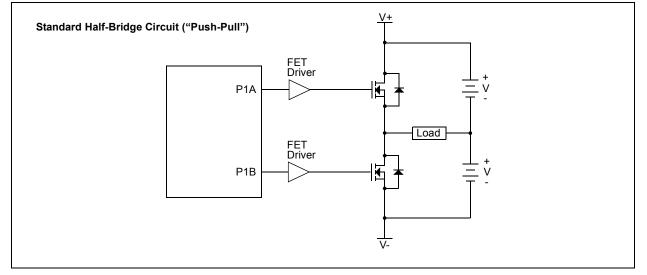

## 24.4.4 PROGRAMMABLE DEAD-BAND DELAY MODE

In half-bridge applications where all power switches are modulated at the PWM frequency, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on, and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shoot-through current*) will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shootthrough current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In Half-Bridge mode, a digitally programmable deadband delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 24-12 for illustration. The lower seven bits of the associated PWM1CON register (Register 24-3) sets the delay period in terms of microcontroller instruction cycles (Tcy or 4 Tosc).

#### FIGURE 24-12: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

#### FIGURE 24-13: EXAMPLE OF HALF-BRIDGE APPLICATIONS

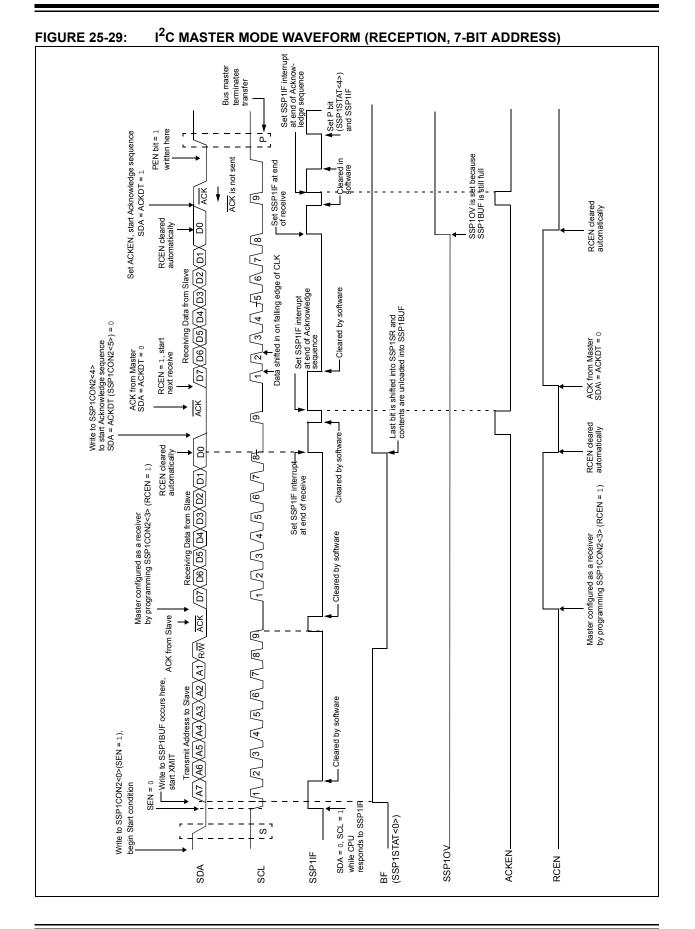

When one device is transmitting a logical one, or letting the line float, and a second device is transmitting a logical zero, or holding the line low, the first device can detect that the line is not a logical one. This detection, when used on the SCL line, is called clock stretching. Clock stretching gives slave devices a mechanism to control the flow of data. When this detection is used on the SDA line, it is called arbitration. Arbitration ensures that there is only one master device communicating at any single time.

#### 25.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of clock stretching. An addressed slave device may hold the SCL clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCL line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCL connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

#### 25.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDA data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDA line.

For example, if one transmitter holds the SDA line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDA line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDA line. If this transmitter is also a master device, it also must stop driving the SCL line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDA line continues with its original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

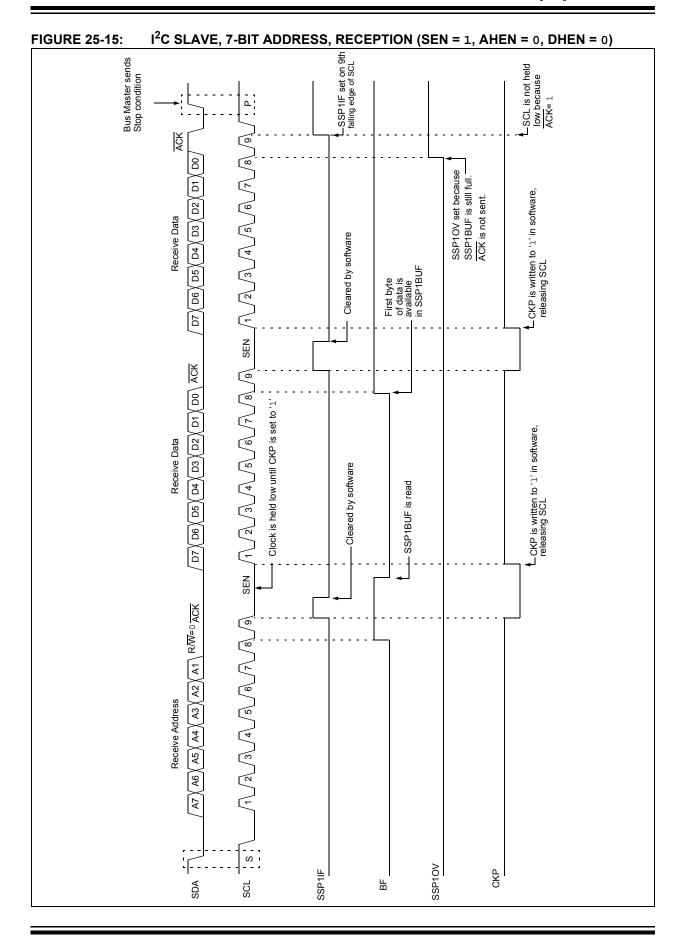

#### 25.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSP1STAT register is cleared. The received address is loaded into the SSP1BUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSP1STAT register is set, or bit SSP1OV of the SSP1CON1 register is set. The BOEN bit of the SSP1CON3 register modifies this operation. For more information see Register 25-4.

An MSSP1 interrupt is generated for each transferred data byte. Flag bit, SSP1IF, must be cleared by software.

When the SEN bit of the SSP1CON2 register is set, SCL will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSP1CON1 register, except sometimes in 10-bit mode. See **Section 25.2.3 "SPI Master Mode"** for more detail.

#### 25.5.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSP1 module configured as an  $I^2C$  Slave in 7-bit Addressing mode. All decisions made by hardware or software and their effect on reception. Figure 25-14 and Figure 25-15 is used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish  $I^2C$  communication.

- 1. Start bit detected.

- 2. S bit of SSP1STAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- 3. Matching address with  $R/\overline{W}$  bit clear is received.

- 4. The slave pulls SDA low sending an ACK to the master, and sets SSP1IF bit.

- 5. Software clears the SSP1IF bit.

- 6. Software reads received address from SSP1BUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCL line.

- 8. The master clocks out a data byte.

- 9. Slave drives SDA low sending an ACK to the master, and sets SSP1IF bit.

- 10. Software clears SSP1IF.

- 11. Software reads the received byte from SSP1BUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the master.

- 13. Master sends Stop condition, setting P bit of SSP1STAT, and the bus goes idle.

#### 25.5.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the 8th falling edge of SCL. These additional interrupts allow the slave software to decide whether it wants to ACK the receive address or data byte, rather than the hardware. This functionality adds support for PMBus<sup>™</sup> that was not present on previous versions of this module.

This list describes the steps that need to be taken by slave software to use these options for  $I^2C$  communication. Figure 25-16 displays a module using both address and data holding. Figure 25-17 includes the operation with the SEN bit of the SSP1CON2 register set.

- 1. S bit of SSP1STAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSP1IF is set and CKP cleared after the 8th falling edge of SCL.

- 3. Slave clears the SSP1IF.

- Slave can look at the ACKTIM bit of the SSP1CON3 register to <u>determine</u> if the SSP1IF was after or before the ACK.

- 5. Slave reads the address value from SSP1BUF, clearing the BF flag.

- 6. Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSP1IF is set after an ACK, not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSP1IF.

**Note:** SSP1IF is still set after the 9th falling edge of SCL even if there is no clock stretching and BF has been cleared. Only if NACK is sent to Master is SSP1IF not set

- 11. SSP1IF set and CKP cleared after 8th falling edge of SCL for a received data byte.

- 12. Slave looks at ACKTIM bit of SSP1CON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSP1BUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop Detect is disabled, the slave will only know by polling the P bit of the SSTSTAT register.

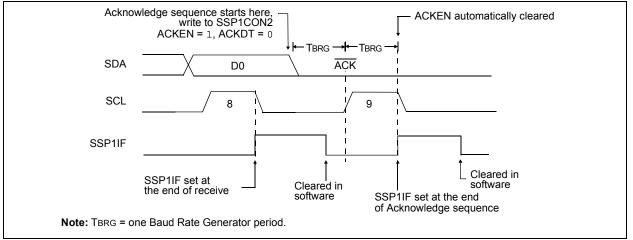

#### 25.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSP1CON2 register. When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP1 module then goes into Idle mode (Figure 25-30).

#### 25.6.8.1 WCOL Status Flag

If the user writes the SSP1BUF when an Acknowledge sequence is in progress, then WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

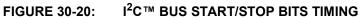

#### 25.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSP1CON2 register. At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit of the SSP1STAT register is set. A TBRG later, the PEN bit is cleared and the SSP1IF bit is set (Figure 25-31).

### 25.6.9.1 WCOL Status Flag

If the user writes the SSP1BUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

### FIGURE 25-30: ACKNOWLEDGE SEQUENCE WAVEFORM

### FIGURE 29-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register op<br>13 8 7 6                                                     |                    |

|------------------------------------------------------------------------------------------------|--------------------|

| OPCODE d                                                                                       | f (FILE #)         |

| d = 0 for destination W<br>d = 1 for destination f<br>f = 7-bit file register addr             | ess                |

| Bit-oriented file register ope<br>13 10 9                                                      | rations<br>7 6 0   |

| OPCODE b (BIT                                                                                  | #) f (FILE #)      |

| b = 3-bit bit address<br>f = 7-bit file register addr                                          | ess                |

| Literal and control operation                                                                  | ıs                 |

| General                                                                                        | -                  |

| 13 8<br>OPCODE                                                                                 | 7 0<br>k (literal) |

| L                                                                                              | . ,                |

| k = 8-bit immediate value                                                                      | 9                  |

| CALL and GOTO instructions or                                                                  | nly                |

| 13 11 10                                                                                       | 0                  |

| OPCODE                                                                                         | k (literal)        |

| k = 11-bit immediate valu MOVLP instruction only 13 7                                          |                    |

| OPCODE                                                                                         | k (literal)        |

| k = 7-bit immediate value                                                                      | 54 0               |

| OPCODE                                                                                         | k (literal)        |

| k = 5-bit immediate value<br>BRA instruction only                                              | 9                  |

| 13 9 8                                                                                         | 0                  |

| OPCODE                                                                                         | k (literal)        |

| k = 9-bit immediate value<br>FSR Offset instructions                                           | e                  |

|                                                                                                | 6 5 0              |

| OPCODE r                                                                                       | n k (literal)      |

|                                                                                                |                    |

| n = appropriate FSR<br>k = 6-bit immediate value                                               | е                  |

| k = 6-bit immediate value<br>FSR Increment instructions<br>13                                  | 3 2 1 0            |

| k = 6-bit immediate value<br>FSR Increment instructions                                        |                    |

| k = 6-bit immediate value<br>FSR Increment instructions<br>13                                  | 3 2 1 0            |

| k = 6-bit immediate value<br>FSR Increment instructions<br>13<br>OPCODE<br>n = appropriate FSR | 3 2 1 0            |

| PIC12LF1840<br>PIC12F1840    |                         | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array} $ |                      |               |                                                                                                                                |       |            |                                               |  |

|------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------|-------|------------|-----------------------------------------------|--|

|                              |                         |                                                                                                                                                                                                                                                                | rd Opera<br>ng tempe |               | ditions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |       |            |                                               |  |

| Param Device Characteristics |                         | Min.                                                                                                                                                                                                                                                           | Тур†                 | Max.<br>+85°C | Max.<br>+125°C                                                                                                                 | Units | Conditions |                                               |  |

|                              | Power-down Base Current | (IPD) <sup>(2)</sup>                                                                                                                                                                                                                                           |                      |               | -                                                                                                                              |       | VDD        | Note                                          |  |

| D026A*                       |                         |                                                                                                                                                                                                                                                                | 250                  | _             | _                                                                                                                              | μA    | 1.8        | ADC Current (Note 1, 3)                       |  |

|                              |                         |                                                                                                                                                                                                                                                                | 250                  | _             | _                                                                                                                              | μΑ    | 3.0        | Conversion in progress                        |  |

| D026A*                       |                         | _                                                                                                                                                                                                                                                              | 280                  | _             | _                                                                                                                              | μA    | 2.3        | ADC Current                                   |  |

| DUZUA                        |                         | _                                                                                                                                                                                                                                                              | 280                  | _             | _                                                                                                                              | μA    | 3.0        | Conversion in progress                        |  |

|                              |                         | _                                                                                                                                                                                                                                                              | 280                  | _             | _                                                                                                                              | μA    | 5.0        | VREGPM = 1 (Note 1, 3)                        |  |

| D027                         |                         | _                                                                                                                                                                                                                                                              | 3                    | 12            | 15                                                                                                                             | μA    | 1.8        | Cap Sense, Low Power                          |  |

|                              |                         | —                                                                                                                                                                                                                                                              | 4                    | 15            | 18                                                                                                                             | μA    | 3.0        | CPSRM = 0, CPSRNG = 01<br>(Note 1)            |  |

| D027                         |                         | _                                                                                                                                                                                                                                                              | 6.3                  | 13            | 16                                                                                                                             | μA    | 2.3        | Cap Sense, Low Power                          |  |

|                              |                         |                                                                                                                                                                                                                                                                | 8.5                  | 18            | 20                                                                                                                             | μA    | 3.0        | CPSRM = 0, CPSRNG = 01                        |  |

|                              |                         |                                                                                                                                                                                                                                                                | 12.8                 | 23            | 25                                                                                                                             | μA    | 5.0        | VREGPM = 1 (Note 1)                           |  |

| D027A                        |                         | —                                                                                                                                                                                                                                                              | 6.0                  | 15            | 20                                                                                                                             | μA    | 1.8        | Cap Sense, Medium Power                       |  |

|                              |                         | —                                                                                                                                                                                                                                                              | 8.0                  | 18            | 25                                                                                                                             | μΑ    | 3.0        | CPSRM = 0, CPSRNG = 10<br>(Note 1)            |  |

| D027A                        |                         |                                                                                                                                                                                                                                                                | 9.5                  | 20            | 25                                                                                                                             | μA    | 2.3        | Cap Sense, Medium Power                       |  |

|                              |                         |                                                                                                                                                                                                                                                                | 13                   | 28            | 30                                                                                                                             | μA    | 3.0        | CPSRM = 0, CPSRNG = 10<br>VREGPM = 1 (Note 1) |  |

|                              |                         |                                                                                                                                                                                                                                                                | 17                   | 32            | 35                                                                                                                             | μA    | 5.0        |                                               |  |

| D027B                        |                         |                                                                                                                                                                                                                                                                | 15                   | 35            | 40                                                                                                                             | μA    | 1.8        | Cap Sense, High Power                         |  |

|                              |                         | —                                                                                                                                                                                                                                                              | 39                   | 60            | 75                                                                                                                             | μA    | 3.0        | CPSRM = 0, CPSRNG = 11<br>(Note 1)            |  |

| D027B                        |                         | _                                                                                                                                                                                                                                                              | 20                   | 40            | 45                                                                                                                             | μA    | 2.3        | Cap Sense, High Power                         |  |

|                              |                         |                                                                                                                                                                                                                                                                | 42                   | 68            | 80                                                                                                                             | μA    | 3.0        | CPSRM = 0, CPSRNG = 11<br>VREGPM = 1 (Note 1) |  |

|                              |                         | —                                                                                                                                                                                                                                                              | 49                   | 72            | 86                                                                                                                             | μA    | 5.0        |                                               |  |

| D028                         |                         |                                                                                                                                                                                                                                                                | 4.8                  | 15            | 20                                                                                                                             | μA    | 1.8        | Comparator,                                   |  |

|                              |                         | _                                                                                                                                                                                                                                                              | 4.9                  | 17            | 23                                                                                                                             | μA    | 3.0        | Low Power, CxSP = 0 (Note 1)                  |  |

| D028                         |                         | _                                                                                                                                                                                                                                                              | 4.9                  | 16            | 21                                                                                                                             | μA    | 2.3        | Comparator,                                   |  |

|                              |                         |                                                                                                                                                                                                                                                                | 5.0                  | 17            | 23                                                                                                                             | μA    | 3.0        | Low Power, CxSP = 0<br>VREGPM = 1 (Note 1)    |  |

|                              |                         | —                                                                                                                                                                                                                                                              | 5.2                  | 18            | 24                                                                                                                             | μA    | 5.0        |                                               |  |

| D028A                        |                         |                                                                                                                                                                                                                                                                | 27                   | 50            | 60                                                                                                                             | μA    | 1.8        | Comparator,                                   |  |

|                              |                         | —                                                                                                                                                                                                                                                              | 28                   | 55            | 70                                                                                                                             | μA    | 3.0        | Normal Power, CxSP = 1<br>(Note 1)            |  |

| D028A                        |                         |                                                                                                                                                                                                                                                                | 27                   | 52            | 62                                                                                                                             | μA    | 2.3        | Comparator,                                   |  |

|                              |                         | _                                                                                                                                                                                                                                                              | 28                   | 55            | 65                                                                                                                             | μA    | 3.0        | Normal Power, CxSP = 1<br>VREGPM = 1 (Note 1) |  |

|                              |                         | _                                                                                                                                                                                                                                                              | 29                   | 57            | 75                                                                                                                             | μA    | 5.0        |                                               |  |

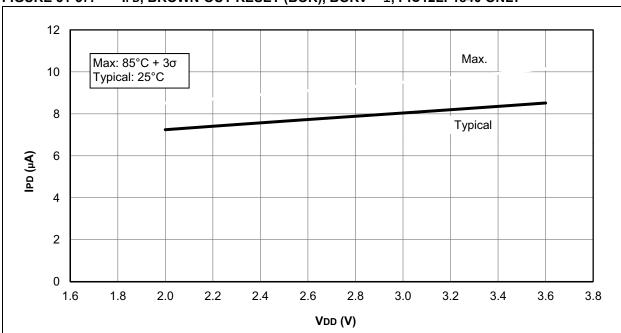

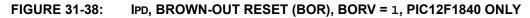

#### 30.3 DC Characteristics: Power-Down Base Current (IPD) (Continued)

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max. values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

3: ADC clock source is FRC.

TABLE 30-15: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS REQUIREMENTS

| Param.<br>No. | Symbol  | Characteristic  |              | Min. | Тур. | Max. | Units | Conditions                                    |  |

|---------------|---------|-----------------|--------------|------|------|------|-------|-----------------------------------------------|--|

| SP90*         | TSU:STA | Start condition | 100 kHz mode | 4700 |      |      | ns    | Only relevant for<br>repeated Start condition |  |

|               |         | Setup time      | 400 kHz mode | 600  | -    | _    |       |                                               |  |

| SP91*         | THD:STA | Start condition | 100 kHz mode | 4000 | -    | —    | ns    | After this period, the first                  |  |

|               |         | Hold time       | 400 kHz mode | 600  | -    | —    |       | clock pulse is generated                      |  |

| SP92*         | TSU:STO | Stop condition  | 100 kHz mode | 4700 | _    | —    | ns    |                                               |  |

|               |         | Setup time      | 400 kHz mode | 600  | —    | _    |       |                                               |  |

| SP93*         | THD:STO | Stop condition  | 100 kHz mode | 4000 | _    |      | ns    |                                               |  |

|               |         | Hold time       | 400 kHz mode | 600  | _    | —    |       |                                               |  |

\* These parameters are characterized but not tested.

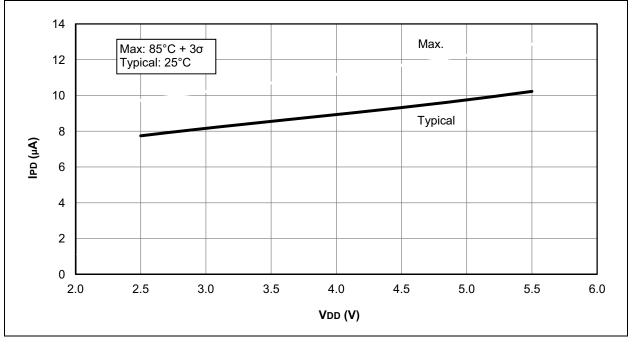

### 8-Lead Plastic Small Outline (SN) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**RECOMMENDED LAND PATTERN**

|                         | MILLIMETERS |          |      |      |

|-------------------------|-------------|----------|------|------|

| Dimension               | MIN         | NOM      | MAX  |      |

| Contact Pitch           | Е           | 1.27 BSC |      |      |

| Contact Pad Spacing     | С           |          | 5.40 |      |

| Contact Pad Width (X8)  | X1          |          |      | 0.60 |

| Contact Pad Length (X8) | Y1          |          |      | 1.55 |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A

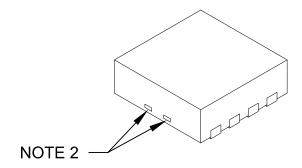

### 8-Lead Plastic Dual Flat, No Lead Package (MF) - 3x3x0.9mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |          |          |      |  |

|------------------------|-------------|----------|----------|------|--|

| Dimensior              | MIN         | NOM      | MAX      |      |  |

| Number of Pins         | N           | 8        |          |      |  |

| Pitch                  | е           |          | 0.65 BSC |      |  |

| Overall Height         | A           | 0.80     | 0.90     | 1.00 |  |

| Standoff               | A1          | 0.00     | 0.02     | 0.05 |  |

| Contact Thickness      | A3          | 0.20 REF |          |      |  |

| Overall Length         | D           | 3.00 BSC |          |      |  |

| Exposed Pad Width      | E2          | 1.34     | -        | 1.60 |  |

| Overall Width          | E           | 3.00 BSC |          |      |  |

| Exposed Pad Length     | D2          | 1.60     | -        | 2.40 |  |

| Contact Width          | b           | 0.25     | 0.30     | 0.35 |  |

| Contact Length         | L           | 0.20     | 0.30     | 0.55 |  |

| Contact-to-Exposed Pad | ĸ           | 0.20     | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package may have one or more exposed tie bars at ends.

3. Package is saw singulated

4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-062C Sheet 2 of 2