Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | F <sup>2</sup> MC-16FX                                                        |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 56MHz                                                                         |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SCI, UART/USART                    |

| Peripherals                | DMA, LVD, LVR, POR, PWM, WDT                                                  |

| Number of I/O              | 80                                                                            |

| Program Memory Size        | 576KB (576K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 24K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                     |

| Data Converters            | A/D 24x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-LQFP                                                                      |

| Supplier Device Package    | 100-LQFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb96f348twbpmc-ge2 |

# 1. Product Lineup

| Features                                         |            | MB96V300B                              | MB96(F)34x                                                                          |  |  |  |

|--------------------------------------------------|------------|----------------------------------------|-------------------------------------------------------------------------------------|--|--|--|

| Product type                                     |            | Evaluation sample                      | Flash product: MB96F34x Mask ROM product: MB9634x                                   |  |  |  |

| Product options                                  |            |                                        |                                                                                     |  |  |  |

| YS                                               |            |                                        | Low voltage reset persistently on / Single clock                                    |  |  |  |

| RS                                               |            |                                        | Low voltage reset can be disabled / Single clock                                    |  |  |  |

| YW                                               |            |                                        | Low voltage reset persistently on / Dual clock                                      |  |  |  |

| RW                                               |            |                                        | Low voltage reset can be disabled / Dual clock                                      |  |  |  |

| TS                                               |            |                                        | indep. 32KB Flash / Low voltage reset persistently on / Single clock                |  |  |  |

| HS                                               |            |                                        | indep. 32KB Flash / Low voltage reset can be disabled / Single clock                |  |  |  |

| TW                                               |            |                                        | indep. 32KB Flash / Low voltage reset persistently on / Dual clock                  |  |  |  |

| HW                                               |            | NA.                                    | indep. 32KB Flash / Low voltage reset can be disabled / Dual clock                  |  |  |  |

| FS                                               |            | NA NA                                  | 64KB Data Flash / Low voltage reset persistently on / Single clock                  |  |  |  |

| DS                                               |            |                                        | 64KB Data Flash / Low voltage reset can be disabled / Single clock                  |  |  |  |

| FW                                               |            |                                        | 64KB Data Flash / Low voltage reset persistently on / Dual clock                    |  |  |  |

| DW                                               |            |                                        | 64KB Data Flash / Low voltage reset can be disabled / Dual clock                    |  |  |  |

| AS                                               |            |                                        | No CAN / Low voltage reset can be disabled / Single clock devices                   |  |  |  |

| CS                                               |            |                                        | No CAN / indep. 32KB Flash / Low voltage reset can be disabled / Single clock       |  |  |  |

| AW                                               |            |                                        | No CAN / Low voltage reset can be disabled / Dual clock                             |  |  |  |

| CW                                               |            |                                        | No CAN / indep. 32KB Flash / Low voltage reset can be disabled / Dual clock         |  |  |  |

| Flash/ROM                                        | RAM        |                                        |                                                                                     |  |  |  |

| 160KB                                            | 8KB        |                                        | MB96345Y <sup>[1]</sup> , MB96345R <sup>[1]</sup>                                   |  |  |  |

| 224KB<br>[Flash A: 160KB, Data<br>Flash A: 64KB] | 8KB        |                                        | MB96F345F <sup>[1]</sup> , MB96F345D <sup>[1]</sup>                                 |  |  |  |

| 288KB                                            | 16KB       | ROM/Flash memory emulation by external | MB96F346Y, MB96346Y <sup>[1]</sup> , MB96F346R, MB96346R <sup>[1]</sup> , MB96F346A |  |  |  |

| 416KB                                            | 16KB       | RAM, 92KB internal<br>RAM              | MB96F347Y, MB96F347R, MB96F347A                                                     |  |  |  |

| 544KB                                            | 544KB 24KB |                                        | MB96F348Y, MB96F348R, MB96F348A                                                     |  |  |  |

| 576KB<br>[Flash A: 544KB, Flash<br>B: 32KB] 24KB |            |                                        | MB96F348T, MB96F348H, MB96F348C                                                     |  |  |  |

| Package                                          |            | BGA416                                 | FPT-100P-M20 FPT-100P-M22                                                           |  |  |  |

| DMA                                              |            | 16 channels                            | 6 channels                                                                          |  |  |  |

| USART                                            |            | 10 channels                            | 7 channels                                                                          |  |  |  |

Document Number: 002-04579 Rev. \*A

# 5. Pin Circuit Type

Table 2: Pin circuit types

| FPT-10   | 00P-M20                        | FPT-10    | 00P-M22                        |

|----------|--------------------------------|-----------|--------------------------------|

| Pin no.  | Circuit<br>type <sup>[1]</sup> | Pin no.   | Circuit<br>type <sup>[1]</sup> |

| 1-10     | Н                              | 1-12      | Н                              |

| 11,12    | B <sup>[2]</sup>               | 13, 14    | B <sup>[2]</sup>               |

| 11,12    | H <sup>[3]</sup>               | 13, 14    | H <sup>[3]</sup>               |

| 13,14    | Supply                         | 15,16     | Supply                         |

| 15       | F                              | 17        | F                              |

| 16,17    | Н                              | 18,19     | Н                              |

| 18-21    | N                              | 20-23     | N                              |

| 22-29    | I                              | 24-31     | I                              |

| 30       | Supply                         | 32        | Supply                         |

| 31-32    | G                              | 33-34     | G                              |

| 33       | Supply                         | 35        | Supply                         |

| 34 to 41 | I                              | 36 to 43  | I                              |

| 42       | Supply                         | 44        | Supply                         |

| 43 to 48 | I                              | 45 to 50  | I                              |

| 49 to 51 | С                              | 51 to 53  | С                              |

| 52       | E                              | 54        | Е                              |

| 53 to 54 | I                              | 55 to 56  | I                              |

| 55 to 62 | Н                              | 57 to 64  | Н                              |

| 63, 64   | Supply                         | 65, 66    | Supply                         |

| 65 to 87 | Н                              | 67 to 89  | Н                              |

| 88,89    | Supply                         | 90, 91    | Supply                         |

| 90, 91   | А                              | 92, 93    | A                              |

| 92-100   | Н                              | 94 to 100 | Н                              |

<sup>[1]:</sup> Please refer to " I/O Circuit Type" for details on the I/O circuit types [2]: Devices with suffix "W"

<sup>[3]:</sup> Devices without suffix "W"

# 6. I/O Circuit Type

| Туре | Circuit                                | Remarks                                                                                                                                                                                                                                                                                                                                                       |

|------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A    | X1 R  MRFBE  R  X0  FCI or osc disable | High-speed oscillation circuit:  Programmable between oscillation mode (external crystal or resonator connected to X0/X1 pins) and Fast external Clock Input (FCI) mode (external clock connected to X0 pin)  Programmable feedback resistor = approx. 2 * 0.5 MΩ. Feedback resistor is grounded in the center when the oscillator is disabled or in FCI mode |

| В    | X1A Xout  SRFBE  Osc disable           | Low-speed oscillation circuit:  ■ Programmable feedback resistor = approx. 2 * 5 MΩ. Feedback resistor is grounded in the center when the oscillator is disabled                                                                                                                                                                                              |

| С    | R<br>Hysteresis<br>inputs              | ■ Mask ROM and EVA device:CMOS Hysteresis input pin ■ Flash device:CMOS input pin                                                                                                                                                                                                                                                                             |

| E    | Pull-up Resistor  Hysteresis inputs    | ■ CMOS Hysteresis input pin ■ Pull-up resistor value: approx. 50 kΩ                                                                                                                                                                                                                                                                                           |

|                                                                      |                                                                      | MB96F346Y<br>MB96F346R<br>MB96F346A | MB96F347Y<br>MB96F347R<br>MB96F347A |           |

|----------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------|-------------------------------------|-----------|

| Alternative mode CPU address                                         | Flash memory mode address                                            | Flash size<br>288kByte              | Flash size<br>416kByte              |           |

| FF:FFFF <sub>H</sub><br>FF:0000 <sub>H</sub>                         | 3F:FFFF <sub>H</sub><br>3F:0000 <sub>H</sub>                         | S39 - 64K                           | S39 - 64K                           |           |

| FE:FFFF <sub>H</sub><br>FE:0000 <sub>H</sub>                         | 3E:FFFF <sub>H</sub><br>3E:0000 <sub>H</sub>                         | S38 - 64K                           | S38 - 64K                           |           |

| FD:FFFF <sub>H</sub><br>FD:0000 <sub>H</sub>                         | 3D:FFFF <sub>H</sub><br>3D:0000 <sub>H</sub>                         | S37 - 64K                           | S37 - 64K                           | Flash A   |

| FC:FFFF <sub>H</sub><br>FC:0000 <sub>H</sub>                         | 3C:FFFF <sub>H</sub><br>3C:0000 <sub>H</sub>                         | S36 - 64K                           | S36 - 64K                           | 1 10311 7 |

| FB:FFFF <sub>H</sub><br>FB:0000 <sub>H</sub>                         | 3B:FFFF <sub>H</sub><br>3B:0000 <sub>H</sub>                         |                                     | S35 - 64K                           |           |

| FA:FFFF <sub>H</sub><br>FA:0000 <sub>H</sub>                         | 3A:FFFF <sub>H</sub><br>3A:0000 <sub>H</sub>                         |                                     | S34 - 64K                           |           |

| F9:FFFF <sub>H</sub><br>F9:0000 <sub>H</sub><br>F8:FFFF <sub>H</sub> | 39:FFF <sub>H</sub><br>39:0000 <sub>H</sub><br>38:FFF <sub>H</sub>   |                                     |                                     |           |

| F8:0000 <sub>H</sub><br>F7:FFFF <sub>H</sub><br>F7:0000 <sub>H</sub> | 38:0000 <sub>H</sub><br>37:FFFF <sub>H</sub><br>37:0000 <sub>H</sub> | -                                   |                                     |           |

| F6:FFFF <sub>H</sub><br>F6:0000 <sub>H</sub>                         | 36:FFFF <sub>H</sub><br>36:0000 <sub>H</sub>                         |                                     |                                     |           |

| F5:FFFF <sub>H</sub><br>F5:0000 <sub>H</sub>                         | 35:FFFF <sub>H</sub><br>35:0000 <sub>H</sub>                         | External bus                        |                                     |           |

| F4:FFFF <sub>H</sub><br>F4:0000 <sub>H</sub>                         | 34:FFFF <sub>H</sub><br>34:0000 <sub>H</sub>                         | j j                                 | External bus                        |           |

| F3:FFFF <sub>H</sub><br>F3:0000 <sub>H</sub>                         | 33:FFFF <sub>H</sub><br>33:0000 <sub>H</sub>                         |                                     |                                     |           |

| F2:FFFF <sub>H</sub><br>F2:0000 <sub>H</sub>                         | 32:FFFF <sub>H</sub><br>32:0000 <sub>H</sub>                         |                                     |                                     |           |

| F1:FFFF <sub>H</sub><br>F1:0000 <sub>H</sub>                         | 31:FFFF <sub>H</sub><br>31:0000 <sub>H</sub>                         | ]                                   |                                     |           |

| F0:FFFF <sub>H</sub><br>F0:0000 <sub>H</sub>                         | 30:FFFF <sub>H</sub><br>30:0000 <sub>H</sub>                         |                                     |                                     |           |

| E0:FFFF <sub>H</sub><br>E0:0000 <sub>H</sub><br>DF:FFFF <sub>H</sub> |                                                                      | _                                   | _                                   |           |

| DF:FFFF <sub>H</sub> DF:8000 <sub>H</sub> DF:7FFF <sub>H</sub>       | 1F:7FFF <sub>H</sub>                                                 | Reserved                            | Reserved                            |           |

| DF:7FFF <sub>H</sub> DF:6000 <sub>H</sub> DF:5FFF <sub>H</sub>       | 1F:7FFF <sub>H</sub><br>1F:6000 <sub>H</sub><br>1F:5FFF <sub>H</sub> | SA3 - 8K                            | SA3 - 8K                            |           |

| DF:4000 <sub>H</sub> DF:3FFF <sub>H</sub>                            | 1F:4000 <sub>H</sub><br>1F:3FFF <sub>H</sub>                         | SA2 - 8K                            | SA2 - 8K                            | Flash A   |

| DF:3FFF <sub>H</sub> DF:2000 <sub>H</sub> DF:1FFF <sub>H</sub>       | 1F:2000 <sub>H</sub>                                                 | SA1 - 8K                            | SA1 - 8K                            |           |

| DF:0000 <sub>H</sub>                                                 | 1F:1FFF <sub>H</sub><br>1F:0000 <sub>H</sub>                         | SA0 - 8K <sup>[1]</sup>             | SA0 - 8K <sup>[1]</sup>             |           |

| DE:FFFF <sub>H</sub><br>DE:0000 <sub>H</sub>                         |                                                                      | Reserved                            | Reserved                            |           |

Table 4: I/O map MB96(F)34x

| Address             | Register                                    | Abbreviation 8-bit access | Abbreviation<br>16-bit access | Access |

|---------------------|---------------------------------------------|---------------------------|-------------------------------|--------|

| 000081 <sub>H</sub> | PPG1 - Timer register                       |                           |                               | R      |

| 000082 <sub>H</sub> | PPG1 - Period setting register              |                           | PCSR1                         | W      |

| 000083 <sub>H</sub> | PPG1 - Period setting register              |                           |                               | W      |

| 000084 <sub>H</sub> | PPG1 - Duty cycle register                  |                           | PDUT1                         | W      |

| 000085 <sub>H</sub> | PPG1 - Duty cycle register                  |                           |                               | W      |

| 000086 <sub>H</sub> | PPG1 - Control status register Low          | PCNL1                     | PCN1                          | R/W    |

| 000087 <sub>H</sub> | PPG1 - Control status register High         | PCNH1                     |                               | R/W    |

| 000088 <sub>H</sub> | PPG2 - Timer register                       |                           | PTMR2                         | R      |

| 000089 <sub>H</sub> | PPG2 - Timer register                       |                           |                               | R      |

| 00008A <sub>H</sub> | PPG2 - Period setting register              |                           | PCSR2                         | W      |

| 00008B <sub>H</sub> | PPG2 - Period setting register              |                           |                               | W      |

| 00008C <sub>H</sub> | PPG2 - Duty cycle register                  |                           | PDUT2                         | W      |

| 00008D <sub>H</sub> | PPG2 - Duty cycle register                  |                           |                               | W      |

| 00008E <sub>H</sub> | PPG2 - Control status register Low          | PCNL2                     | PCN2                          | R/W    |

| 00008F <sub>H</sub> | PPG2 - Control status register High         | PCNH2                     |                               | R/W    |

| 000090 <sub>H</sub> | PPG3 - Timer register                       |                           | PTMR3                         | R      |

| 000091 <sub>H</sub> | PPG3 - Timer register                       |                           |                               | R      |

| 000092 <sub>H</sub> | PPG3 - Period setting register              |                           | PCSR3                         | W      |

| 000093 <sub>H</sub> | PPG3 - Period setting register              |                           |                               | W      |

| 000094 <sub>H</sub> | PPG3 - Duty cycle register                  |                           | PDUT3                         | W      |

| 000095 <sub>H</sub> | PPG3 - Duty cycle register                  |                           |                               | W      |

| 000096 <sub>H</sub> | PPG3 - Control status register Low          | PCNL3                     | PCN3                          | R/W    |

| 000097 <sub>H</sub> | PPG3 - Control status register High         | PCNH3                     |                               | R/W    |

| 000098 <sub>H</sub> | PPG7-PPG4 - General Control register 1 Low  | GCN1L1                    | GCN11                         | R/W    |

| 000099 <sub>H</sub> | PPG7-PPG4 - General Control register 1 High | GCN1H1                    |                               | R/W    |

| 00009A <sub>H</sub> | PPG7-PPG4 - General Control register 2 Low  | GCN2L1                    | GCN21                         | R/W    |

| 00009B <sub>H</sub> | PPG7-PPG4 - General Control register 2 High | GCN2H1                    |                               | R/W    |

| 00009C <sub>H</sub> | PPG4 - Timer register                       |                           | PTMR4                         | R      |

| 00009D <sub>H</sub> | PPG4 - Timer register                       |                           |                               | R      |

| 00009E <sub>H</sub> | PPG4 - Period setting register              |                           | PCSR4                         | W      |

| 00009F <sub>H</sub> | PPG4 - Period setting register              |                           |                               | W      |

| 0000A0 <sub>H</sub> | PPG4 - Duty cycle register                  |                           | PDUT4                         | W      |

Table 4: I/O map MB96(F)34x

| Address             | Register                                       | Abbreviation 8-bit access | Abbreviation 16-bit access | Access |

|---------------------|------------------------------------------------|---------------------------|----------------------------|--------|

| 0003B9 <sub>H</sub> | Memory Patch function - Patch address 0 middle | PFAM0                     |                            | R/W    |

| 0003BA <sub>H</sub> | Memory Patch function - Patch address 0 high   | PFAH0                     |                            | R/W    |

| 0003BB <sub>H</sub> | Memory Patch function - Patch address 1 low    | PFAL1                     |                            | R/W    |

| 0003BC <sub>H</sub> | Memory Patch function - Patch address 1 middle | PFAM1                     |                            | R/W    |

| 0003BD <sub>H</sub> | Memory Patch function - Patch address 1 high   | PFAH1                     |                            | R/W    |

| 0003BE <sub>H</sub> | Memory Patch function - Patch address 2 low    | PFAL2                     |                            | R/W    |

| 0003BF <sub>H</sub> | Memory Patch function - Patch address 2 middle | PFAM2                     |                            | R/W    |

| 0003C0 <sub>H</sub> | Memory Patch function - Patch address 2 high   | PFAH2                     |                            | R/W    |

| 0003C1 <sub>H</sub> | Memory Patch function - Patch address 3 low    | PFAL3                     |                            | R/W    |

| 0003C2 <sub>H</sub> | Memory Patch function - Patch address 3 middle | PFAM3                     |                            | R/W    |

| 0003C3 <sub>H</sub> | Memory Patch function - Patch address 3 high   | PFAH3                     |                            | R/W    |

| 0003C4 <sub>H</sub> | Memory Patch function - Patch address 4 low    | PFAL4                     |                            | R/W    |

| 0003C5 <sub>H</sub> | Memory Patch function - Patch address 4 middle | PFAM4                     |                            | R/W    |

| 0003C6 <sub>H</sub> | Memory Patch function - Patch address 4 high   | PFAH4                     |                            | R/W    |

| 0003C7 <sub>H</sub> | Memory Patch function - Patch address 5 low    | PFAL5                     |                            | R/W    |

| 0003C8 <sub>H</sub> | Memory Patch function - Patch address 5 middle | PFAM5                     |                            | R/W    |

| 0003C9 <sub>H</sub> | Memory Patch function - Patch address 5 high   | PFAH5                     |                            | R/W    |

| 0003CA <sub>H</sub> | Memory Patch function - Patch address 6 low    | PFAL6                     |                            | R/W    |

| 0003CB <sub>H</sub> | Memory Patch function - Patch address 6 middle | PFAM6                     |                            | R/W    |

| 0003CC <sub>H</sub> | Memory Patch function - Patch address 6 high   | PFAH6                     |                            | R/W    |

| 0003CD <sub>H</sub> | Memory Patch function - Patch address 7 low    | PFAL7                     |                            | R/W    |

| 0003CE <sub>H</sub> | Memory Patch function - Patch address 7 middle | PFAM7                     |                            | R/W    |

| 0003CF <sub>H</sub> | Memory Patch function - Patch address 7 high   | PFAH7                     |                            | R/W    |

| 0003D0 <sub>H</sub> | Memory Patch function - Patch data 0 Low       | PFDL0                     | PFD0                       | R/W    |

| 0003D1 <sub>H</sub> | Memory Patch function - Patch data 0 High      | PFDH0                     |                            | R/W    |

| 0003D2 <sub>H</sub> | Memory Patch function - Patch data 1 Low       | PFDL1                     | PFD1                       | R/W    |

| 0003D3 <sub>H</sub> | Memory Patch function - Patch data 1 High      | PFDH1                     |                            | R/W    |

| 0003D4 <sub>H</sub> | Memory Patch function - Patch data 2 Low       | PFDL2                     | PFD2                       | R/W    |

| 0003D5 <sub>H</sub> | Memory Patch function - Patch data 2 High      | PFDH2                     |                            | R/W    |

| 0003D6 <sub>H</sub> | Memory Patch function - Patch data 3 Low       | PFD3                      | R/W                        |        |

| 0003D7 <sub>H</sub> | Memory Patch function - Patch data 3 High      | PFDH3                     |                            | R/W    |

| 0003D8 <sub>H</sub> | Memory Patch function - Patch data 4 Low       | PFDL4                     | PFD4                       | R/W    |

Table 4: I/O map MB96(F)34x

|                                          |                                                   | 8-bit access | 16-bit access | Access |

|------------------------------------------|---------------------------------------------------|--------------|---------------|--------|

| 00043B <sub>H</sub> -000443 <sub>H</sub> | Reserved                                          |              |               | -      |

| 000444 <sub>H</sub>                      | I/O Port P00 - Port Input Enable Register         | PIER00       |               | R/W    |

| 000445 <sub>H</sub>                      | I/O Port P01 - Port Input Enable Register         | PIER01       |               | R/W    |

| 000446 <sub>H</sub>                      | I/O Port P02 - Port Input Enable Register         | PIER02       |               | R/W    |

| 000447 <sub>H</sub>                      | I/O Port P03 - Port Input Enable Register         | PIER03       |               | R/W    |

| 000448 <sub>H</sub>                      | I/O Port P04 - Port Input Enable Register         | PIER04       |               | R/W    |

| 000449 <sub>H</sub>                      | I/O Port P05 - Port Input Enable Register         | PIER05       |               | R/W    |

| 00044A <sub>H</sub>                      | I/O Port P06 - Port Input Enable Register         | PIER06       |               | R/W    |

| 00044B <sub>H</sub>                      | I/O Port P07 - Port Input Enable Register         | PIER07       |               | R/W    |

| 00044C <sub>H</sub>                      | I/O Port P08 - Port Input Enable Register         | PIER08       |               | R/W    |

| 00044D <sub>H</sub>                      | I/O Port P09 - Port Input Enable Register         | PIER09       |               | R/W    |

| 00044E <sub>H</sub>                      | I/O Port P10 - Port Input Enable Register         | PIER10       |               | R/W    |

| 00044F <sub>H</sub> -000457 <sub>H</sub> | Reserved                                          |              |               | -      |

| 000458 <sub>H</sub>                      | I/O Port P00 - Port Input Level Register          | PILR00       |               | R/W    |

| 000459 <sub>H</sub>                      | I/O Port P01 - Port Input Level Register          | PILR01       |               | R/W    |

| 00045A <sub>H</sub>                      | I/O Port P02 - Port Input Level Register          | PILR02       |               | R/W    |

| 00045B <sub>H</sub>                      | I/O Port P03 - Port Input Level Register          | PILR03       |               | R/W    |

| 00045C <sub>H</sub>                      | I/O Port P04 - Port Input Level Register          | PILR04       |               | R/W    |

| 00045D <sub>H</sub>                      | I/O Port P05 - Port Input Level Register          | PILR05       |               | R/W    |

| 00045E <sub>H</sub>                      | I/O Port P06 - Port Input Level Register          | PILR06       |               | R/W    |

| 00045F <sub>H</sub>                      | I/O Port P07 - Port Input Level Register          | PILR07       |               | R/W    |

| 000460 <sub>H</sub>                      | I/O Port P08 - Port Input Level Register          | PILR08       |               | R/W    |

| 000461 <sub>H</sub>                      | I/O Port P09 - Port Input Level Register          | PILR09       |               | R/W    |

| 000462 <sub>H</sub>                      | I/O Port P10 - Port Input Level Register          | PILR10       |               | R/W    |

| 000463 <sub>H</sub> -00046B <sub>H</sub> | Reserved                                          |              |               | -      |

| 00046C <sub>H</sub>                      | I/O Port P00 - Extended Port Input Level Register | EPILR00      |               | R/W    |

| 00046D <sub>H</sub>                      | I/O Port P01 - Extended Port Input Level Register | EPILR01      |               | R/W    |

| 00046E <sub>H</sub>                      | I/O Port P02 - Extended Port Input Level Register | EPILR02      |               | R/W    |

| 00046F <sub>H</sub>                      | I/O Port P03 - Extended Port Input Level Register | EPILR03      |               | R/W    |

| 000470 <sub>H</sub>                      | I/O Port P04 - Extended Port Input Level Register | EPILR04      |               | R/W    |

| 000471 <sub>H</sub>                      | I/O Port P05 - Extended Port Input Level Register | EPILR05      |               | R/W    |

| 000472 <sub>H</sub>                      | I/O Port P06 - Extended Port Input Level Register | EPILR06      |               | R/W    |

Table 4: I/O map MB96(F)34x

| Address                                  | Register                                          | Abbreviation<br>8-bit access | Abbreviation 16-bit access | Access |

|------------------------------------------|---------------------------------------------------|------------------------------|----------------------------|--------|

| 0005AD <sub>H</sub>                      | PPG14 - Timer register                            |                              |                            | R      |

| 0005AE <sub>H</sub>                      | PPG14 - Period setting register                   |                              | PCSR14                     | W      |

| 0005AF <sub>H</sub>                      | PPG14 - Period setting register                   |                              |                            | W      |

| 0005B0 <sub>H</sub>                      | PPG14 - Duty cycle register                       |                              | PDUT14                     | W      |

| 0005B1 <sub>H</sub>                      | PPG14 - Duty cycle register                       |                              |                            | W      |

| 0005B2 <sub>H</sub>                      | PPG14 - Control status register Low               | PCNL14                       | PCN14                      | R/W    |

| 0005B3 <sub>H</sub>                      | PPG14 - Control status register High              | PCNH14                       |                            | R/W    |

| 0005B4 <sub>H</sub>                      | PPG15 - Timer register                            |                              | PTMR15                     | R      |

| 0005B5 <sub>H</sub>                      | PPG15 - Timer register                            |                              |                            | R      |

| 0005B6 <sub>H</sub>                      | PPG15 - Period setting register                   |                              | PCSR15                     | W      |

| 0005B7 <sub>H</sub>                      | PPG15 - Period setting register                   |                              |                            | W      |

| 0005B8 <sub>H</sub>                      | PPG15 - Duty cycle register                       |                              | PDUT15                     | W      |

| 0005B9 <sub>H</sub>                      | PPG15 - Duty cycle register                       |                              |                            | W      |

| 0005BA <sub>H</sub>                      | PPG15 - Control status register Low               | PCNL15                       | PCN15                      | R/W    |

| 0005BB <sub>H</sub>                      | PPG15 - Control status register High              | PCNH15                       |                            | R/W    |

| 0005BC <sub>H</sub> -00065F <sub>H</sub> | Reserved                                          |                              |                            | -      |

| 000660 <sub>H</sub>                      | Peripheral Resource Relocation Register 10        | PRRR10                       |                            | R/W    |

| 000661 <sub>H</sub>                      | Peripheral Resource Relocation Register 11        | PRRR11                       |                            | R/W    |

| 000662 <sub>H</sub>                      | Peripheral Resource Relocation Register 12        | PRRR12                       |                            | R/W    |

| 000663 <sub>H</sub>                      | Peripheral Resource Relocation Register 13        | PRRR13                       |                            | W      |

| 000664 <sub>H</sub> -0006DF <sub>H</sub> | Reserved                                          |                              |                            | -      |

| 0006E0 <sub>H</sub>                      | External Bus - Area configuration register 0 Low  | EACL0                        | EAC0                       | R/W    |

| 0006E1 <sub>H</sub>                      | External Bus - Area configuration register 0 High | EACH0                        |                            | R/W    |

| 0006E2 <sub>H</sub>                      | External Bus - Area configuration register 1 Low  | EACL1                        | EAC1                       | R/W    |

| 0006E3 <sub>H</sub>                      | External Bus - Area configuration register 1 High | EACH1                        |                            | R/W    |

| 0006E4 <sub>H</sub>                      | External Bus - Area configuration register 2 Low  | EACL2                        | EAC2                       | R/W    |

| 0006E5 <sub>H</sub>                      | External Bus - Area configuration register 2 High | EACH2                        |                            | R/W    |

| 0006E6 <sub>H</sub>                      | External Bus - Area configuration register 3 Low  | EACL3                        | EAC3                       | R/W    |

| 0006E7 <sub>H</sub>                      | External Bus - Area configuration register 3 High | EACH3                        |                            | R/W    |

| 0006E8 <sub>H</sub>                      | External Bus - Area configuration register 4 Low  | EACL4                        | EAC4                       | R/W    |

| 0006E9 <sub>H</sub>                      | External Bus - Area configuration register 4 High | EACH4                        |                            | R/W    |

| 0006EA <sub>H</sub>                      | External Bus - Area configuration register 5 Low  | EACL5                        | EAC5                       | R/W    |

Table 4: I/O map MB96(F)34x

| Address                                  | Register                                         | Abbreviation 8-bit access | Abbreviation 16-bit access | Access |  |

|------------------------------------------|--------------------------------------------------|---------------------------|----------------------------|--------|--|

| 000715 <sub>H</sub>                      | CAN0 - IF1 Mask 1 Register High                  | IF1MSK1H0                 |                            | R/W    |  |

| 000716 <sub>H</sub>                      | CAN0 - IF1 Mask 2 Register Low                   | IF1MSK2L0                 | IF1MSK20                   | R/W    |  |

| 000717 <sub>H</sub>                      | CAN0 - IF1 Mask 2 Register High                  | IF1MSK2H0                 |                            | R/W    |  |

| 000718 <sub>H</sub>                      | CAN0 - IF1 Arbitration 1 Register Low            | IF1ARB1L0                 | IF1ARB10                   | R/W    |  |

| 000719 <sub>H</sub>                      | CAN0 - IF1 Arbitration 1 Register High           | IF1ARB1H0                 |                            | R/W    |  |

| 00071A <sub>H</sub>                      | CAN0 - IF1 Arbitration 2 Register Low            | IF1ARB2L0                 | IF1ARB20                   | R/W    |  |

| 00071B <sub>H</sub>                      | CAN0 - IF1 Arbitration 2 Register High           | IF1ARB2H0                 |                            | R/W    |  |

| 00071C <sub>H</sub>                      | CAN0 - IF1 Message Control Register Low          | IF1MCTRL0                 | IF1MCTR0                   | R/W    |  |

| 00071D <sub>H</sub>                      | CAN0 - IF1 Message Control Register High         | IF1MCTRH0                 |                            | R/W    |  |

| 00071E <sub>H</sub>                      | CAN0 - IF1 Data A1 Low                           | IF1DTA1L0                 | IF1DTA10                   | R/W    |  |

| 00071F <sub>H</sub>                      | CAN0 - IF1 Data A1 High                          | IF1DTA1H0                 |                            | R/W    |  |

| 000720 <sub>H</sub>                      | CAN0 - IF1 Data A2 Low                           | IF1DTA2L0                 | IF1DTA20                   | R/W    |  |

| 000721 <sub>H</sub>                      | CAN0 - IF1 Data A2 High                          | IF1DTA2H0                 |                            | R/W    |  |

| 000722 <sub>H</sub>                      | CAN0 - IF1 Data B1 Low                           | IF1DTB1L0                 | IF1DTB10                   | R/W    |  |

| 000723 <sub>H</sub>                      | CAN0 - IF1 Data B1 High                          | IF1DTB1H0                 |                            | R/W    |  |

| 000724 <sub>H</sub>                      | CAN0 - IF1 Data B2 Low                           | IF1DTB2L0                 | IF1DTB20                   | R/W    |  |

| 000725 <sub>H</sub>                      | CAN0 - IF1 Data B2 High                          | IF1DTB2H0                 |                            | R/W    |  |

| 000726 <sub>H</sub> -00073F <sub>H</sub> | Reserved                                         |                           |                            | -      |  |

| 000740 <sub>H</sub>                      | CAN0 - IF2 Command request register Low          | IF2CREQL0                 | IF2CREQ0                   | R/W    |  |

| 000741 <sub>H</sub>                      | CAN0 - IF2 Command request register High         | IF2CREQH0                 |                            | R/W    |  |

| 000742 <sub>H</sub>                      | CAN0 - IF2 Command Mask register Low             | IF2CMSKL0                 | IF2CMSK0                   | R/W    |  |

| 000743 <sub>H</sub>                      | CAN0 - IF2 Command Mask register High (reserved) | IF2CMSKH0                 |                            | R      |  |

| 000744 <sub>H</sub>                      | CAN0 - IF2 Mask 1 Register Low                   | IF2MSK1L0                 | IF2MSK10                   | R/W    |  |

| 000745 <sub>H</sub>                      | CAN0 - IF2 Mask 1 Register High                  | IF2MSK1H0                 |                            | R/W    |  |

| 000746 <sub>H</sub>                      | CAN0 - IF2 Mask 2 Register Low                   | IF2MSK2L0                 | IF2MSK20                   | R/W    |  |

| 000747 <sub>H</sub>                      | CAN0 - IF2 Mask 2 Register High                  | IF2MSK2H0                 |                            | R/W    |  |

| 000748 <sub>H</sub>                      | CAN0 - IF2 Arbitration 1 Register Low            | IF2ARB1L0                 | IF2ARB10                   | R/W    |  |

| 000749 <sub>H</sub>                      | CAN0 - IF2 Arbitration 1 Register High           | IF2ARB1H0                 |                            | R/W    |  |

| 00074A <sub>H</sub>                      | CAN0 - IF2 Arbitration 2 Register Low            | IF2ARB2L0                 | IF2ARB20                   | R/W    |  |

| 00074B <sub>H</sub>                      | CAN0 - IF2 Arbitration 2 Register High           | IF2ARB2H0                 |                            | R/W    |  |

| 00074C <sub>H</sub>                      | CAN0 - IF2 Message Control Register Low          | IF2MCTRL0                 | IF2MCTR0                   | R/W    |  |

| 00074D <sub>H</sub>                      | CAN0 - IF2 Message Control Register High         | IF2MCTRH0                 |                            | R/W    |  |

|                                          |                                                  |                           |                            |        |  |

Document Number: 002-04579 Rev. \*A

### 13. Handling Devices

Special care is required for the following when handling the device:

- Latch-up prevention

- Unused pins handling

- External clock usage

- Unused sub clock signal

- Notes on PLL clock mode operation

- Power supply pins (V<sub>CC</sub>/V<sub>SS</sub>)

- Crystal oscillator circuit

- Turn on sequence of power supply to A/D converter and analog inputs

- Pin handling when not using the A/D converter

- Notes on energization

- Stabilization of power supply voltage

- Serial communication

- Handling of Data Flash

#### 13.1 Latch-up prevention

CMOS IC chips may suffer latch-up under the following conditions:

- A voltage higher than V<sub>CC</sub> or lower than V<sub>SS</sub> is applied to an input or output pin.

- A voltage higher than the rated voltage is applied between V<sub>CC</sub> pins and V<sub>SS</sub> pins.

- The AV<sub>CC</sub> power supply is applied before the V<sub>CC</sub> voltage.

Latch-up may increase the power supply current dramatically, causing thermal damages to the device.

For the same reason, extra care is required to not let the analog power-supply voltage (AV<sub>CC</sub>, AVRH) exceed the digital power-supply voltage.

## 13.2 Unused pins handling

Unused input pins can be left open when the input is disabled (corresponding bit of Port Input Enable register PIER = 0).

Leaving unused input pins open when the input is enabled may result in misbehavior and possible permanent damage of the device. They must therefore be pulled up or pulled down through resistors. To prevent latch-up, those resistors should be more than  $2 \text{ k}\Omega$ .

Unused bidirectional pins can be set either to the output state and be then left open, or to the input state with either input disabled or external pull-up/pull-down resistor as described above.

## 13.3 External clock usage

The permitted frequency range of an external clock depends on the oscillator type and configuration. See AC Characteristics for detailed modes and frequency limits. Single and opposite phase external clocks must be connected as follows:

Document Number: 002-04579 Rev. \*A Page 55 of 109

| Parameter                                                     | Symbol           | Rating |      | Unit  | Remarks                              |

|---------------------------------------------------------------|------------------|--------|------|-------|--------------------------------------|

| r ai ainetei                                                  | Syllibol         | Min    | Max  | Oilit | Remarks                              |

| Permitted Power dissipation (Mask ROM devices) <sup>[4]</sup> | $P_D$            | -      | 350  | mW    | T <sub>A</sub> =105°C                |

| Permitted Power dissipation (Mask ROM devices) <sup>1-3</sup> | FD               | -      | 360  | mW    | T <sub>A</sub> =125°C <sup>[6]</sup> |

|                                                               | T <sub>A</sub>   | 0      | +70  |       | MB96V300B                            |

| Operating ambient temperature                                 |                  | -40    | +105 | °C    |                                      |

|                                                               |                  | -40    | +125 |       | [6]                                  |

| Storage temperature                                           | T <sub>STG</sub> | -55    | +150 | °C    |                                      |

[1]:  $AV_{CC}$  and  $V_{CC}$  must be set to the same voltage. It is required that  $AV_{CC}$  does not exceed  $V_{CC}$  and that the voltage at the analog inputs does not exceed  $AV_{CC}$  neither when the power is switched on.

[2]:  $V_I$  and  $V_O$  should not exceed  $V_{CC}$  + 0.3 V.  $V_I$  should also not exceed the specified ratings. However if the maximum current to/from a input is limited by some means with external components, the  $I_{CLAMP}$  rating supersedes the  $V_I$  rating. Input/output voltages of standard ports depend on  $V_{CC}$ .

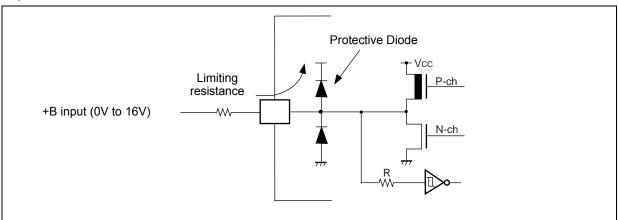

[3]:

- Applicable to all general purpose I/O pins (Pnn\_m)

- Use within recommended operating conditions.

- Use at DC voltage (current)

- The +B signal should always be applied a limiting resistance placed between the +B signal and the microcontroller.

- The value of the limiting resistance should be set so that when the +B signal is applied the input current to the microcontroller pin does not exceed rated values, either instantaneously or for prolonged periods.

- Note that when the microcontroller drive current is low, such as in the power saving modes, the +B input potential may pass through the protective diode and increase the potential at the V<sub>CC</sub> pin, and this may affect other devices.

- Note that if a +B signal is input when the microcontroller power supply is off (not fixed at 0 V), the power supply is provided from the pins, so that incomplete operation may result.

- Note that if the +B input is applied during power-on, the power supply is provided from the pins and the resulting supply voltage may not be sufficient to operate the Power reset (except devices with persistent low voltage reset in internal vector mode).

#### Sample recommended circuits:

#### 14.4 **AC Characteristics**

14.4.1 Source Clock timing ( $T_A$  = -40°C to 125°C,  $V_{CC}$  = AV $_{CC}$  = 3.0V to 5.5V,  $V_{SS}$  = AV $_{SS}$  = 0V)

| Douguestan              | Comple ed                           | Dim      |     | Value  |     | I I m i 4 | Remarks                                                                                                         |

|-------------------------|-------------------------------------|----------|-----|--------|-----|-----------|-----------------------------------------------------------------------------------------------------------------|

| Parameter               | Symbol                              | Pin      | Min | Тур    | Max | Unit      | Remarks                                                                                                         |

|                         |                                     |          | 3   | -      | 16  | MHz       | When using a crystal oscillator, PLL off                                                                        |

| Clock frequency         | $f_{\mathbb{C}}$                    | X0, X1   | 0   | -      | 16  | MHz       | When using an opposite phase external clock, PLL off                                                            |

|                         |                                     |          | 3.5 | -      | 16  | MHz       | When using a crystal oscillator or opposite phase external clock, PLL on                                        |

| Clask fraguancy         | f                                   | X0       | 0   | -      | 56  | MHz       | When using a single phase external clock in "Fast Clock Input mode" (not available in MB96F34xY/R/AxA), PLL off |

| Clock frequency         | f <sub>FCI</sub>                    | χ0       | 3.5 | -      | 56  | MHz       | When using a single phase external clock in "Fast Clock Input mode" (not available in MB96F34xY/R/AxA), PLL on  |

|                         | f <sub>CL</sub>                     | X0A, X1A | 32  | 32.768 | 100 | kHz       | When using an oscillation circuit                                                                               |

| Clock frequency         |                                     |          | 0   | -      | 100 | kHz       | When using an opposite phase external clock                                                                     |

|                         |                                     | X0A      | 0   | -      | 50  | kHz       | When using a single phase external clock                                                                        |

| Clock frequency         | f <sub>CR</sub>                     |          | 50  | 100    | 200 | kHz       | When using slow frequency of RC oscillator                                                                      |

| Clock frequency         | 'CR                                 | -        | 1   | 2      | 4   | MHz       | When using fast frequency of RC oscillator                                                                      |

| PLL Clock frequency     | f <sub>CLKVCO</sub>                 | -        | 64  | -      | 200 | MHz       | Permitted VCO output frequency of PLL (CLKVCO)                                                                  |

| PLL Phase Jitter        | T <sub>PSKEW</sub>                  | -        | -   | -      | ± 5 | ns        | For CLKMC (PLL input clock) ≥ 4MHz                                                                              |

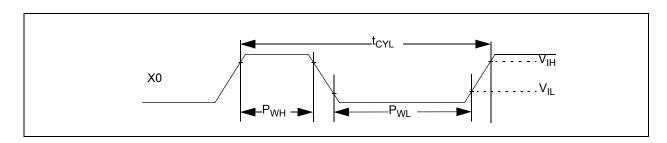

| Input clock pulse width | P <sub>WH</sub> , P <sub>WL</sub>   | X0,X1    | 8   | -      | -   | ns        | Duty ratio is about 30% to 70%                                                                                  |

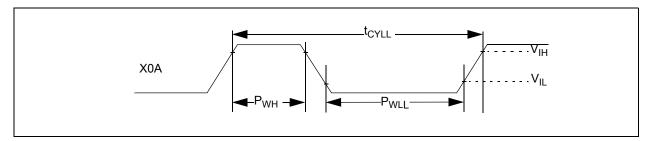

| Input clock pulse width | P <sub>WHL</sub> , P <sub>WLL</sub> | X0A,X1A  | 5   | -      | -   | μS        |                                                                                                                 |

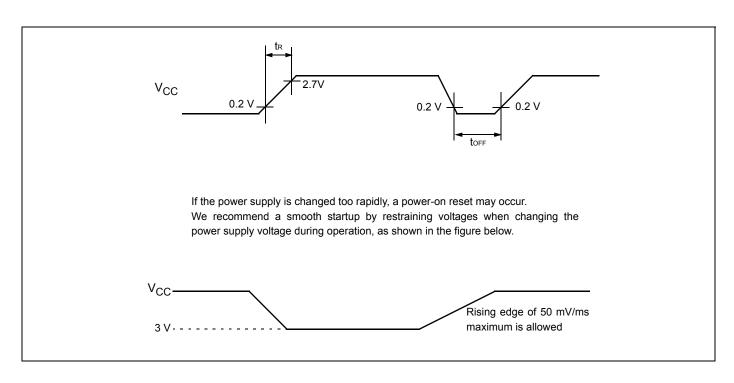

## 14.4.4 Power On Reset timing

$(T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C}, V_{CC} = \text{AV}_{CC} = 3.0\text{V to } 5.5\text{V}, V_{SS} = \text{AV}_{SS} = 0\text{V})$

| Parameter          | Symbol           | Pin |      | Value |     | Unit | Remarks |

|--------------------|------------------|-----|------|-------|-----|------|---------|

| Parameter          | Symbol           |     | Min  | Тур   | Max |      |         |

| Power on rise time | t <sub>R</sub>   | Vcc | 0.05 | -     | 30  | ms   |         |

| Power off time     | t <sub>OFF</sub> | Vcc | 1    | -     | -   | ms   |         |

#### 14.4.12 USART timing

**WARNING**: The values given below are for an I/O driving strength  $IO_{drive} = 5mA$ . If  $IO_{drive}$  is 2mA, all the maximum output timing described in the different tables must then be increased by 10ns.

$(T_A = -40^{\circ}C \text{ to } 125^{\circ}C, V_{CC} = 3.0V \text{ to } 5.5V, V_{SS} = AV_{SS} = 0V, IO_{drive} = 5mA, C_L = 50pF)$

| Parameter                    | Symbol Pin         |               | Condition                    | V <sub>CC</sub> = AV <sub>CC</sub> =     | 4.5V to 5.5V              | $V_{CC} = AV_{CC} =$                     | Unit                      |       |

|------------------------------|--------------------|---------------|------------------------------|------------------------------------------|---------------------------|------------------------------------------|---------------------------|-------|

| raiailletei                  | Syllibol           | FIII          | Condition                    | Min                                      | Max                       | Min                                      | Max                       | Oilit |

| Serial clock cycle time      | t <sub>SCYCI</sub> | SCKn          |                              | 4 t <sub>CLKP1</sub>                     | -                         | 4 t <sub>CLKP1</sub>                     | -                         | ns    |

| SCK ↓→ SOT delay time        | t <sub>SLOVI</sub> | SCKn,<br>SOTn |                              | -20                                      | +20                       | -30                                      | +30                       | ns    |

| SOT → SCK ↑ delay time       | t <sub>OVSHI</sub> | SCKn,<br>SOTn | Internal Shift<br>Clock Mode | N*t <sub>CLKP1</sub> - 20 <sup>[1]</sup> | -                         | N*t <sub>CLKP1</sub> - 30 <sup>[1]</sup> | -                         | ns    |

| Valid SIN → SCK ↑            | t <sub>IVSHI</sub> | SCKn,<br>SINn | - Olosik ilious              | t <sub>CLKP1</sub> + 45                  | -                         | t <sub>CLKP1</sub> + 55                  | -                         | ns    |

| SCK ↑→ Valid SIN hold time   | t <sub>SHIXI</sub> | SCKn,<br>SINn |                              | 0                                        | -                         | 0                                        | -                         | ns    |

| Serial clock "L" pulse width | t <sub>SLSHE</sub> | SCKn          |                              | t <sub>CLKP1</sub> + 10                  | -                         | t <sub>CLKP1</sub> + 10                  | -                         | ns    |

| Serial clock "H" pulse width | t <sub>SHSLE</sub> | SCKn          |                              | t <sub>CLKP1</sub> + 10                  | -                         | t <sub>CLKP1</sub> + 10                  | -                         | ns    |

| SCK ↓→ SOT delay time        | t <sub>SLOVE</sub> | SCKn,<br>SOTn |                              | -                                        | 2 t <sub>CLKP1</sub> + 45 | -                                        | 2 t <sub>CLKP1</sub> + 55 | ns    |

| Valid SIN → SCK ↑            | t <sub>IVSHE</sub> | SCKn,<br>SINn | External Shift<br>Clock Mode | t <sub>CLKP1</sub> /2 + 10               | -                         | t <sub>CLKP1</sub> /2 + 10               | -                         | ns    |

| SCK ↑→ Valid SIN hold time   | t <sub>SHIXE</sub> | SCKn,<br>SINn |                              | t <sub>CLKP1</sub> + 10                  | -                         | t <sub>CLKP1</sub> + 10                  | -                         | ns    |

| SCK fall time                | t <sub>FE</sub>    | SCKn          |                              | -                                        | 20                        | -                                        | 20                        | ns    |

| SCK rise time                | t <sub>RE</sub>    | SCKn          |                              | -                                        | 20                        | -                                        | 20                        | ns    |

#### Notes:

- AC characteristic in CLK synchronized mode.

- C<sub>L</sub> is the load capacity value of pins when testing.

- Depending on the used machine clock frequency, the maximum possible baud rate can be limited by some parameters. These parameters are shown in "MB96300 Super series HARDWARE MANUAL".

- $\blacksquare$   $t_{CLKP1}$  is the cycle time of the peripheral clock 1 (CLKP1), Unit : ns

- [1]: Parameter N depends on  $t_{SCYCI}$  and can be calculated as follows:

- if t<sub>SCYCI</sub> = 2\*k\*t<sub>CLKP1</sub>, then N = k, where k is an integer > 2

- if  $t_{SCYCI} = (2*k+1)*t_{CLKP1}$ , then N = k+1, where k is an integer > 1

#### Examples:

| t <sub>scyci</sub>    | N |

|-----------------------|---|

| 4*t <sub>CLKP1</sub>  | 2 |

| 5*t <sub>CLKP1,</sub> | 3 |

| 7*t <sub>CLKP1,</sub> | 4 |

|                       |   |

Document Number: 002-04579 Rev. \*A Page 85 of 109

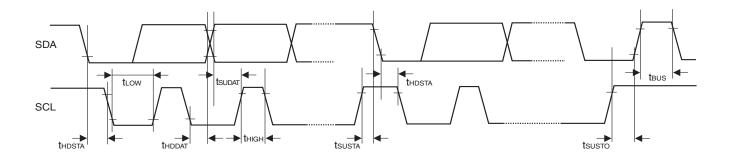

## 14.4.13 I<sup>2</sup>C Timing

$(T_A = -40^{\circ}C \text{ to } 125^{\circ}C, V_{CC} = AV_{CC} = 3.0V \text{ to } 5.5V, V_{SS} = AV_{SS} = 0V)$

| Parameter                                            | Symbol             | Condition                                               | Standar | d-mode              | Fast-mode <sup>[4]</sup> |                    | Unit  |

|------------------------------------------------------|--------------------|---------------------------------------------------------|---------|---------------------|--------------------------|--------------------|-------|

| i didilietei                                         | Cymbol             | Condition                                               | Min     | Max                 | Min                      | Max                | Oilit |

| SCL clock frequency                                  | f <sub>SCL</sub>   |                                                         | 0       | 100                 | 0                        | 400                | kHz   |

| Hold time (repeated) START condition SDA↓→SCL¬       | t <sub>HDSTA</sub> |                                                         | 4.0     | -                   | 0.6                      | -                  | μS    |

| "L" width of the SCL clock                           | t <sub>LOW</sub>   |                                                         | 4.7     | -                   | 1.3                      | -                  | μS    |

| "H" width of the SCL clock                           | t <sub>HIGH</sub>  |                                                         | 4.0     | -                   | 0.6                      | -                  | μS    |

| Set-up time for a repeated START condition SCL↓→SDA↑ | t <sub>SUSTA</sub> | $R = 1.7 \text{ k}\Omega,$<br>$C = 50 \text{ pF}^{[1]}$ | 4.7     | -                   | 0.6                      | -                  | μS    |

| Data hold timeSCL↑→SDA↑↓                             | t <sub>HDDAT</sub> |                                                         | 0       | 3.45 <sup>[2]</sup> | 0                        | 0.9 <sup>[3]</sup> | μS    |

| Data set-up timeSDA↑↓→SCL↑                           | t <sub>SUDAT</sub> |                                                         | 250     | -                   | 100                      | -                  | ns    |

| Set-up time for STOP conditionSCL↑→SDA↑              | t <sub>SUSTO</sub> |                                                         | 4.0     | -                   | 0.6                      | -                  | μS    |

| Bus free time between a STOP and START condition     | t <sub>BUS</sub>   |                                                         | 4.7     | -                   | 1.3                      | -                  | μS    |

<sup>[1]:</sup> R,C: Pull-up resistor and load capacitor of the SCL and SDA lines.

[2]: The maximum  $t_{HDDAT}$  have only to be met if the device does not stretch the "L" width  $(t_{LOW})$  of the SCL signal.

[3] : A Fast-mode  $I^2C$ -bus device can be used in a Standard-mode  $I^2C$ -bus system, but the requirement  $t_{SUDAT} \ge 250$  ns must then be met.

[4]: For use at over 100 kHz, set the peripheral clock 1 to at least 6 MHz.

Document Number: 002-04579 Rev. \*A Page 87 of 109

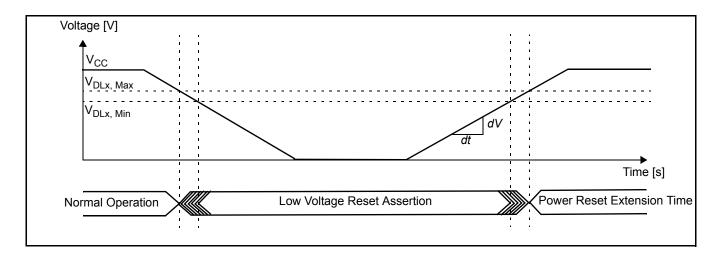

## **Low Voltage Detector Characteristics**

$(T_A = -40 \, ^{\circ}\text{C to} + 125 \, ^{\circ}\text{C}, \, V_{cc} = \text{AV}_{cc} = 3.0\text{V} - 5.5\text{V}, \, V_{ss} = \text{AV}_{ss} = 0\text{V})$

| Parameter          | Symbol               | Value <sup>[1]</sup> |      | Value <sup>[2]</sup> |          | Unit  | Remarks                                     |  |

|--------------------|----------------------|----------------------|------|----------------------|----------|-------|---------------------------------------------|--|

| i didilietei       | Cymbol               | Min                  | Max  | Min                  | Max      | Oiiit | Nemarks                                     |  |

| Stabilization time | T <sub>LVDSTAB</sub> | -                    | 75   | -                    | 110      | μS    | After power-up or change of detection level |  |

| Level 0            | V <sub>DL0</sub>     | 2.7                  | 2.9  | 2.65                 | 2.95     | V     | CILCR:LVL[3:0]="0000"                       |  |

| Level 1            | V <sub>DL1</sub>     | 2.9                  | 3.1  | 2.85                 | 3.2      | V     | CILCR:LVL[3:0]="0001"                       |  |

| Level 2            | V <sub>DL2</sub>     | 3.1                  | 3.3  | 3.05                 | 3.4      | V     | CILCR:LVL[3:0]="0010"                       |  |

| Level 3            | $V_{DL3}$            | 3.5                  | 3.75 | 3.45                 | 3.85     | V     | CILCR:LVL[3:0]="0011"                       |  |

| Level 4            | $V_{DL4}$            | 3.6                  | 3.85 | 3.55                 | 3.95     | V     | CILCR:LVL[3:0]="0100"                       |  |

| Level 5            | $V_{DL5}$            | 3.7                  | 3.95 | 3.65                 | 4.1      | V     | CILCR:LVL[3:0]="0101"                       |  |

| Level 6            | V <sub>DL6</sub>     | 3.8                  | 4.05 | 3.75                 | 4.2      | V     | CILCR:LVL[3:0]="0110"                       |  |

| Level 7            | V <sub>DL7</sub>     | 3.9                  | 4.15 | 3.85                 | 4.3      | V     | CILCR:LVL[3:0]="0111"                       |  |

| Level 8            | V <sub>DL8</sub>     | 4.0                  | 4.25 | 3.95                 | 4.4      | V     | CILCR:LVL[3:0]="1000"                       |  |

| Level 9            | $V_{DL9}$            | 4.1                  | 4.35 | 4.05                 | 4.5      | V     | CILCR:LVL[3:0]="1001"                       |  |

| Level 10           | V <sub>DL10</sub>    | not i                | used | not                  | used     |       |                                             |  |

| Level 11           | V <sub>DL11</sub>    | not i                | used | not                  | not used |       |                                             |  |

| Level 12           | V <sub>DL12</sub>    | not i                | used | not used             |          |       |                                             |  |

| Level 13           | V <sub>DL13</sub>    | not i                | used | not used             |          |       |                                             |  |

| Level 14           | V <sub>DL14</sub>    | not i                | used | not used             |          |       |                                             |  |

| Level 15           | V <sub>DL15</sub>    | not (                | used | not used             |          |       |                                             |  |

[1]: valid for all devices except devices listed under "[2]"

[2]: valid for: MB96F345

CILCR:LVL[3:0] are the low voltage detector level select bits of the CILCR register.

Levels 10 to 15 are not used in this device.

For correct detection, the slope of the voltage level must satisfy  $\left| \frac{dV}{dt} \right| \le 0.004 \frac{V}{\mu s}$ .

Faster variations are regarded as noise and may not be detected.

The functional operation of the MCU is guaranteed down to the minimum low voltage detection level of Vcc = 2.7V. The electrical characteristics however are only valid in the specified range (usually down to 3.0V).

Document Number: 002-04579 Rev. \*A Page 94 of 109

## 14.7.1 Low Voltage Detector Operation

In the following figure, the occurrence of a low voltage condition is illustrated. For a detailed description of the reset and startup behavior, please refer to the corresponding hardware manual chapter.

Table 6: Used settings

| Mode       | Selected Source<br>Clock | Clock/Regulator Settings                                                                                                       |

|------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Run mode   | PLL                      | CLKS1 = CLKS2 = CLKB = CLKP1 = 56 MHz CLKP2 = 28 MHz Regulator in High Power Mode Core Voltage = 1.9 V                         |

|            | Main osc.                | CLKS1 = CLKS2 = CLKB = CLKP1 = CLKP2 = 4 MHz Regulator in High Power Mode Core Voltage = 1.8 V                                 |

|            | RC clock fast            | CLKS1 = CLKS2 = CLKB = CLKP1 = CLKP2 = 2 MHz Regulator in High Power Mode Core Voltage = 1.8 V                                 |

|            | RC clock slow            | CLKS1 = CLKS2 = CLKB = CLKP1 = CLKP2 = 100 kHz Regulator in High Power Mode Core Voltage = 1.8 V                               |

|            | Sub osc.                 | CLKS1 = CLKS2 = CLKB = CLKP1 = CLKP2 = 32 kHz Regulator in Low Power Mode A Core Voltage = 1.8 V                               |

| Sleep mode | PLL                      | CLKS1 = CLKS2 = CLKP1 = 56 MHz CLKP2 = 28 MHz (CLKB is stopped in this mode) Regulator in High Power Mode Core Voltage = 1.9 V |

|            | Main osc.                | CLKS1 = CLKS2 = CLKP1 = CLKP2 = 4 MHz (CLKB is stopped in this mode) Regulator in High Power Mode Core Voltage = 1.8 V         |

|            | RC clock fast            | CLKS1 = CLKS2 = CLKP1 = CLKP2 = 2 MHz (CLKB is stopped in this mode) Regulator in High Power Mode Core Voltage = 1.8 V         |

|            | RC clock slow            | CLKS1 = CLKS2 = CLKP1 = CLKP2 = 100 kHz (CLKB is stopped in this mode) Regulator in High Power Mode Core Voltage = 1.8 V       |

|            | Sub osc.                 | CLKS1 = CLKS2 = CLKP1 = CLKP2 = 32 kHz (CLKB is stopped in this mode) Regulator in Low Power Mode A Core Voltage = 1.8 V       |

Table 6: Used settings

| Mode       | Selected Source<br>Clock | Clock/Regulator Settings                                                                                                         |

|------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Timer mode | PLL                      | CLKMC = 4 MHz, CLKPLL = 56 MHz<br>(System clocks are stopped in this mode)<br>Regulator in High Power Mode, Core Voltage = 1.9 V |

|            | Main osc.                | CLKMC = 4 MHz (System clocks are stopped in this mode) Regulator in High Power Mode, Core Voltage = 1.8 V                        |

|            | RC clock fast            | CLKRC = 2 MHz (System clocks are stopped in this mode) Regulator in High Power Mode, Core Voltage = 1.8 V                        |

|            | RC clock slow            | CLKRC = 100 kHz (System clocks are stopped in this mode) Regulator in High Power Mode, Core Voltage = 1.8 V                      |

|            | Sub osc.                 | CLKSC = 100 kHz (System clocks are stopped in this mode) Regulator in Low Power Mode A, Core Voltage = 1.8 V                     |

| Stop mode  | stopped                  | (All clocks are stopped in this mode) Regulator in Low Power Mode B, Core Voltage = 1.8 V                                        |

#### Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

ARM® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface cypress.com/interface Lighting & Power Control cypress.com/powerpsoc Memory cypress.com/memory **PSoC** cypress.com/psoc Touch Sensing cypress.com/touch **USB Controllers** cypress.com/usb Wireless/RF cypress.com/wireless PSoC® Solutions

cypress.com/psoc

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

**Cypress Developer Community**

Community | Forums | Blogs | Video | Training

**Technical Support**

cypress.com/support

ARM and Cortex are the trademarks of ARM Limited in the EU and other countries

© Cypress Semiconductor Corporation 2009-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you under its copyright rights in the Software, a personal, non-exclusive, nontransferable license (without the right to sublicense) (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units. Cypress also grants you a personal, non-exclusive, nontransferable, license (without the right to sublicense) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely to the minimum extent that is necessary for you to exercise your rights under the copyright license granted in the previous sentence. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and Company shall and hereby does release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. Company shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.