# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 166MHz                                                                |

| Co-Processors/DSP               | Communications; CPM                                                   |

| RAM Controllers                 | DRAM                                                                  |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10Mbps (1)                                                            |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 3.3V                                                                  |

| Operating Temperature           | 0°C ~ 95°C (TA)                                                       |

| Security Features               | -                                                                     |

| Package / Case                  | 256-BBGA                                                              |

| Supplier Device Package         | 256-PBGA (23x23)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc853tzt66a |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Features

- SPI (serial peripheral interface)

- Supports master and slave modes

- Supports multiple-master operation on the same bus

- The MPC853T has a time-slot assigner (TSA) that supports one TDM bus (TDMb)

- Allows SCCs and SMC to run in multiplexed and/or non-multiplexed operation

- Supports T1, CEPT, PCM highway, ISDN basic rate, ISDN primary rate, user defined

- 1- or 8-bit resolution

- Allows independent transmit and receive routing, frame synchronization, and clocking

- Allows dynamic changes

- Can be internally connected to three serial channels (two SCCs and one SMC)

- PCMCIA interface

- Master (socket) interface, release 2.1 compliant

- Supports one independent PCMCIA socket, 8 memory or I/O windows

- Debug interface

- Eight comparators: four operate on instruction address, two operate on data address, and two operate on data

- Supports conditions: =  $\neq < >$

- Each watchpoint can generate a break point internally

- Normal high and normal low power modes to conserve power

- 1.8-V core and 3.3-V I/O operation with 5-V TTL compatibility. Refer to Table 5 for a listing of the 5-V tolerant pins.

**Maximum Tolerated Ratings**

## 3 Maximum Tolerated Ratings

This section provides the maximum tolerated voltage and temperature ranges for the MPC853T. Table 1 provides the maximum ratings and the operating temperatures.

| Rating                      | Symbol                                                        | Value                       | Unit |

|-----------------------------|---------------------------------------------------------------|-----------------------------|------|

| Supply voltage <sup>1</sup> | V <sub>DDL</sub> (core voltage)                               | -0.3 to 3.4                 | V    |

|                             | V <sub>DDH</sub> (I/O voltage)                                | -0.3 to 4                   | V    |

|                             | V <sub>DDSYN</sub>                                            | -0.3 to 3.4                 | V    |

|                             | Difference between V <sub>DDL</sub><br>and V <sub>DDSYN</sub> | 100                         | mV   |

| Input voltage <sup>2</sup>  | V <sub>in</sub>                                               | GND–0.3 to V <sub>DDH</sub> | V    |

| Storage temperature range   | T <sub>stg</sub>                                              | –55 to +150                 | °C   |

### Table 1. Maximum Tolerated Ratings

<sup>1</sup> The power supply of the device must start its ramp from 0.0 V.

<sup>2</sup> Functional operating conditions are provided with the DC electrical specifications in Table 5. Absolute maximum ratings are stress ratings only; functional operation at the maxima is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage to the device.

**Caution**: All inputs that tolerate 5 V cannot be more than 2.5 V greater than  $V_{DDH}$ . This restriction applies to power up and normal operation (that is, if the MPC853T is unpowered, a voltage greater than 2.5 V must not be applied to its inputs).

### **Table 2. Operating Temperatures**

| Rating                              | Symbol              | Value | Unit |

|-------------------------------------|---------------------|-------|------|

| Temperature <sup>1</sup> (standard) | T <sub>A(min)</sub> | 0     | °C   |

|                                     | T <sub>j(max)</sub> | 95    | °C   |

| Temperature (extended)              | T <sub>A(min)</sub> | -40   | °C   |

|                                     | T <sub>j(max)</sub> | 100   | °C   |

<sup>1</sup> Minimum temperatures are guaranteed as ambient temperature, T<sub>A</sub>. Maximum temperatures are guaranteed as junction temperature, T<sub>j</sub>.

This device contains circuitry protecting against damage caused by high-static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND, V<sub>DDL</sub>, or V<sub>DDH</sub>).

**Mandatory Reset Configurations**

## 9 Mandatory Reset Configurations

The MPC853T requires a mandatory configuration during reset.

If hardware reset configuration word (HRCW) is enabled, the HRCW[DBGC] value needs to be set to binary X1 in HRCW, and the SIUMCR[DBGC] should be programmed with the same value in the boot code after reset. This can be done by asserting the RSTCONF during HRESET assertion.

If HRCW is disabled, the SIUMCR[DBGC] should be programmed with binary X1 in the boot code after reset by negating the  $\overline{\text{RSTCONF}}$  during the  $\overline{\text{HRESET}}$  assertion.

The MBMR[GPLB4DIS], PAPAR, PADIR, PBPAR, PBDIR, PCPAR, and PCDIR registers need to be configured with the mandatory value in Table 6 in the boot code after the reset is negated.

| Register/Configuration                        | Field                                     | Value<br>(binary) |

|-----------------------------------------------|-------------------------------------------|-------------------|

| HRCW<br>(Hardware reset configuration word)   | HRCW[DBGC]                                | 0bx1              |

| SIUMCR<br>(SIU module configuration register) | SIUMCR[DBGC]                              | 0bx1              |

| MBMR<br>(Machine B mode register)             | MBMR[GPLB4DIS}                            | 0                 |

| PAPAR<br>(Port A pin assignment register)     | PAPAR[4:7]<br>PAPAR[12:15]                | 0                 |

| PADIR<br>(Port A data direction register)     | PADIR[4:7]<br>PADIR[12:15]                | 1                 |

| PBPAR<br>(Port B pin assignment register)     | PBPAR[14]<br>PBPAR[16:23]<br>PBPAR[26:27] | 0                 |

| PBDIR<br>(Port B Data direction register)     | PBDIR[14]<br>PBDIR[16:23]<br>PBDIR[26:27] | 1                 |

### Table 6. Mandatory Reset Configuration of MPC853T

| Register/Configuration                    | Field                    | Value<br>(binary) |

|-------------------------------------------|--------------------------|-------------------|

| PCPAR<br>(Port C pin assignment register) | PCPAR[8:11]<br>PCDIR[14] | 0                 |

| PCDIR<br>(Port C data direction register) | PCDIR[8:11]<br>PCDIR[14] | 1                 |

| Table 0. Manualory nesel configuration of Mr CossT (continued) | Table 6. Mandatory | y Reset Configuration of MPC853T | (continued) |

|----------------------------------------------------------------|--------------------|----------------------------------|-------------|

|----------------------------------------------------------------|--------------------|----------------------------------|-------------|

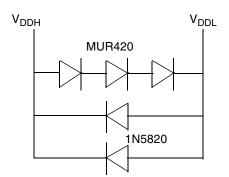

## **10 Layout Practices**

Each  $V_{DD}$  pin on the MPC853T should be provided with a low-impedance path to the board's supply. Each GND pin should likewise be provided with a low-impedance path to ground. The power supply pins drive distinct groups of logic on chip. The  $V_{DD}$  power supply should be bypassed to ground using at least four 0.1-µF bypass capacitors located as close as possible to the four sides of the package. Each board designed should be characterized, and additional appropriate decoupling capacitors should be used if required. Capacitor leads and associated printed circuit traces connecting to chip  $V_{DD}$  and GND should be kept to less than half an inch per capacitor lead. At a minimum, a four-layer board employing two inner layers as  $V_{DD}$  and GND planes should be used.

All output pins on the MPC853T have fast rise and fall times. Printed circuit (PC) trace interconnection length should be minimized in order to minimize undershoot and reflections caused by these fast output switching times. This recommendation particularly applies to the address and data busses. Maximum PC trace lengths of six inches are recommended. Capacitance calculations should consider all device loads, as well as parasitic capacitances caused by the PC traces. Attention to proper PCB layout and bypassing becomes especially critical in systems with higher capacitive loads because these loads create higher transient currents in the  $V_{DD}$  and GND circuits. Pull up all unused inputs or signals that will be inputs during reset. Special care should be taken to minimize the noise levels on the PLL supply pins. For more information, please refer to Section 14.4.3, "Clock Synthesizer Power ( $V_{DDSYN}$ ,  $V_{SSSYN}$ ,  $V_{SSSYN}$ ,  $V_{SSSYN}$ )" in the *MPC866 PowerQUICC Family User's Manual*.

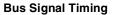

## **11 Bus Signal Timing**

The maximum bus speed supported by the MPC853T is 66 MHz. Table 7 shows the frequency ranges for standard part frequencies in 1:1 bus mode.

| Part Frequency | 50  | MHz | 66 MHz |       |  |  |

|----------------|-----|-----|--------|-------|--|--|

|                | Min | Мах | Min    | Мах   |  |  |

| Core Frequency | 40  | 50  | 40     | 66.67 |  |  |

| Bus Frequency  | 40  | 50  | 40     | 66.67 |  |  |

Table 7. Frequency Ranges for Standard Part Frequencies (1:1 Bus Mode)

Table 8 shows the frequency ranges for standard part frequencies in 2:1 bus mode.

|      | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33 1  | MHz   | 40 MHz |       | 50 MHz |       | 66 MHz |       |      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|--------|-------|--------|-------|--------|-------|------|

| Num  | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Min   | Max   | Min    | Max   | Min    | Max   | Min    | Max   | Unit |

| B26  | CLKOUT rising edge to $\overline{OE}$ negated (MAX = 0.00 × B1 + 9.00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.00  | 9.00  | 2.00   | 9.00  | 2.00   | 9.00  | 2.00   | 9.00  | ns   |

| B27  | A(0:31) and BADDR(28:30) to $\overline{CS}$<br>asserted GPCM ACS = 10, TRLX = 1<br>(MIN = 1.25 × B1 - 2.00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35.90 |       | 29.30  |       | 23.00  |       | 16.90  |       | ns   |

| B27a | A(0:31) and BADDR(28:30) to $\overline{CS}$<br>asserted GPCM ACS = 11, TRLX = 1<br>(MIN = 1.50 × B1 - 2.00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 43.50 |       | 35.50  |       | 28.00  |       | 20.70  |       | ns   |

| B28  | CLKOUT rising edge to<br>$\overline{WE}(0:3)/BS_B[0:3]$ negated GPCM<br>write access CSNT = 0<br>(MAX = 0.00 × B1 + 9.00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       | 9.00  |        | 9.00  |        | 9.00  |        | 9.00  | ns   |

| B28a | CLKOUT falling edge to<br>$\overline{WE}(0:3)/BS_B[0:3]$ negated GPCM<br>write access TRLX = 0,1 CSNT = 1,<br>EBDF = 0 (MAX = 0.25 × B1 + 6.80)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7.60  | 14.30 | 6.30   | 13.00 | 5.00   | 11.80 | 3.80   | 10.50 | ns   |

| B28b | CLKOUT falling edge to $\overline{CS}$ negated<br>GPCM write access TRLX = 0,1<br>CSNT = 1 ACS = 10 or ACS = 11,<br>EBDF = 0 (MAX = 0.25 × B1 + 6.80)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _     | 14.30 | _      | 13.00 | _      | 11.80 | _      | 10.50 | ns   |

| B28c | $\label{eq:clkout_falling} \begin{array}{l} \text{clkout_falling edge to} \\ \hline WE(0:3)/BS_B[0:3] \text{ negated GPCM} \\ \text{write access TRLX} = 0,1 \text{ CSNT} = 1 \text{ write} \\ \text{access TRLX} = 0,1 \text{ CSNT} = 1, \\ \text{EBDF} = 1 \mbox{ (MAX} = 0.375 \times B1 + 6.6) \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10.90 | 18.00 | 10.90  | 18.00 | 7.00   | 14.30 | 5.20   | 12.30 | ns   |

| B28d | CLKOUT falling edge to $\overline{CS}$ negated<br>GPCM write access TRLX = 0,1<br>CSNT = 1, ACS = 10, or ACS = 11,<br>EBDF = 1 (MAX = 0.375 × B1 + 6.6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _     | 18.00 | _      | 18.00 | _      | 14.30 | _      | 12.30 | ns   |

| B29  | $\label{eq:weighted_states} \begin{array}{l} \overline{\text{WE}}(0:3)/\text{BS}_{B}[0:3] \text{ negated to D}(0:31), \\ \text{DP}(0:3) \text{ High-Z GPCM write access,} \\ \text{CSNT} = 0, \text{ EBDF} = 0 \\ (\text{MIN} = 0.25 \times \text{B1} - 2.00) \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.60  | _     | 4.30   | _     | 3.00   | _     | 1.80   | _     | ns   |

| B29a | $eq:weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_$ | 13.20 | _     | 10.50  | _     | 8.00   | _     | 5.60   | _     | ns   |

| B29b | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3), High-Z<br>GPCM write access, ACS = 00,<br>TRLX = 0,1 & CSNT = 0<br>(MIN = 0.25 × B1 - 2.00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5.60  | _     | 4.30   |       | 3.00   | _     | 1.80   |       | ns   |

## Table 9. Bus Operation Timings (continued)

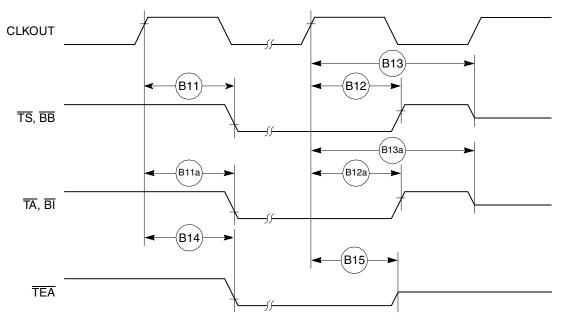

Figure 5 provides the timing for the synchronous output signals.

Figure 6 provides the timing for the synchronous active pull-up and open-drain output signals.

Figure 6. Synchronous Active Pull-Up Resistor and Open-Drain Outputs Signals Timing

MPC853T Hardware Specification, Rev. 1

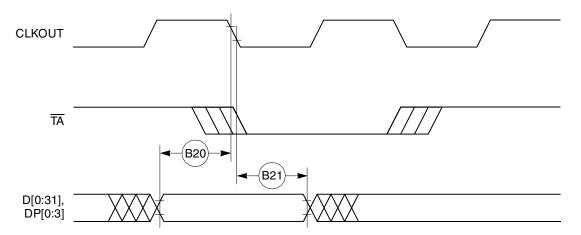

Figure 9 provides the timing for the input data controlled by the UPM for data beats where DLT3 = 1 in the UPM RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.)

### Figure 9. Input Data Timing When Controlled by the UPM in the Memory Controller and DLT3 = 1

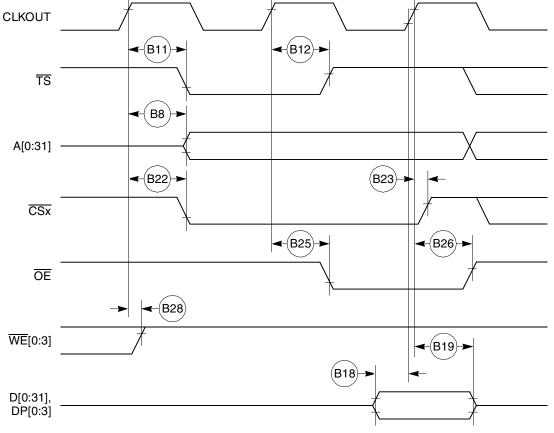

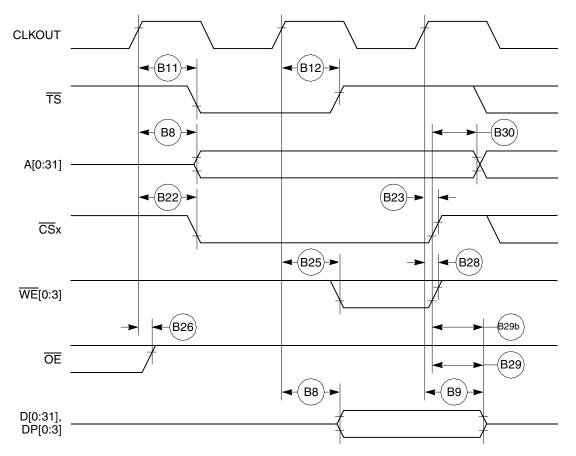

Figure 10 through Figure 13 provide the timing for the external bus read controlled by various GPCM factors.

Figure 10. External Bus Read Timing (GPCM Controlled—ACS = 00)

MPC853T Hardware Specification, Rev. 1

**Bus Signal Timing**

Figure 14. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 0)

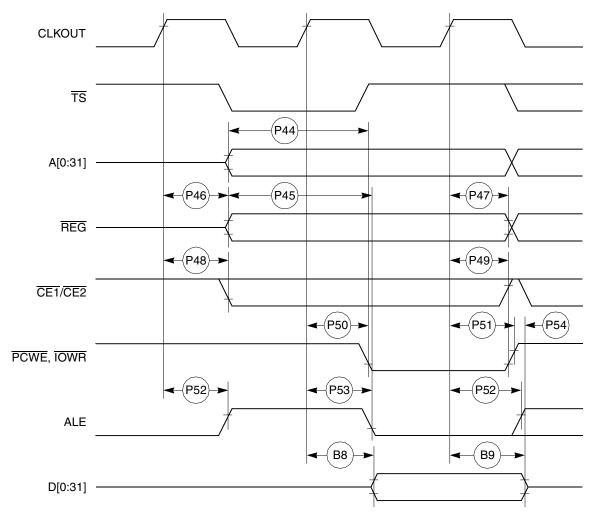

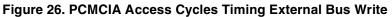

Table 11 shows the PCMCIA timing for the MPC853T.

Table 11. PCMCIA Timing

| Num | Characteristic                                                                                                                                              |       | 33 MHz |       | 40 MHz |       | 50 MHz |       | 66 MHz |      |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|-------|--------|-------|--------|-------|--------|------|

| Num | Gharacteristic                                                                                                                                              | Min   | Max    | Min   | Max    | Min   | Max    | Min   | Max    | Unit |

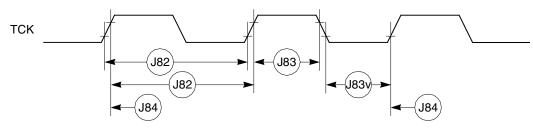

| J82 | A(0:31), $\overline{\text{REG}}$ valid to PCMCIA strobe<br>asserted <sup>1</sup> (MIN = 0.75 × B1 - 2.00)                                                   | 20.70 |        | 16.70 |        | 13.00 | _      | 9.40  | _      | ns   |

| J83 | A(0:31), $\overline{\text{REG}}$ valid to ALE negation <sup>1</sup><br>(MIN = 1.00 × B1 - 2.00)                                                             | 28.30 | _      | 23.00 | _      | 18.00 | —      | 13.20 | —      | ns   |

| J84 | CLKOUT to $\overline{\text{REG}}$ valid<br>(MAX = 0.25 × B1 + 8.00)                                                                                         | 7.60  | 15.60  | 6.30  | 14.30  | 5.00  | 13.00  | 3.80  | 11.80  | ns   |

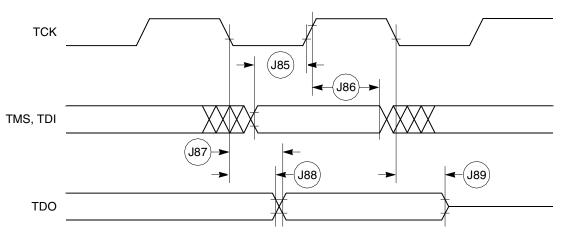

| J85 | CLKOUT to $\overline{\text{REG}}$ invalid<br>(MIN = 0.25 × B1 + 1.00)                                                                                       | 8.60  | —      | 7.30  | —      | 6.00  | _      | 4.80  | _      | ns   |

| J86 | CLKOUT to $\overline{CE1}$ , $\overline{CE2}$ asserted<br>(MAX = 0.25 × B1 + 8.00)                                                                          | 7.60  | 15.60  | 6.30  | 14.30  | 5.00  | 13.00  | 3.80  | 11.80  | ns   |

| J87 | CLKOUT to $\overline{CE1}$ , $\overline{CE2}$ negated<br>(MAX = 0.25 × B1 + 8.00)                                                                           | 7.60  | 15.60  | 6.30  | 14.30  | 5.00  | 13.00  | 3.80  | 11.80  | ns   |

| J88 | CLKOUT to PCOE, IORD, PCWE,<br>IOWR assert time<br>(MAX = 0.00 × B1 + 11.00)                                                                                |       | 11.00  |       | 11.00  |       | 11.00  | _     | 11.00  | ns   |

| J89 | CLKOUT to $\overrightarrow{PCOE}$ , $\overrightarrow{IORD}$ , $\overrightarrow{PCWE}$ ,<br>$\overrightarrow{IOWR}$ negate time<br>(MAX = 0.00 × B1 + 11.00) | 2.00  | 11.00  | 2.00  | 11.00  | 2.00  | 11.00  | 2.00  | 11.00  | ns   |

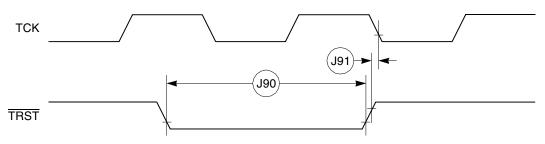

| J90 | CLKOUT to ALE assert time<br>(MAX = $0.25 \times B1 + 6.30$ )                                                                                               | 7.60  | 13.80  | 6.30  | 12.50  | 5.00  | 11.30  | 3.80  | 10.00  | ns   |

| J91 | CLKOUT to ALE negate time $(MAX = 0.25 \times B1 + 8.00)$                                                                                                   | _     | 15.60  | _     | 14.30  |       | 13.00  |       | 11.80  | ns   |

| J92 | $\overline{\text{PCWE}}, \overline{\text{IOWR}} \text{ negated to } D(0:31)$ invalid <sup>1</sup> (MIN = 0.25 × B1 – 2.00)                                  | 5.60  | _      | 4.30  | —      | 3.00  | —      | 1.80  | _      | ns   |

| J93 | $\overline{\text{WAITA}}$ and $\overline{\text{WAITB}}$ valid to CLKOUT rising edge <sup>1</sup> (MIN = 0.00 × B1 + 8.00)                                   | 8.00  |        | 8.00  | —      | 8.00  | —      | 8.00  | —      | ns   |

| J94 | CLKOUT rising edge to $\overline{WAITA}$ and $\overline{WAITB}$ invalid <sup>1</sup><br>(MIN = 0.00 × B1 + 2.00)                                            | 2.00  | —      | 2.00  | —      | 2.00  | —      | 2.00  | —      | ns   |

<sup>1</sup> PSST = 1. Otherwise add PSST times cycle time.

PSHT = 0. Otherwise add PSHT times cycle time.

These synchronous timings define when the WAITA signals are detected in order to freeze (or relieve) the PCMCIA current cycle. The WAITA assertion will be effective only if it is detected two cycles before the PSL timer expiration. See the Chapter 16, "PCMCIA Interface," in the *MPC866 PowerQUICC Family User's Manual*.

Figure 26 provides the PCMCIA access cycle timing for the external bus write.

Figure 27 provides the PCMCIA  $\overline{WAIT}$  signals detection timing.

Figure 27. PCMCIA WAIT Signals Detection Timing

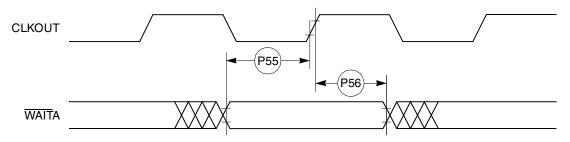

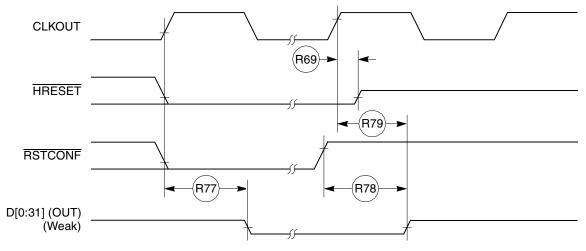

Figure 32 shows the reset timing for the data bus configuration.

Figure 32. Reset Timing—Configuration from Data Bus

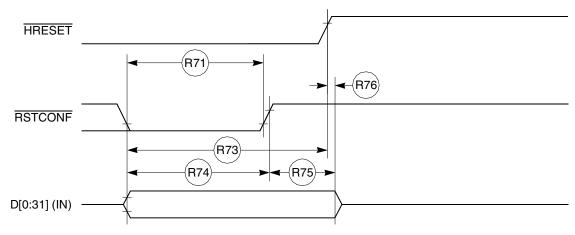

Figure 33 provides the reset timing for the data bus weak drive during configuration.

Figure 33. Reset Timing—Data Bus Weak Drive During Configuration

#### **IEEE 1149.1 Electrical Specifications**

Figure 35. JTAG Test Clock Input Timing

Figure 36. JTAG Test Access Port Timing Diagram

Figure 37. JTAG TRST Timing Diagram

| Num | Characteristic                                                           | All Freq | Unit                  |            |  |

|-----|--------------------------------------------------------------------------|----------|-----------------------|------------|--|

| Num | Characteristic                                                           | Min      | Мах                   |            |  |

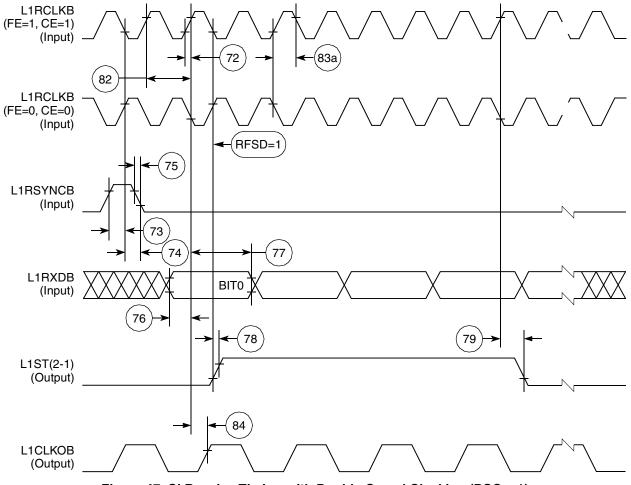

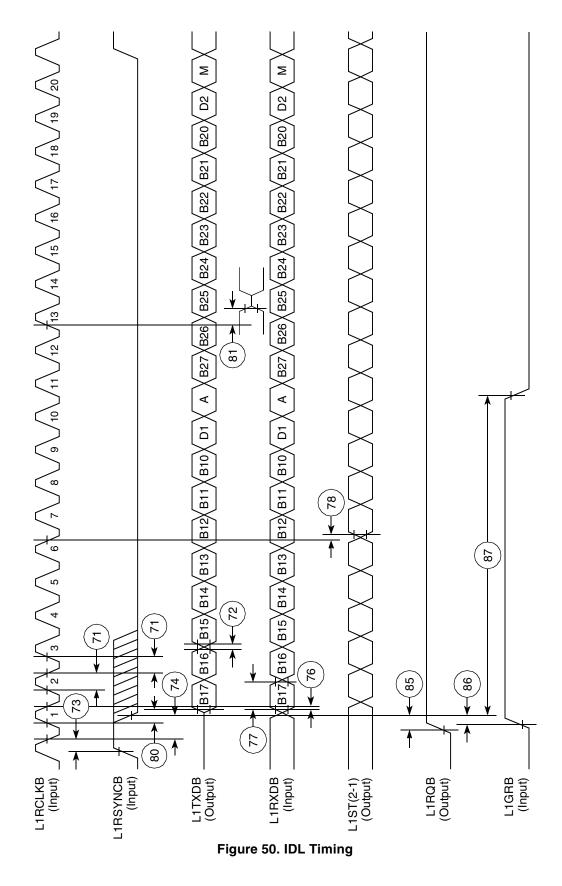

| 75  | L1RSYNCB, L1TSYNCB rise/fall time                                        |          | 15.00                 | ns         |  |

| 76  | L1RXDB valid to L1CLKB edge (L1RXDB setup time)                          | 17.00    | —                     | ns         |  |

| 77  | L1CLKB edge to L1RXDB invalid (L1RXDB hold time)                         | 13.00    | —                     | ns         |  |

| 78  | L1CLKB edge to L1ST1 and L1ST2 valid <sup>4</sup>                        | 10.00    | 45.00                 | ns         |  |

| 78A | L1SYNCB valid to L1ST1 and L1ST2 valid                                   | 10.00    | 45.00                 | ns         |  |

| 79  | L1CLKB edge to L1ST1 and L1ST2 invalid                                   | 10.00    | 45.00                 | ns         |  |

| 80  | L1CLKB edge to L1TXDB valid                                              | 10.00    | 55.00                 | ns         |  |

| 80A | L1TSYNCB valid to L1TXDB valid <sup>4</sup>                              | 10.00    | 55.00                 | ns         |  |

| 81  | L1CLKB edge to L1TXDB high impedance                                     | 0.00     | 42.00                 | ns         |  |

| 82  | L1RCLKB, L1TCLKB frequency (DSC =1)                                      | —        | 16.00 or<br>SYNCCLK/2 | MHz        |  |

| 83  | L1RCLKB, L1TCLKB width low (DSC =1)                                      | P + 10   | —                     | ns         |  |

| 83a | L1RCLKB, L1TCLKB width high (DSC = $1$ ) <sup>3</sup>                    | P + 10   | —                     | ns         |  |

| 84  | L1CLKB edge to L1CLKOB valid (DSC = 1)                                   | —        | 30.00                 | ns         |  |

| 85  | L1RQB valid before falling edge of L1TSYNCB <sup>4</sup>                 | 1.00     | _                     | L1TC<br>LK |  |

| 86  | L1GRB setup time <sup>2</sup>                                            | 42.00    | —                     | ns         |  |

| 87  | L1GRB hold time                                                          | 42.00    | —                     | ns         |  |

| 88  | L1CLKB edge to L1SYNCB valid (FSD = 00) CNT = 0000, BYT = 0,<br>DSC = 0) | —        | 0.00                  | ns         |  |

### Table 20. SI Timing (continued)

<sup>1</sup> The ratio SyncCLK/L1RCLKB must be greater than 2.5/1.

<sup>2</sup> These specs are valid for IDL mode only.

$^3~$  Where P = 1/CLKOUT. Thus for a 25-MHz CLKO1 rate, P = 40 ns.

<sup>4</sup> These strobes and TxD on the first bit of the frame become valid after L1CLKB edge or L1SYNCB, whichever comes later.

**CPM Electrical Characteristics**

Figure 47. SI Receive Timing with Double-Speed Clocking (DSC = 1)

#### **CPM Electrical Characteristics**

MPC853T Hardware Specification, Rev. 1

## **13.6 SCC in NMSI Mode Electrical Specifications**

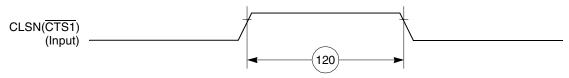

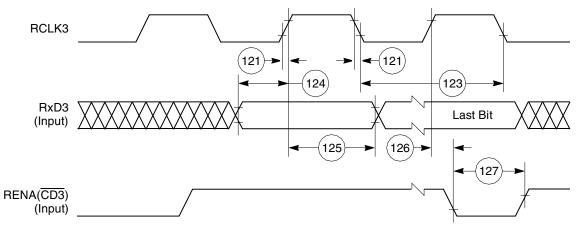

Table 21 provides the NMSI external clock timing.

| Num | Characteristic                                       | All Frequencie | Unit  |      |

|-----|------------------------------------------------------|----------------|-------|------|

| num | Characteristic                                       | Min            | Max   | Unit |

| 100 | RCLK3 and TCLK3 width high <sup>1</sup>              | 1/SYNCCLK      | —     | ns   |

| 101 | RCLK3 and TCLK3 width low                            | 1/SYNCCLK +5   | —     | ns   |

| 102 | RCLK3 and TCLK3 rise/fall time                       | —              | 15.00 | ns   |

| 103 | TXD3 active delay (from TCLK3 falling edge)          | 0.00           | 50.00 | ns   |

| 104 | RTS3 active/inactive delay (from TCLK3 falling edge) | 0.00           | 50.00 | ns   |

| 105 | CTS3 setup time to TCLK3 rising edge                 | 5.00           | _     | ns   |

| 106 | RXD3 setup time to RCLK3 rising edge                 | 5.00           | _     | ns   |

| 107 | RXD3 hold time from RCLK3 rising edge <sup>2</sup>   | 5.00           | _     | ns   |

| 108 | CD3 setup Time to RCLK3 rising edge                  | 5.00           | _     | ns   |

### Table 21. NMSI External Clock Timing

<sup>1</sup> The ratios SyncCLK/RCLK3 and SyncCLK/TCLK3 must be greater than or equal to 2.25/1.

<sup>2</sup> Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as external sync signals.

Table 22 provides the NMSI internal clock timing.

### Table 22. NMSI Internal Clock Timing

| Num   | Characteristic                                       | A     | Unit      |      |

|-------|------------------------------------------------------|-------|-----------|------|

| Nulli | Characteristic                                       | Min   | Мах       | Onit |

| 100   | RCLK3 and TCLK3 frequency <sup>1</sup>               | 0.00  | SYNCCLK/3 | MHz  |

| 102   | RCLK3 and TCLK3 rise/fall time                       | —     | _         | ns   |

| 103   | TXD3 active delay (from TCLK3 falling edge)          | 0.00  | 30.00     | ns   |

| 104   | RTS3 active/inactive delay (from TCLK3 falling edge) | 0.00  | 30.00     | ns   |

| 105   | CTS3 setup time to TCLK3 rising edge                 | 40.00 | _         | ns   |

| 106   | RXD3 setup time to RCLK3 rising edge                 | 40.00 | _         | ns   |

| 107   | RXD3 hold time from RCLK3 rising edge <sup>2</sup>   | 0.00  | _         | ns   |

| 108   | CD3 setup time to RCLK3 rising edge                  | 40.00 | _         | ns   |

<sup>1</sup> The ratios SyncCLK/RCLK3 and SyncCLK/TCLK3 must be greater than or equal to 3/1.

<sup>2</sup> Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as external sync signals.

#### **CPM Electrical Characteristics**

| Num | Chavastavistis                                 | All Freq | Unit |     |

|-----|------------------------------------------------|----------|------|-----|

|     | Characteristic                                 |          |      | Max |

| 134 | TENA inactive delay (from TCLK3 rising edge)   | 10       | 50   | ns  |

| 135 | RSTRT active delay (from TCLK3 falling edge)   | 10       | 50   | ns  |

| 136 | RSTRT inactive delay (from TCLK3 falling edge) | 10       | 50   | ns  |

| 137 | REJECT width low                               | 1        | —    | CLK |

| 138 | CLKO1 low to SDACK asserted <sup>2</sup>       | _        | 20   | ns  |

| 139 | CLKO1 low to SDACK negated <sup>2</sup>        | _        | 20   | ns  |

### Table 23. Ethernet Timing (continued)

$^1$  The ratios SyncCLK/RCLK3 and SyncCLK/TCLK3 must be greater than or equal to 2/1.

$^2$  SDACK is asserted whenever the SDMA writes the incoming frame DA into memory.

Figure 54. Ethernet Collision Timing Diagram

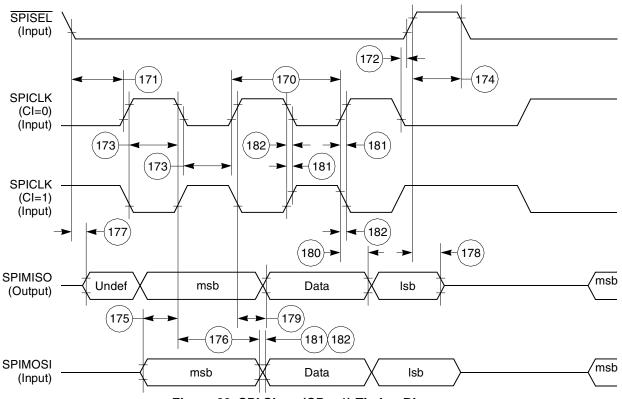

Figure 62. SPI Slave (CP = 1) Timing Diagram

## **14 FEC Electrical Characteristics**

This section provides the AC electrical specifications for the Fast Ethernet controller (FEC). Note that the timing specifications for the MII signals are independent of system clock frequency (part speed designation). Also, MII signals use TTL signal levels compatible with devices operating at either 5.0 V or 3.3 V.

## 14.1 MII Receive Signal Timing (MII\_RXD[3:0], MII\_RX\_DV, MII\_RX\_ER, MII\_RX\_CLK)

The receiver functions correctly up to a MII\_RX\_CLK maximum frequency of 25MHz + 1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII\_RX\_CLK frequency - 1%.

Table 26 provides information on the MII receive signal timing.

| Num | Characteristic                                         | Min | Max | Unit              |

|-----|--------------------------------------------------------|-----|-----|-------------------|

| M1  | MII_RXD[3:0], MII_RX_DV, MII_RX_ER to MII_RX_CLK setup | 5   | _   | ns                |

| M2  | MII_RX_CLK to MII_RXD[3:0], MII_RX_DV, MII_RX_ER hold  | 5   | _   | ns                |

| M3  | MII_RX_CLK pulse width high                            | 35% | 65% | MII_RX_CLK period |

| M4  | MII_RX_CLK pulse width low                             | 35% | 65% | MII_RX_CLK period |

| Table 26. | MII | Receive | Signal | Timing |

|-----------|-----|---------|--------|--------|

|-----------|-----|---------|--------|--------|

| Name                      | Pin Number | Туре                           |

|---------------------------|------------|--------------------------------|

| PC12<br>RTS4<br>L1ST4     | E15        | Bidirectional<br>(5V tolerant) |

| PC7<br>L1TSYNCB<br>CTS3   | J14        | Bidirectional<br>(5V tolerant) |

| PC6<br>L1RSYNCB<br>CD3    | K15        | Bidirectional<br>(5V tolerant) |

| PC5<br>CTS4<br>SDACK1     | J13        | Bidirectional<br>(5V tolerant) |

| PC4<br>CD4                | L14        | Bidirectional<br>(5V tolerant) |

| PD15<br>MII-RXD3          | M14        | Bidirectional<br>(5V tolerant) |

| PD14<br>MII-RXD2          | N16        | Bidirectional<br>(5V tolerant) |

| PD13<br>MII-RXD1          | К13        | Bidirectional<br>(5V tolerant) |

| PD12<br>MII-MDC           | N15        | Bidirectional<br>(5V tolerant) |

| PD11<br>RXD3<br>MII-TXERR | P16        | Bidirectional<br>(5V tolerant) |

| PD10<br>TXD3<br>MII-RXD0  | R15        | Bidirectional<br>(5V tolerant) |

| PD9<br>RXD4<br>MII-TXD0   | N14        | Bidirectional<br>(5V tolerant) |

| PD8<br>TXD4<br>MII_RX_CLK | M13        | Bidirectional<br>(5V tolerant) |

| PD7<br>RTS3<br>MII_RX_ER  | T15        | Bidirectional<br>(5V tolerant) |

| PD6<br>RTS4<br>MII_RX_DV  | N13        | Bidirectional<br>(5V tolerant) |

| Table 31. Pin Assignments - JEDEC Standard | (continued) |

|--------------------------------------------|-------------|

|--------------------------------------------|-------------|

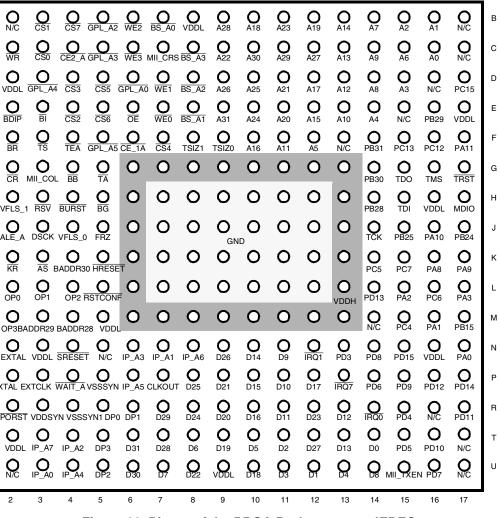

NOTE: This is the top view of the device.

Figure 68. Pinout of the PBGA Package—non-JEDEC

Table 32 contains a list of the MPC853T input and output signals and shows multiplexing and pin assignments.

| Table 32. | Pin | Assignments- | -Non-JEDEC |

|-----------|-----|--------------|------------|

|-----------|-----|--------------|------------|

| Name         | Pin Number                                                                                                                                                 | Туре                                      |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| A[0:31]      | C16, B16, B15, D15, E14, F12, C15, B14, D14, C14, E13, F11, D13, C13, B13, E12, F10, D12, B10, B12, E11, D11, C9, B11, E10, D10, D9, C12, B9, C11, C10, E9 | Bidirectional<br>Three-state (3.3 V only) |

| TSIZ0<br>REG | F9                                                                                                                                                         | Bidirectional<br>Three-state (3.3 V only) |

| TSIZ1        | F8                                                                                                                                                         | Bidirectional<br>Three-state (3.3 V only) |

| RD/WR        | C2                                                                                                                                                         | Bidirectional<br>Three-state (3.3 V only) |