#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 25                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                |                                                                          |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 11x8b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

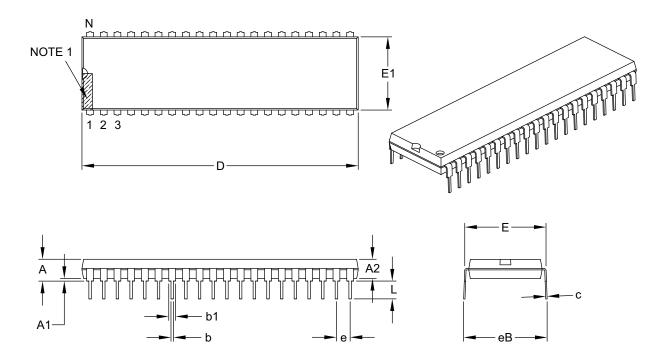

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f722-e-sp |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC16(L)F72X Family Types

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data SRAM<br>(bytes) | High-Endurance Flash<br>Memory (bytes) | I/O's <sup>(2)</sup> | 8-bit ADC (ch) | CapSense (ch) | Timers<br>(8/16-bit) | AUSART | SSP (I <sup>2</sup> C/SPI) | ССР | Debug <sup>(1)</sup> | ХГР |

|---------------|------------------|---------------------------------|----------------------|----------------------------------------|----------------------|----------------|---------------|----------------------|--------|----------------------------|-----|----------------------|-----|

| PIC16(L)F707  | (1)              | 8192                            | 363                  | 0                                      | 36                   | 14             | 32            | 4/2                  | 1      | 1                          | 2   |                      | Y   |

| PIC16(L)F720  | (2)              | 2048                            | 128                  | 128                                    | 18                   | 12             | _             | 2/1                  | 1      | 1                          | 1   | I                    | Y   |

| PIC16(L)F721  | (2)              | 4096                            | 256                  | 128                                    | 18                   | 12             | _             | 2/1                  | 1      | 1                          | 1   | I                    | Y   |

| PIC16(L)F722  | (4)              | 2048                            | 128                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | -                    | Y   |

| PIC16(L)F722A | (3)              | 2048                            | 128                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

| PIC16(L)F723  | (4)              | 4096                            | 192                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | Ι                    | Y   |

| PIC16(L)F723A | (3)              | 4096                            | 192                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | -                    | Y   |

| PIC16(L)F724  | (4)              | 4096                            | 192                  | 0                                      | 36                   | 14             | 16            | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

| PIC16(L)F726  | (4)              | 8192                            | 368                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | Ι                    | Y   |

| PIC16(L)F727  | (4)              | 8192                            | 368                  | 0                                      | 36                   | 14             | 16            | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

**Note 1:** I - Debugging, Integrated on Chip; H - Debugging, Requires Debug Header.

2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

- 1: DS41418 PIC16(L)F707 Data Sheet, 40/44-Pin Flash, 8-bit Microcontrollers

- 2: DS41430 PIC16(L)F720/721 Data Sheet, 20-Pin Flash, 8-bit Microcontrollers

- 3: DS41417 PIC16(L)F722A/723A Data Sheet, 28-Pin Flash, 8-bit Microcontrollers

- 4: DS41341 PIC16(L)F72X Data Sheet, 28/40/44-Pin Flash, 8-bit Microcontrollers

| Name               | Function | Input<br>Type    | Output<br>Type | Description                                                                                          |

|--------------------|----------|------------------|----------------|------------------------------------------------------------------------------------------------------|

| RB4/AN11/CPS4      | RB4      | TTL              | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |

|                    | AN11     | AN               | _              | A/D Channel 11 input.                                                                                |

|                    | CPS4     | AN               | _              | Capacitive sensing input 4.                                                                          |

| RB5/AN13/CPS5/T1G  | RB5      | TTL              | CMOS           | General purpose I/O. Individually controlled inter-                                                  |

|                    |          |                  | CIVIOS         | rupt-on-change. Individually enabled pull-up.                                                        |

|                    | AN13     | AN               | —              | A/D Channel 13 input.                                                                                |

|                    | CPS5     | AN               | —              | Capacitive sensing input 5.                                                                          |

|                    | T1G      | ST               | —              | Timer1 Gate input.                                                                                   |

| RB6/ICSPCLK/ICDCLK | RB6      | TTL              | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |

|                    | ICSPCLK  | ST               | _              | Serial Programming Clock.                                                                            |

|                    | ICDCLK   | ST               | _              | In-Circuit Debug Clock.                                                                              |

| RB7/ICSPDAT/ICDDAT | RB7      | TTL              | CMOS           | General purpose I/O. Individually controlled inter-                                                  |

|                    |          |                  |                | rupt-on-change. Individually enabled pull-up.                                                        |

|                    | ICSPDAT  | ST               | CMOS           | ICSP™ Data I/O.                                                                                      |

|                    | ICDDAT   | ST               | —              | In-Circuit Data I/O.                                                                                 |

| RC0/T1OSO/T1CKI    | RC0      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | T1OSO    | XTAL             | XTAL           | Timer1 oscillator connection.                                                                        |

|                    | T1CKI    | ST               | _              | Timer1 clock input.                                                                                  |

| RC1/T1OSI/CCP2     | RC1      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | T10SI    | XTAL             | XTAL           | Timer1 oscillator connection.                                                                        |

|                    | CCP2     | ST               | CMOS           | Capture/Compare/PWM2.                                                                                |

| RC2/CCP1           | RC2      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | CCP1     | ST               | CMOS           | Capture/Compare/PWM1.                                                                                |

| RC3/SCK/SCL        | RC3      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | SCK      | ST               | CMOS           | SPI clock.                                                                                           |

|                    | SCL      | l <sup>2</sup> C | OD             | I <sup>2</sup> C clock.                                                                              |

| RC4/SDI/SDA        | RC4      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | SDI      | ST               | _              | SPI data input.                                                                                      |

|                    | SDA      | l <sup>2</sup> C | OD             | I <sup>2</sup> C data input/output.                                                                  |

| RC5/SDO            | RC5      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | SDO      | _                | CMOS           | SPI data output.                                                                                     |

| RC6/TX/CK          | RC6      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | ТХ       | _                | CMOS           | USART asynchronous transmit.                                                                         |

|                    | СК       | ST               | CMOS           | USART synchronous clock.                                                                             |

| RC7/RX/DT          | RC7      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | RX       | ST               | _              | USART asynchronous input.                                                                            |

|                    | DT       | ST               | CMOS           | USART synchronous data.                                                                              |

| RD0/CPS8           | RD0      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | CPS8     | AN               | _              | Capacitive sensing input 8.                                                                          |

| RD1/CPS9           | RD1      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | CPS9     | AN               |                | Capacitive sensing input 9.                                                                          |

| RD2/CPS10          | RD2      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    |          |                  |                |                                                                                                      |

| TABLE 1-1: | PIC16(L)F722/3/4/6/7 PINOUT DESCRIPTION (CONTINUED) |

|------------|-----------------------------------------------------|

| IABLE 1-1: | PIC16(L)F/22/3/4/6/7 PINOUT DESCRIPTION (CONTINUED) |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output

XTAL = Crystal levels HV = High Voltage

| Name                                                                      | Function | Input<br>Type | Output<br>Type | Description                                                                                              |  |  |

|---------------------------------------------------------------------------|----------|---------------|----------------|----------------------------------------------------------------------------------------------------------|--|--|

| RD3/CPS11                                                                 | RD3      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | CPS11    | AN            | —              | Capacitive sensing input 11.                                                                             |  |  |

| RD4/CPS12                                                                 | RD4      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | CPS12    | AN            | —              | Capacitive sensing input 12.                                                                             |  |  |

| RD5/CPS13                                                                 | RD5      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | CPS13    | AN            | —              | Capacitive sensing input 13.                                                                             |  |  |

| RD6/CPS14                                                                 | RD6      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | CPS14    | AN            | _              | Capacitive sensing input 14.                                                                             |  |  |

| RD7/CPS15                                                                 | RD7      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | CPS15    | AN            | _              | Capacitive sensing input 15.                                                                             |  |  |

| RE0/AN5                                                                   | RE0      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | AN5      | AN            | —              | A/D Channel 5 input.                                                                                     |  |  |

| RE1/AN6                                                                   | RE1      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | AN6      | AN            | —              | A/D Channel 6 input.                                                                                     |  |  |

| RE2/AN7                                                                   | RE2      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | AN7      | AN            | _              | A/D Channel 7 input.                                                                                     |  |  |

| RE3/MCLR/Vpp                                                              | RE3      | TTL           | —              | General purpose input.                                                                                   |  |  |

|                                                                           | MCLR     | ST            | _              | Master Clear with internal pull-up.                                                                      |  |  |

|                                                                           | Vpp      | ΗV            | —              | Programming voltage.                                                                                     |  |  |

| VDD                                                                       | Vdd      | Power         | —              | Positive supply.                                                                                         |  |  |

| Vss                                                                       | Vss      | Power         | _              | Ground reference.                                                                                        |  |  |

| Legend: AN = Analog input or<br>TTL = TTL compatible<br>HV = High Voltage | input ST |               | nitt Trigger   | ble input or output OD = Open Drain<br>input with CMOS levels $I^2C$ = Schmitt Trigger input with $I^2C$ |  |  |

#### TABLE 1-1: PIC16(L)F722/3/4/6/7 PINOUT DESCRIPTION (CONTINUED)

**Note:** The PIC16F722/3/4/6/7 devices have an internal low dropout voltage regulator. An external capacitor must be connected to one of the available VCAP pins to stabilize the regulator. For more information, see **Section 5.0 "Low Dropout (LDO) Voltage Regulator**". The PIC16LF722/3/4/6/7 devices do not have the voltage regulator and therefore no external capacitor is required.

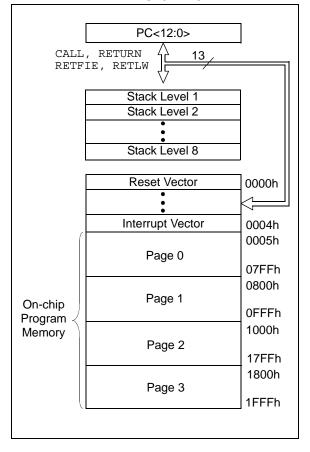

## FIGURE 2-3:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16F726/LF726 AND PIC16F727/LF727

# 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers (GPRs) and the Special Function Registers (SFRs). Bits RP0 and RP1 are bank select bits.

| <u>RP1</u> | <u>RP0</u> |

|------------|------------|

|            |            |

| 0 | 0 | $\rightarrow$ | Bank 0 is selected |

|---|---|---------------|--------------------|

| 0 | 1 | $\rightarrow$ | Bank 1 is selected |

| 1 | 0 | $\rightarrow$ | Bank 2 is selected |

| 1 | 1 | $\rightarrow$ | Bank 3 is selected |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are the General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank are mirrored in another bank for code reduction and quicker access.

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 128 x 8 bits in the PIC16F722/LF722, 192 x 8 bits in the PIC16F723/LF723 and PIC16F724/LF724, and 368 x 8 bits in the PIC16F726/LF726 and PIC16F727/LF727. Each register is accessed either directly or indirectly through the File Select Register (FSR), (Refer to **Section 2.5** "Indirect Addressing, INDF and FSR Registers").

# 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (refer to Table 2-1). These registers are static RAM.

The Special Function Registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the "core" are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| FIGURE 2-5: | PIC16F723/LF723 AND PIC16F724/LF724 SPECIAL FUNCTION REGISTERS |

|-------------|----------------------------------------------------------------|

|             |                                                                |

| Indirect addr. <sup>(*)</sup> | 00h     | Indirect addr. <sup>(*)</sup>   | 80h    | Indirect addr. <sup>(*)</sup>           | 100h         | Indirect addr.(*)     | 180h |

|-------------------------------|---------|---------------------------------|--------|-----------------------------------------|--------------|-----------------------|------|

| TMR0                          | 01h     | OPTION                          | 81h    | TMR0                                    | 101h         | OPTION                | 181h |

| PCL                           | 02h     | PCL                             | 82h    | PCL                                     | 102h         | PCL                   | 182h |

| STATUS                        | 03h     | STATUS                          | 83h    | STATUS                                  | 103h         | STATUS                | 183h |

| FSR                           | 04h     | FSR                             | 84h    | FSR                                     | 104h         | FSR                   | 184h |

| PORTA                         | 05h     | TRISA                           | 85h    |                                         | 105h         | ANSELA                | 185h |

| PORTB                         | 06h     | TRISB                           | 86h    |                                         | 106h         | ANSELB                | 186h |

| PORTC                         | 07h     | TRISC                           | 87h    |                                         | 107h         |                       | 187h |

| PORTD <sup>(1)</sup>          | 08h     | TRISD <sup>(1)</sup>            | 88h    | CPSCON0                                 | 108h         | ANSELD <sup>(1)</sup> | 188h |

| PORTE                         | 09h     | TRISE                           | 89h    | CPSCON1                                 | 109h         | ANSELE <sup>(1)</sup> | 189h |

| PCLATH                        | 0Ah     | PCLATH                          | 8Ah    | PCLATH                                  | 10Ah         | PCLATH                | 18Ah |

| INTCON                        | 0Bh     | INTCON                          | 8Bh    | INTCON                                  | 10Bh         | INTCON                | 18Bh |

| PIR1                          | 0Ch     | PIE1                            | 8Ch    | PMDATL                                  | 10Ch         | PMCON1                | 18Ch |

| PIR2                          | 0Dh     | PIE2                            | 8Dh    | PMADRL                                  | 10Dh         | Reserved              | 18Dh |

| TMR1L                         | 0Eh     | PCON                            | 8Eh    | PMDATH                                  | 10Eh         | Reserved              | 18Eh |

| TMR1H                         | 0Fh     | T1GCON                          | 8Fh    | PMADRH                                  | 10Fh         | Reserved              | 18Fh |

| T1CON                         | 10h     | OSCCON                          | 90h    |                                         | 110h         |                       | 190h |

| TMR2                          | 11h     | OSCTUNE                         | 91h    |                                         | 111h         |                       | 191h |

| T2CON                         | 12h     | PR2                             | 92h    |                                         | 112h         |                       | 192h |

| SSPBUF                        | 13h     | SSPADD/SSPMSK                   | 93h    |                                         | 113h         |                       | 193h |

| SSPCON                        | 14h     | SSPSTAT                         | 94h    |                                         | 114h         |                       | 194h |

| CCPR1L                        | 15h     | WPUB                            | 95h    |                                         | 115h         |                       | 195h |

| CCPR1H                        | 16h     | IOCB                            | 96h    | -                                       | 116h         |                       | 196h |

| CCP1CON                       | 17h     |                                 | 97h    | -                                       | 117h         |                       | 197h |

| RCSTA                         | 18h     | TXSTA                           | 98h    | -                                       | 118h         |                       | 198h |

| TXREG                         | 19h     | SPBRG                           | 99h    |                                         | 119h         |                       | 199h |

| RCREG                         | 1Ah     |                                 | 9Ah    |                                         | 11Ah         |                       | 19Ah |

| CCPR2L                        | 1Bh     |                                 | 9Bh    |                                         | 11Bh         |                       | 19Bh |

| CCPR2H                        | 1Ch     | APFCON                          | 9Ch    |                                         | 11Ch         |                       | 19Ch |

| CCP2CON                       | 1Dh     | FVRCON                          | 9Dh    |                                         | 11Dh         |                       | 19Dh |

| ADRES                         | 1Eh     |                                 | 9Eh    |                                         | 11Eh         |                       | 19Eh |

| ADCON0                        | 1Fh     | ADCON1                          | 9Fh    |                                         | 11Fh         |                       | 19Fh |

|                               | 20h     | General                         | A0h    | General Purpose<br>Register             | 120h         |                       | 1A0h |

| General<br>Purpose            |         | Purpose<br>Register<br>80 Bytes |        | 16 Bytes                                | 12Fh<br>130h |                       |      |

| Register                      |         |                                 | EFh    |                                         | 16Fh         |                       | 1EFh |

| 96 Bytes                      |         | Accesses<br>70h-7Fh             | F0h    | Accesses<br>70h-7Fh                     | 170h         | Accesses<br>70h-7Fh   | 1F0h |

|                               | 7Fh     | 701-7111                        | FFh    | / ///////////////////////////////////// | 17Fh         | 701-7111              | 1FFh |

| Bank 0                        | ],      | Bank 1                          | l      | Bank 2                                  | ]            | Bank 3                | J    |

| nd: = Unimple                 | emented | data memory locatio             | ns rea | d as '0'                                |              |                       |      |

| Address               | Name    | Bit 7        | Bit 6                                                                       | Bit 5         | Bit 4           | Bit 3         | Bit 2              | Bit 1              | Bit 0              | Value on:<br>POR, BOR | Page   |

|-----------------------|---------|--------------|-----------------------------------------------------------------------------|---------------|-----------------|---------------|--------------------|--------------------|--------------------|-----------------------|--------|

| Bank 0                |         |              |                                                                             |               |                 |               |                    |                    |                    |                       |        |

| 00h <sup>(2)</sup>    | INDF    | Addressing   | this location                                                               | gister)       | xxxx xxxx       | 29,37         |                    |                    |                    |                       |        |

| 01h                   | TMR0    | Timer0 Mod   | ule Register                                                                |               |                 |               |                    |                    |                    | xxxx xxxx             | 105,37 |

| 02h <sup>(2)</sup>    | PCL     | Program Co   | ounter (PC) L                                                               | east Signific | ant Byte        |               |                    |                    |                    | 0000 0000             | 28,37  |

| 03h <sup>(2)</sup>    | STATUS  | IRP          | RP1                                                                         | RP0           | TO              | PD            | Z                  | DC                 | С                  | 0001 1xxx             | 25,37  |

| 04h <sup>(2)</sup>    | FSR     | Indirect Dat | a Memory Ad                                                                 | dress Point   | er              |               |                    |                    |                    | xxxx xxxx             | 29,37  |

| 05h                   | PORTA   | RA7          | RA6                                                                         | RA5           | RA4             | RA3           | RA2                | RA1                | RA0                | xxxx xxxx             | 51,37  |

| 06h                   | PORTB   | RB7          | RB6                                                                         | RB5           | RB4             | RB3           | RB2                | RB1                | RB0                | xxxx xxxx             | 60,37  |

| 07h                   | PORTC   | RC7          | RC6                                                                         | RC5           | RC4             | RC3           | RC2                | RC1                | RC0                | XXXX XXXX             | 70,37  |

| 08h <sup>(3)</sup>    | PORTD   | RD7          | RD6                                                                         | RD5           | RD4             | RD3           | RD2                | RD1                | RD0                | XXXX XXXX             | 77,37  |

| 09h                   | PORTE   | —            | _                                                                           | _             | _               | RE3           | RE2 <sup>(3)</sup> | RE1 <sup>(3)</sup> | RE0 <sup>(3)</sup> | xxxx                  | 81,37  |

| 0Ah <sup>(1, 2)</sup> | PCLATH  | —            | _                                                                           | _             | Write Buffer    | for the upper | 5 bits of the F    | Program Cou        | nter               | 0 0000                | 28,37  |

| 0Bh <b>(2)</b>        | INTCON  | GIE          | PEIE                                                                        | T0IE          | INTE            | RBIE          | T0IF               | INTF               | RBIF               | 0000 000x             | 44,37  |

| 0Ch                   | PIR1    | TMR1GIF      | ADIF                                                                        | RCIF          | TXIF            | SSPIF         | CCP1IF             | TMR2IF             | TMR1IF             | 0000 0000             | 47,37  |

| 0Dh                   | PIR2    | —            | _                                                                           | _             | _               | _             | _                  | _                  | CCP2IF             | 0                     | 48,37  |

| 0Eh                   | TMR1L   | Holding Reg  | lolding Register for the Least Significant Byte of the 16-bit TMR1 Register |               |                 |               |                    |                    |                    |                       |        |

| 0Fh                   | TMR1H   | Holding Reg  | gister for the                                                              | Most Signific | cant Byte of th | ne 16-bit TMR | R1 Register        |                    |                    | XXXX XXXX             | 113,37 |

| 10h                   | T1CON   | TMR1CS1      | TMR1CS0                                                                     | T1CKPS1       | T1CKPS0         | T1OSCEN       | T1SYNC             | _                  | TMR10N             | 0000 00-0             | 117,37 |

| 11h                   | TMR2    | Timer2 Mod   | ule Register                                                                |               |                 |               |                    |                    |                    | 0000 0000             | 120,37 |

| 12h                   | T2CON   | —            | TOUTPS3                                                                     | TOUTPS2       | TOUTPS1         | TOUTPS0       | TMR2ON             | T2CKPS1            | T2CKPS0            | -000 0000             | 121,37 |

| 13h                   | SSPBUF  | Synchronou   | s Serial Port                                                               | Receive Bu    | ffer/Transmit   | Register      |                    |                    |                    | xxxx xxxx             | 161,37 |

| 14h                   | SSPCON  | WCOL         | SSPOV                                                                       | SSPEN         | CKP             | SSPM3         | SSPM2              | SSPM1              | SSPM0              | 0000 0000             | 178,37 |

| 15h                   | CCPR1L  | Capture/Co   | mpare/PWM                                                                   | Register (L   | SB)             |               |                    |                    |                    | xxxx xxxx             | 130,37 |

| 16h                   | CCPR1H  | Capture/Co   | mpare/PWM                                                                   | Register (M   | SB)             |               |                    |                    |                    | xxxx xxxx             | 130,37 |

| 17h                   | CCP1CON | —            | —                                                                           | DC1B1         | DC1B0           | CCP1M3        | CCP1M2             | CCP1M1             | CCP1M0             | 00 0000               | 129,37 |

| 18h                   | RCSTA   | SPEN         | RX9                                                                         | SREN          | CREN            | ADDEN         | FERR               | OERR               | RX9D               | 0000 000x             | 148,37 |

| 19h                   | TXREG   | USART Tra    | nsmit Data R                                                                | egister       | •               |               | •                  |                    | •                  | 0000 0000             | 147,37 |

| 1Ah                   | RCREG   | USART Red    | eive Data R                                                                 | egister       |                 |               |                    |                    |                    | 0000 0000             | 145,37 |

| 1Bh                   | CCPR2L  | Capture/Co   | mpare/PWM                                                                   | Register 2 (  | LSB)            |               |                    |                    |                    | xxxx xxxx             | 130,37 |

| 1Ch                   | CCPR2H  | Capture/Co   | mpare/PWM                                                                   | Register 2 (  | MSB)            |               |                    |                    |                    | xxxx xxxx             | 130,37 |

| 1Dh                   | CCP2CON | _            | —                                                                           | DC2B1         | DC2B0           | CCP2M3        | CCP2M2             | CCP2M1             | CCP2M0             | 00 0000               | 129,37 |

| 1Eh                   | ADRES   | A/D Result   | Register                                                                    |               |                 |               |                    |                    | •                  | xxxx xxxx             | 100,37 |

| 1Fh                   | ADCON0  | _            | _                                                                           | CHS3          | CHS2            | CHS1          | CHS0               | GO/DONE            | ADON               | 00 0000               | 99,37  |

#### **TABLE 2-1:** PIC16(L)F722/3/4/6/7 SPECIAL FUNCTION REGISTER SUMMARY

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter. These registers can be addressed from any bank. These registers/bits are not implemented on PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'. Accessible only when SSPM<3:0> = 1001. Accessible only when SSPM<3:0>  $\neq$  1001. This bit is always '1' as RE3 is input-only. Note 1:

2:

3:

4:

5:

6:

#### 2.2.2.2 OPTION register

The OPTION register, shown in Register 2-2, is a readable and writable register, which contains various control bits to configure:

- Timer0/WDT prescaler

- External RB0/INT interrupt

- Timer0

- Weak pull-ups on PORTB

| Note: | To achieve a 1:1 prescaler assignment for |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|

|       | Timer0, assign the prescaler to the WDT   |  |  |  |  |  |  |  |  |

|       | by setting the PSA bit of the             |  |  |  |  |  |  |  |  |

|       | OPTION_REG register to '1'. Refer to      |  |  |  |  |  |  |  |  |

|       | Section 11.1.3 "Software                  |  |  |  |  |  |  |  |  |

|       | Programmable Prescaler".                  |  |  |  |  |  |  |  |  |

# REGISTER 2-2: OPTION\_REG: OPTION REGISTER

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 7   | <b>RBPU:</b> PORTB Pull-up Enable bit<br>1 = PORTB pull-ups are disabled<br>0 = PORTB pull-ups are enabled by individual bits in the WPUB register                                                                             |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| bit 6   | INTEDG: Interrupt Edge Select bit<br>1 = Interrupt on rising edge of RB0/INT pin<br>0 = Interrupt on falling edge of RB0/INT pin                                                                                               |  |  |  |  |  |

| bit 5   | <b>T0CS:</b> Timer0 Clock Source Select bit<br>1 = Transition on RA4/T0CKI pin<br>0 = Internal instruction cycle clock (Fosc/4)                                                                                                |  |  |  |  |  |

| bit 4   | <b>T0SE:</b> Timer0 Source Edge Select bit<br>1 = Increment on high-to-low transition on RA4/T0CKI pin<br>0 = Increment on low-to-high transition on RA4/T0CKI pin                                                             |  |  |  |  |  |

| bit 3   | <b>PSA:</b> Prescaler Assignment bit<br>1 = Prescaler is assigned to the WDT<br>0 = Prescaler is assigned to the Timer0 module                                                                                                 |  |  |  |  |  |

| bit 2-0 | PS<2:0>: Prescaler Rate Select bits                                                                                                                                                                                            |  |  |  |  |  |

|         | Bit Value Timer0 Rate WDT Rate                                                                                                                                                                                                 |  |  |  |  |  |

|         | 000         1:2         1:1           001         1:4         1:2           010         1:8         1:4           011         1:16         1:8           100         1:32         1:16           101         1:64         1:32 |  |  |  |  |  |

1:128

1:256

1:64

1 : 128

110

111

| Register              | Address | Power-on Reset/<br>Brown-out Reset <sup>(1)</sup> | MCLR Reset/<br>WDT Reset | Wake-up from Sleep through<br>Interrupt/Time out |

|-----------------------|---------|---------------------------------------------------|--------------------------|--------------------------------------------------|

| PCON                  | 8Eh     | dd                                                |                          | uu                                               |

| T1GCON                | 8Fh     | 0000 0x00                                         | uuuu uxuu                | uuuu uxuu                                        |

| OSCCON                | 90h     | 10 qq                                             | 10 qq                    | uu qq                                            |

| OSCTUNE               | 91h     | 00 0000                                           | uu uuuu                  | uu uuuu                                          |

| PR2                   | 92h     | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |

| SSPADD                | 93h     | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |

| SSPMSK                | 93h     | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |

| SSPSTAT               | 94h     | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |

| WPUB                  | 95h     | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |

| IOCB                  | 96h     | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |

| TXSTA                 | 98h     | 0000 -010                                         | 0000 -010                | uuuu -uuu                                        |

| SPBRG                 | 99h     | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |

| APFCON                | 9Ch     | 00                                                | 00                       | uu                                               |

| FVRCON                | 9Dh     | q00000                                            | d00000                   | uuuuuu                                           |

| ADCON1                | 9Fh     | -00000                                            | -00000                   | -uuuuu                                           |

| CPSCON0               | 108h    | 0 0000                                            | 0 0000                   | u uuuu                                           |

| CPSCON1               | 109h    | 0000                                              | 0000                     | uuuu                                             |

| PMDATL                | 10Ch    | XXXX XXXX                                         | XXXX XXXX                | uuuu uuuu                                        |

| PMADRL                | 10Dh    | xxxx xxxx                                         | xxxx xxxx                | սսսս սսսս                                        |

| PMDATH                | 10Eh    | xx xxxx                                           | xx xxxx                  | uu uuuu                                          |

| PMADRH                | 10Fh    | x xxxx                                            | x xxxx                   | u uuuu                                           |

| ANSELA                | 185h    | 11 1111                                           | 11 1111                  | uu uuuu                                          |

| ANSELB                | 186h    | 11 1111                                           | 11 1111                  | uu uuuu                                          |

| ANSELD <sup>(6)</sup> | 188h    | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |

| ANSELE                | 189h    | 111                                               | 111                      | uuu                                              |

| PMCON1                | 18Ch    | 10                                                | 10                       | uu                                               |

#### TABLE 3-4: INITIALIZATION CONDITION FOR REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 and PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 3-5 for Reset value for specific condition.

5: If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

6: PIC16F724/727/PIC16LF724/727 only.

Note

#### 6.2.1 ANSELA REGISTER

The ANSELA register (Register 6-4) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

## REGISTER 6-4: ANSELA: PORTA ANALOG SELECT REGISTER

| U-0                               | U-0 | R/W-1            | R/W-1                              | R/W-1            | R/W-1 | R/W-1           | R/W-1 |  |

|-----------------------------------|-----|------------------|------------------------------------|------------------|-------|-----------------|-------|--|

| —                                 | —   | ANSA5            | ANSA4                              | ANSA3            | ANSA2 | ANSA1           | ANSA0 |  |

| bit 7 bit 0                       |     |                  |                                    |                  |       |                 |       |  |

|                                   |     |                  |                                    |                  |       |                 |       |  |

| Legend:                           |     |                  |                                    |                  |       |                 |       |  |

| R = Readable bit W = Writable bit |     |                  | U = Unimplemented bit, read as '0' |                  |       |                 |       |  |

| -n = Value at POR '1' = Bit       |     | '1' = Bit is set |                                    | '0' = Bit is cle | ared  | x = Bit is unki | nown  |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **ANSA<5:0>**: Analog Select between Analog or Digital Function on pins RA<5:0>, respectively 0 = Digital I/O. Pin is assigned to port or Digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital Input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

# 7.4 Oscillator Control

The Oscillator Control (OSCCON) register (Figure 7-1) displays the status and allows frequency selection of the internal oscillator (INTOSC) system clock. The OSCCON register contains the following bits:

- Frequency selection bits (IRCF)

- Status Locked bits (ICSL)

- Status Stable bits (ICSS)

#### REGISTER 7-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0     | U-0             | R/W-1 | R/W-0 | R-q  | R-q | U-0 | U-0   |

|---------|-----------------|-------|-------|------|-----|-----|-------|

|         | — — IRCF1 IRCF0 |       | ICSL  | ICSS | _   | —   |       |

| bit 7   |                 |       |       |      |     |     | bit 0 |

|         |                 |       |       |      |     |     |       |

| Legend: |                 |       |       |      |     |     |       |

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |

|-----------------------------------|------------------|-----------------------|------------------------------------|--|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |

| q = Value depends on condition    |                  |                       |                                    |  |  |  |

| bit 7-6 | Unimplemented: Read as '0'                                                               |

|---------|------------------------------------------------------------------------------------------|

| bit 5-4 | IRCF<1:0>: Internal Oscillator Frequency Select bits                                     |

|         | <u>When PLLEN = 1 (16 MHz INTOSC)</u>                                                    |

|         | 11 = 16 MHz                                                                              |

|         | 10 = 8 MHz (POR value)                                                                   |

|         | 01 = 4  MHz                                                                              |

|         | 00 = 2 MHz                                                                               |

|         | <u>When PLLEN = <math>0</math> (500 kHz INTOSC)</u>                                      |

|         | 11 = 500 kHz                                                                             |

|         | 10 = 250 kHz (POR value)<br>01 = 125 kHz                                                 |

|         | 01 = 125  kHz<br>00 = 62.5  kHz                                                          |

|         |                                                                                          |

| bit 3   | ICSL: Internal Clock Oscillator Status Locked bit (2% Stable)                            |

|         | 1 = 16 MHz/500 kHz Internal Oscillator (HFIOSC) is in lock                               |

|         | 0 = 16 MHz/500 kHz Internal Oscillator (HFIOSC) has not yet locked                       |

| bit 2   | ICSS: Internal Clock Oscillator Status Stable bit (0.5% Stable)                          |

|         | 1 = 16 MHz/500 kHz Internal Oscillator (HFIOSC) has stabilized to its maximum accuracy   |

|         | 0 = 16 MHz/500 kHz Internal Oscillator (HFIOSC) has not yet reached its maximum accuracy |

| bit 1-0 | Unimplemented: Read as '0'                                                               |

|         | -                                                                                        |

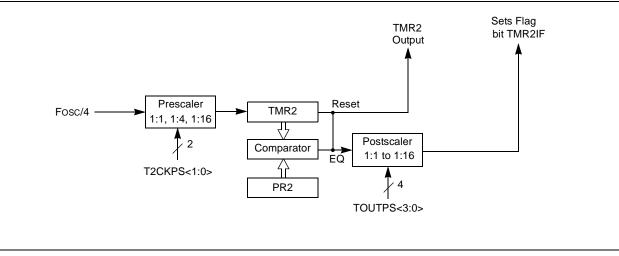

# 13.0 TIMER2 MODULE

The Timer2 module is an 8-bit timer with the following features:

- 8-bit timer register (TMR2)

- 8-bit period register (PR2)

- Interrupt on TMR2 match with PR2

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

See Figure 13-1 for a block diagram of Timer2.

## 13.1 Timer2 Operation

The clock input to the Timer2 module is the system instruction clock (Fosc/4). The clock is fed into the Timer2 prescaler, which has prescale options of 1:1, 1:4 or 1:16. The output of the prescaler is then used to increment the TMR2 register.

The values of TMR2 and PR2 are constantly compared to determine when they match. TMR2 will increment from 00h until it matches the value in PR2. When a match occurs, two things happen:

- TMR2 is reset to 00h on the next increment cycle.

- The Timer2 postscaler is incremented.

The match output of the Timer2/PR2 comparator is then fed into the Timer2 postscaler. The postscaler has postscale options of 1:1 to 1:16 inclusive. The output of the Timer2 postscaler is used to set the TMR2IF interrupt flag bit in the PIR1 register.

#### FIGURE 13-1: TIMER2 BLOCK DIAGRAM

The TMR2 and PR2 registers are both fully readable and writable. On any Reset, the TMR2 register is set to 00h and the PR2 register is set to FFh.

Timer2 is turned on by setting the TMR2ON bit in the T2CON register to a '1'. Timer2 is turned off by clearing the TMR2ON bit to a '0'.

The Timer2 prescaler is controlled by the T2CKPS bits in the T2CON register. The Timer2 postscaler is controlled by the TOUTPS bits in the T2CON register. The prescaler and postscaler counters are cleared when:

- A write to TMR2 occurs.

- A write to T2CON occurs.

- Any device Reset occurs (Power-on Reset, MCLR Reset, Watchdog Timer Reset, or Brown-out Reset).

Note: TMR2 is not cleared when T2CON is written.

| R/W-0                                                                                                                                                                                 | U-0                                                | U-0                                                  | U-0                           | R/W-0                             | R/W-0                                                            | R-0             | R/W-0 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------|-------------------------------|-----------------------------------|------------------------------------------------------------------|-----------------|-------|

| CPSON                                                                                                                                                                                 | —                                                  | —                                                    | —                             | CPSRNG1                           | CPSRNG0                                                          | CPSOUT          | TOXCS |

| bit 7                                                                                                                                                                                 |                                                    |                                                      |                               |                                   |                                                                  |                 | bit 0 |

|                                                                                                                                                                                       |                                                    |                                                      |                               |                                   |                                                                  |                 |       |

| Legend:                                                                                                                                                                               |                                                    |                                                      |                               |                                   |                                                                  |                 |       |

| R = Readable I                                                                                                                                                                        | bit                                                | W = Writable I                                       | bit                           | U = Unimpler                      | mented bit, read                                                 | l as '0'        |       |

| -n = Value at P                                                                                                                                                                       | OR                                                 | '1' = Bit is set                                     |                               | '0' = Bit is cle                  | ared                                                             | x = Bit is unkn | own   |

| bit 7 <b>CPSON:</b> Capacitive Sensing Module Enable bit<br>1 = Capacitive sensing module is operating<br>0 = Capacitive sensing module is shut off and consumes no operating current |                                                    |                                                      |                               |                                   |                                                                  |                 |       |

| bit 6-4                                                                                                                                                                               | Unimplement                                        | ted: Read as '                                       | )'                            |                                   |                                                                  |                 |       |

| bit 3-2                                                                                                                                                                               | 00 = Oscillato<br>01 = Oscillato<br>10 = Oscillato | or is in low rang<br>or is in medium                 | e. Charge/dis<br>range. Charg | scharge curren<br>je/discharge cu | ts<br>t is nominally 0.<br>urrent is nomina<br>nt is nominally 1 | lly 1.2 μΑ.     |       |

| bit 1                                                                                                                                                                                 | 1 = Oscillator                                     | pacitive Sensin<br>is sourcing cu<br>is sinking curr | rrent (Current                | t flowing out the                 | • •                                                              |                 |       |

| bit 0                                                                                                                                                                                 |                                                    |                                                      |                               |                                   |                                                                  |                 |       |

# REGISTER 14-1: CPSCON0: CAPACITIVE SENSING CONTROL REGISTER 0

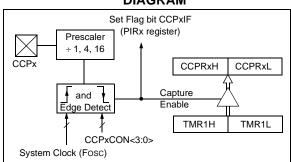

## 15.1 Capture Mode

In Capture mode, CCPRxH:CCPRxL captures the 16-bit value of the TMR1 register when an event occurs on pin CCPx. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value (refer to Figure 15-1).

#### 15.1.1 CCPx PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

Either RC1 or RB3 can be selected as the CCP2 pin. Refer to **Section 6.1** "Alternate Pin Function" for more information.

**Note:** If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

#### FIGURE 15-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

# 15.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode or when Timer1 is clocked at Fosc, the capture operation may not work.

#### 15.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in operating mode.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Capture Mode. In order for Capture Mode to recognize the trigger event on the CCPx pin, Timer1 must be clocked from the Instruction Clock (Fosc/4) or from an external clock source.

## 15.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler (refer to Example 15-1).

#### EXAMPLE 15-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCP1CON     | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCP1CON             |

| CLRF    | CCP1CON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|         |             | ; the new prescaler     |

|         |             | ; move value and CCP ON |

| MOVWF   | CCP1CON     | ;Load CCP1CON with this |

|         |             | ; value                 |

|         |             |                         |

# 15.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (Fosc/4), or by an external clock source.

If Timer1 is clocked by FOSC/4, then Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

If Timer1 is clocked by an external clock source, then Capture mode will operate as defined in **Section 15.1** "**Capture Mode**".

| Name    | Bit 7                                                                       | Bit 6          | Bit 5          | Bit 4          | Bit 3                   | Bit 2    | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-----------------------------------------------------------------------------|----------------|----------------|----------------|-------------------------|----------|---------|---------|----------------------|---------------------------------|

| ADCON0  | _                                                                           |                | CHS3           | CHS2           | CHS1                    | CHS0     | GO/DONE | ADON    | 00 0000              | 00 0000                         |

| ANSELB  | _                                                                           | _              | ANSB5          | ANSB4          | ANSB3                   | ANSB2    | ANSB1   | ANSB0   | 11 1111              | 11 1111                         |

| APFCON  | _                                                                           | _              | _              | _              | _                       | _        | SSSEL   | CCP2SEL | 00                   | 00                              |

| CCP1CON | _                                                                           | _              | DC1B1          | DC1B0          | CCP1M3                  | CCP1M2   | CCP1M1  | CCP1M0  | 00 0000              | 00 0000                         |

| CCP2CON | _                                                                           | _              | DC2B1          | DC2B0          | CCP2M3                  | CCP2M2   | CCP2M1  | CCP2M0  | 00 0000              | 00 0000                         |

| CCPRxL  | Capture/Com                                                                 | npare/PWM R    | egister X Lov  | v Byte         |                         |          |         |         | xxxx xxxx            | uuuu uuuu                       |

| CCPRxH  | Capture/Com                                                                 | npare/PWM R    | egister X Hig  | h Byte         |                         |          |         |         | xxxx xxxx            | uuuu uuuu                       |

| INTCON  | GIE                                                                         | PEIE           | TOIE           | INTE           | RBIE                    | T0IF     | INTF    | RBIF    | 0000 000x            | 0000 000x                       |

| PIE1    | TMR1GIE                                                                     | ADIE           | RCIE           | TXIE           | SSPIE                   | CCP1IE   | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIE2    | —                                                                           | -              | —              | -              | —                       | —        | —       | CCP2IE  | 0                    | 0                               |

| PIR1    | TMR1GIF                                                                     | ADIF           | RCIF           | TXIF           | SSPIF                   | CCP1IF   | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| PIR2    | —                                                                           | -              | —              | -              | —                       | —        | —       | CCP2IF  | 0                    | 0                               |

| T1CON   | TMR1CS1                                                                     | TMR1CS0        | T1CKPS1        | T1CKPS0        | T1OSCEN                 | T1SYNC   | _       | TMR10N  | 0000 00-0            | uuuu uu-u                       |

| T1GCON  | TMR1GE                                                                      | T1GPOL         | T1GTM          | T1GSPM         | T <u>1GGO</u> /<br>DONE | T1GVAL   | T1GSS1  | T1GSS0  | 0000 0x00            | 00x0 0x00                       |

| TMR1L   | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                |                |                |                         |          |         |         | xxxx xxxx            | uuuu uuuu                       |

| TMR1H   | Holding Regi                                                                | ster for the M | ost Significar | nt Byte of the | 16-bit TMR1 F           | Register |         |         | xxxx xxxx            | uuuu uuuu                       |

| TRISB   | TRISB7                                                                      | TRISB6         | TRISB5         | TRISB4         | TRISB3                  | TRISB2   | TRISB1  | TRISB0  | 1111 1111            | 1111 1111                       |

| TRISC   | TRISC7                                                                      | TRISC6         | TRISC5         | TRISC4         | TRISC3                  | TRISC2   | TRISC1  | TRISC0  | 1111 1111            | 1111 1111                       |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Compare.

# PIC16(L)F722/3/4/6/7

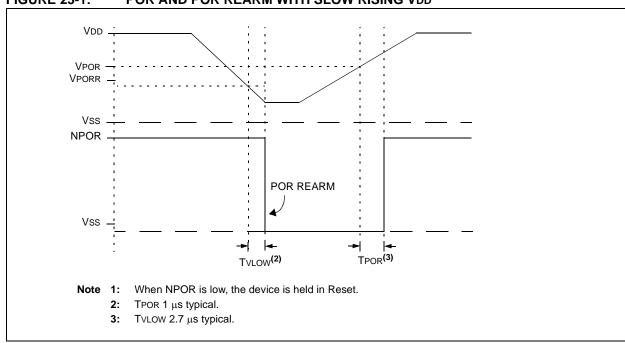

#### FIGURE 23-1: POR AND POR REARM WITH SLOW RISING VDD

#### 23.5 **Thermal Considerations**

| Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |           |                                        |      |       |                                                          |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------|------|-------|----------------------------------------------------------|--|--|--|

| Param<br>No.                                                                                                             | Sym.      | Characteristic                         | Тур. | Units | Conditions                                               |  |  |  |

| TH01                                                                                                                     | θJA       | Thermal Resistance Junction to Ambient | 60   | °C/W  | 28-pin SPDIP package                                     |  |  |  |

|                                                                                                                          |           |                                        | 80   | °C/W  | 28-pin SOIC package                                      |  |  |  |

|                                                                                                                          |           |                                        | 90   | °C/W  | 28-pin SSOP package                                      |  |  |  |

|                                                                                                                          |           |                                        | 27.5 | °C/W  | 28-pin UQFN 4x4mm package                                |  |  |  |

|                                                                                                                          |           |                                        | 27.5 | °C/W  | 28-pin QFN 6x6mm package                                 |  |  |  |

|                                                                                                                          |           |                                        | 47.2 | °C/W  | 40-pin PDIP package                                      |  |  |  |

|                                                                                                                          |           |                                        | 46   | °C/W  | 44-pin TQFP package                                      |  |  |  |

|                                                                                                                          |           |                                        | 24.4 | °C/W  | 44-pin QFN 8x8mm package                                 |  |  |  |

| TH02                                                                                                                     | θJC       | Thermal Resistance Junction to Case    | 31.4 | °C/W  | 28-pin SPDIP package                                     |  |  |  |

|                                                                                                                          |           |                                        | 24   | °C/W  | 28-pin SOIC package                                      |  |  |  |

|                                                                                                                          |           |                                        | 24   | °C/W  | 28-pin SSOP package                                      |  |  |  |

|                                                                                                                          |           |                                        | 24   | °C/W  | 28-pin UQFN 4x4mm package                                |  |  |  |

|                                                                                                                          |           |                                        | 24   | °C/W  | 28-pin QFN 6x6mm package                                 |  |  |  |

|                                                                                                                          |           |                                        | 24.7 | °C/W  | 40-pin PDIP package                                      |  |  |  |

|                                                                                                                          |           |                                        | 14.5 | °C/W  | 44-pin TQFP package                                      |  |  |  |