Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 25                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 11x8b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-QFN (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f722-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

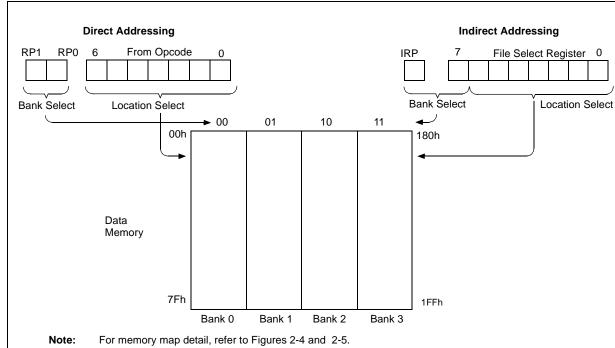

# 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit of the STATUS register, as shown in Figure 2-8.

A simple program to clear RAM location 020h-02Fh using indirect addressing is shown in Example 2-2.

#### EXAMPLE 2-2: INDIRECT ADDRESSING

|      | MOVLW<br>MOVWF<br>BANKISEL | 020h<br>FSR<br>020h | ;initialize pointer<br>;to RAM       |

|------|----------------------------|---------------------|--------------------------------------|

| NEXT | CLRF<br>INCF               | INDF<br>FSR         | ;clear INDF register<br>;inc pointer |

|      | BTFSS                      | FSR,4               | ;all done?                           |

|      | GOTO                       | NEXT                | ;no clear next                       |

| CONT | INUE                       |                     | ;yes continue                        |

|      |                            |                     |                                      |

# FIGURE 2-8: DIRECT/INDIRECT ADDRESSING

| IADLL | TABLE 3-1. STATUS BITS AND THEIR SIGNIFICANCE |    |    |                                                         |  |  |  |  |  |

|-------|-----------------------------------------------|----|----|---------------------------------------------------------|--|--|--|--|--|

| POR   | BOR                                           | то | PD | Condition                                               |  |  |  |  |  |

| 0     | x                                             | 1  | 1  | Power-on Reset or LDO Reset                             |  |  |  |  |  |

| 0     | x                                             | 0  | x  | legal, TO is set on POR                                 |  |  |  |  |  |

| 0     | x                                             | x  | 0  | Illegal, PD is set on POR                               |  |  |  |  |  |

| 1     | 0                                             | 1  | 1  | Brown-out Reset                                         |  |  |  |  |  |

| 1     | 1                                             | 0  | 1  | WDT Reset                                               |  |  |  |  |  |

| 1     | 1                                             | 0  | 0  | WDT Wake-up                                             |  |  |  |  |  |

| 1     | 1                                             | u  | u  | MCLR Reset during normal operation                      |  |  |  |  |  |

| 1     | 1                                             | 1  | 0  | MCLR Reset during Sleep or interrupt wake-up from Sleep |  |  |  |  |  |

# TABLE 3-1: STATUS BITS AND THEIR SIGNIFICANCE

# TABLE 3-2: RESET CONDITION FOR SPECIAL REGISTERS<sup>(2)</sup>

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 0000h                 | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 0000h                 | 0001 Ouuu          | uu               |

| WDT Reset                          | 0000h                 | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | uu               |

| Brown-out Reset                    | 0000h                 | 0001 luuu          | u0               |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

**2:** If a Status bit is not implemented, that bit will be read as '0'.

# REGISTER 6-5: PORTB: PORTB REGISTER

| R/W-x                              | R/W-x                                                                | R/W-x | R/W-x                                   | R/W-x    | R/W-x | R/W-x | R/W-x |

|------------------------------------|----------------------------------------------------------------------|-------|-----------------------------------------|----------|-------|-------|-------|

| RB7                                | RB6                                                                  | RB5   | RB4                                     | RB3      | RB2   | RB1   | RB0   |

| bit 7                              |                                                                      |       |                                         |          |       |       | bit 0 |

|                                    |                                                                      |       |                                         |          |       |       |       |

| Legend:                            |                                                                      |       |                                         |          |       |       |       |

| R = Readable                       | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                                         | l as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set |                                                                      |       | '0' = Bit is cleared x = Bit is unknown |          |       |       |       |

bit 7-0 **RB<7:0>**: PORTB I/O Pin bit 1 = Port pin is > VIH 0 = Port pin is < VIL

# REGISTER 6-6: TRISB: PORTB TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 TRISB<7:0>: PORTB Tri-State Control bit

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

### 9.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

- **Note 1:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

- **2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the GIE and PEIE bits of the INTCON register must be disabled. If the GIE and PEIE bits of the INT-CON register are enabled, execution will switch to the Interrupt Service Routine.

Please refer to **Section 9.1.5** "Interrupts" for more information.

# 9.2 ADC Operation

# 9.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

Note: The GO/DONE bit should not be set in the same instruction that turns on the ADC. Refer to Section 9.2.6 "A/D Conversion Procedure".

# 9.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRES register with new conversion result

# 9.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRES register will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

| Note: | A device Reset forces all registers to their |  |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|--|

|       | Reset state. Thus, the ADC module is         |  |  |  |  |  |  |  |

|       | turned off and any pending conversion is     |  |  |  |  |  |  |  |

|       | terminated.                                  |  |  |  |  |  |  |  |

# 9.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

# 9.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCP module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 15.0 "Capture/Compare/PWM (CCP) Module" for more information.

| FIGURE 12-5:           | TIMER1 GATE SINGLE-PULSE MODE                                                                  |

|------------------------|------------------------------------------------------------------------------------------------|

|                        |                                                                                                |

| TMR1GE                 |                                                                                                |

| T1GPOL                 |                                                                                                |

| T1GSPM                 |                                                                                                |

| T1GG <u>O/</u><br>DONE | <ul> <li>Cleared by hardware on falling edge of T1GVAL</li> <li>Counting enabled on</li> </ul> |

| T1G_IN                 | rising edge of T1G                                                                             |

| Т1СКІ                  |                                                                                                |

| T1GVAL                 |                                                                                                |

| TIMER1                 | N N + 1 N + 2                                                                                  |

| TMR1GIF                | <ul> <li>Cleared by software</li> <li>Set by hardware on falling edge of T1GVAL</li> </ul>     |

| U-0             | R/W-0                        | R/W-0                 | R/W-0          | R/W-0             | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |  |

|-----------------|------------------------------|-----------------------|----------------|-------------------|-----------------|-----------------|---------|--|--|--|--|--|

|                 | TOUTPS3                      | TOUTPS2               | TOUTPS1        | TOUTPS0           | TMR2ON          | T2CKPS1         | T2CKPS0 |  |  |  |  |  |

| bit 7           |                              |                       |                |                   |                 |                 | bit 0   |  |  |  |  |  |

|                 |                              |                       |                |                   |                 |                 |         |  |  |  |  |  |

| Legend:         |                              |                       |                |                   |                 |                 |         |  |  |  |  |  |

| R = Readable    | bit                          | W = Writable          | bit            | U = Unimplen      | nented bit, rea | d as '0'        |         |  |  |  |  |  |

| -n = Value at P | POR                          | '1' = Bit is set      |                | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |  |  |  |  |  |

| bit 7           | Unimplemen                   | ted: Read as '        | 0'             |                   |                 |                 |         |  |  |  |  |  |

| bit 6-3         | TOUTPS<3:0                   | >: Timer2 Out         | out Postscaler | Select bits       |                 |                 |         |  |  |  |  |  |

|                 | 0000 = 1:1 P                 | -                     |                |                   |                 |                 |         |  |  |  |  |  |

|                 | 0001 = 1:2 P                 | ostscaler             |                |                   |                 |                 |         |  |  |  |  |  |

|                 | 0010 = 1:3 P                 | ostscaler             |                |                   |                 |                 |         |  |  |  |  |  |

|                 |                              | 0011 = 1:4 Postscaler |                |                   |                 |                 |         |  |  |  |  |  |

|                 | 0100 = 1:5 Postscaler        |                       |                |                   |                 |                 |         |  |  |  |  |  |

|                 | 0101 = 1:6 Postscaler        |                       |                |                   |                 |                 |         |  |  |  |  |  |

|                 | 0110 = 1:7 P<br>0111 = 1:8 P |                       |                |                   |                 |                 |         |  |  |  |  |  |

|                 | 1000 = 1.9 P                 |                       |                |                   |                 |                 |         |  |  |  |  |  |

|                 | 1000 = 1.31                  |                       |                |                   |                 |                 |         |  |  |  |  |  |

|                 | 1010 = 1:11                  |                       |                |                   |                 |                 |         |  |  |  |  |  |

|                 | 1011 = <b>1:12</b>           | Postscaler            |                |                   |                 |                 |         |  |  |  |  |  |

|                 | 1100 = 1:13 Postscaler       |                       |                |                   |                 |                 |         |  |  |  |  |  |

|                 | 1101 = 1:14 Postscaler       |                       |                |                   |                 |                 |         |  |  |  |  |  |

|                 | 1110 = 1:15 Postscaler       |                       |                |                   |                 |                 |         |  |  |  |  |  |

|                 | 1111 = 1:16                  |                       |                |                   |                 |                 |         |  |  |  |  |  |

| bit 2           | TMR2ON: Timer2 On bit        |                       |                |                   |                 |                 |         |  |  |  |  |  |

|                 | 1 = Timer2 is                |                       |                |                   |                 |                 |         |  |  |  |  |  |

|                 | 0 = Timer2 is                | s off                 |                |                   |                 |                 |         |  |  |  |  |  |

| bit 1-0         | T2CKPS<1:0                   | >: Timer2 Cloc        | k Prescale Sel | ect bits          |                 |                 |         |  |  |  |  |  |

|                 | 00 = Prescale                |                       |                |                   |                 |                 |         |  |  |  |  |  |

|                 | 01 = Prescale                | -                     |                |                   |                 |                 |         |  |  |  |  |  |

|                 | 1x = Prescale                | er is 16              |                |                   |                 |                 |         |  |  |  |  |  |

| TABLE 13-1:     | SUMMAR                       |                       | FRS ASSO       |                   | H TIMER2        |                 |         |  |  |  |  |  |

# REGISTER 13-1: T2CON: TIMER2 CONTROL REGISTER

| IADEE  |                                              |         |         |         |         |        |         |         |                      |                                 |  |

|--------|----------------------------------------------|---------|---------|---------|---------|--------|---------|---------|----------------------|---------------------------------|--|

| Name   | Bit 7                                        | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |  |

| INTCON | GIE                                          | PEIE    | T0IE    | INTE    | RBIE    | T0IF   | INTF    | RBIF    | 0000 000x            | 0000 000x                       |  |

| PIE1   | TMR1GIE                                      | ADIE    | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |  |

| PIR1   | TMR1GIF                                      | ADIF    | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |  |

| PR2    | Timer2 Module Period Register                |         |         |         |         |        |         |         | 1111 1111            | 1111 1111                       |  |

| TMR2   | Holding Register for the 8-bit TMR2 Register |         |         |         |         |        |         |         | 0000 0000            | 0000 0000                       |  |

| T2CON  | _                                            | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |  |

x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module. Legend:

# 15.3.4 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 15-4.

## EQUATION 15-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2+1)]}{\log(2)}$$

bits

Note: If the pulse-width value is greater than the period, the assigned PWM pin(s) will remain unchanged.

# TABLE 15-5: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

# TABLE 15-6: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

# 15.3.5 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 15.3.6 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency (Fosc). Any changes in the system clock frequency will result in changes to the PWM frequency. Refer to **Section 7.0** "**Oscillator Module**" for additional details.

#### 15.3.7 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 15.3.8 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Disable the PWM pin (CCPx) output driver(s) by setting the associated TRIS bit(s).

- 2. Load the PR2 register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- Load the CCPRxL register and the DCxBx bits of the CCPxCON register, with the PWM duty cycle value.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register. See Note below.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until Timer2 overflows, TMR2IF bit of the PIR1 register is set. See Note below.

- Enable the PWM pin (CCPx) output driver(s) by clearing the associated TRIS bit(s).

- **Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

|        |                |            |                             |                |            | SYNC = 0,                   | BRGH =         | 0          |                             |                |                   |                             |  |

|--------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|-------------------|-----------------------------|--|

| BAUD   | Foso           | ; = 20.00  | 0 MHz                       | Fosc           | ; = 18.43  | 2 MHz                       | Fosc           | = 16.000   | 00 MHz                      | Fosc           | Fosc = 11.0592 MH |                             |  |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) |  |

| 300    |                | _          | _                           |                | _          | _                           |                | —          | —                           |                | _                 | _                           |  |

| 1200   | 1221           | 1.73       | 255                         | 1200           | 0.00       | 239                         | 1201           | 0.08       | 207                         | 1200           | 0.00              | 143                         |  |

| 2400   | 2404           | 0.16       | 129                         | 2400           | 0.00       | 119                         | 2403           | 0.16       | 103                         | 2400           | 0.00              | 71                          |  |

| 9600   | 9470           | -1.36      | 32                          | 9600           | 0.00       | 29                          | 9615           | 0.16       | 25                          | 9600           | 0.00              | 17                          |  |

| 10417  | 10417          | 0.00       | 29                          | 10286          | -1.26      | 27                          | 10416          | -0.01      | 23                          | 10165          | -2.42             | 16                          |  |

| 19.2k  | 19.53k         | 1.73       | 15                          | 19.20k         | 0.00       | 14                          | 19.23k         | 0.16       | 12                          | 19.20k         | 0.00              | 8                           |  |

| 57.6k  | _              | —          | _                           | 57.60k         | 0.00       | 7                           | —              | —          | _                           | 57.60k         | 0.00              | 2                           |  |

| 115.2k | —              | _          | —                           | _              | _          | —                           | _              | —          | —                           | _              | —                 | —                           |  |

### TABLE 16-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        |                |            |                             |                |            | SYNC = 0,                   | BRGH = 0       | D          |                             |                  |            |                             |

|--------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fos            | c = 8.000  | ) MHz                       | Fos            | c = 4.000  | ) MHz                       | Fosc           | : = 3.686  | 4 MHz                       | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _              | _          | _                           | 300            | 0.16       | 207                         | 300            | 0.00       | 191                         | 300              | 0.16       | 51                          |

| 1200   | 1202           | 0.16       | 103                         | 1202           | 0.16       | 51                          | 1200           | 0.00       | 47                          | 1202             | 0.16       | 12                          |

| 2400   | 2404           | 0.16       | 51                          | 2404           | 0.16       | 25                          | 2400           | 0.00       | 23                          | —                | _          | _                           |

| 9600   | 9615           | 0.16       | 12                          | —              | _          | _                           | 9600           | 0.00       | 5                           | —                | _          | _                           |

| 10417  | 10417          | 0.00       | 11                          | 10417          | 0.00       | 5                           | —              | _          | _                           | —                | _          | _                           |

| 19.2k  | _              | _          | _                           | —              | _          | _                           | 19.20k         | 0.00       | 2                           | —                | _          | _                           |

| 57.6k  | —              | _          | —                           | —              | _          | —                           | 57.60k         | 0.00       | 0                           | —                | _          | —                           |

| 115.2k |                | —          | —                           |                | —          | —                           |                | _          | —                           |                  | _          | —                           |

|        |                |            |                             |                |            | SYNC = 0,                   | BRGH = 2       | L          |                             |                |                    |                             |  |

|--------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|--------------------|-----------------------------|--|

| BAUD   | Fosc           | : = 20.00  | 0 MHz                       | Fosc           | = 18.43    | 2 MHz                       | Fosc           | = 16.000   | 00 MHz                      | Fosc           | Fosc = 11.0592 MHz |                             |  |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |

| 300    | —              |            | _                           |                | _          | _                           | _              | —          | _                           | —              | —                  | —                           |  |

| 1200   | —              | —          | —                           | —              | —          | —                           | —              | —          | —                           | —              | —                  | —                           |  |

| 2400   | —              | _          | _                           | _              | _          | _                           | _              | _          | _                           | —              | —                  | _                           |  |

| 9600   | 9615           | 0.16       | 129                         | 9600           | 0.00       | 119                         | 9615           | 0.16       | 103                         | 9600           | 0.00               | 71                          |  |

| 10417  | 10417          | 0.00       | 119                         | 10378          | -0.37      | 110                         | 10417          | 0.00       | 95                          | 10473          | 0.53               | 65                          |  |

| 19.2k  | 19.23k         | 0.16       | 64                          | 19.20k         | 0.00       | 59                          | 19.23k         | 0.16       | 51                          | 19.20k         | 0.00               | 35                          |  |

| 57.6k  | 56.82k         | -1.36      | 21                          | 57.60k         | 0.00       | 19                          | 58.8k          | 2.12       | 16                          | 57.60k         | 0.00               | 11                          |  |

| 115.2k | 113.64k        | -1.36      | 10                          | 115.2k         | 0.00       | 9                           | _              | _          | _                           | 115.2k         | 0.00               | 5                           |  |

# REGISTER 17-2: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (SPI MODE)

| R/W-0 | R/W-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| SMP   | CKE   | D/Ā | Р   | S   | R/W | UA  | BF    |

| bit 7 |       |     |     |     |     |     | bit 0 |

| R = Readab   | le bit                       | W = Writable bit                                                    | U = Unimplemented bit | , read as '0'      |  |  |  |  |  |

|--------------|------------------------------|---------------------------------------------------------------------|-----------------------|--------------------|--|--|--|--|--|

| -n = Value a | t POR                        | '1' = Bit is set                                                    | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |  |  |

|              |                              |                                                                     |                       |                    |  |  |  |  |  |

| bit 7        | SMP: SF                      | PI Data Input Sample Phase                                          | bit                   |                    |  |  |  |  |  |

|              |                              | SPI Master mode:                                                    |                       |                    |  |  |  |  |  |

|              | •                            | t data sampled at end of data                                       | •                     |                    |  |  |  |  |  |

|              | 0 = Input<br><u>SPI Slav</u> | t data sampled at middle of c                                       | data output time      |                    |  |  |  |  |  |

|              |                              | st be cleared when SPI is us                                        | sed in Slave mode     |                    |  |  |  |  |  |

| bit 6        | CKE: SP                      | PI Clock Edge Select bit                                            |                       |                    |  |  |  |  |  |

|              | <u>SPI mod</u>               | <u>SPI mode, CKP = <math>0</math>:</u>                              |                       |                    |  |  |  |  |  |

|              |                              | 1 = Data stable on rising edge of SCK                               |                       |                    |  |  |  |  |  |

|              |                              | 0 = Data stable on falling edge of SCK<br><u>SPI mode, CKP = 1:</u> |                       |                    |  |  |  |  |  |

|              |                              | = Data stable on falling edge of SCK                                |                       |                    |  |  |  |  |  |

|              |                              | stable on rising edge of SCI                                        |                       |                    |  |  |  |  |  |

| bit 5        |                              | D/A: Data/Address bit                                               |                       |                    |  |  |  |  |  |

|              | Used in I                    | I <sup>2</sup> C mode only.                                         |                       |                    |  |  |  |  |  |

| bit 4        | P: Stop b                    | P: Stop bit                                                         |                       |                    |  |  |  |  |  |

|              | Used in I                    | l <sup>2</sup> C mode only.                                         |                       |                    |  |  |  |  |  |

| bit 3        | S: Start b                   | oit                                                                 |                       |                    |  |  |  |  |  |

|              | Used in I                    | l <sup>2</sup> C mode only.                                         |                       |                    |  |  |  |  |  |

| bit 2        | R/W: Re                      | ad/Write Information bit                                            |                       |                    |  |  |  |  |  |

|              | Used in I                    | l <sup>2</sup> C mode only.                                         |                       |                    |  |  |  |  |  |

| bit 1        | UA: Upd                      | ate Address bit                                                     |                       |                    |  |  |  |  |  |

|              | Used in I                    | Used in I <sup>2</sup> C mode only.                                 |                       |                    |  |  |  |  |  |

| bit 0        | BF: Buffe                    | BF: Buffer Full Status bit                                          |                       |                    |  |  |  |  |  |

|              | 1 = Rece                     | eive complete, SSPBUF is fu                                         | II                    |                    |  |  |  |  |  |

|              | 0 - Rece                     | eive not complete, SSPBUF                                           | is omntv              |                    |  |  |  |  |  |

# 17.2.5 RECEPTION

When the  $R/\overline{W}$  bit of the received address byte is clear, the master will write data to the slave. If an address match occurs, the received address is loaded into the SSPBUF register. An address byte overflow will occur if that loaded address is not read from the SSPBUF before the next complete byte is received.

An SSP interrupt is generated for each data transfer byte. The BF,  $R/\overline{W}$  and  $D/\overline{A}$  bits of the SSPSTAT register are used to determine the status of the last received byte.

### FIGURE 17-10: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| R/<br>Receiving Address    | $\overline{W} = 0$<br>$\overline{\Delta C K}$ Receiving Data $\overline{\Delta C K}$ Receiving Data |                                                                  |

|----------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| SDA 1 A7XA6XA5XA4XA3XA2XA1 | ACK Receiving Data ACK Receiving Data<br>/D7/D6/D5/D4/D3/D2/D1/D0//D7/D6/D5/D4/D3/                  |                                                                  |

|                            | 3, 9, 1, 2, 3, 4, 5, 6, 7, 8, 9, 1, 2, 3, 4, 5,                                                     | /6\_/7\_/8 <del>\_</del> _/9\_/ <sup>!</sup> ₽ <sup>!</sup><br>I |

| SSPIF                      | Cleared in software                                                                                 | Bus Master<br>sends Stop                                         |

| BF                         | <ul> <li>SSPBUF register is read</li> </ul>                                                         | condition                                                        |

| SSPOV                      |                                                                                                     |                                                                  |

|                            | Bit SSPOV is set because the SSPBUF register is                                                     | s still full. 🗕                                                  |

|                            |                                                                                                     | s not sent.                                                      |

| Operands         Image: Stree of the second sec | Mnem   | nonic,                                 | Description                  | Cycles       |       | 14-Bit | Opcode | )        | Status   | Notes   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------|------------------------------|--------------|-------|--------|--------|----------|----------|---------|

| ADDWF         f, d         Add W and f         1         00         0111         dfff         C, DC, Z         1, 2           ANDWF         f, d         AND W with f         1         00         0101         dfff         Z         1, 2           CLRF         f         Clear W         1         00         0001         dfff         Z         2           COMF         f, d         Complement f         1         00         0001         dfff         Z         1, 2           COMF         f, d         Decrement f, Skip if 0         1(2)         00         1011         dfff         T, 2, 3           INCFS         f, d         Increment f, Skip if 0         1(2)         00         1010         dfff         T, 2, 3           INCFS         f, d         Increment f, Skip if 0         1(2)         00         1010         dfff         T, 2, 3           INCFS         f, d         Increment f, Skip if 0         1(2)         00         1010         dfff         T, 2, 3           INCFS         f, d         Indusive OR W with f         1         00         0000         dffff         Z         1, 2           MOVF         f, d         Rotate Right through Carry </th <th>Oper</th> <th>ands</th> <th>Description</th> <th>Cycles</th> <th colspan="2"></th> <th>LSb</th> <th>Affected</th> <th>Notes</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Oper   | ands                                   | Description                  | Cycles       |       |        | LSb    | Affected | Notes    |         |

| ANDWF         f, d         AND W with f         1         00         0101         dfff         fff         Z         1, 2           CLRF         f         Clear f         1         00         0001         lfff         fff         Z         2           COMF         f, d         Complement f         1         00         0001         dfff         fff         Z         1, 2, 3           DECFS         f, d         Decrement f, Skip if 0         1(2)         00         1011         dfff         fff         Z         1, 2, 3           INCFS         f, d         Increment f         1         00         1010         dfff         fff         Z         1, 2           INCFSZ         f, d         Increment f, Skip if 0         1(2)         00         1111         dfff         1         1, 2         1, 2           INCFSZ         f, d         Movef         1         00         1000         dfff         1, 2         1, 2         1, 2           INCFWF         f, d         Movef to         1         00         1000         dfff         1, 2         1, 2           MOVF         f, d         Rotate left through Carry         1         00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        | BYTE-ORIENTED FILE REGISTER OPERATIONS |                              |              |       |        |        |          |          |         |

| CLRF         f         Clear f         Clear W         1         00         0001         lfff         fff         Z         2           COMF         f, d         Complement f         1         00         0001         0xxxxxx         Z         1         1         00         0001         0xxxxxx         Z         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2         1         2 <th>ADDWF</th> <th>f, d</th> <th>Add W and f</th> <th>1</th> <th>00</th> <th>0111</th> <th>dfff</th> <th>ffff</th> <th>C, DC, Z</th> <th>1, 2</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADDWF  | f, d                                   | Add W and f                  | 1            | 00    | 0111   | dfff   | ffff     | C, DC, Z | 1, 2    |

| CLRW         -         Clear W         1         00         0001         0xxx xxxx         Z           COMF         f, d         Complement f         1         00         1010         dfff         ffff         Z         1, 2           DECF         f, d         Decrement f, Skip if 0         1(2)         00         1011         dfff         ffff         Z         1, 2           DECF         f, d         Increment f, Skip if 0         1(2)         00         1010         dfff         ffff         Z         1, 2           INCFS         f, d         Increment f, Skip if 0         1(2)         00         1111         dfff         ffff         Z         1, 2           INCFS         f, d         Increment f, Skip if 0         1(2)         00         1111         dfff         T         2, 2         1, 2           MOVF         f, d         Move f         1         00         0000         dfff         ffff         Z         1, 2         1, 2           MOVF         f, d         Rotate Left ftrough Carry         1         0         100         dfff         ffff         C         1, 2           SUBWF         f, d         Subtract W from f         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ANDWF  | f, d                                   | AND W with f                 | 1            | 00    | 0101   | dfff   | ffff     | Z        | 1, 2    |

| COMF         f, d         Complement f         1         00         1011         dfff         ffff         Z         1,2           DECF         f, d         Decrement f, Skip if 0         1(2)         00         1011         dfff         ffff         Z         1,2           INCF         f, d         Increment, Skip if 0         1(2)         00         1010         dfff         ffff         Z         1,2           INCF         f, d         Increment, Skip if 0         1(2)         00         1010         dfff         ffff         Z         1,2           INCF         f, d         Increment, Skip if 0         1(2)         00         1010         dfff         ffff         Z         1,2           INCF         f, d         Move OR         With f         1         00         000         dfff         ffff         Z         1,2           MOVF         f, d         Rotate Left fthrough Carry         1         00         1000         dfff         ffff         C         1,2           RF         f, d         Rotate Right fthrough Carry         1         00         1010         dfff         ffff         Z         1,2           SWAPF         f, d<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CLRF   | f                                      | Clear f                      | 1            | 00    | 0001   | lfff   | ffff     | Z        | 2       |

| DECF         f, d         Decrement f         1         00         0011         dfff         ffff         Z         1, 2           DECFSZ         f, d         Decrement f, Skip if 0         1(2)         00         1011         dfff         ffff         Z         1, 2           INCF         f, d         Increment f, Skip if 0         1(2)         00         1111         dfff         ffff         Z         1, 2           INCFSZ         f, d         Increment f, Skip if 0         1(2)         00         1111         dfff         ffff         Z         1, 2           INCFSZ         f, d         Incuesive OR W with f         1         00         100         dfff         ffff         Z         1, 2           MOVF         f         Move f         Move f         1         00         100         dfff         ffff         Z         1, 2           MOVF         f         Move f         Nove f         Nove f         1         00         100         dfff         ffff         Z         1, 2           SUBWF         f, d         Subtract W from f         1         00         110         dfff         ffff         Z         1, 2         1, 2 <td< td=""><td>CLRW</td><td>-</td><td>Clear W</td><td>1</td><td>00</td><td>0001</td><td>0xxx</td><td>xxxx</td><td>Z</td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CLRW   | -                                      | Clear W                      | 1            | 00    | 0001   | 0xxx   | xxxx     | Z        |         |

| DECFSZ         f, d         Decrement f, Skip if 0         1(2)         00         1011         dfff         fff         1, 2, 3           INCF         f, d         Increment f, Skip if 0         1(2)         00         1010         dff ffff         Z         1, 2, 3           INCFSZ         f, d         Increment, Skip if 0         1(2)         00         1010         dff ffff         Z         1, 2, 3           INCFSZ         f, d         Increment, Skip if 0         1         00         0100         dff ffff         Z         1, 2, 3           INCFSZ         f, d         Move f         1         00         0100         dff ffff         Z         1, 2, 3           MOVF         f, d         Move f         1         00         1000         dff ffff         Z         1, 2           MOVF         f, d         Rotate Left fthrough Carry         1         00         1100         dfff ffff         C         1, 2         1, 2           SUBWF         f, d         Subtract W from f         1         00         01010         dfff ffff         C         1, 2         1, 2           SUBWF         f, d         Subtract W from f         1         01         010 0bb fff <td>COMF</td> <td>f, d</td> <td>Complement f</td> <td>1</td> <td>00</td> <td>1001</td> <td>dfff</td> <td>ffff</td> <td>Z</td> <td>1, 2</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | COMF   | f, d                                   | Complement f                 | 1            | 00    | 1001   | dfff   | ffff     | Z        | 1, 2    |

| INCF         f, d         Increment f         1         00         1010         dff ffff         Z         1,2           INCFSZ         f, d         Increment f, Skip if 0         1(2)         00         1111         dff ffff         Z         1,2         3           IORWF         f, d         Incusive OR W with f         1         00         1000         dff fffff         Z         1,2           MOVF         f, d         Move f         1         00         1000         dff fffff         Z         1,2           MOVF         f, d         Move f         1         00         1000         dff fffff         Z         1,2           MOVF         f, d         Rotate Left fthrough Carry         1         00         1101         dfff ffff         C         1,2           SUBWF         f, d         Subract W from f         1         00         1100         dfff ffff         C, DC, Z         1,2           SUBWF         f, d         Subract W from f         1         00         1101         dfff ffff         Z         1,2           SUBWF         f, d         But at f         1         01         010 bb fff         fffff         Z         1,2 <td>DECF</td> <td>f, d</td> <td>Decrement f</td> <td>1</td> <td>00</td> <td>0011</td> <td>dfff</td> <td>ffff</td> <td>Z</td> <td>1, 2</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DECF   | f, d                                   | Decrement f                  | 1            | 00    | 0011   | dfff   | ffff     | Z        | 1, 2    |

| INCF         f, d         Increment f         1         00         1010         dff ffff         Z         1, 2           INCFSZ         f, d         Increment f, Skip if 0         1(2)         00         1111         dff ffff         Z         1, 2         3           IORWF         f, d         Inclusive OR W with f         1         00         1000         dff ffff         Z         1, 2           MOVF         f, d         Move f         1         00         1000         dff ffff         Z         1, 2           MOVF         f, d         Move f         1         00         1000         dff ffff         Z         1, 2           MOVF         f, d         Rotate Left through Carry         1         00         1101         dfff ffff         C         1, 2           SUBWF         f, d         Subract W from f         1         00         110         dfff ffff         Z         1, 2           SUBWF         f, d         Subract W from f         1         00         110         dfff ffff         Z         1, 2           SUBWF         f, d         Bit Test f         Skip if Clear         1         1         01         010 bb fff         fffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DECFSZ | f, d                                   | Decrement f, Skip if 0       | 1 <b>(2)</b> | 00    | 1011   | dfff   | ffff     |          | 1, 2, 3 |

| IORWF         f, d         Inclusive OR W with f         1         00         0100         dfff         ffff         Z         1, 2           MOVF         f, d         Move f         1         00         1000         dfff         fffff         Z         1, 2           MOVWF         f         Move W to f         1         00         0000         lfff         fffff         Z         1, 2           MOVWF         f         Move W to f         1         00         0000         lfff         fffff         Z         1, 2           MOVF         f, d         Rotate Left fthrough Carry         1         00         1100         dfff         ffff         C         1, 2           SUBWF         f, d         Subtract W from f         1         00         1010         dfff         ffff         Z         1, 2           XORWF         f, d         Exclusive OR W with f         1         00         0110         dfff         ffff         Z         1, 2           XORWF         f, d         Exclusive OR W with f         1         01         010bb         bfff         ffff         Z         1, 2           SUBWF         f, d         Bit Set f         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | INCF   | f, d                                   | Increment f                  | 1            | 00    | 1010   | dfff   | ffff     | Z        | 1, 2    |

| IORWF         f, d         Inclusive OR W with f         1         00         0100         dfff         ffff         Z         1, 2           MOVF         f, d         Move f         1         00         0000         dfff         fffff         Z         1, 2           MOVWF         f         Move W to f         1         00         0000         lfff         fffff         Z         1, 2           MOVWF         f         Move W to f         1         00         0000         lfff         fffff         Z         1, 2           MOVF         f, d         Rotate Left fhrough Carry         1         00         100         dfff         ffff         C         1, 2           SUBWF         f, d         Subtract W from f         1         00         1010         dfff         ffff         Z         1, 2           SUBWF         f, d         Exclusive OR W with f         1         00         1100         dfff         fffff         Z         1, 2           SUBWF         f, d         Exclusive OR W with f         1         01         010bb         bfff         fffff         Z         1, 2           SUBWF         f, d         Exclusive OR W with f <td>INCFSZ</td> <td>f, d</td> <td>Increment f, Skip if 0</td> <td>1<b>(2)</b></td> <td>00</td> <td>1111</td> <td>dfff</td> <td>ffff</td> <td></td> <td>1, 2, 3</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | INCFSZ | f, d                                   | Increment f, Skip if 0       | 1 <b>(2)</b> | 00    | 1111   | dfff   | ffff     |          | 1, 2, 3 |

| MOVWF         f         Move W to f         1         00         0000         lfff         ffff           NOP         -         No Operation         1         00         0000         0xx0         0000           RLF         f, d         Rotate Left through Carry         1         00         1100         dfff         ffff         C         1,2           SUBWF         f, d         Subtract W from f         1         00         1100         dfff         ffff         C         1,2           SWAPF         f, d         Swap nibbles in f         1         00         1100         dfff         ffff         Z         1,2           XORWF         f, d         Exclusive OR W with f         1         00         010         dfff         ffff         Z         1,2           XORWF         f, d         Exclusive OR W with f         1         00         010         dfff         ffff         Z         1,2           SWAPF         f, d         Exclusive OR W with f         1         01         00bb         bfff         fffff         Z         1,2           BCF         f, b         Bit Clear f         1         1         01         010bb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IORWF  | f, d                                   |                              |              | 00    | 0100   | dfff   | ffff     | Z        |         |

| MOVWF         f         Move W to f         1         00         0000         lfff         ffff           NOP         -         No Operation         1         00         0000         0xx0         0000           RLF         f, d         Rotate Left through Carry         1         00         1100         dfff         ffff         C         1,2           SUBWF         f, d         Subtract W from f         1         00         1100         dfff         ffff         C         1,2           SWAPF         f, d         Swap nibbles in f         1         00         1100         dfff         ffff         Z         1,2           XORWF         f, d         Exclusive OR W with f         1         00         010         dfff         ffff         Z         1,2           XORWF         f, d         Exclusive OR W with f         1         00         010         dfff         ffff         Z         1,2           SWAPF         f, d         Exclusive OR W with f         1         01         00bb         bfff         fffff         Z         1,2           BCF         f, b         Bit Clear f         1         1         01         010bb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MOVF   | f, d                                   | Move f                       | 1            | 00    | 1000   | dfff   | ffff     | Z        | 1, 2    |

| RLF         f, d         Rotate Left f through Carry         1         00         1101         dfff         fff         C         1,2           RRF         f, d         Subtract W from f         1         00         1100         dfff         ffff         C         1,2           SUBWF         f, d         Subtract W from f         1         00         0100         dfff         ffff         C         1,2           SWAPF         f, d         Swap nibbles in f         1         00         0110         dfff         ffff         Z,0,7,2         1,2           XORWF         f, d         Exclusive OR W with f         1         00         0110         dfff         ffff         Z,1,2           XORWF         f, d         Exclusive OR W with f         1         01         010bb         bfff         ffff         Z,2         1,2           BCF         f, b         Bit Clear f         Bit Set f         1         01         010bb         bfff         ffff         1,2           BTFSC         f, b         Bit Test f, Skip if Clear         1         1         1         1         1,2         3           ADDLW         k         Add literal and W         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        | f                                      | Move W to f                  | 1            | 00    | 0000   | lfff   | ffff     |          |         |

| RRF         f, d         Rotate Right fthrough Carry         1         00         1100         dfff         ffff         C         1,2           SUBWF         f, d         Subtract W from f         1         00         0010         dfff         ffff         C, DC, Z         1,2           SWAPF         f, d         Swap nibbles in f         1         00         1110         dfff         ffff         Z, DC, Z         1,2           XORWF         f, d         Exclusive OR W with f         1         00         0110         dfff         ffff         Z         1,2           XORWF         f, d         Exclusive OR W with f         1         01         00bb         bfff         ffff         Z         1,2           SUBWF         f, d         Bit Clear f         1         01         00bb         bfff         ffff         Z         1,2           BSF         f, b         Bit Test f, Skip if Clear         1         1         10b         bfff         ffff         3           BTFSS         f, b         Bit Test f, Skip if Set         1         1         1         111         111x         kkkk kkkk         Z         Z         Z         10         0kkkk kkkkk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | NOP    | -                                      | No Operation                 | 1            | 00    | 0000   | 0xx0   | 0000     |          |         |