Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 25                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 × 8                                                                  |

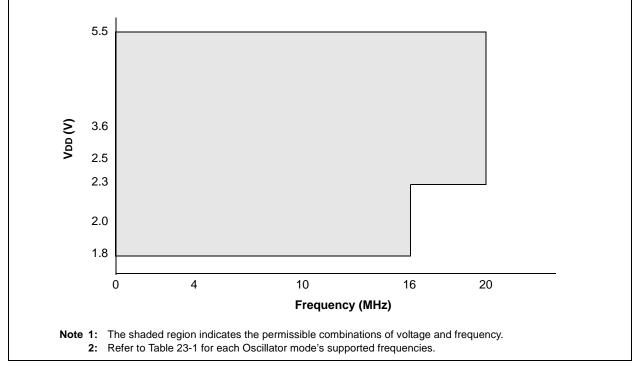

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 11x8b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-UFQFN Exposed Pad                                                     |

| Supplier Device Package    | 28-UQFN (4x4)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f722-i-mv |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## FIGURE 2-6:

## PIC16F726/LF726 AND PIC16F727/LF727 SPECIAL FUNCTION REGISTERS

| Indirect addr.(*)    | 00h      | Indirect addr.(*)      | 80h     | Indirect addr.(*)  | 100h | Indirect addr.(*)     | 180h |

|----------------------|----------|------------------------|---------|--------------------|------|-----------------------|------|

| TMR0                 | 01h      | OPTION                 | 81h     | TMR0               | 101h | OPTION                | 181h |

| PCL                  | 02h      | PCL                    | 82h     | PCL                | 102h | PCL                   | 182h |

| STATUS               | 03h      | STATUS                 | 83h     | STATUS             | 103h | STATUS                | 183h |

| FSR                  | 04h      | FSR                    | 84h     | FSR                | 104h | FSR                   | 184h |

| PORTA                | 05h      | TRISA                  | 85h     |                    | 105h | ANSELA                | 185h |

| PORTB                | 06h      | TRISB                  | 86h     |                    | 106h | ANSELB                | 186h |

| PORTC                | 07h      | TRISC                  | 87h     |                    | 107h |                       | 187h |

| PORTD <sup>(1)</sup> | 08h      | TRISD <sup>(1)</sup>   | 88h     | CPSCON0            | 108h | ANSELD <sup>(1)</sup> | 188h |

| PORTE                | 09h      | TRISE                  | 89h     | CPSCON1            | 109h | ANSELE <sup>(1)</sup> | 189h |

| PCLATH               | 0Ah      | PCLATH                 | 8Ah     | PCLATH             | 10Ah | PCLATH                | 18Ah |

| INTCON               | 0Bh      | INTCON                 | 8Bh     | INTCON             | 10Bh | INTCON                | 18Bh |

| PIR1                 | 0Ch      | PIE1                   | 8Ch     | PMDATL             | 10Ch | PMCON1                | 18Ch |

| PIR2                 | 0Dh      | PIE2                   | 8Dh     | PMADRL             | 10Dh | Reserved              | 18Dh |

| TMR1L                | 0Eh      | PCON                   | 8Eh     | PMDATH             | 10Eh | Reserved              | 18Eh |

| TMR1H                | 0Fh      | T1GCON                 | 8Fh     | PMADRH             | 10Fh | Reserved              | 18Fh |

| T1CON                | 10h      | OSCCON                 | 90h     |                    | 110h |                       | 190h |

| TMR2                 | 11h      | OSCTUNE                | 91h     |                    | 111h |                       | 191h |

| T2CON                | 12h      | PR2                    | 92h     |                    | 112h |                       | 192h |

| SSPBUF               | 13h      | SSPADD/SSPMSK          | 93h     |                    | 113h |                       | 193h |

| SSPCON               | 14h      | SSPSTAT                | 94h     |                    | 114h |                       | 194h |

| CCPR1L               | 15h      | WPUB                   | 95h     |                    | 115h |                       | 195h |

| CCPR1H               | 16h      | IOCB                   | 96h     | General            | 116h | General               | 196h |

| CCP1CON              | 17h      |                        | 97h     | Purpose            | 117h | Purpose               | 197h |

| RCSTA                | 18h      | TXSTA                  | 98h     | Register           | 118h | Register              | 198h |

| TXREG                | 19h      | SPBRG                  | 99h     | 16 Bytes           | 119h | 16 Bytes              | 199h |

| RCREG                | 1Ah      |                        | 9Ah     |                    | 11Ah |                       | 19Ah |

| CCPR2L               | 1Bh      |                        | 9Bh     |                    | 11Bh |                       | 19Bh |

| CCPR2H               | 1Ch      | APFCON                 | 9Ch     |                    | 11Ch |                       | 19Ch |

| CCP2CON              | 1Dh      | FVRCON                 | 9Dh     |                    | 11Dh |                       | 19Dh |

| ADRES                | 1Eh      |                        | 9Eh     |                    | 11Eh |                       | 19Eh |

| ADCON0               | 1Fh      | ADCON1                 | 9Fh     |                    | 11Fh |                       | 19Fh |

|                      | 20h      |                        | A0h     |                    | 120h |                       | 1A0h |

|                      |          | General                |         | General            |      | General               |      |

|                      |          | Purpose                |         | Purpose            |      | Purpose               |      |

| General              |          | Register               |         | Register           |      | Register              |      |

| Purpose              |          | 80 Bytes               |         | 80 Bytes           |      | 80 Bytes              |      |

| Register<br>96 Bytes |          |                        | EFh     |                    | 16Fh |                       | 1EFh |

| So Bytes             |          | Accesses               | F0h     | Accesses           | 170h | Accesses              | 1F0h |

|                      |          | 70h-7Fh                |         | 70h-7Fh            |      | 70h-7Fh               |      |

|                      | 7Fh      |                        | FFh     |                    | 17Fh |                       | 1FFh |

| Bank 0               |          | Bank 1                 |         | Bank 2             | 1    | Bank 3                | 1    |

| d: = Unimple         | mented o | data memory locations, | read as | ʻ0',               |      |                       |      |

| * = Not a ph         |          |                        |         | implemented on the |      |                       |      |

| IADLE . | J-1. C |    |    | S AND THEIR SIGNIFICANCE                                |

|---------|--------|----|----|---------------------------------------------------------|

| POR     | BOR    | то | PD | Condition                                               |

| 0       | x      | 1  | 1  | Power-on Reset or LDO Reset                             |

| 0       | x      | 0  | x  | Illegal, TO is set on POR                               |

| 0       | x      | x  | 0  | Illegal, PD is set on POR                               |

| 1       | 0      | 1  | 1  | Brown-out Reset                                         |

| 1       | 1      | 0  | 1  | WDT Reset                                               |

| 1       | 1      | 0  | 0  | WDT Wake-up                                             |

| 1       | 1      | u  | u  | MCLR Reset during normal operation                      |

| 1       | 1      | 1  | 0  | MCLR Reset during Sleep or interrupt wake-up from Sleep |

## TABLE 3-1: STATUS BITS AND THEIR SIGNIFICANCE

## TABLE 3-2: RESET CONDITION FOR SPECIAL REGISTERS<sup>(2)</sup>

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 0000h                 | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 0000h                 | 0001 Ouuu          | uu               |

| WDT Reset                          | 0000h                 | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | uu               |

| Brown-out Reset                    | 0000h                 | 0001 luuu          | u0               |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

**2:** If a Status bit is not implemented, that bit will be read as '0'.

# PIC16(L)F722/3/4/6/7

## 4.5.5 PIR2 REGISTER

The PIR2 register contains the interrupt flag bits, as shown in Register 4-5.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## REGISTER 4-5: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

| —     | —   | _   |     | —   | —   |     | CCP2IF |

| bit 7 |     |     |     |     |     |     | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

## bit 7-1 Unimplemented: Read as '0'

## bit 0 CCP2IF: CCP2 Interrupt Flag bit

Capture Mode:

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 register capture occurred

## Compare Mode:

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

## PWM mode:

Unused in this mode

## TABLE 4-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name       | Bit 7   | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|---------|--------|-------|-------|-------|--------|--------|--------|----------------------|---------------------------------|

| INTCON     | GIE     | PEIE   | TOIE  | INTE  | RBIE  | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| OPTION_REG | RBPU    | INTEDG | TOCS  | T0SE  | PSA   | PS2    | PS1    | PS0    | 1111 1111            | 1111 1111                       |

| PIE1       | TMR1GIE | ADIE   | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIE2       | _       | _      | _     |       |       | —      |        | CCP2IE | 0                    | 0                               |

| PIR1       | TMR1GIF | ADIF   | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIR2       | _       | _      | _     | _     | _     | _      | _      | CCP2IF | 0                    | 0                               |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Capture, Compare and PWM.

# PIC16(L)F722/3/4/6/7

| REGISTER      | <b>19-2.</b> ADCO              |                        | ITROL REG        |                    |                    |                  |        |

|---------------|--------------------------------|------------------------|------------------|--------------------|--------------------|------------------|--------|

| U-0           | R/W-0                          | R/W-0                  | R/W-0            | U-0                | U-0                | R/W-0            | R/W-0  |

| _             | ADCS2                          | ADCS1                  | ADCS0            | _                  | _                  | ADREF1           | ADREF0 |

| bit 7         |                                |                        |                  |                    |                    |                  | bit 0  |

| Legend:       |                                |                        |                  |                    |                    |                  |        |

| R = Readabl   | le bit                         | W = Writable bi        | t                | U = Unimpleme      | ented bit, read as | s 'O'            |        |

| -n = Value at | t POR                          | '1' = Bit is set       |                  | '0' = Bit is clear | red                | x = Bit is unkno | wn     |

|               |                                |                        |                  |                    |                    |                  |        |

| bit 7         | Unimplemente                   | ed: Read as '0'        |                  |                    |                    |                  |        |

| bit 6-4       | ADCS<2:0>: A                   | /D Conversion C        | lock Select bits |                    |                    |                  |        |

|               | 000 = Fosc/2                   |                        |                  |                    |                    |                  |        |

|               | 001 = Fosc/8                   |                        |                  |                    |                    |                  |        |

|               | 010 = Fosc/32                  | -                      |                  |                    |                    |                  |        |

|               | · · ·                          | ock supplied from      | a dedicated RC   | Coscillator)       |                    |                  |        |

|               | 100 = Fosc/4<br>101 = Fosc/16  |                        |                  |                    |                    |                  |        |

|               | 101 = FOSC/10<br>110 = FOSC/64 | -                      |                  |                    |                    |                  |        |

|               |                                | ,<br>ock supplied from | a dedicated RC   | coscillator)       |                    |                  |        |

| bit 3-2       | Unimplemente                   | ••                     |                  | ,                  |                    |                  |        |

| bit 1-0       | ADREF<1:0>:                    | Voltage Referend       | e Configuration  | bits               |                    |                  |        |

|               |                                | connected to VDD       | 0                |                    |                    |                  |        |

|               | 10 = VREF is c                 | connected to exte      | rnal VREF (RA3   | /AN3)              |                    |                  |        |

|               |                                |                        | nal Fixed Voltag |                    |                    |                  |        |

## REGISTER 9-2: ADCON1: A/D CONTROL REGISTER 1

## REGISTER 9-3: ADRES: ADC RESULT REGISTER

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 | ADRES1 | ADRES0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 **ADRES<7:0>**: ADC Result Register bits 8-bit conversion result.

## 10.0 FIXED VOLTAGE REFERENCE

This device contains an internal voltage regulator. To provide a reference for the regulator, a band gap reference is provided. This band gap is also user accessible via an A/D converter channel.

User level band gap functions are controlled by the FVRCON register, which is shown in Register 10-1.

## REGISTER 10-1: FVRCON: FIXED VOLTAGE REFERENCE REGISTER

| R-q                                | R/W-0             | U-0            | U-0              | U-0                                | U-0             | R/W-0  | R/W-0  |  |

|------------------------------------|-------------------|----------------|------------------|------------------------------------|-----------------|--------|--------|--|

| FVRRDY                             | FVREN             | —              | —                | —                                  | —               | ADFVR1 | ADFVR0 |  |

| bit 7                              |                   |                |                  |                                    |                 |        | bit 0  |  |

|                                    |                   |                |                  |                                    |                 |        |        |  |

| Legend:                            |                   |                |                  |                                    |                 |        |        |  |

| R = Readable I                     | bit               | W = Writable I | bit              | U = Unimplemented bit, read as '0' |                 |        |        |  |

| -n = Value at POR '1' = Bit is set |                   |                | '0' = Bit is cle | ared                               | x = Bit is unkr | nown   |        |  |

| q = Value depends on condition     |                   |                |                  |                                    |                 |        |        |  |

| q = Value depe                     | ends on condition | on             |                  |                                    |                 |        |        |  |

| bit 7   | FVRRDY <sup>(1)</sup> : Fixed Voltage Reference Ready Flag bit                        |

|---------|---------------------------------------------------------------------------------------|

|         | 0 = Fixed Voltage Reference output is not active or stable                            |

|         | 1 = Fixed Voltage Reference output is ready for use                                   |

| bit 6   | FVREN <sup>(2)</sup> : Fixed Voltage Reference Enable bit                             |

|         | 0 = Fixed Voltage Reference is disabled                                               |

|         | 1 = Fixed Voltage Reference is enabled                                                |

| bit 5-2 | Unimplemented: Read as '0'                                                            |

| bit 1-0 | ADFVR<1:0>: A/D Converter Fixed Voltage Reference Selection bits                      |

|         | 00 = A/D Converter Fixed Voltage Reference Peripheral output is off.                  |

|         | 01 = A/D Converter Fixed Voltage Reference Peripheral output is 1x (1.024V)           |

|         | $10 = A/D$ Converter Fixed Voltage Reference Peripheral output is $2x (2.048V)^{(2)}$ |

|         | 11 = A/D Converter Fixed Voltage Reference Peripheral output is $4x (4.096V)^{(2)}$   |

| Note 1: | FVRRDY is always '1' for the PIC16F72X devices.                                       |

2: Fixed Voltage Reference output cannot exceed VDD.

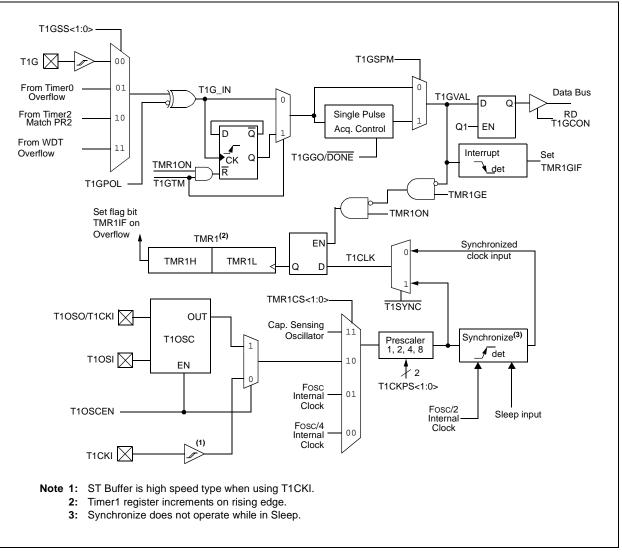

## 12.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- 3-bit prescaler

- Dedicated LP oscillator circuit

- Synchronous or asynchronous operation

- Multiple Timer1 gate (count enable) sources

- Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Time base for the Capture/Compare function

- Special Event Trigger (with CCP)

- Gate Single-pulse mode

- Gate Value StatusGate Event Interrupt

· Gate Toggle mode

Selectable Gate Source Polarity

Figure 12-1 is a block diagram of the Timer1 module.

## FIGURE 12-1: TIMER1 BLOCK DIAGRAM

## 12.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR1ON bit of the T1CON register

- TMR1IE bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

## 12.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- PEIE bit of the INTCON register must be set

- TISYNC bit of the T1CON register must be set

- TMR1CS bits of the T1CON register must be configured

- T1OSCEN bit of the T1CON register must be configured

- TMR1GIE bit of the T1GCON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine (0004h).

## 12.9 CCP Capture/Compare Time Base

The CCP module uses the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Special Event Trigger.

For more information, see Section 15.0 "Capture/Compare/PWM (CCP) Module".

## 12.10 CCP Special Event Trigger

When the CCP is configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair becomes the period register for Timer1.

Timer1 should be synchronized to the Fosc/4 to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the CCP, the write will take precedence.

For more information, see Section 9.2.5 "Special Event Trigger".

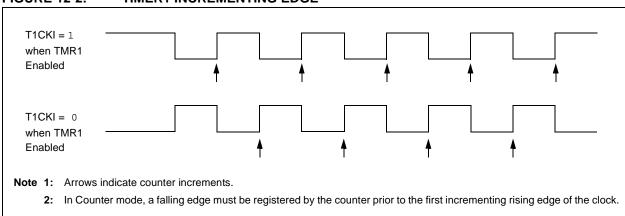

## FIGURE 12-2: TIMER1 INCREMENTING EDGE

## 12.12 Timer1 Gate Control Register

The Timer1 Gate Control register (T1GCON), shown in Register 12-2, is used to control Timer1 Gate.

| R/W-0         | R/W-0                                                                                                                                                                 | R/W-0                                     | R/W-0                            | R/W-0            | R-x             | R/W-0           | R/W-0  |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------|------------------|-----------------|-----------------|--------|--|--|--|--|--|

| TMR1GE        | T1GPOL                                                                                                                                                                | T1GTM                                     | T1GSPM                           | T1GGO/<br>DONE   | T1GVAL          | T1GSS1          | T1GSS0 |  |  |  |  |  |

| bit 7         | •                                                                                                                                                                     |                                           |                                  |                  |                 |                 | bit    |  |  |  |  |  |

|               |                                                                                                                                                                       |                                           |                                  |                  |                 |                 |        |  |  |  |  |  |

| Legend:       |                                                                                                                                                                       |                                           |                                  |                  |                 |                 |        |  |  |  |  |  |

| R = Readable  |                                                                                                                                                                       | W = Writable                              |                                  | -                | nented bit, rea |                 |        |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                                                   | '1' = Bit is set                          |                                  | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |  |  |  |  |  |

| h:+ 7         |                                                                                                                                                                       | nor1 Coto Eng                             | hla hit                          |                  |                 |                 |        |  |  |  |  |  |

| bit 7         | If TMR1GE: If                                                                                                                                                         | ner1 Gate Ena                             | DIE DIT                          |                  |                 |                 |        |  |  |  |  |  |

|               | This bit is ign                                                                                                                                                       |                                           |                                  |                  |                 |                 |        |  |  |  |  |  |

|               | <u>If TMR10N =</u>                                                                                                                                                    | <u>1</u> :                                |                                  |                  |                 |                 |        |  |  |  |  |  |

|               |                                                                                                                                                                       |                                           | rolled by the Ti                 |                  | ction           |                 |        |  |  |  |  |  |

| 1.11.0        |                                                                                                                                                                       | -                                         | ss of Timer1 ga                  | ate function     |                 |                 |        |  |  |  |  |  |

| bit 6         |                                                                                                                                                                       | ner1 Gate Pola                            | •                                | into whon goto   | ic high)        |                 |        |  |  |  |  |  |

|               |                                                                                                                                                                       |                                           | gh (Timer1 cou<br>w (Timer1 coui |                  |                 |                 |        |  |  |  |  |  |

| bit 5         |                                                                                                                                                                       | er1 Gate Toggl                            |                                  | J                | /               |                 |        |  |  |  |  |  |

|               |                                                                                                                                                                       | 1 = Timer1 Gate Toggle mode is enabled.   |                                  |                  |                 |                 |        |  |  |  |  |  |

|               |                                                                                                                                                                       |                                           | de is disabled                   |                  | flop is cleared |                 |        |  |  |  |  |  |

| 1.11.4        | •                                                                                                                                                                     |                                           | on every rising                  |                  |                 |                 |        |  |  |  |  |  |

| bit 4         |                                                                                                                                                                       | T1GSPM: Timer1 Gate Single Pulse Mode bit |                                  |                  |                 |                 |        |  |  |  |  |  |

|               | <ul> <li>1 = Timer1 gate Single-Pulse mode is enabled and is controlling Timer1 gate</li> <li>0 = Timer1 gate Single-Pulse mode is disabled</li> </ul>                |                                           |                                  |                  |                 |                 |        |  |  |  |  |  |

| bit 3         |                                                                                                                                                                       | _                                         |                                  |                  | atus bit        |                 |        |  |  |  |  |  |

|               | <b>T1GGO/DONE:</b> Timer1 Gate Single-Pulse Acquisition Status bit<br>1 = Timer1 gate single-pulse acquisition is ready, waiting for an edge                          |                                           |                                  |                  |                 |                 |        |  |  |  |  |  |

|               | <ul> <li>0 = Timer1 gate single-pulse acquisition has completed or has not been started</li> <li>This bit is automatically cleared when T1GSPM is cleared.</li> </ul> |                                           |                                  |                  |                 |                 |        |  |  |  |  |  |

|               |                                                                                                                                                                       | -                                         |                                  | SPM is cleared   | d.              |                 |        |  |  |  |  |  |

| bit 2         |                                                                                                                                                                       | ner1 Gate Curr                            |                                  |                  |                 |                 |        |  |  |  |  |  |

|               |                                                                                                                                                                       |                                           | f the Timer1 ga<br>Enable (TMR1) |                  | e provided to   | IMR1H:TMR1L     |        |  |  |  |  |  |

| bit 1-0       | T1GSS<1:0>                                                                                                                                                            | : Timer1 Gate                             | Source Select                    | bits             |                 |                 |        |  |  |  |  |  |

|               | 00 = Timer1                                                                                                                                                           |                                           |                                  |                  |                 |                 |        |  |  |  |  |  |

|               |                                                                                                                                                                       | Overflow outpu<br>latch PR2 outp          |                                  |                  |                 |                 |        |  |  |  |  |  |

|               |                                                                                                                                                                       | og Timer scale                            |                                  |                  |                 |                 |        |  |  |  |  |  |

|               | Watchde                                                                                                                                                               |                                           |                                  |                  |                 |                 |        |  |  |  |  |  |

## REGISTER 12-2: T1GCON: TIMER1 GATE CONTROL REGISTER

| Name    | Bit 7        | Bit 6                                   | Bit 5         | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------------|-----------------------------------------|---------------|---------|---------|--------|---------|---------|----------------------|---------------------------------|

| ANSELB  | —            | —                                       | ANSB5         | ANSB4   | ANSB3   | ANSB2  | ANSB1   | ANSB0   | 11 1111              | 11 1111                         |

| APFCON  | _            | _                                       | _             | _       | _       | _      | SSSEL   | CCP2SEL | 00                   | 00                              |

| CCP1CON | _            | _                                       | DC1B1         | DC1B0   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00 0000              | 00 0000                         |

| CCP2CON | _            | _                                       | DC2B1         | DC2B0   | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00 0000              | 00 0000                         |

| CCPRxL  | Capture/Con  | Capture/Compare/PWM Register X Low Byte |               |         |         |        |         |         |                      | uuuu uuuu                       |

| CCPRxH  | Capture/Con  | npare/PWM R                             | egister X Hig | h Byte  |         |        |         |         | xxxx xxxx            | uuuu uuuu                       |

| PR2     | Timer2 Perio | d Register                              |               |         |         |        |         |         | 1111 1111            | 1111 1111                       |

| T2CON   | _            | TOUTPS3                                 | TOUTPS2       | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

| TMR2    | Timer2 Modu  | ule Register                            |               |         |         |        |         |         | 0000 0000            | 0000 0000                       |

| TRISB   | TRISB7       | TRISB6                                  | TRISB5        | TRISB4  | TRISB3  | TRISB2 | TRISB1  | TRISB0  | 1111 1111            | 1111 1111                       |

| TRISC   | TRISC7       | TRISC6                                  | TRISC5        | TRISC4  | TRISC3  | TRISC2 | TRISC1  | TRISC0  | 1111 1111            | 1111 1111                       |

TABLE 15-7: SUMMARY OF REGISTERS ASSOCIATED WITH PWM

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the PWM.

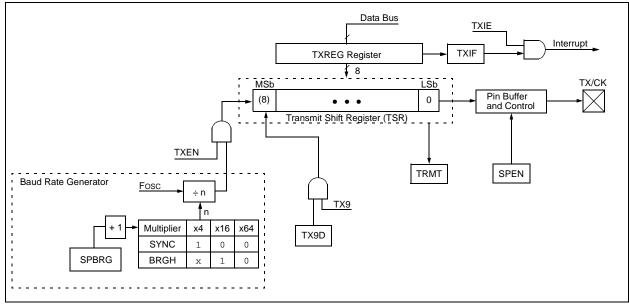

## 16.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (AUSART)

The Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The AUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The AUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- Address detection in 9-bit mode

- Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- · Half-duplex synchronous slave

- Sleep operation

Block diagrams of the AUSART transmitter and receiver are shown in Figure 16-1 and Figure 16-2.

## FIGURE 16-1: AUSART TRANSMIT BLOCK DIAGRAM

## 17.1.2.4 Slave Select Operation

The  $\overline{SS}$  pin allows Synchronous Slave mode operation. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPM<3:0> = 0100). The associated TRIS bit for the  $\overline{SS}$  pin must be set, making  $\overline{SS}$  an input.

In Slave Select mode, when:

- SS = 0, The device operates as specified in Section 17.1.2 "Slave Mode".

- $\overline{SS} = 1$ , The SPI module is held in Reset and the SDO pin will be tri-stated.

- Note 1: When the SPI is in Slave mode with  $\overline{SS}$  pin control enabled (SSPM<3:0> = 0100), the SPI module will reset if the  $\overline{SS}$  pin is driven high.

- 2: If the SPI is used in Slave mode with CKE set, the SS pin control must be enabled.

When the SPI module resets, the bit counter is cleared to '0'. This can be done by either forcing the SS pin to a high level or clearing the SSPEN bit. Figure 17-6 shows the timing waveform for such a synchronization event.

| Note: | SSPSR must be reinitialized by writing to |

|-------|-------------------------------------------|

|       | the SSPBUF register before the data can   |

|       | be clocked out of the slave again.        |

## 17.1.2.5 Sleep in Slave Mode

While in Sleep mode, the slave can transmit/receive data. The SPI Transmit/Receive Shift register operates asynchronously to the device on the externally supplied clock source. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the SSP Interrupt Flag bit will be set and if enabled, will wake the device from Sleep.

| <u>88</u>                            |             |                                       |                  |                                                |                  |                              |                                        |                                                    |                                   |                                               |

|--------------------------------------|-------------|---------------------------------------|------------------|------------------------------------------------|------------------|------------------------------|----------------------------------------|----------------------------------------------------|-----------------------------------|-----------------------------------------------|

| SCK<br>(CKP = 0                      |             |                                       |                  |                                                |                  | 5                            |                                        |                                                    |                                   | ;<br>;<br>;<br>;<br>;                         |

| SCK<br>(CKP = 1                      |             |                                       |                  |                                                |                  |                              |                                        |                                                    | ;<br>,<br>,<br>,                  | · · · · · · · · · · · · · · · · · · ·         |

| vine u<br>SSPSUF                     |             |                                       | -<br>            | 2<br>2<br>2<br>2<br>2<br>2<br>3<br>3<br>3<br>3 |                  | SSPSR<br>the SSP<br>be bloc* | must be a<br>BUF regis<br>ed out of it | sinitistized by<br>ter before the<br>le siève agai | / writing to<br>e data can<br>n.] |                                               |

| soc                                  |             | :                                     | (****)<br>(****) |                                                |                  |                              |                                        | **************************************             | × 58 0                            | (<br>)<br>*********************************** |

| <b>SDI</b><br>(SMP = 0)              | ·<br>·<br>· | <br>bit 7                             | $\bigcirc$       | 4<br>4<br>5<br>5                               | ,<br>,<br>,<br>, | <                            |                                        | $\rightarrow$                                      | <u>}</u>                          |                                               |

| Input<br>Sample<br>(3869 = c)        | :<br>:<br>: |                                       | <b>1</b>         | ><br>><br>><br>>                               | ;<br>;<br>;      |                              |                                        |                                                    |                                   | *                                             |

| SPER<br>Interrupt<br>Pag<br>SSPSR to | ,<br>;<br>, | , , , , , , , , , , , , , , , , , , , | •<br>•<br>•      | ,<br>,<br>,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,   | ,<br>,<br>,      | 5<br>5<br>5                  | •<br>•<br>•                            |                                                    |                                   |                                               |

## REGISTER 17-5: SSPMSK: SSP MASK REGISTER

| R/W-1                               | R/W-1 | R/W-1 | R/W-1                              | R/W-1 | R/W-1            | R/W-1 | R/W-1 |  |

|-------------------------------------|-------|-------|------------------------------------|-------|------------------|-------|-------|--|

| MSK7                                | MSK6  | MSK5  | MSK4                               | MSK3  | MSK2             | MSK1  | MSK0  |  |

| bit 7                               |       |       |                                    |       | -                |       | bit   |  |

| Legend:                             |       |       |                                    |       |                  |       |       |  |

| R = Readable bit $W = Writable bit$ |       | t     | U = Unimplemented bit, read as '0' |       |                  |       |       |  |

| -n = Value at POR '1' = Bit is set  |       |       | '0' = Bit is clear                 | ed    | x = Bit is unkno | wn    |       |  |

|       | 0 = 110 received address bit instructused to detect i C address match                              |

|-------|----------------------------------------------------------------------------------------------------|

| bit 0 | MSK<0>: Mask bit for I <sup>2</sup> C Slave Mode, 10-bit Address                                   |

|       | I <sup>2</sup> C Slave Mode, 10-bit Address (SSPM<3:0> = 0111):                                    |

|       | 1 = The received address bit '0' is compared to SSPADD<0> to detect I <sup>2</sup> C address match |

|       | $0 =$ The received address bit '0' is not used to detect $1^2$ C address match                     |

|       | All other SSP modes: this bit has no effect.                                                       |

|       |                                                                                                    |

## REGISTER 17-6: SSPADD: SSP I<sup>2</sup>C ADDRESS REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ADD7  | ADD6  | ADD5  | ADD4  | ADD3  | ADD2  | ADD1  | ADD0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

|       |       |       |       |       |       |       |       |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | ʻ0'                |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-0 **ADD<7:0>:** Address bits Received address

## TABLE 17-7: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

| Name                  | Bit 7                                                    | Bit 6              | Bit 5                   | Bit 4      | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|----------------------------------------------------------|--------------------|-------------------------|------------|------------|--------|--------|--------|----------------------|---------------------------------|

| INTCON                | GIE                                                      | PEIE               | TOIE                    | INTE       | RBIE       | TOIF   | INTF   | RBIF   | x000 0000x           | 0000 000u                       |

| PIR1                  | TMR1GIF                                                  | ADIF               | RCIF                    | TXIF       | SSPIF      | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1                  | TMR1GIE                                                  | ADIE               | RCIE                    | TXIE       | SSPIE      | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| SSPBUF                | Synchronous Serial Port Receive Buffer/Transmit Register |                    |                         |            |            |        |        |        | xxxx xxxx            | uuuu uuuu                       |

| SSPADD                | Synchronous                                              | Serial Por         | t (I <sup>2</sup> C mod | e) Address | s Register |        |        |        | 0000 0000            | 0000 0000                       |

| SSPCON                | WCOL                                                     | SSPOV              | SSPEN                   | CKP        | SSPM3      | SSPM2  | SSPM1  | SSPM0  | 0000 0000            | 0000 0000                       |

| SSPMSK <sup>(2)</sup> | Synchronous                                              | Serial Por         | t (I <sup>2</sup> C mod | e) Address | s Mask Re  | gister |        |        | 1111 1111            | 1111 1111                       |

| SSPSTAT               | SMP <sup>(1)</sup>                                       | CKE <sup>(1)</sup> | D/A                     | Р          | S          | R/W    | UA     | BF     | 0000 0000            | 0000 0000                       |

| TRISC                 | TRISC7                                                   | TRISC6             | TRISC5                  | TRISC4     | TRISC3     | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| المسمسيان             |                                                          |                    |                         |            |            |        |        |        |                      | 1 1 2 2                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in I<sup>2</sup>C mode.

**Note 1:** Maintain these bits clear in  $I^2C$  mode.

**2:** Accessible only when SSPM<3:0> = 1001.

# PIC16(L)F722/3/4/6/7

| SUBWF            | Subtract W                                                                                                                                                                        | from f   |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|

| Syntax:          | [label] SU                                                                                                                                                                        | JBWF f,d |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                   |          |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                             |          |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                          |          |  |  |  |

| Description:     | on: Subtract (2's complement me<br>W register from register 'f'. If '<br>'0', the result is stored in the V<br>register. If 'd' is '1', the result<br>stored back in register 'f. |          |  |  |  |

|                  | <b>C</b> = 0                                                                                                                                                                      | W > f    |  |  |  |

|                  | <b>C</b> = 1                                                                                                                                                                      | W≤f      |  |  |  |

$\overline{DC} = 0$

**DC** = 1

W<3:0> > f<3:0> W<3:0>  $\leq$  f<3:0>

| XORLW            | Exclusive OR literal with W                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] XORLW k                                                                                                        |

| Operands:        | $0 \le k \le 255$                                                                                                      |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                          |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of the W register<br>are XOR'ed with the 8-bit<br>literal 'k'. The result is placed in<br>the W register. |

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                      |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                |

| Status Affected: | None                                                                                                                                                                   |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                      |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                 |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |

## 22.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 22.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

## 23.7 AC Characteristics: PIC16F72X-I/E

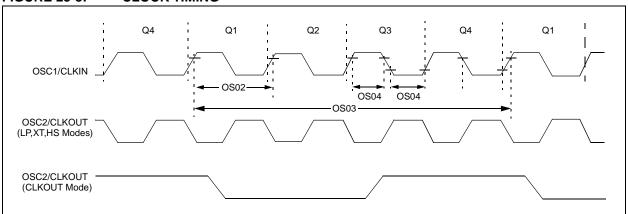

## FIGURE 23-3: CLOCK TIMING

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |       |                                         |      |        |        |       |                    |

|----------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------|------|--------|--------|-------|--------------------|

| Param<br>No.                                                                                                         | Sym.  | Characteristic                          | Min. | Тур†   | Max.   | Units | Conditions         |

| OS01                                                                                                                 | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC   | _      | 37     | kHz   | LP Oscillator mode |

|                                                                                                                      |       |                                         | DC   | _      | 4      | MHz   | XT Oscillator mode |

|                                                                                                                      |       |                                         | DC   | _      | 20     | MHz   | HS Oscillator mode |

|                                                                                                                      |       |                                         | DC   | _      | 20     | MHz   | EC Oscillator mode |

| Osci                                                                                                                 |       | Oscillator Frequency <sup>(1)</sup>     | —    | 32.768 | —      | kHz   | LP Oscillator mode |

|                                                                                                                      |       |                                         | 0.1  | _      | 4      | MHz   | XT Oscillator mode |

|                                                                                                                      |       |                                         | 1    | _      | 20     | MHz   | HS Oscillator mode |

|                                                                                                                      |       |                                         | DC   | _      | 4      | MHz   | RC Oscillator mode |

| OS02 1                                                                                                               | Tosc  | External CLKIN Period <sup>(1)</sup>    | 27   | —      | ×      | μs    | LP Oscillator mode |

|                                                                                                                      |       |                                         | 250  | _      | ×      | ns    | XT Oscillator mode |

|                                                                                                                      |       |                                         | 50   | _      | ×      | ns    | HS Oscillator mode |

|                                                                                                                      |       |                                         | 50   | _      | ×      | ns    | EC Oscillator mode |

|                                                                                                                      |       | Oscillator Period <sup>(1)</sup>        | —    | 30.5   | —      | μs    | LP Oscillator mode |

|                                                                                                                      |       |                                         | 250  | _      | 10,000 | ns    | XT Oscillator mode |

|                                                                                                                      |       |                                         | 50   | _      | 1,000  | ns    | HS Oscillator mode |

|                                                                                                                      |       |                                         | 250  | _      | —      | ns    | RC Oscillator mode |

| OS03                                                                                                                 | Тсү   | Instruction Cycle Time <sup>(1)</sup>   | 200  | Тсү    | DC     | ns    | TCY = 4/FOSC       |

| OS04*                                                                                                                | TosH, | External CLKIN High,                    | 2    | —      | —      | μS    | LP oscillator      |

|                                                                                                                      | TosL  | External CLKIN Low                      | 100  | —      | —      | ns    | XT oscillator      |

|                                                                                                                      |       |                                         | 20   | —      | —      | ns    | HS oscillator      |

| OS05*                                                                                                                | TosR, | External CLKIN Rise,                    | 0    | —      | ×      | ns    | LP oscillator      |

|                                                                                                                      | TosF  | External CLKIN Fall                     | 0    | —      | ×      | ns    | XT oscillator      |

|                                                                                                                      |       |                                         | 0    | —      | ×      | ns    | HS oscillator      |

## TABLE 23-1: CLOCK OSCILLATOR TIMING REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

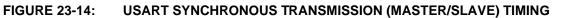

## TABLE 23-9: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                              |                                   |                |     |      |       |            |

|----------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------|----------------|-----|------|-------|------------|

| Param.<br>No.                                                                                                        | Symbol                       | Characteristic                    | Characteristic |     | Max. | Units | Conditions |

| US120                                                                                                                | TCKH2DTV                     | SYNC XMIT (Master and Slave)      | 3.0-5.5V       | —   | 80   | ns    |            |

|                                                                                                                      | Clock high to data-out valid | 1.8-5.5V                          | _              | 100 | ns   |       |            |

| US121                                                                                                                | TCKRF                        | Clock out rise time and fall time | 3.0-5.5V       | _   | 45   | ns    |            |

|                                                                                                                      | (Master mode)                | 1.8-5.5V                          | _              | 50  | ns   |       |            |

| US122                                                                                                                | TDTRF                        | Data-out rise time and fall time  | 3.0-5.5V       | _   | 45   | ns    |            |

|                                                                                                                      |                              | 1.8-5.5V                          | _              | 50  | ns   |       |            |

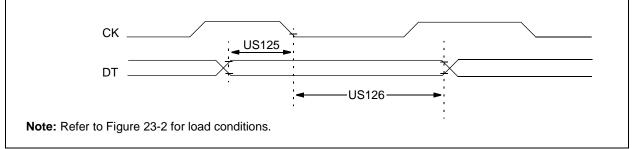

## FIGURE 23-15: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

10

15

ns

ns

## TABLE 23-10: USART SYNCHRONOUS RECEIVE REQUIREMENTS

Data-hold before  $CK \downarrow (DT hold time)$

Data-hold after  $CK \downarrow (DT hold time)$

# Standard Operating Conditions (unless otherwise stated) Operating Temperature -40°C ≤ TA ≤ +125°C Param. Symbol Characteristic Min. Max. Units Conditions US125 TDTV2CKL SYNC RCV (Master and Slave) Image: Condition state s

US126

TCKL2DTL

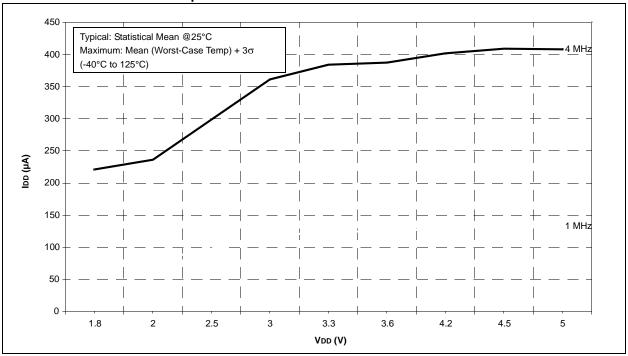

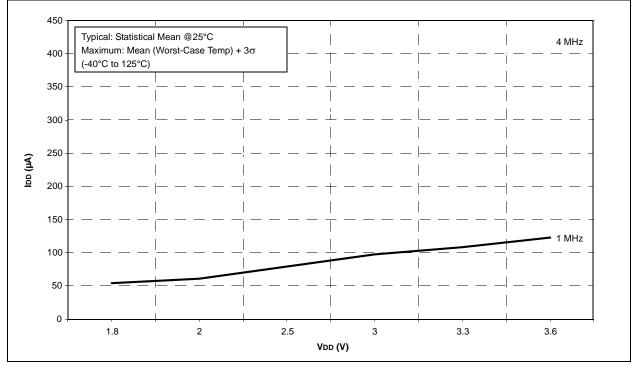

## FIGURE 24-7: PIC16F722/3/4/6/7 TYPICAL IDD vs. VDD OVER Fosc, EXTRC MODE, VCAP = $0.1 \mu$ F

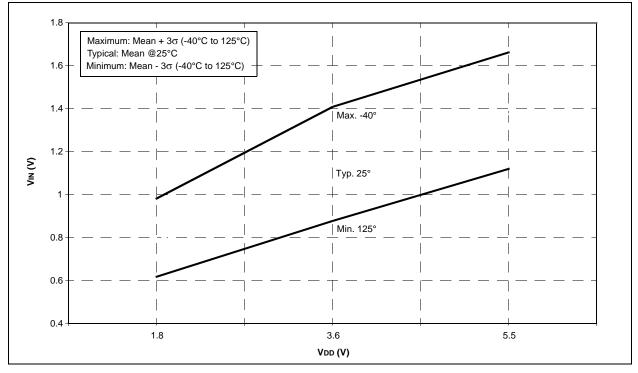

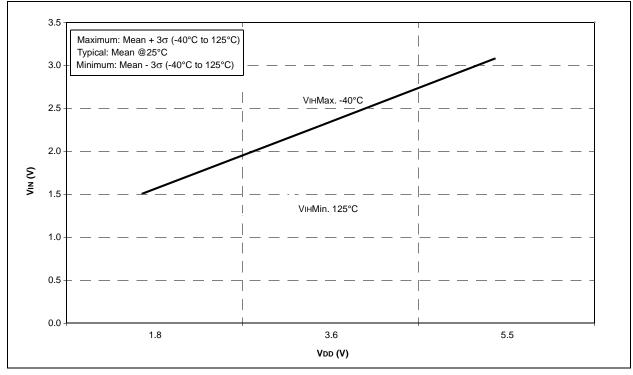

## FIGURE 24-49: TTL INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

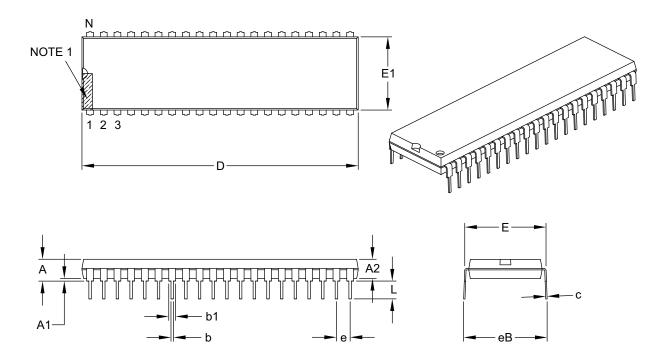

## 40-Lead Plastic Dual In-Line (P) – 600 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |          | INCHES |       |  |

|----------------------------|------------------|----------|--------|-------|--|

| Dimensior                  | Dimension Limits |          | NOM    | MAX   |  |

| Number of Pins             | Ν                | 40       |        |       |  |

| Pitch                      | е                | .100 BSC |        |       |  |

| Top to Seating Plane       | Α                | -        | -      | .250  |  |

| Molded Package Thickness   | A2               | .125     | -      | .195  |  |

| Base to Seating Plane      | A1               | .015     | -      | -     |  |

| Shoulder to Shoulder Width | E                | .590     | -      | .625  |  |

| Molded Package Width       | E1               | .485     | -      | .580  |  |

| Overall Length             | D                | 1.980    | -      | 2.095 |  |

| Tip to Seating Plane       | L                | .115     | -      | .200  |  |

| Lead Thickness             | С                | .008     | -      | .015  |  |

| Upper Lead Width           | b1               | .030     | -      | .070  |  |

| Lower Lead Width           | b                | .014     | -      | .023  |  |

| Overall Row Spacing §      | eB               | _        | _      | .700  |  |

### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-016B