Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I²C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 25                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 11x8b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-UFQFN Exposed Pad                                                     |

| Supplier Device Package    | 28-UQFN (4x4)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f723-e-mv |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### FIGURE 2-4:

# PIC16F722/LF722 SPECIAL FUNCTION REGISTERS

| Indirect addr. <sup>(*)</sup> | 00h    | Indirect addr. <sup>(*)</sup> | 80h      | Indirect addr. <sup>(*)</sup> | 100h | Indirect addr.(*) | 180h |

|-------------------------------|--------|-------------------------------|----------|-------------------------------|------|-------------------|------|

| TMR0                          | 01h    | OPTION                        | 81h      | TMR0                          | 101h | OPTION            | 181h |

| PCL                           | 02h    | PCL                           | 82h      | PCL                           | 102h | PCL               | 182h |

| STATUS                        | 03h    | STATUS                        | 83h      | STATUS                        | 103h | STATUS            | 183h |

| FSR                           | 04h    | FSR                           | 84h      | FSR                           | 104h | FSR               | 184h |

| PORTA                         | 05h    | TRISA                         | 85h      |                               | 105h | ANSELA            | 185h |

| PORTB                         | 06h    | TRISB                         | 86h      |                               | 106h | ANSELB            | 186h |

| PORTC                         | 07h    | TRISC                         | 87h      |                               | 107h |                   | 187h |

|                               | 08h    | -                             | 88h      | CPSCON0                       | 108h |                   | 188h |

| PORTE                         | 09h    | TRISE                         | 89h      | CPSCON1                       | 109h |                   | 189h |

| PCLATH                        | 0Ah    | PCLATH                        | 8Ah      | PCLATH                        | 10Ah | PCLATH            | 18Ah |

| INTCON                        | 0Bh    | INTCON                        | 8Bh      | INTCON                        | 10Bh | INTCON            | 18Bh |

| PIR1                          | 0Ch    | PIE1                          | 8Ch      | PMDATL                        | 10Ch | PMCON1            | 18Ch |

| PIR2                          | 0Dh    | PIE2                          | 8Dh      | PMADRL                        | 10Dh | Reserved          | 18Dh |

| TMR1L                         | 0Eh    | PCON                          | 8Eh      | PMDATH                        | 10Eh | Reserved          | 18Eh |

| TMR1H                         | 0Fh    | T1GCON                        | 8Fh      | PMADRH                        | 10Fh | Reserved          | 18Fh |

| T1CON                         | 10h    | OSCCON                        | 90h      |                               | 110h |                   | 190h |

| TMR2                          | 11h    | OSCTUNE                       | 91h      |                               | 111h |                   | 191h |

| T2CON                         | 12h    | PR2                           | 92h      |                               | 112h |                   | 192h |

| SSPBUF                        | 13h    | SSPADD/SSPMSK                 | 93h      |                               | 113h |                   | 193h |

| SSPCON                        | 14h    | SSPSTAT                       | 94h      |                               | 114h |                   | 194h |

| CCPR1L                        | 15h    | WPUB                          | 95h      |                               | 115h |                   | 195h |

| CCPR1H                        | 16h    | IOCB                          | 96h      |                               | 116h |                   | 196h |

| CCP1CON                       | 17h    | -                             | 97h      |                               | 117h |                   | 197h |

| RCSTA                         | 18h    | TXSTA                         | 98h      |                               | 118h |                   | 198h |

| TXREG                         | 19h    | SPBRG                         | 99h      |                               | 119h |                   | 199h |

| RCREG                         | 1Ah    |                               | 9Ah      |                               | 11Ah |                   | 19Ah |

| CCPR2L                        | 1Bh    |                               | 9Bh      |                               | 11Bh |                   | 19Bh |

| CCPR2H                        | 1Ch    | APFCON                        | 9Ch      |                               | 11Ch |                   | 19Ch |

| CCP2CON                       | 1Dh    | FVRCON                        | 9Dh      |                               | 11Dh |                   | 19Dh |

| ADRES                         | 1Eh    |                               | 9Eh      |                               | 11Eh |                   | 19Eh |

| ADCON0                        | 1Fh    | ADCON1                        | 9Fh      |                               | 11Fh |                   | 19Fh |

|                               | 20h    | -                             | A0h      |                               | 120h |                   | 1A0h |

|                               |        | General                       |          |                               |      |                   |      |

|                               |        | Purpose                       |          |                               |      |                   |      |

|                               |        | Register                      |          |                               |      |                   |      |

| General                       |        | 32 Bytes                      |          |                               |      |                   |      |

| Purpose                       |        |                               | BFh      |                               |      |                   |      |

| Register                      |        |                               | C0h      |                               |      |                   |      |

| 96 Bytes                      |        |                               | EFh      |                               | 16Fh |                   | 1EFh |

|                               |        |                               | F0h      |                               | 170h |                   | 1F0h |

|                               |        | Accesses                      |          | Accesses                      |      | Accesses          |      |

|                               |        | 70h-7Fh                       |          | 70h-7Fh                       |      | 70h-7Fh           |      |

|                               | 7Fh    |                               | FFh      |                               | 17Fh |                   | 1FFh |

| Bank 0                        | 1,411  | Bank 1                        |          | Bank 2                        |      | Bank 3            |      |

| Dalik U                       |        | Ddiik I                       |          | Dalik Z                       |      | Dalik J           |      |

| gend: = Un                    | implem | ented data memory lo          | cations. | read as '0'.                  |      |                   |      |

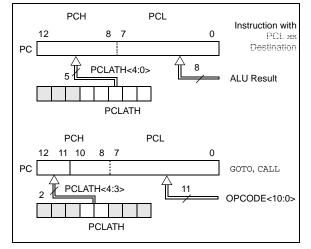

# 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-7 shows the two situations for the loading of the PC. The upper example in Figure 2-7 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-7 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 2-7: LOADING OF PC IN DIFFERENT SITUATIONS

# 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the Application Note *AN556, Implementing a Table Read* (DS00556).

# 2.3.2 STACK

All devices have an 8-level x 13-bit wide hardware stack (refer to Figures 2-1 and 2-3). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth PUSH overwrites the value that was stored from the first PUSH. The tenth PUSH overwrites the second PUSH (and so on).

- Note 1: There are no Status bits to indicate Stack Overflow or Stack Underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

# 2.4 **Program Memory Paging**

All devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper two bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is POPed off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the RETURN instructions (which POPs the address from the stack).

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 500 | h       |                     |

|---------|---------|---------|---------------------|

|         | PAGESEL | SUB_P1  | ;Select page 1      |

|         |         |         | ;(800h-FFFh)        |

|         | CALL    | SUB1_P1 | ;Call subroutine in |

|         | :       |         | ;page 1 (800h-FFFh) |

|         | :       |         |                     |

|         | ORG     | 900h    | ;page 1 (800h-FFFh) |

| SUB1_P1 |         |         |                     |

|         | :       |         | ;called subroutine  |

|         |         |         | ;page 1 (800h-FFFh) |

|         | :       |         |                     |

|         | RETURN  |         | ;return to          |

|         |         |         | ;Call subroutine    |

|         |         |         | ;in page 0          |

|         |         |         | ;(000h-7FFh)        |

Note: The contents of the PCLATH register are unchanged after a RETURN or RETFIE instruction is executed. The user must rewrite the contents of the PCLATH register for any subsequent subroutine calls or GOTO instructions.

#### EXAMPLE 4-1: SAVING W, STATUS AND PCLATH REGISTERS IN RAM

| MOVWF<br>SWAPF          | W_TEMP<br>STATUS,W                                      | ;Copy W to W_TEMP register<br>;Swap status to be saved into W<br>;Swaps are used because they do not affect the status bits                           |

|-------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVWF<br>MOVF           | STATUS_TEMP<br>STATUS_TEMP<br>PCLATH,W<br>PCLATH_TEMP   | ;Select regardless of current bank<br>;Copy status to bank zero STATUS_TEMP register<br>;Copy PCLATH to W register<br>;Copy W register to PCLATH_TEMP |

| :(ISR)<br>:             |                                                         | ;Insert user code here                                                                                                                                |

| MOVF                    | STATUS_TEMP<br>PCLATH_TEMP,W<br>PCLATH<br>STATUS_TEMP,W | ;Select regardless of current bank<br>;<br>;Restore PCLATH<br>;Swap STATUS_TEMP register into W<br>;(sets bank to original state)                     |

| MOVWF<br>SWAPF<br>SWAPF | STATUS<br>W_TEMP,F<br>W_TEMP,W                          | ;Move W into STATUS register<br>;Swap W_TEMP<br>;Swap W_TEMP into W                                                                                   |

# 4.5.1 INTCON REGISTER

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, PORTB change and external RB0/INT/SEG0 pin interrupts.

```

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

```

| R/W-1           | R/W-1                             | R/W-1            | R/W-1                              | R/W-1                               | R/W-1 | R/W-1 | R/W-1 |

|-----------------|-----------------------------------|------------------|------------------------------------|-------------------------------------|-------|-------|-------|

| WPUB7           | WPUB6                             | WPUB5            | WPUB4                              | WPUB3                               | WPUB2 | WPUB1 | WPUB0 |

| bit 7           |                                   |                  |                                    |                                     |       | bit 0 |       |

|                 |                                   |                  |                                    |                                     |       |       |       |

| Legend:         |                                   |                  |                                    |                                     |       |       |       |

| R = Readable    | R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                                     |       |       |       |

| -n = Value at P | OR                                | '1' = Bit is set |                                    | '0' = Bit is cleared x = Bit is unl |       | nown  |       |

# REGISTER 6-7: WPUB: WEAK PULL-UP PORTB REGISTER

bit 7-0 WPUB<7:0>: Weak Pull-up Register bits

- 1 = Pull-up enabled

- 0 = Pull-up disabled

**Note 1:** Global RBPU bit of the OPTION register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

# REGISTER 6-8: IOCB: INTERRUPT-ON-CHANGE PORTB REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IOCB7 | IOCB6 | IOCB5 | IOCB4 | IOCB3 | IOCB2 | IOCB1 | IOCB0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 **IOCB<7:0>:** Interrupt-on-Change PORTB Control bits

1 = Interrupt-on-change enabled

0 = Interrupt-on-change disabled

# REGISTER 6-9: ANSELB: PORTB ANALOG SELECT REGISTER

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | ANSB5 | ANSB4 | ANSB3 | ANSB2 | ANSB1 | ANSB0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 ANSB<5:0>: Analog Select between Analog or Digital Function on Pins RB<5:0>, respectively

0 = Digital I/O. Pin is assigned to port or Digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital Input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| REGISTER 6-13: | TRISD: PORTD TRI-STATE REGISTER <sup>(1)</sup> |

|----------------|------------------------------------------------|

|                |                                                |

| TRISD7         TRISD6         TRISD5         TRISD4         TRISD3         TRISD2         TRISD1         TRISD0           bit 7         bit 0 | R/W-1  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| bit 7 bit 0                                                                                                                                   | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 |

|                                                                                                                                               | bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0

**TRISD<7:0>:** PORTD Tri-State Control bits 1 = PORTD pin configured as an input (tri-stated) 0 = PORTD pin configured as an output

Note 1: TRISD is not implemented on PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'.

# REGISTER 6-14: ANSELD: PORTD ANALOG SELECT REGISTER<sup>(2)</sup>

| R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ANSD7 | ANSD6 | ANSD5 | ANSD4 | ANSD3 | ANSD2 | ANSD1 | ANSD0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 **ANSD<7:0>**: Analog Select between Analog or Digital Function on Pins RD<7:0>, respectively 0 = Digital I/O. Pin is assigned to port or Digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital Input buffer disabled.

- **Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

- 2: ANSELD register is not implemented on the PIC16F722/723/726/PIC16LF722/723/726. Read as '0'.

Note: PORTD is available on PIC16F724/LF724 and PIC16F727/LF727 only.

# 6.5.2 RD0/CPS8

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

# 6.5.3 RD1/CPS9

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

# 6.5.4 RD2/CPS10

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

# 6.5.5 RD3/CPS11

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

# REGISTER 8-1: CONFIG1: CONFIGURATION WORD REGISTER 1 (CONTINUED)

- bit 4 **PWRTE:** Power-up Timer Enable bit 1 = PWRT disabled

- 1 = PWRT disabled0 = PWRT enabled

- bit 3 WDTE: Watchdog Timer Enable bit 1 = WDT enabled

- 1 = WDT enabled0 = WDT disabled

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = RC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, RC on RA7/OSC1/CLKIN

- 110 = RCIO oscillator: I/O function on RA6/OSC2/CLKOUT pin, RC on RA7/OSC1/CLKIN

- 101 = INTOSC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN

- 100 = INTOSCIO oscillator: I/O function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN

- 011 = EC: I/O function on RA6/OSC2/CLKOUT pin, CLKIN on RA7/OSC1/CLKIN

- 010 = HS oscillator: High-speed crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN

- 001 = XT oscillator: Crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN

- 000 = LP oscillator: Low-power crystal on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN

Note 1: Enabling Brown-out Reset does not automatically enable Power-up Timer.

- 2: The entire program memory will be erased when the code protection is turned off.

- 3: When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.

- 4: MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

# REGISTER 8-2: CONFIG2: CONFIGURATION WORD REGISTER 2

|        |   |   | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> |

|--------|---|---|--------------------|--------------------|--------------------|--------------------|

|        | — | _ | _                  | —                  | —                  | —                  |

| bit 15 |   |   |                    |                    |                    | bit 8              |

| U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | R/P-1   | R/P-1   | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> |

|--------------------|--------------------|---------|---------|--------------------|--------------------|--------------------|--------------------|

| —                  | —                  | VCAPEN1 | VCAPEN0 | —                  | —                  | _                  | —                  |

| bit 7              |                    |         |         |                    |                    |                    | bit 0              |

| Legend:           | P = Programmable bit |                             |                    |

|-------------------|----------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared        | x = Bit is unknown |

bit 13-6 Unimplemented: Read as '1'

bit 5-4 VCAPEN<1:0>: Voltage Regulator Capacitor Enable bits For the PIC16LF72X: These bits are ignored. All VCAP pin functions are disabled. For the PIC16F72X: 00 = VCAP functionality is enabled on RA0 01 = VCAP functionality is enabled on RA5 10 = VCAP functionality is enabled on RA6 11 = All VCAP functions are disabled (not recommended) bit 3-0 Unimplemented: Read as '1'

**Note 1:** MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

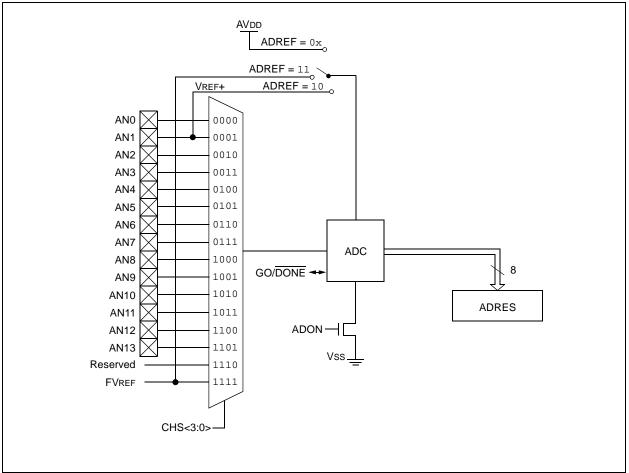

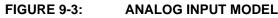

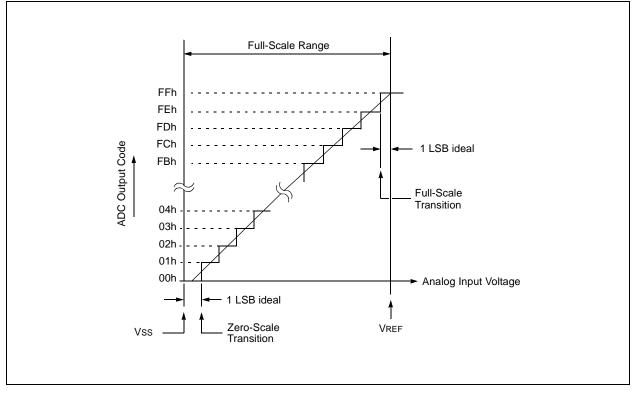

# 9.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 8-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 8-bit binary result via successive approximation and stores the conversion result into the ADC result register (ADRES). Figure 9-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

# FIGURE 9-1: ADC BLOCK DIAGRAM

# PIC16(L)F722/3/4/6/7

# 11.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the OPTION register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

| Note: | When the prescaler is assigned to WDT, a    |

|-------|---------------------------------------------|

|       | CLRWDT instruction will clear the prescaler |

|       | along with the WDT.                         |

# 11.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The T0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The T0IF bit can only be cleared in software. The Timer0 interrupt enable is the T0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |

|-------|-----------------------------------------|

|       | processor from Sleep since the timer is |

|       | frozen during Sleep.                    |

# 11.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 23.0** "**Electrical Specifications**".

# 12.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# 12.4 Timer1 Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

| Note: | The oscillator requires a start-up and   |

|-------|------------------------------------------|

|       | stabilization time before use. Thus,     |

|       | T1OSCEN should be set and a suitable     |

|       | delay observed prior to enabling Timer1. |

# 12.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 12.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

# 12.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

# 12.11 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 12-1, is used to control Timer1 and select the various features of the Timer1 module.

# REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0         | U-0 | R/W-0  |

|---------|---------|---------|---------|---------|---------------|-----|--------|

| TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | T1OSCEN | <b>T1SYNC</b> | —   | TMR10N |

| bit 7   |         |         |         |         |               |     | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7-6 | TMR1CS<1:0>: Timer1 Clock Source Select bits                                                                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------|

|         | 11 = Timer1 clock source is Capacitive Sensing Oscillator (CAPOSC)                                                                     |

|         | 10 = Timer1 clock source is pin or oscillator:                                                                                         |

|         | <u>If T1OSCEN = 0</u> :<br>External clock from T1CKI pin (on the rising edge)                                                          |

|         | $\frac{1}{10000000000000000000000000000000000$                                                                                         |

|         | Crystal oscillator on T1OSI/T1OSO pins                                                                                                 |

|         | 01 = Timer1 clock source is system clock (Fosc)                                                                                        |

|         | 00 = Timer1 clock source is instruction clock (Fosc/4)                                                                                 |

| bit 5-4 | T1CKPS<1:0>: Timer1 Input Clock Prescale Select bits                                                                                   |

|         | 11 = 1:8 Prescale value                                                                                                                |

|         | 10 = 1:4 Prescale value<br>01 = 1:2 Prescale value                                                                                     |

|         | 00 = 1:1 Prescale value                                                                                                                |

| bit 3   | T10SCEN: LP Oscillator Enable Control bit                                                                                              |

|         | 1 = Dedicated Timer1 oscillator circuit enabled                                                                                        |

|         | 0 = Dedicated Timer1 oscillator circuit disabled                                                                                       |

| bit 2   | T1SYNC: Timer1 External Clock Input Synchronization Control bit                                                                        |

|         | $\underline{TMR1CS<1:0>} = \underline{1X}$                                                                                             |

|         | <ul> <li>1 = Do not synchronize external clock input</li> <li>0 = Synchronize external clock input with system clock (Fosc)</li> </ul> |

|         | 0 = Synchronize external clock input with system clock (FOSC)                                                                          |

|         | <u>TMR1CS&lt;1:0&gt; = 0X</u>                                                                                                          |

|         | This bit is ignored. Timer1 uses the internal clock when $TMR1CS<1:0 > = 1X$ .                                                         |

| bit 1   | Unimplemented: Read as '0'                                                                                                             |

| bit 0   | TMR1ON: Timer1 On bit                                                                                                                  |

|         | 1 = Enables Timer1                                                                                                                     |

|         | 0 = Stops Timer1                                                                                                                       |

|         | Clears Timer1 Gate flip-flop                                                                                                           |

# 14.5 Software Control

The software portion of the capacitive sensing module is required to determine the change in frequency of the capacitive sensing oscillator. This is accomplished by the following:

- Setting a fixed time base to acquire counts on Timer0 or Timer1

- Establishing the nominal frequency for the capacitive sensing oscillator

- Establishing the reduced frequency for the capacitive sensing oscillator due to an additional capacitive load

- Set the frequency threshold

# 14.5.1 NOMINAL FREQUENCY (NO CAPACITIVE LOAD)

To determine the nominal frequency of the capacitive sensing oscillator:

- Remove any extra capacitive load on the selected CPSx pin

- At the start of the fixed time base, clear the timer resource

- At the end of the fixed time base save the value in the timer resource

The value of the timer resource is the number of oscillations of the capacitive sensing oscillator for the given time base. The frequency of the capacitive sensing oscillator is equal to the number of counts on in the timer divided by the period of the fixed time base.

# 14.5.2 REDUCED FREQUENCY (ADDITIONAL CAPACITIVE LOAD)

The extra capacitive load will cause the frequency of the capacitive sensing oscillator to decrease. To determine the reduced frequency of the capacitive sensing oscillator:

- Add a typical capacitive load on the selected CPSx pin

- Use the same fixed-time base as the nominal frequency measurement

- At the start of the fixed-time base, clear the timer resource

- At the end of the fixed-time base save the value in the timer resource

The value of the timer resource is the number of oscillations of the capacitive sensing oscillator with an additional capacitive load. The frequency of the capacitive sensing oscillator is equal to the number of counts on in the timer divided by the period of the fixed time base. This frequency should be less than the value obtained during the nominal frequency measurement.

# 14.5.3 FREQUENCY THRESHOLD

The frequency threshold should be placed midway between the value of nominal frequency and the reduced frequency of the capacitive sensing oscillator. Refer to Application Note AN1103, *Software Handling for Capacitive Sensing* (DS01103) for more detailed information the software required for capacitive sensing module.

| Note: | For more      |  | information |       | 0  | n general   |

|-------|---------------|--|-------------|-------|----|-------------|

|       | Capa<br>Notes |  | Sensing     | refer | to | Application |

- AN1101, Introduction to Capacitive Sensing (DS01101)

- AN1102, Layout and Physical Design Guidelines for Capacitive Sensing (DS01102).

# PIC16(L)F722/3/4/6/7

| FIGURE 16-8:                | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                                 |

|-----------------------------|-------------------------------------------------------------------------------------------|

| RX/DT<br>pin                | bit 0         bit 2         bit 3         bit 4         bit 5         bit 6         bit 7 |

| TX/CK pin                   |                                                                                           |

| Write to<br>bit SREN        |                                                                                           |

| SREN bit                    |                                                                                           |

| CREN bit                    | ʻ0'                                                                                       |

| RCIF bit<br>(Interrupt) ——— |                                                                                           |

| Read<br>RCREG               |                                                                                           |

| Note: Timing d              | iagram demonstrates Synchronous Master mode with bit SREN = $1$ and bit BRGH = $0$ .      |

| Name   | Bit 7                              | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|------------------------------------|--------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE                                | PEIE   | TOIE   | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE                            | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF                            | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCREG  | RCREG AUSART Receive Data Register |        |        |        |        |        |        |        |                      | 0000 0000                       |

| RCSTA  | SPEN                               | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| TRISC  | TRISC7                             | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC                               | TX9    | TXEN   | SYNC   | _      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

# TABLE 16-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Reception.

# 17.2.2 START AND STOP CONDITIONS

During times of no data transfer (Idle time), both the clock line (SCL) and the data line (SDA) are pulled high through external pull-up resistors. The Start and Stop conditions determine the start and stop of data transmission. The Start condition is defined as a high-to-low transition of the SDA line while SCL is high. The Stop condition is defined as a low-to-high transition of the SDA line while SCL is high.

Figure 17-9 shows the Start and Stop conditions. A master device generates these conditions for starting and terminating data transfer. Due to the definition of the Start and Stop conditions, when data is being transmitted, the SDA line can only change state when the SCL line is low.

# 17.2.3 ACKNOWLEDGE

After the valid reception of an address or data byte, the hardware automatically will generate the Acknowledge (ACK) pulse and load the SSPBUF register with the received value currently in the SSPSR register. There are certain conditions that will cause the SSP module not to generate this ACK pulse. They include any or all of the following:

- The Buffer Full bit, BF of the SSPSTAT register, was set before the transfer was received.

- The SSP Overflow bit, SSPOV of the SSPCON register, was set before the transfer was received.

- The SSP Module is being operated in Firmware Master mode.

In such a case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF of the PIR1 register is set. Table 17-2 shows the results of when a data transfer byte is received, given the status of bits BF and SSPOV. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

# FIGURE 17-9: START AND STOP CONDITIONS

|  | TABLE 17-2: | DATA TRANSFER RECEIVED BYTE ACTIONS |

|--|-------------|-------------------------------------|

|--|-------------|-------------------------------------|

|    | ts as Data<br>s Received | $SSPSR \to SSPBUF$ | Generate ACK | Set bit SSPIF<br>(SSP Interrupt occurs |

|----|--------------------------|--------------------|--------------|----------------------------------------|

| BF | SSPOV                    |                    | Pulse        | if enabled)                            |

| 0  | 0                        | Yes                | Yes          | Yes                                    |

| 1  | 0                        | No                 | No           | Yes                                    |

| 1  | 1                        | No                 | No           | Yes                                    |

| 0  | 1                        | No                 | No           | Yes                                    |

Note 1: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

| Mnemonic,<br>Operands |      | Description                                      |              |       | 14-Bit | Opcode | Status | Natas    |         |

|-----------------------|------|--------------------------------------------------|--------------|-------|--------|--------|--------|----------|---------|

|                       |      |                                                  |              | MSb   |        |        | LSb    | Affected | Notes   |

|                       |      | BYTE-ORIENTED FILE                               | REGISTER OPE | RATIC | ONS    |        |        |          |         |

| ADDWF                 | f, d | Add W and f                                      | 1            | 00    | 0111   | dfff   | ffff   | C, DC, Z | 1, 2    |

| ANDWF                 | f, d | AND W with f                                     | 1            | 00    | 0101   | dfff   | ffff   | Z        | 1, 2    |

| CLRF                  | f    | Clear f                                          | 1            | 00    | 0001   | lfff   | ffff   | Z        | 2       |

| CLRW                  | -    | Clear W                                          | 1            | 00    | 0001   | 0xxx   | xxxx   | Z        |         |

| COMF                  | f, d | Complement f                                     | 1            | 00    | 1001   | dfff   | ffff   | Z        | 1, 2    |

| DECF                  | f, d | Decrement f                                      | 1            | 00    | 0011   | dfff   | ffff   | Z        | 1, 2    |

| DECFSZ                | f, d | Decrement f, Skip if 0                           | 1 <b>(2)</b> | 00    | 1011   | dfff   | ffff   |          | 1, 2, 3 |

| INCF                  | f, d | Increment f                                      | 1            | 00    | 1010   | dfff   | ffff   | Z        | 1, 2    |

| INCFSZ                | f, d | Increment f, Skip if 0                           | 1 <b>(2)</b> | 00    | 1111   | dfff   | ffff   |          | 1, 2, 3 |

| IORWF                 | f, d | Inclusive OR W with f                            | 1            | 00    | 0100   | dfff   | ffff   | Z        | 1, 2    |

| MOVF                  | f, d | Move f                                           | 1            | 00    | 1000   | dfff   | ffff   | Z        | 1, 2    |

| MOVWF                 | f    | Move W to f                                      | 1            | 00    | 0000   | lfff   | ffff   |          | -       |

| NOP                   | -    | No Operation                                     | 1            | 00    | 0000   | 0xx0   | 0000   |          |         |

| RLF                   | f, d | Rotate Left f through Carry                      | 1            | 00    | 1101   | dfff   | ffff   | С        | 1, 2    |

| RRF                   | f, d | Rotate Right f through Carry                     | 1            | 00    | 1100   | dfff   | ffff   | С        | 1, 2    |

| SUBWF                 | f, d | Subtract W from f                                | 1            | 00    | 0010   | dfff   | ffff   | C, DC, Z | 1, 2    |

| SWAPF                 | f, d | Swap nibbles in f                                | 1            | 00    | 1110   | dfff   | ffff   |          | 1, 2    |

| XORWF                 | f, d | Exclusive OR W with f                            | 1            | 00    | 0110   | dfff   | ffff   | Z        | 1, 2    |

|                       |      | BIT-ORIENTED FILE R                              | EGISTER OPER | RATIO | NS     |        |        |          |         |

| BCF                   | f, b | Bit Clear f                                      | 1            | 01    | 00bb   | bfff   | ffff   |          | 1, 2    |

| BSF                   | f, b | Bit Set f                                        | 1            | 01    |        | bfff   | ffff   |          | 1, 2    |

| BTFSC                 | f, b | Bit Test f, Skip if Clear                        | 1 <b>(2)</b> | 01    | 10bb   | bfff   | ffff   |          | 3       |

| BTFSS                 | f, b | Bit Test f, Skip if Set                          | 1 (2)        | 01    | 11bb   | bfff   | ffff   |          | 3       |

|                       |      | LITERAL AND CON                                  | ITROL OPERAT | IONS  |        |        |        |          |         |

| ADDLW                 | k    | Add literal and W                                | 1            | 11    | 111x   | kkkk   | kkkk   | C, DC, Z |         |

| ANDLW                 | k    | AND literal with W                               | 1            | 11    | 1001   | kkkk   | kkkk   | Z        |         |

| CALL                  | k    | Call Subroutine                                  | 2            | 10    | 0kkk   | kkkk   | kkkk   |          |         |

| CLRWDT                | -    | Clear Watchdog Timer                             | 1            | 00    | 0000   | 0110   | 0100   | TO, PD   |         |

| GOTO                  | k    | Go to address                                    | 2            | 10    | 1kkk   | kkkk   | kkkk   |          |         |

| IORLW                 | k    | Inclusive OR literal with W                      | 1            | 11    | 1000   | kkkk   | kkkk   | Z        |         |

| MOVLW                 | k    | Move literal to W                                | 1            | 11    | 00xx   | kkkk   | kkkk   |          |         |

| RETFIE                | -    | Return from interrupt                            | 2            | 00    | 0000   | 0000   | 1001   |          |         |

| RETLW                 | k    | Return with literal in W                         | 2            | 11    | 01xx   | kkkk   | kkkk   |          |         |

| RETURN                | -    | Return from Subroutine                           | 2            | 00    | 0000   | 0000   | 1000   |          |         |

| SLEEP                 | _    | Go into Standby mode                             | 1            | 00    | 0000   | 0110   | 0011   | TO, PD   |         |

| SUBLW                 | k    | Subtract W from literal                          | 1            | 11    |        | kkkk   |        | C, DC, Z |         |

| XORLW                 | k    | Exclusive OR literal with W                      | 1            | 11    |        | kkkk   |        | Z        |         |

| Noto 1                |      | 1/O register is modified as a function of itself |              | I     |        |        |        | I        | l       |

# TABLE 21-2: PIC16(L)F722/3/4/6/7 INSTRUCTION SET

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF PORTA, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

**3:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

# TABLE 23-5: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

Standard Operating Conditions (unless otherwise stated)

| Param<br>No. | Sym.      |                                     | Characteristic                                            |                | Min.                                      | Тур†   | Max. | Units               | Conditions                         |

|--------------|-----------|-------------------------------------|-----------------------------------------------------------|----------------|-------------------------------------------|--------|------|---------------------|------------------------------------|

| 40* T⊤0H     |           | T0CKI High Pulse Width No Prescaler |                                                           |                | 0.5 Tcy + 20                              | —      | _    | ns                  |                                    |

|              |           |                                     |                                                           | With Prescaler | 10                                        | _      | _    | ns                  |                                    |

| 41*          | TT0L      | T0CKI Low F                         | ulse Width                                                | No Prescaler   | 0.5 TCY + 20                              | —      | _    | ns                  |                                    |

|              |           |                                     |                                                           | With Prescaler | 10                                        | —      | _    | ns                  |                                    |

| 42*          | Тт0Р      | T0CKI Period                        | 1                                                         |                | Greater of:<br>20 or <u>Tcy + 40</u><br>N | —      | _    | ns                  | N = prescale value<br>(2, 4,, 256) |

| 45* T⊤1H     | T⊤1H      | T1CKI High                          | Synchronous, No Prescaler                                 |                | 0.5 TCY + 20                              | _      | _    | ns                  |                                    |

|              | Time      | Synchronous, with Prescaler         |                                                           | 15             | _                                         | _      | ns   |                     |                                    |

|              |           |                                     | Asynchronous                                              |                | 30                                        | —      | _    | ns                  |                                    |

| 46*          | T⊤1L      | T1CKI Low<br>Time                   | Synchronous, No Prescaler                                 |                | 0.5 TCY + 20                              | —      | _    | ns                  |                                    |

|              |           |                                     | Synchronous, with Prescaler                               |                | 15                                        | —      | _    | ns                  |                                    |

|              |           |                                     | Asynchronous                                              |                | 30                                        | —      | _    | ns                  |                                    |

| 47*          | TT1P      | T1CKI Input<br>Period               | Synchronous                                               | ,              |                                           | —      |      | ns                  | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                     | Asynchronous                                              | 3              | 60                                        | _      | _    | ns                  |                                    |

| 48           | F⊤1       |                                     | lator Input Frequency Range abled by setting bit T1OSCEN) |                | 32.4                                      | 32.768 | 33.1 | kHz                 |                                    |

| 49*          | TCKEZTMR1 | Delay from E<br>Increment           | xternal Clock E                                           | 2 Tosc         | —                                         | 7 Tosc | —    | Timers in Sync mode |                                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

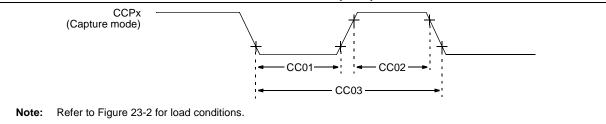

# FIGURE 23-11: CAPTURE/COMPARE/PWM TIMINGS (CCP)

# TABLE 23-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP)

|              | Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                      |                |                       |      |      |       |                                 |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|----------------------|----------------|-----------------------|------|------|-------|---------------------------------|--|--|--|

| Param<br>No. | Sym.                                                                                                                 | Characteristic       |                | Min.                  | Тур† | Max. | Units | Conditions                      |  |  |  |

| CC01*        | TccL                                                                                                                 | CCPx Input Low Time  | No Prescaler   | 0.5Tcy + 20           | _    | —    | ns    |                                 |  |  |  |

|              |                                                                                                                      |                      | With Prescaler | 20                    | _    | _    | ns    |                                 |  |  |  |

| CC02*        | TccH                                                                                                                 | CCPx Input High Time | No Prescaler   | 0.5TCY + 20           | _    | _    | ns    |                                 |  |  |  |

|              |                                                                                                                      |                      | With Prescaler | 20                    | _    | _    | ns    |                                 |  |  |  |

| CC03*        | TccP                                                                                                                 | CCPx Input Period    |                | <u>3Tcy + 40</u><br>N |      | _    | ns    | N = prescale value (1, 4 or 16) |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Param.<br>No. | Symbol                         | Symbol Characteri      |              | Min.       | Max. | Units | Conditions                                  |

|---------------|--------------------------------|------------------------|--------------|------------|------|-------|---------------------------------------------|

| SP100*        | Тнідн                          | Clock high time        | 100 kHz mode | 4.0        | —    | μs    | Device must operate at a minimum of 1.5 MHz |

|               |                                |                        | 400 kHz mode | 0.6        | _    | μs    | Device must operate at a minimum of 10 MHz  |

|               |                                |                        | SSP Module   | 1.5Tcy     | _    |       |                                             |

| SP101*        | TLOW                           | Clock low time         | 100 kHz mode | 4.7        | _    | μs    | Device must operate at a minimum of 1.5 MHz |

|               |                                |                        | 400 kHz mode | 1.3        | _    | μS    | Device must operate at a minimum of 10 MHz  |

|               |                                |                        | SSP Module   | 1.5Tcy     | _    |       |                                             |

| SP102*        | P102* TR SDA and SCL r<br>time | SDA and SCL rise       | 100 kHz mode | —          | 1000 | ns    |                                             |

|               |                                | time                   | 400 kHz mode | 20 + 0.1CB | 300  | ns    | CB is specified to be from 10-400 pF        |

| SP103*        | TF                             | SDA and SCL fall time  | 100 kHz mode | —          | 250  | ns    |                                             |

|               |                                |                        | 400 kHz mode | 20 + 0.1CB | 250  | ns    | CB is specified to be from 10-400 pF        |

| SP106*        | THD:DAT                        | Data input hold time   | 100 kHz mode | 0          |      | ns    |                                             |

|               |                                |                        | 400 kHz mode | 0          | 0.9  | μs    |                                             |

| SP107*        | TSU:DAT                        | Data input setup time  | 100 kHz mode | 250        |      | ns    | (Note 2)                                    |

|               |                                |                        | 400 kHz mode | 100        |      | ns    | -                                           |

| SP109*        | ΤΑΑ                            | Output valid from      | 100 kHz mode | —          | 3500 | ns    | (Note 1)                                    |

|               |                                | clock                  | 400 kHz mode | _          |      | ns    |                                             |

| SP110*        | TBUF                           | Bus free time          | 100 kHz mode | 4.7        | _    | μs    | Time the bus must be free                   |

|               |                                |                        | 400 kHz mode | 1.3        | —    | μs    | before a new transmission can start         |

| SP111         | Св                             | Bus capacitive loading |              | —          | 400  | pF    |                                             |

# TABLE 23-13: I<sup>2</sup>C BUS DATA REQUIREMENTS

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement TsU:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

# PIC16(L)F722/3/4/6/7

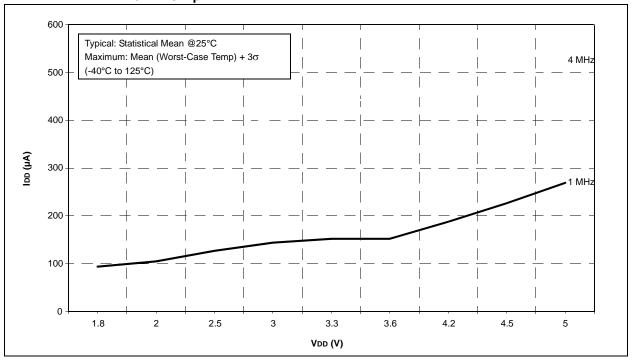

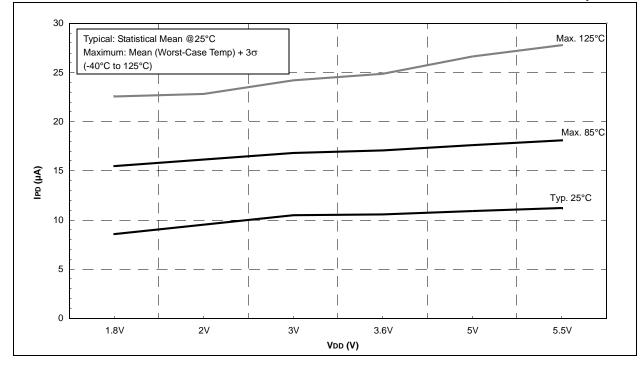

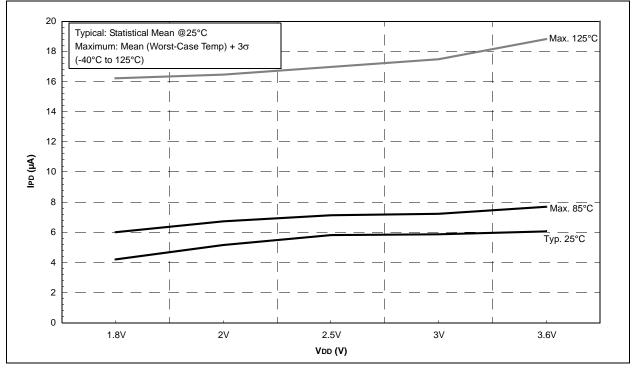

# FIGURE 24-5: PIC16F722/3/4/6/7 MAXIMUM IDD vs. VDD OVER Fosc, EXTRC MODE, VCAP = $0.1 \mu$ F

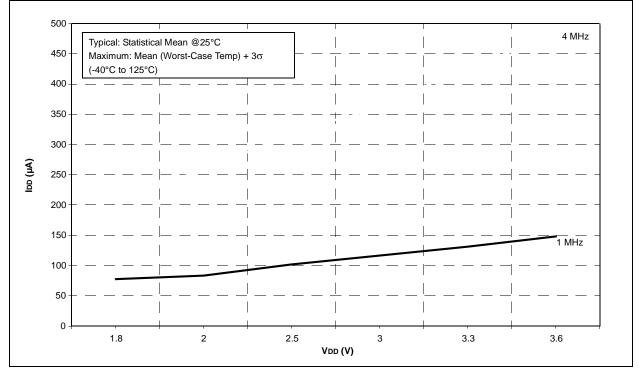

#### FIGURE 24-37: PIC16F722/3/4/6/7 CAP SENSE MEDIUM POWER IPD vs. VDD, VCAP = 0.1 µF

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, RightTouch logo, REAL ICE, SQI, Serial Quad I/O, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2007-2015, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0042-4

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.