Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 25                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 11x8b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-QFN (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f723-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                          | Function | Input<br>Type    | Output<br>Type | Description                                                                                          |

|-------------------------------|----------|------------------|----------------|------------------------------------------------------------------------------------------------------|

| RB4/AN11/CPS4                 | RB4      | TTL              | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |

|                               | AN11     | AN               | _              | A/D Channel 11 input.                                                                                |

|                               | CPS4     | AN               | _              | Capacitive sensing input 4.                                                                          |

| RB5/AN13/CPS5/T1G             | RB5      | TTL              | CMOS           | General purpose I/O. Individually controlled inter-                                                  |

|                               |          |                  | CIVIOS         | rupt-on-change. Individually enabled pull-up.                                                        |

|                               | AN13     | AN               | _              | A/D Channel 13 input.                                                                                |

|                               | CPS5     | AN               | —              | Capacitive sensing input 5.                                                                          |

|                               | T1G      | ST               | —              | Timer1 Gate input.                                                                                   |

| RB6/ICSPCLK/ICDCLK            | RB6      | TTL              | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |

|                               | ICSPCLK  | ST               | _              | Serial Programming Clock.                                                                            |

|                               | ICDCLK   | ST               | _              | In-Circuit Debug Clock.                                                                              |

| RB7/ICSPDAT/ICDDAT            | RB7      | TTL              | CMOS           | General purpose I/O. Individually controlled inter-                                                  |

|                               |          |                  |                | rupt-on-change. Individually enabled pull-up.                                                        |

|                               | ICSPDAT  | ST               | CMOS           | ICSP™ Data I/O.                                                                                      |

|                               | ICDDAT   | ST               | —              | In-Circuit Data I/O.                                                                                 |

| 0/T1OSO/T1CKI<br>1/T1OSI/CCP2 | RC0      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                               | T1OSO    | XTAL             | XTAL           | Timer1 oscillator connection.                                                                        |

|                               | T1CKI    | ST               | _              | Timer1 clock input.                                                                                  |

| RC1/T1OSI/CCP2                | RC1      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                               | T10SI    | XTAL             | XTAL           | Timer1 oscillator connection.                                                                        |

|                               | CCP2     | ST               | CMOS           | Capture/Compare/PWM2.                                                                                |

| RC2/CCP1                      | RC2      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                               | CCP1     | ST               | CMOS           | Capture/Compare/PWM1.                                                                                |

| RC3/SCK/SCL                   | RC3      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                               | SCK      | ST               | CMOS           | SPI clock.                                                                                           |

|                               | SCL      | l <sup>2</sup> C | OD             | I <sup>2</sup> C clock.                                                                              |

| RC4/SDI/SDA                   | RC4      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                               | SDI      | ST               | _              | SPI data input.                                                                                      |

|                               | SDA      | l <sup>2</sup> C | OD             | I <sup>2</sup> C data input/output.                                                                  |

| RC5/SDO                       | RC5      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                               | SDO      | _                | CMOS           | SPI data output.                                                                                     |

| RC6/TX/CK                     | RC6      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                               | ТХ       | _                | CMOS           | USART asynchronous transmit.                                                                         |

|                               | СК       | ST               | CMOS           | USART synchronous clock.                                                                             |

| RC7/RX/DT                     | RC7      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                               | RX       | ST               | _              | USART asynchronous input.                                                                            |

|                               | DT       | ST               | CMOS           | USART synchronous data.                                                                              |

| RD0/CPS8                      | RD0      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                               | CPS8     | AN               | _              | Capacitive sensing input 8.                                                                          |

| RD1/CPS9                      | RD1      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                               | CPS9     | AN               |                | Capacitive sensing input 9.                                                                          |

| RD2/CPS10                     | RD2      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                               | 1102     |                  |                |                                                                                                      |

| TABLE 1-1: | PIC16(L)F722/3/4/6/7 PINOUT DESCRIPTION (CONTINUED) |

|------------|-----------------------------------------------------|

| IABLE 1-1: | PIC16(L)F/22/3/4/6/7 PINOUT DESCRIPTION (CONTINUED) |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output

XTAL = Crystal levels HV = High Voltage

### 4.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to the **Section 19.0** "**Power-Down Mode (Sleep)**" for more details.

#### 4.4 INT Pin

The external interrupt, INT pin, causes an asynchronous, edge-triggered interrupt. The INTEDG bit of the OPTION register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector. This interrupt is disabled by clearing the INTE bit of the INTCON register.

### 4.5 Context Saving

When an interrupt occurs, only the return PC value is saved to the stack. If the ISR modifies or uses an instruction that modifies key registers, their values must be saved at the beginning of the ISR and restored when the ISR completes. This prevents instructions following the ISR from using invalid data. Examples of key registers include the W, STATUS, FSR and PCLATH registers.

The code shown in Example 4-1 can be used to do the following.

- Save the W register

- Save the STATUS register

- Save the PCLATH register

- Execute the ISR program

- Restore the PCLATH register

- Restore the STATUS register

- Restore the W register

Since most instructions modify the W register, it must be saved immediately upon entering the ISR. The SWAPF instruction is used when saving and restoring the W and STATUS registers because it will not affect any bits in the STATUS register. It is useful to place  $W_{TEMP}$  in shared memory because the ISR cannot predict which bank will be selected when the interrupt occurs.

The processor will branch to the interrupt vector by loading the PC with 0004h. The PCLATH register will remain unchanged. This requires the ISR to ensure that the PCLATH register is set properly before using an instruction that causes PCLATH to be loaded into the PC. See **Section 2.3 "PCL and PCLATH"** for details on PC operation.

#### EXAMPLE 4-1: SAVING W, STATUS AND PCLATH REGISTERS IN RAM

| MOVWF<br>SWAPF          | W_TEMP<br>STATUS,W                                      | ;Copy W to W_TEMP register<br>;Swap status to be saved into W<br>;Swaps are used because they do not affect the status bits                           |

|-------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVWF<br>MOVF           | STATUS_TEMP<br>STATUS_TEMP<br>PCLATH,W<br>PCLATH_TEMP   | ;Select regardless of current bank<br>;Copy status to bank zero STATUS_TEMP register<br>;Copy PCLATH to W register<br>;Copy W register to PCLATH_TEMP |

| :(ISR)<br>:             |                                                         | ;Insert user code here                                                                                                                                |

| MOVF                    | STATUS_TEMP<br>PCLATH_TEMP,W<br>PCLATH<br>STATUS_TEMP,W | ;Select regardless of current bank<br>;<br>;Restore PCLATH<br>;Swap STATUS_TEMP register into W<br>;(sets bank to original state)                     |

| MOVWF<br>SWAPF<br>SWAPF | STATUS<br>W_TEMP,F<br>W_TEMP,W                          | ;Move W into STATUS register<br>;Swap W_TEMP<br>;Swap W_TEMP into W                                                                                   |

#### 4.5.1 INTCON REGISTER

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, PORTB change and external RB0/INT/SEG0 pin interrupts.

```

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

```

| R/W-0                  | R/W-0                                                                                                                                                                             | R/W-0                                                     | R/W-0          | R/W-0               | R/W-0               | R/W-0           | R/W-x |  |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------|---------------------|---------------------|-----------------|-------|--|--|

| GIE                    | PEIE                                                                                                                                                                              | TOIE                                                      | INTE           | RBIE <sup>(1)</sup> | T0IF <sup>(2)</sup> | INTF            | RBIF  |  |  |

| bit 7                  |                                                                                                                                                                                   |                                                           |                |                     |                     |                 | bit C |  |  |

|                        |                                                                                                                                                                                   |                                                           |                |                     |                     |                 |       |  |  |

| Legend:<br>R = Readabl | o hit                                                                                                                                                                             | W = Writable I                                            | nit            | II – I Inimpler     | nented bit, read    | 1 26 '0'        |       |  |  |

| -n = Value at          |                                                                                                                                                                                   | '1' = Bit is set                                          | JIL            | '0' = Bit is cle    |                     | x = Bit is unkr | NOWD  |  |  |

|                        |                                                                                                                                                                                   | 1 – Dit 13 Set                                            |                |                     | areu                |                 | IOWIT |  |  |

| bit 7                  | GIE: Global Ir                                                                                                                                                                    | nterrupt Enable                                           | bit            |                     |                     |                 |       |  |  |

|                        | 1 = Enables a<br>0 = Disables a                                                                                                                                                   | all unmasked in all interrupts                            | terrupts       |                     |                     |                 |       |  |  |

| bit 6                  | 1 = Enables a                                                                                                                                                                     | eral Interrupt Er<br>all unmasked pe<br>all peripheral in | eripheral inte | rrupts              |                     |                 |       |  |  |

| bit 5                  | 1 = Enables t                                                                                                                                                                     | Overflow Interr<br>he Timer0 inter<br>the Timer0 inter    | rupt           | it                  |                     |                 |       |  |  |

| bit 4                  | 1 = Enables t                                                                                                                                                                     | IT External Inte<br>he RB0/INT ext<br>the RB0/INT ex      | ernal interru  | ot                  |                     |                 |       |  |  |

| bit 3                  | 1 = Enables t                                                                                                                                                                     | B Change Intern<br>he PORTB cha<br>the PORTB cha          | nge interrupt  |                     |                     |                 |       |  |  |

| bit 2                  | 1 = TMR0 reg                                                                                                                                                                      | Overflow Interr<br>gister has overfl<br>gister did not ov | owed (must l   |                     | oftware)            |                 |       |  |  |

| bit 1                  | <b>INTF:</b> RB0/INT External Interrupt Flag bit<br>1 = The RB0/INT external interrupt occurred (must be cleared in software)<br>0 = The RB0/INT external interrupt did not occur |                                                           |                |                     |                     |                 |       |  |  |

| bit 0                  | <ul> <li>RBIF: PORTB Change Interrupt Flag bit</li> <li>1 = When at least one of the PORTB general purpose I/O pins changed state (must be cleared software)</li> </ul>           |                                                           |                |                     |                     |                 |       |  |  |

|                        | 0 = None of t                                                                                                                                                                     |                                                           |                |                     | h                   |                 |       |  |  |

#### **REGISTER 4-1:** INTCON: INTERRUPT CONTROL REGISTER

- The appropriate bits in the IOCB register must also be set. Note 1:

- 2: T0IF bit is set when Timer0 rolls over. Timer0 is unchanged on Reset and should be initialized before clearing T0IF bit.

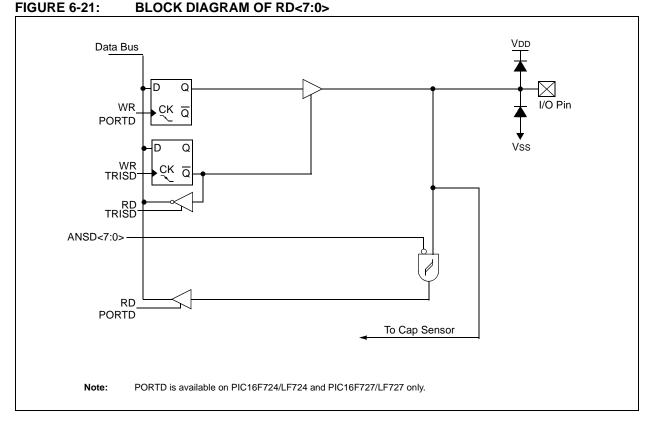

#### 6.5.6 RD4/CPS12

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### 6.5.7 RD5/CPS13

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- a capacitive sensing input

#### 6.5.8 RD6/CPS14

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### 6.5.9 RD7/CPS15

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

| TABLE 6-4: SUMM | IARY OF REGISTERS ASSOCIATED WITH PORTD <sup>(1)</sup> |

|-----------------|--------------------------------------------------------|

|-----------------|--------------------------------------------------------|

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|--------|--------|--------|---------|---------|--------|--------|----------------------|---------------------------------|

| ANSELD  | ANSD7  | ANSD6  | ANSD5  | ANSD4  | ANSD3   | ANSD2   | ANSD1  | ANSD0  | 1111 1111            | 1111 1111                       |

| CPSCON0 | CPSON  | —      | —      | —      | CPSRNG1 | CPSRNG0 | CPSOUT | TOXCS  | 0 0000               | 0 0000                          |

| CPSCON1 |        | —      | —      | _      | CPSCH3  | CPSCH2  | CPSCH1 | CPSCH0 | 0000                 | 0000                            |

| PORTD   | RD7    | RD6    | RD5    | RD4    | RD3     | RD2     | RD1    | RD0    | XXXX XXXX            | xxxx xxxx                       |

| TRISD   | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3  | TRISD2  | TRISD1 | TRISD0 | 1111 1111            | 1111 1111                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTD.**Note 1:**These registers are not implemented on the PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'.

#### © 2007-2015 Microchip Technology Inc.

#### DS40001341F-page 79

#### 9.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

- **Note 1:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

- **2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the GIE and PEIE bits of the INTCON register must be disabled. If the GIE and PEIE bits of the INT-CON register are enabled, execution will switch to the Interrupt Service Routine.

Please refer to **Section 9.1.5** "Interrupts" for more information.

# 9.2 ADC Operation

#### 9.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

Note: The GO/DONE bit should not be set in the same instruction that turns on the ADC. Refer to Section 9.2.6 "A/D Conversion Procedure".

# 9.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRES register with new conversion result

#### 9.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRES register will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

| Note: | A device Reset forces all registers to their |

|-------|----------------------------------------------|

|       | Reset state. Thus, the ADC module is         |

|       | turned off and any pending conversion is     |

|       | terminated.                                  |

#### 9.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 9.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCP module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 15.0 "Capture/Compare/PWM (CCP) Module" for more information.

# PIC16(L)F722/3/4/6/7

# 15.2 Compare Mode

In Compare mode, the 16-bit CCPRx register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCPx module may:

- Toggle the CCPx output

- Set the CCPx output

- · Clear the CCPx output

- Generate a Special Event Trigger

- Generate a Software Interrupt

The action on the pin is based on the value of the CCPxM<3:0> control bits of the CCPxCON register.

All Compare modes can generate an interrupt.

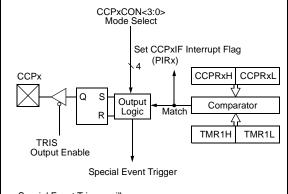

#### FIGURE 15-2: COMPARE MODE OPERATION BLOCK DIAGRAM

- Special Event Trigger will:

- Clear TMR1H and TMR1L registers.

- NOT set interrupt flag bit TMR1IF of the PIR1 register.

Set the GO/DONE bit to start the ADC conversion

- (CCP2 only).

#### 15.2.1 CCPx PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

Either RC1 or RB3 can be selected as the CCP2 pin. Refer to **Section 6.1** "Alternate Pin Function" for more information.

| Note: | Clearing the CCPxCON register will force    |

|-------|---------------------------------------------|

|       | the CCPx compare output latch to the        |

|       | default low level. This is not the PORT I/O |

|       | data latch.                                 |

#### 15.2.2 TIMER1 MODE SELECTION

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode. Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. For the Compare operation of the TMR1 register to the CCPRx register to occur, Timer1 must be clocked from the Instruction Clock (Fosc/4) or from an external clock source.

#### 15.2.3 SOFTWARE INTERRUPT MODE

When Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPxIF bit in the PIRx register is set and the CCPx module does not assert control of the CCPx pin (refer to the CCPxCON register).

#### 15.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is chosen (CCPxM<3:0> = 1011), the CCPx module does the following:

- Resets Timer1

- Starts an ADC conversion if ADC is enabled (CCP2 only)

The CCPx module does not assert control of the CCPx pin in this mode (refer to the CCPxCON register).

The Special Event Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPRxH, CCPRxL register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. This allows the CCPRxH, CCPRxL register pair to effectively provide a 16-bit programmable period register for Timer1.

Note 1: The Special Event Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

2: Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Special Event Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

#### 15.2.5 COMPARE DURING SLEEP

The Compare Mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

| R/W-0         | R/W-0                                                                                                                               | R/W-0                                                            | R/W-0            | R/W-0            | R-0              | R-0               | R-x          |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------|------------------|------------------|-------------------|--------------|--|--|--|--|

| SPEN          | RX9                                                                                                                                 | SREN                                                             | CREN             | ADDEN            | FERR             | OERR              | RX9D         |  |  |  |  |

| bit 7         |                                                                                                                                     |                                                                  |                  | •<br>•           |                  |                   | bit (        |  |  |  |  |

|               |                                                                                                                                     |                                                                  |                  |                  |                  |                   |              |  |  |  |  |

| Legend:       |                                                                                                                                     |                                                                  |                  |                  |                  | ( <b>a</b> )      |              |  |  |  |  |

| R = Readable  |                                                                                                                                     | W = Writable                                                     |                  | -                | mented bit, read |                   |              |  |  |  |  |

| -n = Value at | POR                                                                                                                                 | '1' = Bit is set                                                 |                  | '0' = Bit is cle | ared             | x = Bit is unkn   | lown         |  |  |  |  |

| bit 7         | CDEN: Coriol                                                                                                                        | Dort Enchla bi                                                   | :(1)             |                  |                  |                   |              |  |  |  |  |

|               | <b>SPEN:</b> Serial Port Enable bit <sup>(1)</sup><br>1 = Serial port enabled (configures RX/DT and TX/CK pins as serial port pins) |                                                                  |                  |                  |                  |                   |              |  |  |  |  |

|               |                                                                                                                                     | rt disabled (be                                                  |                  |                  | ins as senai poi | t pins)           |              |  |  |  |  |

| bit 6         | <b>RX9:</b> 9-bit Re                                                                                                                | ceive Enable b                                                   | oit              |                  |                  |                   |              |  |  |  |  |

|               | 1 = Selects 9                                                                                                                       | -bit reception                                                   |                  |                  |                  |                   |              |  |  |  |  |

|               | 0 = Selects 8                                                                                                                       | -bit reception                                                   |                  |                  |                  |                   |              |  |  |  |  |

| bit 5         | -                                                                                                                                   | Receive Enal                                                     | ole bit          |                  |                  |                   |              |  |  |  |  |

|               | Asynchronous                                                                                                                        | <u>s mode</u> :                                                  |                  |                  |                  |                   |              |  |  |  |  |

|               | Don't care                                                                                                                          | mode - Maste                                                     | vr.              |                  |                  |                   |              |  |  |  |  |

|               | -                                                                                                                                   | <u>Synchronous mode – Master</u> :<br>1 = Enables single receive |                  |                  |                  |                   |              |  |  |  |  |

|               | 1 = Enables single receive<br>0 = Disables single receive                                                                           |                                                                  |                  |                  |                  |                   |              |  |  |  |  |

|               | This bit is cleared after reception is complete.                                                                                    |                                                                  |                  |                  |                  |                   |              |  |  |  |  |

|               | Synchronous mode – Slave:                                                                                                           |                                                                  |                  |                  |                  |                   |              |  |  |  |  |

| L:1 1         | Don't care                                                                                                                          |                                                                  | Enchla hit       |                  |                  |                   |              |  |  |  |  |

| bit 4         |                                                                                                                                     | nuous Receive                                                    | Enable bit       |                  |                  |                   |              |  |  |  |  |

|               | <u>Asynchronous</u><br>1 = Enables                                                                                                  |                                                                  |                  |                  |                  |                   |              |  |  |  |  |

|               | 0 = Disables                                                                                                                        |                                                                  |                  |                  |                  |                   |              |  |  |  |  |

|               | <u>Synchronous</u>                                                                                                                  | mode:                                                            |                  |                  |                  |                   |              |  |  |  |  |

|               |                                                                                                                                     | continuous rec<br>continuous rec                                 |                  | ble bit CREN is  | cleared (CREN    | l overrides SRE   | EN)          |  |  |  |  |

| bit 3         |                                                                                                                                     | ress Detect Er                                                   |                  |                  |                  |                   |              |  |  |  |  |

| DIL J         |                                                                                                                                     | s mode 9-bit (F                                                  |                  |                  |                  |                   |              |  |  |  |  |

|               |                                                                                                                                     | •                                                                |                  | terrupt and loa  | d the receive bu | uffer when RSR    | <8> is set   |  |  |  |  |

|               | 0 = Disables                                                                                                                        | address detec                                                    | tion, all bytes  |                  | nd ninth bit can |                   |              |  |  |  |  |

|               | <u>Asynchronous mode 8-bit (RX9 = 0)</u> :                                                                                          |                                                                  |                  |                  |                  |                   |              |  |  |  |  |

|               | Don't care<br><u>Synchronous mode</u> :                                                                                             |                                                                  |                  |                  |                  |                   |              |  |  |  |  |

|               | Must be set to                                                                                                                      |                                                                  |                  |                  |                  |                   |              |  |  |  |  |

| bit 2         | FERR: Frami                                                                                                                         |                                                                  |                  |                  |                  |                   |              |  |  |  |  |

|               |                                                                                                                                     | -                                                                | updated by rea   | adina RCREG I    | egister and rec  | eive next valid l | ovte)        |  |  |  |  |

|               | 0 = No framin                                                                                                                       |                                                                  |                  |                  | -9               |                   | - ) )        |  |  |  |  |

| bit 1         | OERR: Overr                                                                                                                         | un Error bit                                                     |                  |                  |                  |                   |              |  |  |  |  |

|               | 1 = Overrun<br>0 = No overr                                                                                                         |                                                                  | leared by clea   | aring bit CREN   | )                |                   |              |  |  |  |  |

| bit 0         | RX9D: Ninth                                                                                                                         | bit of Received                                                  | l Data           |                  |                  |                   |              |  |  |  |  |

|               | This can be a                                                                                                                       | ddress/data bi                                                   | t or a parity bi | t and must be o  | calculated by us | er firmware.      |              |  |  |  |  |

|               | he AUSART m<br>RISx = 1.                                                                                                            | odule automa                                                     | tically change   | es the pin fro   | m tri-state to o | drive as neede    | ed. Configur |  |  |  |  |

### REGISTER 16-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

# 16.3.2.3 AUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 16.3.1.4 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never Idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE interrupt enable bit of the PIE1 register is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 16.3.2.4 Synchronous Slave Reception Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 3. If 9-bit reception is desired, set the RX9 bit.

- 4. Verify address detection is disabled by clearing the ADDEN bit of the RCSTA register.

- 5. Set the CREN bit to enable reception.

- The RCIF bit of the PIR1 register will be set when reception is complete. An interrupt will be generated if the RCIE bit of the PIE1 register was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register.

| Name   | Bit 7                        | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|------------------------------|--------|--------|--------|--------|--------|--------|-----------|----------------------|---------------------------------|

| INTCON | GIE                          | PEIE   | TOIE   | INTE   | RBIE   | T0IF   | INTF   | RBIF      | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE                      | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE    | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF                      | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF    | 0000 0000            | 0000 0000                       |

| RCREG  | AUSART Receive Data Register |        |        |        |        |        |        | 0000 0000 | 0000 0000            |                                 |

| RCSTA  | SPEN                         | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D      | 0000 000X            | 0000 000X                       |

| TRISC  | TRISC7                       | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0    | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC                         | TX9    | TXEN   | SYNC   | —      | BRGH   | TRMT   | TX9D      | 0000 -010            | 0000 -010                       |

#### TABLE 16-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Reception.

# 19.2 Wake-up Using Interrupts

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will not be cleared, the TO bit will not be set and the PD bit will not be cleared.

- If the interrupt occurs **during or after** the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

#### FIGURE 19-1: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| : 1 02 03 04;01 02 03 04;01 02 03 04;01 02 03 04;01 02 03 04;01 02 03 04;01 02 03 04;01 02 03 04;01 02 03 04;01<br>                                                                                                                                               | Q4.<br>~' |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|                                                                                                                                                                                                                                                                   |           |

| INT pin                                                                                                                                                                                                                                                           | !         |

| INTF flag<br>(INTCON reg.)                                                                                                                                                                                                                                        |           |

| GIE bit<br>(INTCON reg.), Sleep                                                                                                                                                                                                                                   |           |

|                                                                                                                                                                                                                                                                   |           |

| PC         V         PC + 1         V         PC + 2         V         PC + 2         V         PC + 2         V         0005h           Instruction {         Inst(PC) = Sleep         Inst(PC + 1)         Inst(PC + 2)         Inst(0004h)         Inst(0005h) | h)        |

| Instruction Inst(PC - 1) Sleep Inst(PC + 1) Dummy Cycle Dummy Cycle Inst(0004                                                                                                                                                                                     | h)        |

Note 1: XT, HS or LP Oscillator mode assumed.

2: TOST = 1024 Tosc (drawing not to scale). This delay does not apply to EC and RC Oscillator modes.

3: GIE = 1 assumed. In this case after wake-up, the processor jumps to 0004h. If GIE = 0, execution will continue in-line.

4: CLKOUT is not available in XT, HS, LP or EC Oscillator modes, but shown here for timing reference.

| Name   | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on all other Resets |

|--------|---------|-------|-------|-------|-------|--------|--------|--------|----------------------|---------------------------|

| IOCB   | IOCB7   | IOCB6 | IOCB5 | IOCB4 | IOCB3 | IOCB2  | IOCB1  | IOCB0  | 0000 0000            | 0000 0000                 |

| INTCON | GIE     | PEIE  | TOIE  | INTE  | RBIE  | T0IF   | INTF   | RBIF   | 0000 0000            | 0000 0000                 |

| PIE1   | TMR1GIE | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                 |

| PIE2   | —       | _     | _     | _     | —     | —      | _      | CCP2IE | 0                    | 0                         |

| PIR1   | TMR1GIF | ADIF  | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                 |

| PIR2   | —       | _     | _     | —     | —     | —      | —      | CCP2IF | 0                    | 0                         |

#### TABLE 19-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used in Power-Down mode.

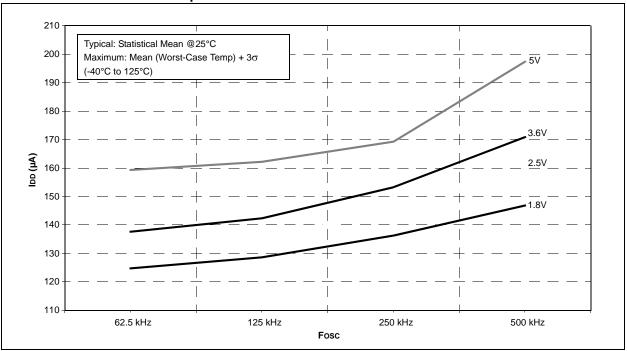

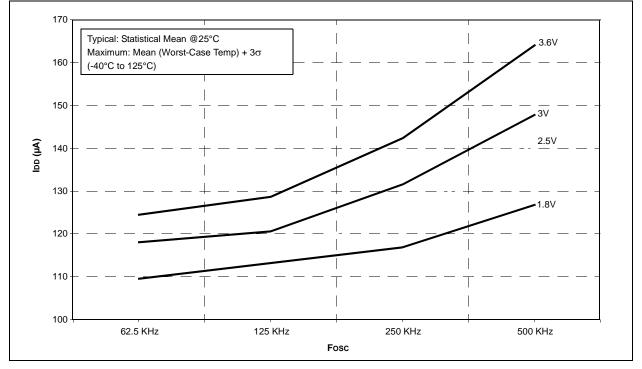

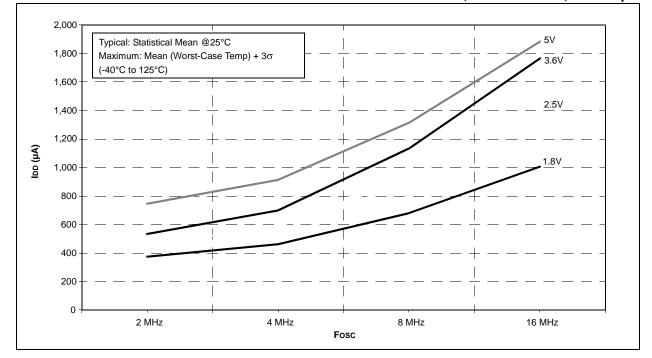

### 23.2 DC Characteristics: PIC16(L)F722/3/4/6/7-I/E (Industrial, Extended) (Continued)

| PIC16LF722/3/4/6/7                     |                 |                                                      | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array} $ |      |       |            |                             |  |  |

|----------------------------------------|-----------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|-----------------------------|--|--|

| PIC16F722/3/4/6/7                      |                 | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                                                                                                                                                                                                                              |      |       |            |                             |  |  |

| Param                                  | Device          | Min.                                                 | Тур†                                                                                                                                                                                                                                                         | Max. | Units | Conditions |                             |  |  |

| No.                                    | Characteristics |                                                      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                                                                                                                                                                                                      |      |       | Vdd        | Note                        |  |  |

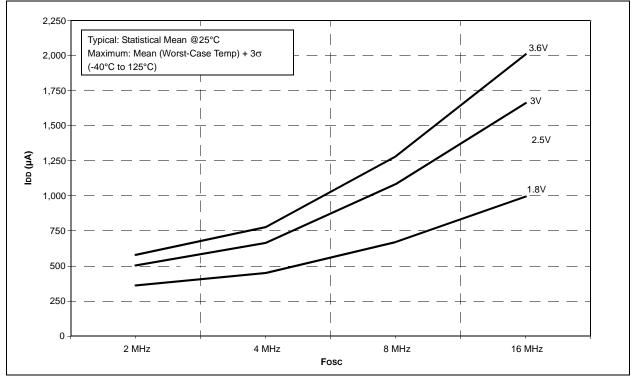

| Supply Current (IDD) <sup>(1, 2)</sup> |                 |                                                      |                                                                                                                                                                                                                                                              |      |       |            |                             |  |  |

| D014                                   |                 | _                                                    | 290                                                                                                                                                                                                                                                          | 330  | μA    | 1.8        | Fosc = 4 MHz                |  |  |

|                                        |                 | _                                                    | 460                                                                                                                                                                                                                                                          | 500  | μA    | 3.0        | EC Oscillator mode          |  |  |

| D014                                   |                 | _                                                    | 300                                                                                                                                                                                                                                                          | 430  | μA    | 1.8        | Fosc = 4 MHz                |  |  |

|                                        |                 |                                                      | 450                                                                                                                                                                                                                                                          | 655  | μA    | 3.0        | EC Oscillator mode (Note 5) |  |  |

|                                        |                 | —                                                    | 500                                                                                                                                                                                                                                                          | 730  | μΑ    | 5.0        |                             |  |  |

| D015                                   |                 | _                                                    | 100                                                                                                                                                                                                                                                          | 130  | μA    | 1.8        | Fosc = 500 kHz              |  |  |

|                                        |                 | _                                                    | 120                                                                                                                                                                                                                                                          | 150  | μA    | 3.0        | MFINTOSC mode               |  |  |

| D015                                   |                 | _                                                    | 115                                                                                                                                                                                                                                                          | 195  | μA    | 1.8        | Fosc = 500 kHz              |  |  |

|                                        |                 | _                                                    | 135                                                                                                                                                                                                                                                          | 200  | μΑ    | 3.0        | MFINTOSC mode (Note 5)      |  |  |

|                                        |                 | —                                                    | 150                                                                                                                                                                                                                                                          | 220  | μA    | 5.0        |                             |  |  |

| D016                                   |                 | _                                                    | 650                                                                                                                                                                                                                                                          | 800  | μΑ    | 1.8        | Fosc = 8 MHz                |  |  |

|                                        |                 |                                                      | 1000                                                                                                                                                                                                                                                         | 1200 | μA    | 3.0        | HFINTOSC mode               |  |  |

| D016                                   |                 | _                                                    | 625                                                                                                                                                                                                                                                          | 850  | μA    |            | Fosc = 8 MHz                |  |  |

|                                        |                 | _                                                    | 1000                                                                                                                                                                                                                                                         | 1200 | μA    | 3.0        | HFINTOSC mode (Note 5)      |  |  |

|                                        |                 | —                                                    | 1100                                                                                                                                                                                                                                                         | 1500 | μA    | 5.0        |                             |  |  |

| D017                                   |                 |                                                      | 1.0                                                                                                                                                                                                                                                          | 1.2  | mA    | 1.8        | Fosc = 16 MHz               |  |  |

|                                        |                 |                                                      | 1.5                                                                                                                                                                                                                                                          | 1.85 | mA    | 3.0        | HFINTOSC mode               |  |  |

| D017                                   |                 | _                                                    | 1                                                                                                                                                                                                                                                            | 1.2  | mA    | 1.8        | Fosc = 16 MHz               |  |  |

|                                        |                 | _                                                    | 1.5                                                                                                                                                                                                                                                          | 1.7  | mA    | 3.0        | HFINTOSC mode (Note 5)      |  |  |

|                                        |                 | —                                                    | 1.7                                                                                                                                                                                                                                                          | 2.1  | mA    | 5.0        |                             |  |  |

| D018                                   |                 | _                                                    | 210                                                                                                                                                                                                                                                          | 240  | μA    | 1.8        | Fosc = 4 MHz                |  |  |

|                                        |                 | _                                                    | 340                                                                                                                                                                                                                                                          | 380  | μA    | 3.0        | EXTRC mode (Note 3, Note 5) |  |  |

| D018                                   |                 | _                                                    | 225                                                                                                                                                                                                                                                          | 320  | μA    | 1.8        | Fosc = 4 MHz                |  |  |

|                                        |                 |                                                      | 360                                                                                                                                                                                                                                                          | 445  | μA    | 3.0        | EXTRC mode (Note 3, Note 5) |  |  |

|                                        |                 | —                                                    | 410                                                                                                                                                                                                                                                          | 650  | μA    | 5.0        |                             |  |  |

| D019                                   |                 |                                                      | 1.6                                                                                                                                                                                                                                                          | 1.9  | mA    | 3.0        | Fosc = 20 MHz               |  |  |

|                                        |                 |                                                      | 2.0                                                                                                                                                                                                                                                          | 2.8  | mA    | 3.6        | HS Oscillator mode          |  |  |

| D019                                   |                 | _                                                    | 1.6                                                                                                                                                                                                                                                          | 2    | mA    | 3.0        | Fosc = 20 MHz               |  |  |

|                                        |                 |                                                      | 1.9                                                                                                                                                                                                                                                          | 3.2  | mA    | 5.0        | HS Oscillator mode (Note 5) |  |  |

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

4: FVR and BOR are disabled.

5: 0.1 μF capacitor on VCAP (RA0).

#### 23.5 **Thermal Considerations**

| Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |           |                                        |      |       |                                                          |  |  |

|--------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------|------|-------|----------------------------------------------------------|--|--|

| Param<br>No.                                                                                                             | Sym.      | Characteristic                         | Тур. | Units | Conditions                                               |  |  |

| TH01                                                                                                                     | θJA       | Thermal Resistance Junction to Ambient | 60   | °C/W  | 28-pin SPDIP package                                     |  |  |

|                                                                                                                          |           |                                        | 80   | °C/W  | 28-pin SOIC package                                      |  |  |

|                                                                                                                          |           |                                        | 90   | °C/W  | 28-pin SSOP package                                      |  |  |

|                                                                                                                          |           |                                        | 27.5 | °C/W  | 28-pin UQFN 4x4mm package                                |  |  |

|                                                                                                                          |           |                                        | 27.5 | °C/W  | 28-pin QFN 6x6mm package                                 |  |  |

|                                                                                                                          |           |                                        | 47.2 | °C/W  | 40-pin PDIP package                                      |  |  |

|                                                                                                                          |           |                                        | 46   | °C/W  | 44-pin TQFP package                                      |  |  |

|                                                                                                                          |           |                                        | 24.4 | °C/W  | 44-pin QFN 8x8mm package                                 |  |  |

| TH02 θJC                                                                                                                 | θJC       | Thermal Resistance Junction to Case    | 31.4 | °C/W  | 28-pin SPDIP package                                     |  |  |

|                                                                                                                          |           |                                        | 24   | °C/W  | 28-pin SOIC package                                      |  |  |

|                                                                                                                          |           |                                        | 24   | °C/W  | 28-pin SSOP package                                      |  |  |

|                                                                                                                          |           |                                        | 24   | °C/W  | 28-pin UQFN 4x4mm package                                |  |  |

|                                                                                                                          |           |                                        | 24   | °C/W  | 28-pin QFN 6x6mm package                                 |  |  |

|                                                                                                                          |           |                                        | 24.7 | °C/W  | 40-pin PDIP package                                      |  |  |

|                                                                                                                          |           |                                        | 14.5 | °C/W  | 44-pin TQFP package                                      |  |  |

|                                                                                                                          |           |                                        | 20   | °C/W  | 44-pin QFN 8x8mm package                                 |  |  |

| TH03                                                                                                                     | Тјмах     | Maximum Junction Temperature           | 150  | °C    |                                                          |  |  |

| TH04                                                                                                                     | PD        | Power Dissipation                      | _    | W     | PD = PINTERNAL + PI/O                                    |  |  |

| TH05                                                                                                                     | PINTERNAL | Internal Power Dissipation             | _    | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |  |  |

| TH06                                                                                                                     | Pi/o      | I/O Power Dissipation                  | _    | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |  |  |

| TH07                                                                                                                     | Pder      | Derated Power                          | _    | W     | Pder = PDmax (Tj - Ta)/θja <sup>(2)</sup>                |  |  |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

**2:** TA = Ambient Temperature

**3:** T<sub>J</sub> = Junction Temperature

# 23.6 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| 2. Tpp3 |                                      |     |                |

|---------|--------------------------------------|-----|----------------|

| т       |                                      |     |                |

| F       | Frequency                            | Т   | Time           |

| Lowerc  | ase letters (pp) and their meanings: |     |                |

| рр      |                                      |     |                |

| сс      | CCP1                                 | osc | OSC1           |

| ck      | CLKOUT                               | rd  | RD             |

| CS      | CS                                   | rw  | RD or WR       |

| di      | SDI                                  | sc  | SCK            |

| do      | SDO                                  | SS  | SS             |

| dt      | Data in                              | tO  | TOCKI          |