#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I²C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 25                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 11x8b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 28-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f723-i-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

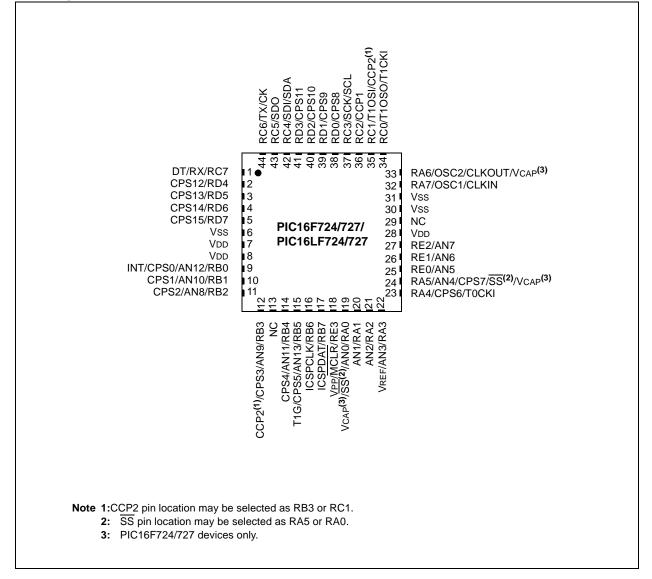

| Name               | Function | Input<br>Type    | Output<br>Type | Description                                                                                          |

|--------------------|----------|------------------|----------------|------------------------------------------------------------------------------------------------------|

| RB4/AN11/CPS4      | RB4      | TTL              | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |

|                    | AN11     | AN               | _              | A/D Channel 11 input.                                                                                |

|                    | CPS4     | AN               | _              | Capacitive sensing input 4.                                                                          |

| RB5/AN13/CPS5/T1G  | RB5      | TTL              | CMOS           | General purpose I/O. Individually controlled inter-                                                  |

|                    |          |                  | CIVIOS         | rupt-on-change. Individually enabled pull-up.                                                        |

|                    | AN13     | AN               | —              | A/D Channel 13 input.                                                                                |

|                    | CPS5     | AN               | —              | Capacitive sensing input 5.                                                                          |

|                    | T1G      | ST               | —              | Timer1 Gate input.                                                                                   |

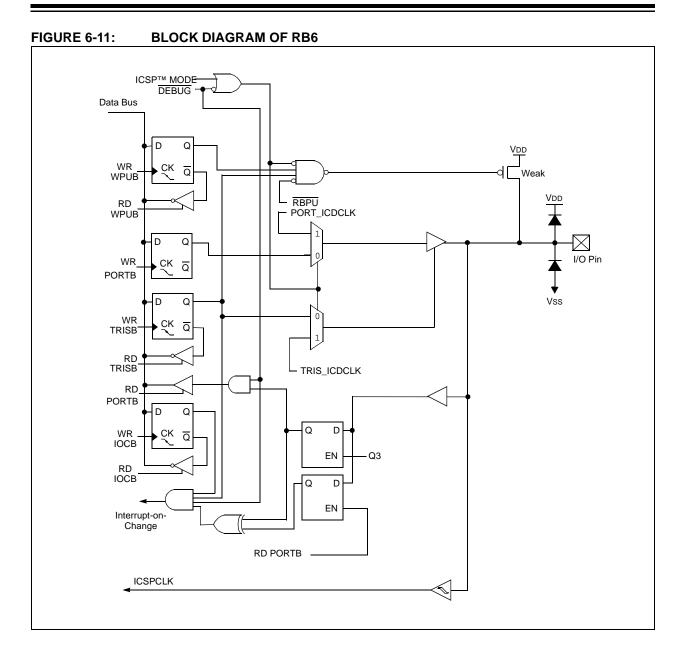

| RB6/ICSPCLK/ICDCLK | RB6      | TTL              | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |

|                    | ICSPCLK  | ST               | _              | Serial Programming Clock.                                                                            |

|                    | ICDCLK   | ST               | _              | In-Circuit Debug Clock.                                                                              |

| RB7/ICSPDAT/ICDDAT | RB7      | TTL              | CMOS           | General purpose I/O. Individually controlled inter-                                                  |

|                    |          |                  |                | rupt-on-change. Individually enabled pull-up.                                                        |

|                    | ICSPDAT  | ST               | CMOS           | ICSP™ Data I/O.                                                                                      |

|                    | ICDDAT   | ST               | —              | In-Circuit Data I/O.                                                                                 |

| RC0/T1OSO/T1CKI    | RC0      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | T1OSO    | XTAL             | XTAL           | Timer1 oscillator connection.                                                                        |

|                    | T1CKI    | ST               | _              | Timer1 clock input.                                                                                  |

| RC1/T1OSI/CCP2     | RC1      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | T10SI    | XTAL             | XTAL           | Timer1 oscillator connection.                                                                        |

|                    | CCP2     | ST               | CMOS           | Capture/Compare/PWM2.                                                                                |

| RC2/CCP1           | RC2      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | CCP1     | ST               | CMOS           | Capture/Compare/PWM1.                                                                                |

| RC3/SCK/SCL        | RC3      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | SCK      | ST               | CMOS           | SPI clock.                                                                                           |

|                    | SCL      | l <sup>2</sup> C | OD             | I <sup>2</sup> C clock.                                                                              |

| RC4/SDI/SDA        | RC4      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | SDI      | ST               | _              | SPI data input.                                                                                      |

|                    | SDA      | l <sup>2</sup> C | OD             | I <sup>2</sup> C data input/output.                                                                  |

| RC5/SDO            | RC5      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | SDO      | _                | CMOS           | SPI data output.                                                                                     |

| RC6/TX/CK          | RC6      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | ТХ       | _                | CMOS           | USART asynchronous transmit.                                                                         |

|                    | СК       | ST               | CMOS           | USART synchronous clock.                                                                             |

| RC7/RX/DT          | RC7      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | RX       | ST               | _              | USART asynchronous input.                                                                            |

|                    | DT       | ST               | CMOS           | USART synchronous data.                                                                              |

| RD0/CPS8           | RD0      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | CPS8     | AN               | _              | Capacitive sensing input 8.                                                                          |

| RD1/CPS9           | RD1      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | CPS9     | AN               |                | Capacitive sensing input 9.                                                                          |

| RD2/CPS10          | RD2      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    |          |                  |                |                                                                                                      |

| TABLE 1-1: | PIC16(L)F722/3/4/6/7 PINOUT DESCRIPTION (CONTINUED) |

|------------|-----------------------------------------------------|

| IABLE 1-1: | PIC16(L)F/22/3/4/6/7 PINOUT DESCRIPTION (CONTINUED) |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output

XTAL = Crystal levels HV = High Voltage

#### EXAMPLE 4-1: SAVING W, STATUS AND PCLATH REGISTERS IN RAM

| MOVWF<br>SWAPF          | W_TEMP<br>STATUS,W                                      | ;Copy W to W_TEMP register<br>;Swap status to be saved into W<br>;Swaps are used because they do not affect the status bits                           |

|-------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVWF<br>MOVF           | STATUS_TEMP<br>STATUS_TEMP<br>PCLATH,W<br>PCLATH_TEMP   | ;Select regardless of current bank<br>;Copy status to bank zero STATUS_TEMP register<br>;Copy PCLATH to W register<br>;Copy W register to PCLATH_TEMP |

| :(ISR)<br>:             |                                                         | ;Insert user code here                                                                                                                                |

| MOVF                    | STATUS_TEMP<br>PCLATH_TEMP,W<br>PCLATH<br>STATUS_TEMP,W | ;Select regardless of current bank<br>;<br>;Restore PCLATH<br>;Swap STATUS_TEMP register into W<br>;(sets bank to original state)                     |

| MOVWF<br>SWAPF<br>SWAPF | STATUS<br>W_TEMP,F<br>W_TEMP,W                          | ;Move W into STATUS register<br>;Swap W_TEMP<br>;Swap W_TEMP into W                                                                                   |

#### 4.5.1 INTCON REGISTER

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, PORTB change and external RB0/INT/SEG0 pin interrupts.

```

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

```

#### 6.2.1 ANSELA REGISTER

The ANSELA register (Register 6-4) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

#### REGISTER 6-4: ANSELA: PORTA ANALOG SELECT REGISTER

| U-0                                | U-0 | R/W-1                                    | R/W-1                              | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|------------------------------------|-----|------------------------------------------|------------------------------------|-------|-------|-------|-------|

| —                                  | —   | ANSA5                                    | ANSA4                              | ANSA3 | ANSA2 | ANSA1 | ANSA0 |

| bit 7                              |     |                                          |                                    |       |       |       | bit 0 |

|                                    |     |                                          |                                    |       |       |       |       |

| Legend:                            |     |                                          |                                    |       |       |       |       |

| R = Readable bit W = Writable bit  |     |                                          | U = Unimplemented bit, read as '0' |       |       |       |       |

| -n = Value at POR '1' = Bit is set |     | 0' = Bit is cleared $x = Bit is unknown$ |                                    |       | nown  |       |       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **ANSA<5:0>**: Analog Select between Analog or Digital Function on pins RA<5:0>, respectively 0 = Digital I/O. Pin is assigned to port or Digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital Input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### REGISTER 6-17: ANSELE: PORTE ANALOG SELECT REGISTER

| U-0                                | U-0 | U-0                                     | U-0 | U-0 | R/W-1                | R/W-1                | R/W-1                |

|------------------------------------|-----|-----------------------------------------|-----|-----|----------------------|----------------------|----------------------|

| —                                  | _   |                                         | _   | _   | ANSE2 <sup>(2)</sup> | ANSE1 <sup>(2)</sup> | ANSE0 <sup>(2)</sup> |

| bit 7                              |     |                                         |     |     |                      |                      | bit 0                |

|                                    |     |                                         |     |     |                      |                      |                      |

| Legend:                            |     |                                         |     |     |                      |                      |                      |

| R = Readable bit W = Writable bit  |     | U = Unimplemented bit, read as '0'      |     |     |                      |                      |                      |

| -n = Value at POR '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |     |     | nown                 |                      |                      |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 **ANSE<2:0>:** Analog Select between Analog or Digital Function on Pins RE<2:0>, respectively 0 = Digital I/O. Pin is assigned to port or Digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital Input buffer disabled.

2: ANSELE register is not implemented on the PIC16F722/723/726/PIC16LF722/723/726. Read as '0'

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3                 | Bit 2                 | Bit 1                 | Bit 0                 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-------|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|----------------------|---------------------------------|

| ADCON0 |       |       | CHS3  | CHS2  | CHS1                  | CHS0                  | GO/DONE               | ADON                  | 00 0000              | 00 0000                         |

| ANSELE | _     |       | _     | _     | _                     | ANSE2                 | ANSE1                 | ANSE0                 | 111                  | 111                             |

| PORTE  | _     | _     | _     | _     | RE3                   | RE2                   | RE1                   | RE0                   | xxxx                 | xxxx                            |

| TRISE  | _     |       | _     | _     | TRISE3 <sup>(2)</sup> | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> | 1111                 | 1111                            |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE

Note 1: These registers are not implemented on the PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'.

**2:** This bit is always '1' as RE3 is input only.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

### 7.6 External Clock Modes

#### 7.6.1 OSCILLATOR START-UP TIMER (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations on the OSC1 pin before the device is released from Reset. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

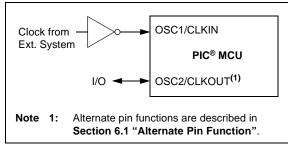

#### 7.6.2 EC MODE

The External Clock (EC) mode allows an externally generated logic level as the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input and the OSC2 is available for general purpose I/O. Figure 7-2 shows the pin connections for EC mode.

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### FIGURE 7-2: EXTERNAL CLOCK (EC) MODE OPERATION

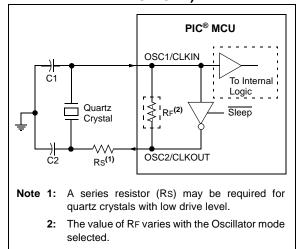

#### 7.6.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 7-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

LP Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is best suited to drive resonators with a low drive level specification, for example, tuning fork type crystals.

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 7-3 and Figure 7-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

#### FIGURE 7-3: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices (DS00826)

- AN849, Basic PIC<sup>®</sup> Oscillator Design (DS00849)

- AN943, Practical PIC<sup>®</sup> Oscillator Analysis and Design (DS00943)

- AN949, Making Your Oscillator Work (DS00949).

# 9.3 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 9-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 9-3. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the source

impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 9-1 may be used. This equation assumes that 1/2 LSb error is used (256 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 9-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V VDD$

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

$V_{APPLIED}\left(1 - \frac{1}{1-1}\right) = V_{CHOLD}$

$:[11VCHOLD charged to within 1/2 lsb$

$$(2^{n+1}) - 1'$$

$$V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{CHOLD}$$

;[2] V\_{CHOLD charge response to V\_{APPLIED}}

$$V_{APPLIED}\left(1-e^{\frac{-ic}{RC}}\right) = V_{APPLIED}\left(1-\frac{1}{(2^{n+1})-l}\right) \quad (combining [1] and [2])$$

*Note:* Where n = number of bits of the ADC.

Solving for TC:

$$T_{C} = -C_{HOLD}(R_{IC} + R_{SS} + R_{S}) \ln(1/511)$$

=  $-10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.001957)$

=  $1.12\mu s$

$$c_{O} = 2M_{S} + 1.12M_{S} + [(50^{\circ}C - 25^{\circ}C)(0.05M_{S}/^{\circ}C)]$$

Therefore:

$$TACQ = 2MS + 1.12MS + [(50°C-25°C)(0.05MS/°C)]$$

= 4.42MS

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

#### 12.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

## 12.4 Timer1 Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

| Note: | The oscillator requires a start-up and   |  |  |  |

|-------|------------------------------------------|--|--|--|

|       | stabilization time before use. Thus,     |  |  |  |

|       | T1OSCEN should be set and a suitable     |  |  |  |

|       | delay observed prior to enabling Timer1. |  |  |  |

# 12.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 12.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

#### 12.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

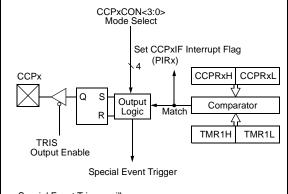

# 15.2 Compare Mode

In Compare mode, the 16-bit CCPRx register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCPx module may:

- Toggle the CCPx output

- Set the CCPx output

- Clear the CCPx output

- Generate a Special Event Trigger

- Generate a Software Interrupt

The action on the pin is based on the value of the CCPxM<3:0> control bits of the CCPxCON register.

All Compare modes can generate an interrupt.

#### FIGURE 15-2: COMPARE MODE OPERATION BLOCK DIAGRAM

- Special Event Trigger will:

- Clear TMR1H and TMR1L registers.

- NOT set interrupt flag bit TMR1IF of the PIR1 register.

Set the GO/DONE bit to start the ADC conversion

- (CCP2 only).

#### 15.2.1 CCPx PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

Either RC1 or RB3 can be selected as the CCP2 pin. Refer to **Section 6.1** "Alternate Pin Function" for more information.

| Note: | Clearing the CCPxCON register will force    |

|-------|---------------------------------------------|

|       | the CCPx compare output latch to the        |

|       | default low level. This is not the PORT I/O |

|       | data latch.                                 |

#### 15.2.2 TIMER1 MODE SELECTION

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode. Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. For the Compare operation of the TMR1 register to the CCPRx register to occur, Timer1 must be clocked from the Instruction Clock (Fosc/4) or from an external clock source.

#### 15.2.3 SOFTWARE INTERRUPT MODE

When Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPxIF bit in the PIRx register is set and the CCPx module does not assert control of the CCPx pin (refer to the CCPxCON register).

#### 15.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is chosen (CCPxM<3:0> = 1011), the CCPx module does the following:

- Resets Timer1

- Starts an ADC conversion if ADC is enabled (CCP2 only)

The CCPx module does not assert control of the CCPx pin in this mode (refer to the CCPxCON register).

The Special Event Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPRxH, CCPRxL register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. This allows the CCPRxH, CCPRxL register pair to effectively provide a 16-bit programmable period register for Timer1.

Note 1: The Special Event Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

2: Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Special Event Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

#### 15.2.5 COMPARE DURING SLEEP

The Compare Mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

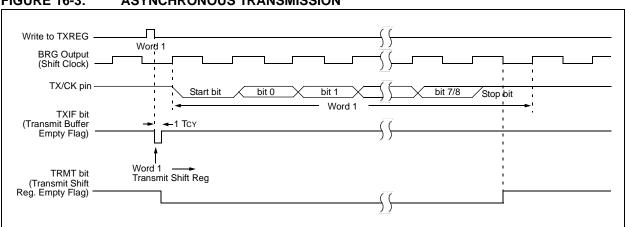

#### 16.1.1.4 TSR Status

The TRMT bit of the TXSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

Note: The TSR register is not mapped in data memory, so it is not available to the user.

#### 16.1.1.5 Transmitting 9-Bit Characters

The AUSART supports 9-bit character transmissions. When the TX9 bit of the TXSTA register is set the AUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXSTA register is the ninth, and Most Significant, data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXREG is written.

A special 9-bit Address mode is available for use with multiple receivers. Refer to **Section 16.1.2.7** "Address **Detection**" for more information on the Address mode.

#### 16.1.1.6 Asynchronous Transmission Set-up:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (Refer to Section 16.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 4. Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 7. Load 8-bit data into the TXREG register. This will start the transmission.

#### FIGURE 16-3: ASYNCHRONOUS TRANSMISSION

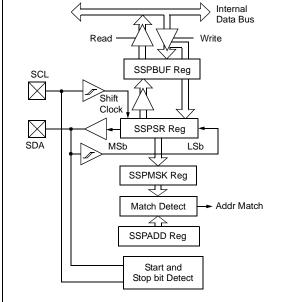

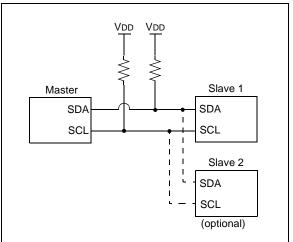

# 17.2 I<sup>2</sup>C Mode

The SSP module, in  $I^2C$  mode, implements all slave functions, except general call support. It provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the  $I^2C$  Standard mode specifications:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- Start and Stop bit interrupts enabled to support firmware Master mode

- Address masking

Two pins are used for data transfer; the SCL pin (clock line) and the SDA pin (data line). The user must configure the two pin's data direction bits as inputs in the appropriate TRIS register. Upon enabling  $I^2C$  mode, the  $I^2C$  slew rate limiters in the I/O pads are controlled by the SMP bit of SSPSTAT register. The SSP module functions are enabled by setting the SSPEN bit of SSPCON register.

Data is sampled on the rising edge and shifted out on the falling edge of the clock. This ensures that the SDA signal is valid during the SCL high time. The SCL clock input must have minimum high and low times for proper operation. Refer to **Section 23.0** "**Electrical Specifications**".

# FIGURE 17-7: I<sup>2</sup>C MODE BLOCK DIAGRAM

# FIGURE 17-8: TYPICAL I<sup>2</sup>C

#### CONNECTIONS

The SSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. They are:

- SSP Control (SSPCON) register

- SSP Status (SSPSTAT) register

- Serial Receive/Transmit Buffer (SSPBUF) register

- SSP Shift Register (SSPSR), not directly accessible

- SSP Address (SSPADD) register

- SSP Address Mask (SSPMSK) register

#### 17.2.1 HARDWARE SETUP

Selection of  $I^2C$  mode, with the SSPEN bit of the SSPCON register set, forces the SCL and SDA pins to be open drain, provided these pins are programmed as inputs by setting the appropriate TRISC bits. The SSP module will override the input state with the output data, when required, such as for Acknowledge and slave-transmitter sequences.

**Note:** Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module

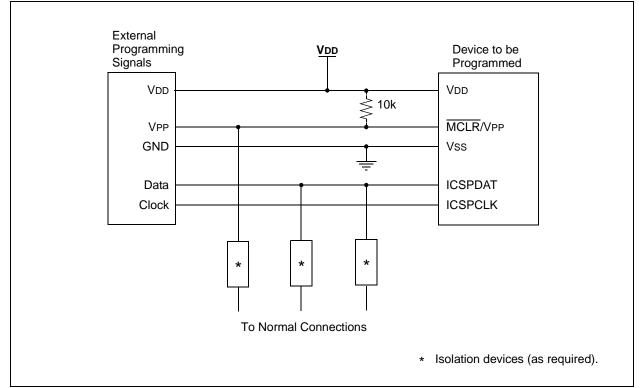

# 20.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

The device is placed into Program/Verify mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP from 0v to VPP. In Program/Verify mode the program memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ISCPCLK pin is the clock input. For more information on ICSP, refer to the "*PIC16(L)F72x Memory Programming Specification*" (DS41332).

**Note:** The ICD 2 produces a VPP voltage greater than the maximum VPP specification of the PIC16(L)F722/3/4/6/7. When using this programmer, an external circuit, such as the AC164112 MPLAB ICD 2 VPP voltage limiter, is required to keep the VPP voltage within the device specifications.

#### FIGURE 20-1: TYPICAL CONNECTION FOR ICSP™ PROGRAMMING

| MOVF             | Move f                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                          |

| Operation:       | (f) $\rightarrow$ (dest)                                                                                                                                                                                                                                                             |

| Status Affected: | Z                                                                                                                                                                                                                                                                                    |

| Description:     | The contents of register f is<br>moved to a destination dependent<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |

| Words:           | 1                                                                                                                                                                                                                                                                                    |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                          |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                           |

| MOVWF            | Move W to f                                                          |  |  |  |  |  |

|------------------|----------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] MOVWF f                                                      |  |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                                                  |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                                                |  |  |  |  |  |

| Status Affected: | None                                                                 |  |  |  |  |  |

| Description:     | Move data from W register to<br>register 'f'.                        |  |  |  |  |  |

| Words:           | 1                                                                    |  |  |  |  |  |

| Cycles:          | 1                                                                    |  |  |  |  |  |

| Example:         | MOVW OPTION<br>F                                                     |  |  |  |  |  |

|                  | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F<br>After Instruction |  |  |  |  |  |

|                  | $ \begin{array}{rcl} OPTION &= & 0x4F \\ W &= & 0x4F \end{array} $   |  |  |  |  |  |

| MOVLW            | Move literal to W                                                                         |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                         |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                       |  |  |  |  |  |

| Status Affected: | None                                                                                      |  |  |  |  |  |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |  |  |  |  |  |

| Words:           | 1                                                                                         |  |  |  |  |  |

| Cycles:          | 1                                                                                         |  |  |  |  |  |

| Example:         | MOVLW 0x5A                                                                                |  |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                             |  |  |  |  |  |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

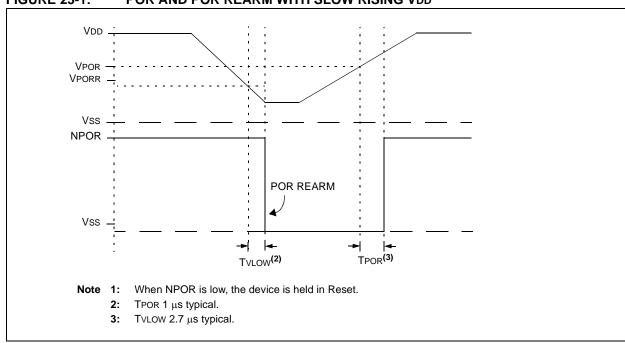

#### FIGURE 23-1: POR AND POR REARM WITH SLOW RISING VDD

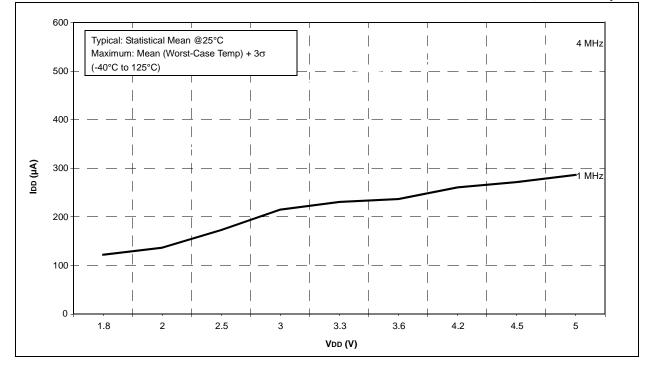

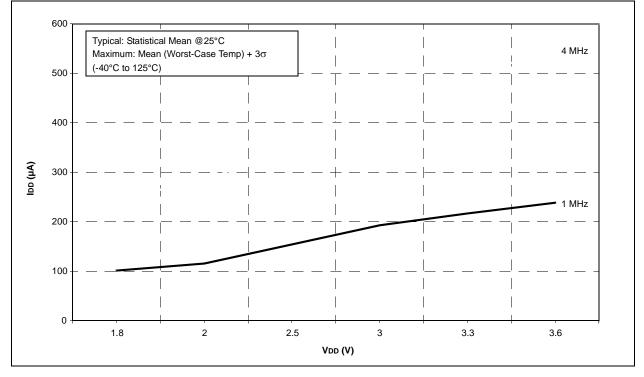

#### FIGURE 24-13: PIC16F722/3/4/6/7 MAXIMUM IDD vs. VDD OVER Fosc, XT MODE, VCAP = 0.1 µF

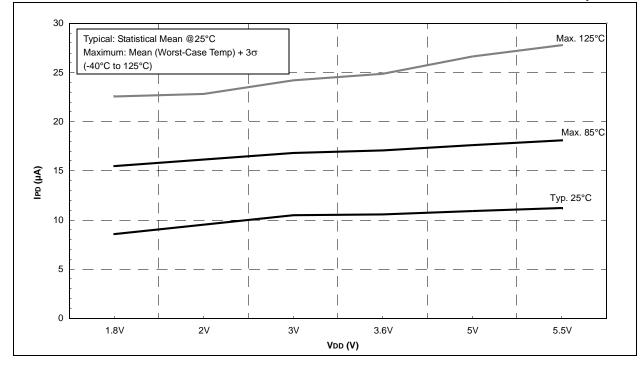

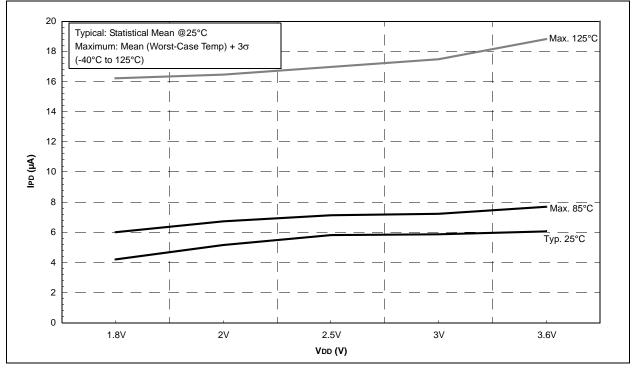

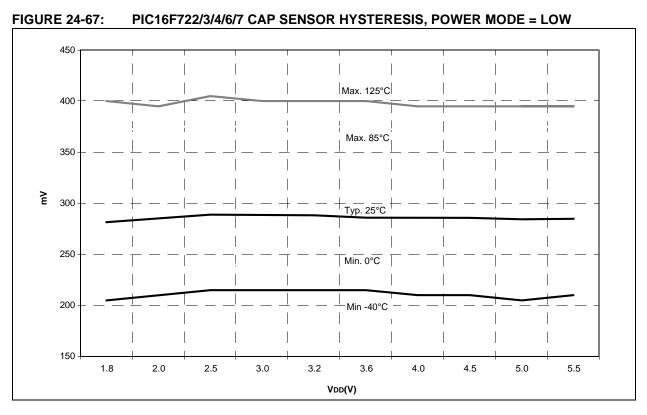

#### FIGURE 24-37: PIC16F722/3/4/6/7 CAP SENSE MEDIUM POWER IPD vs. VDD, VCAP = 0.1 µF

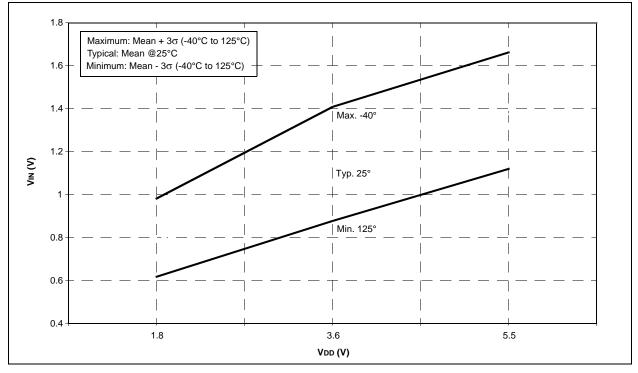

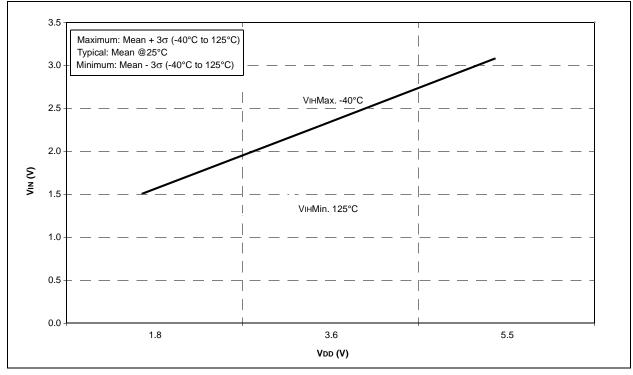

#### FIGURE 24-49: TTL INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

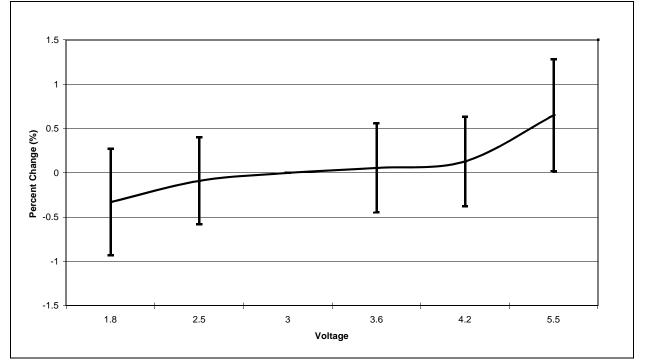

FIGURE 24-68: TYPICAL FVR (X1 AND X2) VS. SUPPLY VOLTAGE (V) NORMALIZED AT 3.0V

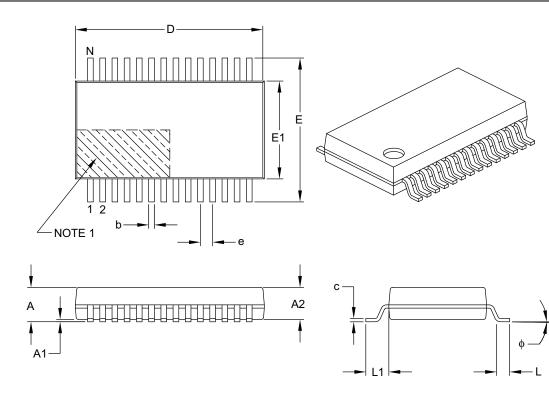

# 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units |          |       | MILLIMETERS |  |  |

|--------------------------|-------|----------|-------|-------------|--|--|

| Dimension Limits         |       | MIN      | NOM   | MAX         |  |  |

| Number of Pins           | Ν     | 28       |       |             |  |  |

| Pitch                    | е     | 0.65 BSC |       |             |  |  |

| Overall Height           | Α     | -        | -     | 2.00        |  |  |

| Molded Package Thickness | A2    | 1.65     | 1.75  | 1.85        |  |  |

| Standoff                 | A1    | 0.05     | -     | -           |  |  |

| Overall Width            | E     | 7.40     | 7.80  | 8.20        |  |  |

| Molded Package Width     | E1    | 5.00     | 5.30  | 5.60        |  |  |

| Overall Length           | D     | 9.90     | 10.20 | 10.50       |  |  |

| Foot Length              | L     | 0.55     | 0.75  | 0.95        |  |  |

| Footprint                | L1    | 1.25 REF |       |             |  |  |

| Lead Thickness           | с     | 0.09     | -     | 0.25        |  |  |

| Foot Angle               | φ     | 0°       | 4°    | 8°          |  |  |

| Lead Width               | b     | 0.22     | -     | 0.38        |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B