Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f723t-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| Device Overview                                                              |     |

|------------------------------------------------------------------------------|-----|

| Memory Organization                                                          |     |

| Resets                                                                       |     |

| Interrupts                                                                   |     |

| Low Dropout (LDO) Voltage Regulator                                          |     |

| I/O Ports                                                                    |     |

| Oscillator Module                                                            |     |

| Device Configuration                                                         |     |

| Analog-to-Digital Converter (ADC) Module                                     |     |

| Fixed Voltage Reference                                                      |     |

| Timer0 Module                                                                |     |

| Timer1 Module with Gate Control                                              |     |

| Timer2 Module                                                                |     |

| Capacitive Sensing Module                                                    |     |

| Capture/Compare/PWM (CCP) Module                                             |     |

| Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) |     |

| SSP Module Overview                                                          | 159 |

| Program Memory Read                                                          |     |

| Power-Down Mode (Sleep)                                                      |     |

| In-Circuit Serial Programming <sup>™</sup> (ICSP <sup>™</sup> )              |     |

| Instruction Set Summary                                                      |     |

| Development Support                                                          |     |

| Electrical Specifications                                                    |     |

| DC and AC Characteristics Graphs and Charts                                  |     |

| Packaging Information                                                        |     |

| Appendix A: Data Sheet Revision History                                      |     |

| Appendix B: Migrating From Other PIC® Devices                                |     |

| The Microchip Website                                                        |     |

| Customer Change Notification Service                                         |     |

| Customer Support                                                             |     |

| Product Identification System                                                | 279 |

| IADLL | ABLE 5-1. STATUS BITS AND THEIR SIGNIFICANCE |    |    |                                                         |  |  |  |  |

|-------|----------------------------------------------|----|----|---------------------------------------------------------|--|--|--|--|

| POR   | BOR                                          | то | PD | Condition                                               |  |  |  |  |

| 0     | x                                            | 1  | 1  | Power-on Reset or LDO Reset                             |  |  |  |  |

| 0     | x                                            | 0  | x  | Illegal, TO is set on POR                               |  |  |  |  |

| 0     | x                                            | x  | 0  | legal, PD is set on POR                                 |  |  |  |  |

| 1     | 0                                            | 1  | 1  | Brown-out Reset                                         |  |  |  |  |

| 1     | 1                                            | 0  | 1  | VDT Reset                                               |  |  |  |  |

| 1     | 1                                            | 0  | 0  | VDT Wake-up                                             |  |  |  |  |

| 1     | 1                                            | u  | u  | MCLR Reset during normal operation                      |  |  |  |  |

| 1     | 1                                            | 1  | 0  | MCLR Reset during Sleep or interrupt wake-up from Sleep |  |  |  |  |

## TABLE 3-1: STATUS BITS AND THEIR SIGNIFICANCE

# TABLE 3-2: RESET CONDITION FOR SPECIAL REGISTERS<sup>(2)</sup>

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 0000h                 | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 0000h                 | 0001 Ouuu          | uu               |

| WDT Reset                          | 0000h                 | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | uu               |

| Brown-out Reset                    | 0000h                 | 0001 luuu          | u0               |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

**2:** If a Status bit is not implemented, that bit will be read as '0'.

#### 4.5.4 PIR1 REGISTER

The PIR1 register contains the interrupt flag bits, as shown in Register 4-4.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 4-4: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W-0   | R/W-0 | R-0  | R-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|---------|-------|------|------|-------|--------|--------|--------|

| TMR1GIF | ADIF  | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| bit 7   |       |      |      |       |        |        | bit 0  |

| Legend:           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 7 | <b>TMR1GIF:</b> Timer1 Gate Interrupt Flag bit<br>1 = Timer1 Gate is inactive                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 0 = Timer1 Gate is active                                                                                                                           |

| bit 6 | ADIF: A/D Converter Interrupt Flag bit                                                                                                              |

|       | <ul> <li>1 = A/D conversion complete (must be cleared in software)</li> <li>0 = A/D conversion has not completed or has not been started</li> </ul> |

| bit 5 | RCIF: USART Receive Interrupt Flag bit                                                                                                              |

|       | <ul><li>1 = The USART receive buffer is full (cleared by reading RCREG)</li><li>0 = The USART receive buffer is not full</li></ul>                  |

| bit 4 | TXIF: USART Transmit Interrupt Flag bit                                                                                                             |

|       | <ul> <li>1 = The USART transmit buffer is empty (cleared by writing to TXREG)</li> <li>0 = The USART transmit buffer is full</li> </ul>             |

| bit 3 | SSPIF: Synchronous Serial Port (SSP) Interrupt Flag bit                                                                                             |

|       | <ul><li>1 = The Transmission/Reception is complete (must be cleared in software)</li><li>0 = Waiting to Transmit/Receive</li></ul>                  |

| bit 2 | CCP1IF: CCP1 Interrupt Flag bit                                                                                                                     |

|       | Capture mode:                                                                                                                                       |

|       | <ul> <li>1 = A TMR1 register capture occurred (must be cleared in software)</li> <li>0 = No TMR1 register capture occurred</li> </ul>               |

|       | Compare mode:                                                                                                                                       |

|       | <ul> <li>1 = A TMR1 register compare match occurred (must be cleared in software)</li> <li>0 = No TMR1 register compare match occurred</li> </ul>   |

|       | <u>PWM mode</u> :<br>Unused in this mode                                                                                                            |

| bit 1 | TMR2IF: Timer2 to PR2 Interrupt Flag bit                                                                                                            |

|       | <ul><li>1 = A Timer2 to PR2 match occurred (must be cleared in software)</li><li>0 = No Timer2 to PR2 match occurred</li></ul>                      |

| bit 0 | TMR1IF: Timer1 Overflow Interrupt Flag bit                                                                                                          |

|       | <ul> <li>1 = The TMR1 register overflowed (must be cleared in software)</li> <li>0 = The TMR1 register did not overflow</li> </ul>                  |

### 6.2 PORTA and the TRISA Registers

PORTA is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 6-3). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 6-1 shows how to initialize PORTA.

Reading the PORTA register (Register 6-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISA register (Register 6-3) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the

#### REGISTER 6-2: PORTA: PORTA REGISTER

TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

| Note: | The ANSELA register must be initialized     |  |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | to configure an analog channel as a digital |  |  |  |  |  |  |  |  |  |

|       | input. Pins configured as analog inputs     |  |  |  |  |  |  |  |  |  |

|       | will read '0'.                              |  |  |  |  |  |  |  |  |  |

| EXAMPLE 6-1:                                                                                              | INITIALIZING PORTA                                                                                          |

|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| BANKSEL PORTA<br>CLRF PORTA<br>BANKSEL ANSELA<br>CLRF ANSELA<br>BANKSEL TRISA<br>MOVLW 0Ch<br>MOVWF TRISA | ;<br>;Init PORTA<br>;<br>;digital I/O<br>;<br>;Set RA<3:2> as inputs<br>;and set RA<7:4,1:0><br>;as outputs |

| R/W-x    | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |

|----------|-------|-------|-------|-------|-------|-------|-------|--|

| RA7      | RA6   | RA5   | RA4   | RA3   | RA2   | RA1   | RA0   |  |

| bit 7    |       |       |       |       |       |       |       |  |

|          |       |       |       |       |       |       |       |  |

| l egend: |       |       |       |       |       |       |       |  |

| Legena.           |                                                       |                      |                    |

|-------------------|-------------------------------------------------------|----------------------|--------------------|

| R = Readable bit  | t W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |

| -n = Value at POR | '1' = Bit is set                                      | '0' = Bit is cleared | x = Bit is unknown |

**RA<7:0>**: PORTA I/O Pin bit 1 = Port pin is > VIH 0 = Port pin is < VIL

#### REGISTER 6-3: TRISA: PORTA TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-0

bit 7-0

TRISA<7:0>: PORTA Tri-State Control bit

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

## 6.5 **PORTD and TRISD Registers**

PORTD is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISD (Register 6-13). Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 6-4 shows how to initialize PORTD.

Reading the PORTD register (Register 6-12) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

Note: PORTD is available on PIC16F724/LF724 and PIC16F727/LF727 only.

The TRISD register (Register 6-13) controls the PORTD pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISD register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### EXAMPLE 6-4: INITIALIZING PORTD

| BANKSEL | PORTD       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTD       | ;Init PORTD            |

| BANKSEL | ANSELD      |                        |

| CLRF    | ANSELD      | ;Make PORTD digital    |

| BANKSEL | TRISD       | ;                      |

| MOVLW   | B`00001100′ | ;Set RD<3:2> as inputs |

| MOVWF   | TRISD       | ;and set RD<7:4,1:0>   |

|         |             | ;as outputs            |

|         |             |                        |

#### 6.5.1 ANSELD REGISTER

The ANSELD register (Register 6-9) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELD bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELD bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELD register must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

# **REGISTER 6-12: PORTD: PORTD REGISTER<sup>(1)</sup>**

| R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| RD7         | RD6   | RD5   | RD4   | RD3   | RD2   | RD1   | RD0   |  |  |

| bit 7 bit 0 |       |       |       |       |       |       |       |  |  |

| Legend:           |                  |                                       |                    |  |  |

|-------------------|------------------|---------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | it U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                  | x = Bit is unknown |  |  |

bit 7-0 RD<7:0>: PORTD General Purpose I/O Pin bits

1 = Port pin is > VIH

0 = Port pin is < VIL

Note 1: PORTD is not implemented on PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'.

# PIC16(L)F722/3/4/6/7

| REGISTER      | <b>19-2.</b> ADCO              |                        | ITROL REG        |                    |                    |                  |        |  |  |  |

|---------------|--------------------------------|------------------------|------------------|--------------------|--------------------|------------------|--------|--|--|--|

| U-0           | R/W-0                          | R/W-0                  | R/W-0            | U-0                | U-0                | R/W-0            | R/W-0  |  |  |  |

| _             | ADCS2                          | ADCS1                  | ADCS0            | _                  | _                  | ADREF1           | ADREF0 |  |  |  |

| bit 7         |                                |                        |                  |                    |                    |                  | bit 0  |  |  |  |

| Legend:       |                                |                        |                  |                    |                    |                  |        |  |  |  |

| R = Readabl   | le bit                         | W = Writable bi        | t                | U = Unimpleme      | ented bit, read as | s 'O'            |        |  |  |  |

| -n = Value at | t POR                          | '1' = Bit is set       |                  | '0' = Bit is clear | red                | x = Bit is unkno | wn     |  |  |  |

|               |                                |                        |                  |                    |                    |                  |        |  |  |  |

| bit 7         | Unimplemente                   | ed: Read as '0'        |                  |                    |                    |                  |        |  |  |  |

| bit 6-4       | ADCS<2:0>: A                   | /D Conversion C        | lock Select bits |                    |                    |                  |        |  |  |  |

|               | 000 = Fosc/2                   |                        |                  |                    |                    |                  |        |  |  |  |

|               | 001 = Fosc/8                   |                        |                  |                    |                    |                  |        |  |  |  |

|               | 010 = Fosc/32                  | -                      |                  |                    |                    |                  |        |  |  |  |

|               | · · ·                          | ock supplied from      | a dedicated RC   | Coscillator)       |                    |                  |        |  |  |  |

|               | 100 = Fosc/4<br>101 = Fosc/16  |                        |                  |                    |                    |                  |        |  |  |  |

|               | 101 = FOSC/10<br>110 = FOSC/64 | -                      |                  |                    |                    |                  |        |  |  |  |

|               |                                | ,<br>ock supplied from | a dedicated RC   | coscillator)       |                    |                  |        |  |  |  |

| bit 3-2       | Unimplemente                   | ••                     |                  | ,                  |                    |                  |        |  |  |  |

| bit 1-0       | ADREF<1:0>:                    | Voltage Referend       | e Configuration  | bits               |                    |                  |        |  |  |  |

|               | 0x = VREF is connected to VDD  |                        |                  |                    |                    |                  |        |  |  |  |

|               | 10 = VREF is c                 | connected to exte      | rnal VREF (RA3   | /AN3)              |                    |                  |        |  |  |  |

|               |                                |                        | nal Fixed Voltag |                    |                    |                  |        |  |  |  |

# REGISTER 9-2: ADCON1: A/D CONTROL REGISTER 1

#### REGISTER 9-3: ADRES: ADC RESULT REGISTER

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 | ADRES1 | ADRES0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 **ADRES<7:0>**: ADC Result Register bits 8-bit conversion result.

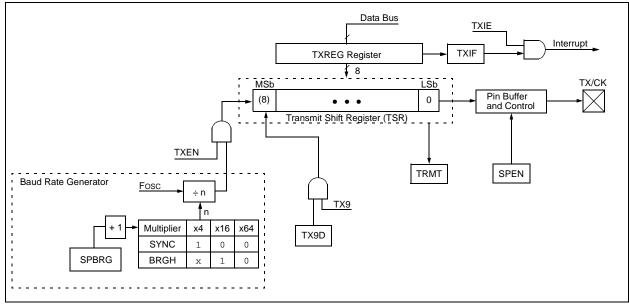

# 16.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (AUSART)

The Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The AUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The AUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- Address detection in 9-bit mode

- Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- · Half-duplex synchronous slave

- Sleep operation

Block diagrams of the AUSART transmitter and receiver are shown in Figure 16-1 and Figure 16-2.

# FIGURE 16-1: AUSART TRANSMIT BLOCK DIAGRAM

| R/W-0         | R/W-0                                                                                                                                      | R/W-0                                                            | R/W-0            | R/W-0            | R-0               | R-0               | R-x          |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------|------------------|-------------------|-------------------|--------------|--|--|--|

| SPEN          | RX9                                                                                                                                        | SREN                                                             | CREN             | ADDEN            | FERR              | OERR              | RX9D         |  |  |  |

| bit 7         |                                                                                                                                            |                                                                  |                  | •<br>•           |                   |                   | bit (        |  |  |  |

|               |                                                                                                                                            |                                                                  |                  |                  |                   |                   |              |  |  |  |

| Legend:       |                                                                                                                                            |                                                                  |                  |                  |                   | ( <b>a</b> )      |              |  |  |  |

| R = Readable  |                                                                                                                                            | W = Writable                                                     |                  | -                | mented bit, read  |                   |              |  |  |  |

| -n = Value at | POR                                                                                                                                        | '1' = Bit is set                                                 |                  | '0' = Bit is cle | ared              | x = Bit is unkn   | lown         |  |  |  |

| bit 7         | CDEN: Coriol                                                                                                                               | Port Enable b                                                    | :(1)             |                  |                   |                   |              |  |  |  |

|               |                                                                                                                                            |                                                                  |                  | T and TX/CK n    | ins as serial por | rt nine)          |              |  |  |  |

|               |                                                                                                                                            | rt disabled (be                                                  |                  |                  | ins as senai poi  | t pins)           |              |  |  |  |

| bit 6         | <b>RX9:</b> 9-bit Re                                                                                                                       | ceive Enable b                                                   | oit              |                  |                   |                   |              |  |  |  |

|               | 1 = Selects 9                                                                                                                              | -bit reception                                                   |                  |                  |                   |                   |              |  |  |  |

|               | 0 = Selects 8                                                                                                                              | -bit reception                                                   |                  |                  |                   |                   |              |  |  |  |

| bit 5         | -                                                                                                                                          | Receive Enal                                                     | ole bit          |                  |                   |                   |              |  |  |  |

|               | Asynchronous                                                                                                                               | <u>s mode</u> :                                                  |                  |                  |                   |                   |              |  |  |  |

|               | Don't care                                                                                                                                 | mode - Maste                                                     | vr.              |                  |                   |                   |              |  |  |  |

|               | -                                                                                                                                          | <u>Synchronous mode – Master</u> :<br>1 = Enables single receive |                  |                  |                   |                   |              |  |  |  |

|               |                                                                                                                                            | single receive                                                   |                  |                  |                   |                   |              |  |  |  |

|               |                                                                                                                                            | ared after rece                                                  | •                | ete.             |                   |                   |              |  |  |  |

|               | -                                                                                                                                          | mode – Slave                                                     | <u>.</u>         |                  |                   |                   |              |  |  |  |

| L:1 1         | Don't care                                                                                                                                 |                                                                  | Enchla hit       |                  |                   |                   |              |  |  |  |

| bit 4         |                                                                                                                                            | nuous Receive                                                    | Enable bit       |                  |                   |                   |              |  |  |  |

|               | Asynchronous mode:<br>1 = Enables receiver                                                                                                 |                                                                  |                  |                  |                   |                   |              |  |  |  |

|               | 0 = Disables                                                                                                                               |                                                                  |                  |                  |                   |                   |              |  |  |  |

|               | Synchronous                                                                                                                                | mode:                                                            |                  |                  |                   |                   |              |  |  |  |

|               |                                                                                                                                            | continuous rec<br>continuous rec                                 |                  | ble bit CREN is  | cleared (CREN     | l overrides SRE   | EN)          |  |  |  |

| bit 3         |                                                                                                                                            |                                                                  |                  |                  |                   |                   |              |  |  |  |

| DIL J         | ADDEN: Address Detect Enable bit<br>Asynchronous mode 9-bit (RX9 = 1):                                                                     |                                                                  |                  |                  |                   |                   |              |  |  |  |

|               | 1 = Enables address detection, enable interrupt and load the receive buffer when RSR<8> is set                                             |                                                                  |                  |                  |                   |                   |              |  |  |  |

|               | 0 = Disables                                                                                                                               | address detec                                                    | tion, all bytes  |                  | nd ninth bit can  |                   |              |  |  |  |

|               | <u>Asynchronous mode 8-bit (RX9 = 0)</u> :                                                                                                 |                                                                  |                  |                  |                   |                   |              |  |  |  |

|               | Don't care<br>Synchronous                                                                                                                  | modo:                                                            |                  |                  |                   |                   |              |  |  |  |

|               | Must be set to                                                                                                                             |                                                                  |                  |                  |                   |                   |              |  |  |  |

| bit 2         | FERR: Frami                                                                                                                                |                                                                  |                  |                  |                   |                   |              |  |  |  |

|               |                                                                                                                                            | -                                                                | updated by rea   | adina RCREG I    | edister and rec   | eive next valid l | ovte)        |  |  |  |

|               | <ul> <li>1 = Framing error (can be updated by reading RCREG register and receive next valid byte)</li> <li>0 = No framing error</li> </ul> |                                                                  |                  |                  |                   |                   |              |  |  |  |

| bit 1         | OERR: Overr                                                                                                                                | un Error bit                                                     |                  |                  |                   |                   |              |  |  |  |

|               | 1 = Overrun<br>0 = No overr                                                                                                                |                                                                  | leared by clea   | aring bit CREN   | )                 |                   |              |  |  |  |

| bit 0         | RX9D: Ninth                                                                                                                                | bit of Received                                                  | l Data           |                  |                   |                   |              |  |  |  |

|               | This can be a                                                                                                                              | ddress/data bi                                                   | t or a parity bi | t and must be o  | calculated by us  | er firmware.      |              |  |  |  |

|               | he AUSART m<br>RISx = 1.                                                                                                                   | odule automa                                                     | tically change   | es the pin fro   | m tri-state to o  | drive as neede    | ed. Configur |  |  |  |

# REGISTER 16-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

# 17.2.2 START AND STOP CONDITIONS

During times of no data transfer (Idle time), both the clock line (SCL) and the data line (SDA) are pulled high through external pull-up resistors. The Start and Stop conditions determine the start and stop of data transmission. The Start condition is defined as a high-to-low transition of the SDA line while SCL is high. The Stop condition is defined as a low-to-high transition of the SDA line while SCL is high.

Figure 17-9 shows the Start and Stop conditions. A master device generates these conditions for starting and terminating data transfer. Due to the definition of the Start and Stop conditions, when data is being transmitted, the SDA line can only change state when the SCL line is low.

# 17.2.3 ACKNOWLEDGE

After the valid reception of an address or data byte, the hardware automatically will generate the Acknowledge (ACK) pulse and load the SSPBUF register with the received value currently in the SSPSR register. There are certain conditions that will cause the SSP module not to generate this ACK pulse. They include any or all of the following:

- The Buffer Full bit, BF of the SSPSTAT register, was set before the transfer was received.

- The SSP Overflow bit, SSPOV of the SSPCON register, was set before the transfer was received.

- The SSP Module is being operated in Firmware Master mode.

In such a case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF of the PIR1 register is set. Table 17-2 shows the results of when a data transfer byte is received, given the status of bits BF and SSPOV. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

# FIGURE 17-9: START AND STOP CONDITIONS

| Status Bits as Data<br>Transfer is Received |       | $SSPSR \to SSPBUF$ | Generate ACK | Set bit SSPIF<br>(SSP Interrupt occurs |  |

|---------------------------------------------|-------|--------------------|--------------|----------------------------------------|--|

| BF                                          | SSPOV |                    | Pulse        | if enabled)                            |  |

| 0                                           | 0     | Yes                | Yes          | Yes                                    |  |

| 1                                           | 0     | No                 | No           | Yes                                    |  |

| 1                                           | 1     | No                 | No           | Yes                                    |  |

| 0                                           | 1     | No                 | No           | Yes                                    |  |

Note 1: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

# 19.2 Wake-up Using Interrupts

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will not be cleared, the TO bit will not be set and the PD bit will not be cleared.

- If the interrupt occurs **during or after** the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

#### FIGURE 19-1: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| : 1 02 03 04;01 02 03 04;01 02 03 04;01 02 03 04;01 02 03 04;01 02 03 04;01 02 03 04;01 02 03 04;01 02 03 04;01<br>                                                                                                                                               | Q4.<br>~' |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|                                                                                                                                                                                                                                                                   |           |

| INT pin                                                                                                                                                                                                                                                           | !         |

| INTF flag<br>(INTCON reg.)                                                                                                                                                                                                                                        |           |

| GIE bit<br>(INTCON reg.), Sleep                                                                                                                                                                                                                                   |           |

|                                                                                                                                                                                                                                                                   |           |

| PC         V         PC + 1         V         PC + 2         V         PC + 2         V         PC + 2         V         0005h           Instruction {         Inst(PC) = Sleep         Inst(PC + 1)         Inst(PC + 2)         Inst(0004h)         Inst(0005h) | h)        |

| Instruction Inst(PC - 1) Sleep Inst(PC + 1) Dummy Cycle Dummy Cycle Inst(0004                                                                                                                                                                                     | h)        |

Note 1: XT, HS or LP Oscillator mode assumed.

2: TOST = 1024 Tosc (drawing not to scale). This delay does not apply to EC and RC Oscillator modes.

3: GIE = 1 assumed. In this case after wake-up, the processor jumps to 0004h. If GIE = 0, execution will continue in-line.

4: CLKOUT is not available in XT, HS, LP or EC Oscillator modes, but shown here for timing reference.

| Name   | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on all other Resets |

|--------|---------|-------|-------|-------|-------|--------|--------|--------|----------------------|---------------------------|

| IOCB   | IOCB7   | IOCB6 | IOCB5 | IOCB4 | IOCB3 | IOCB2  | IOCB1  | IOCB0  | 0000 0000            | 0000 0000                 |

| INTCON | GIE     | PEIE  | TOIE  | INTE  | RBIE  | T0IF   | INTF   | RBIF   | 0000 0000            | 0000 0000                 |

| PIE1   | TMR1GIE | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                 |

| PIE2   | —       | _     | _     | _     | _     | —      | _      | CCP2IE | 0                    | 0                         |

| PIR1   | TMR1GIF | ADIF  | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                 |

| PIR2   | —       | _     | _     | —     | —     | —      | —      | CCP2IF | 0                    | 0                         |

#### TABLE 19-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used in Power-Down mode.

| PIC16LF722/3/4/6/7<br>PIC16F722/3/4/6/7 |        |                                                        |                          | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                          |                  |                                                                                                                                                                                                                                                              |  |  |  |

|-----------------------------------------|--------|--------------------------------------------------------|--------------------------|-------------------------------------------------------|--------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                         |        |                                                        |                          | $\begin{array}{llllllllllllllllllllllllllllllllllll$  |                          |                  |                                                                                                                                                                                                                                                              |  |  |  |

| Param.<br>No.                           | Sym.   | Characteristic                                         | Min.                     | Тур†                                                  | Max.                     | Units            | Conditions                                                                                                                                                                                                                                                   |  |  |  |

| D001                                    | Vdd    | Supply Voltage                                         |                          |                                                       |                          |                  |                                                                                                                                                                                                                                                              |  |  |  |

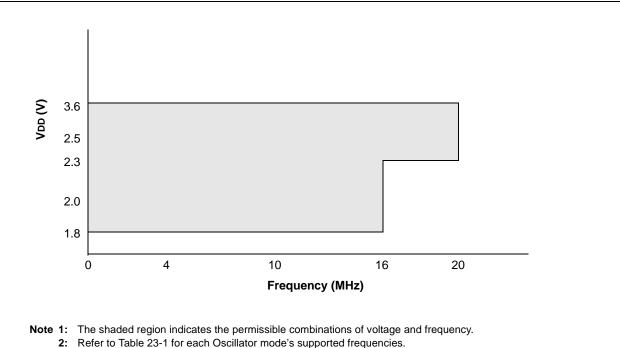

|                                         |        | PIC16LF722/3/4/6/7                                     | 1.8<br>1.8<br>2.3<br>2.5 |                                                       | 3.6<br>3.6<br>3.6<br>3.6 | V<br>V<br>V<br>V | Fosc $\leq$ 16 MHz: HFINTOSC, EC<br>Fosc $\leq$ 4 MHz<br>Fosc $\leq$ 20 MHz, EC<br>Fosc $\leq$ 20 MHz, HS                                                                                                                                                    |  |  |  |

| D001                                    |        | PIC16F722/3/4/6/7                                      | 1.8<br>1.8<br>2.3<br>2.5 |                                                       | 5.5<br>5.5<br>5.5<br>5.5 | V<br>V<br>V<br>V | Fosc $\leq$ 16 MHz: HFINTOSC, EC<br>Fosc $\leq$ 4 MHz<br>Fosc $\leq$ 20 MHz, EC<br>Fosc $\leq$ 20 MHz, HS                                                                                                                                                    |  |  |  |

| D002*                                   | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>              |                          |                                                       |                          |                  |                                                                                                                                                                                                                                                              |  |  |  |

|                                         |        | PIC16LF722/3/4/6/7                                     | 1.5                      |                                                       | _                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |  |  |

| D002*                                   |        | PIC16F722/3/4/6/7                                      | 1.7                      | _                                                     | _                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |  |  |

|                                         | VPOR*  | Power-on Reset Release Voltage                         | _                        | 1.6                                                   | _                        | V                |                                                                                                                                                                                                                                                              |  |  |  |

|                                         | VPORR* | Power-on Reset Rearm Voltage                           |                          |                                                       |                          |                  |                                                                                                                                                                                                                                                              |  |  |  |

|                                         |        | PIC16LF722/3/4/6/7                                     | _                        | 0.8                                                   | _                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |  |  |

|                                         |        | PIC16F722/3/4/6/7                                      |                          | 1.7                                                   | _                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |  |  |

| D003                                    | Vfvr   | Fixed Voltage Reference Voltage,<br>Initial Accuracy   | -8<br>-8<br>-8           | <br>                                                  | 6<br>6<br>6              | %<br>%<br>%      | $ \begin{array}{l} {\sf VFVR} = 1.024{\sf V},  {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 2.048{\sf V},  {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 4.096{\sf V},  {\sf VDD} \geq 4.75{\sf V}; \\ {\sf -40} \leq {\sf TA} \leq 85^{\circ}{\sf C} \end{array} $ |  |  |  |

|                                         |        |                                                        | -8<br>-8<br>-8           |                                                       | 6<br>6<br>6              | %<br>%<br>%      | $ \begin{array}{l} V{\sf FVR} = 1.024V, \ V{\sf DD} \geq 2.5V \\ V{\sf FVR} = 2.048V, \ V{\sf DD} \geq 2.5V \\ V{\sf FVR} = 4.096V, \ V{\sf DD} \geq 4.75V; \\ -40 \leq {\sf TA} \leq 125^{\circ}{\sf C} \end{array} $                                       |  |  |  |

| D004*                                   | SVDD   | VDD Rise Rate to ensure internal Power-on Reset signal | 0.05                     | —                                                     | —                        | V/ms             | See Section 3.2 "Power-on Reset (POR)" for details.                                                                                                                                                                                                          |  |  |  |

# 23.1 DC Characteristics: PIC16(L)F722/3/4/6/7-I/E (Industrial, Extended)

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

# 23.4 DC Characteristics: PIC16(L)F722/3/4/6/7-I/E (Continued)

|              |        | HARACTERISTICS                                   | Standard Operating Conditions (unless otherwise stated)Operating temperature -40°C $\leq$ TA $\leq$ +85°C for industrial-40°C $\leq$ TA $\leq$ +125°C for extended |      |      |       |                                                                         |  |  |

|--------------|--------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------------------------------------------------------------------------|--|--|

| Param<br>No. | Sym.   | Characteristic                                   | Min.                                                                                                                                                               | Тур† | Max. | Units | Conditions                                                              |  |  |

| D130         | Eр     | Cell Endurance                                   | 100                                                                                                                                                                | 1k   | —    | E/W   | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

| D131         |        | VDD for Read                                     | Vmin                                                                                                                                                               | —    | _    | V     |                                                                         |  |  |

|              |        | Voltage on MCLR/VPP during<br>Erase/Program      | 8.0                                                                                                                                                                | _    | 9.0  | V     | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

|              |        | VDD for Bulk Erase                               | 2.7                                                                                                                                                                | 3    | _    | V     | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

| D132         | VPEW   | VDD for Write or Row Erase                       | 2.7                                                                                                                                                                | _    | —    | V     | VMIN = Minimum operating voltage<br>VMAX = Maximum operating<br>voltage |  |  |

|              | IPPPGM | Current on MCLR/VPP during<br>Erase/Write        | —                                                                                                                                                                  | -    | 5.0  | mA    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

|              | IDDPGM | Current on VDD during Erase/<br>Write            | —                                                                                                                                                                  |      | 5.0  | mA    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

| D133         | TPEW   | Erase/Write cycle time                           | -                                                                                                                                                                  |      | 2.8  | ms    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

| D134         | TRETD  | Characteristic Retention                         | 40                                                                                                                                                                 | —    | —    | Year  | Provided no other specifications are violated                           |  |  |

|              |        | VCAP Capacitor Charging                          | •                                                                                                                                                                  | •    |      |       |                                                                         |  |  |

| D135         |        | Charging current                                 | —                                                                                                                                                                  | 200  | _    | μΑ    |                                                                         |  |  |

| D135A        |        | Source/sink capability when<br>charging complete | —                                                                                                                                                                  | 0.0  | —    | mA    |                                                                         |  |  |

Legend: TBD = To Be Determined

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

**3:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: Including OSC2 in CLKOUT mode.

# PIC16(L)F722/3/4/6/7

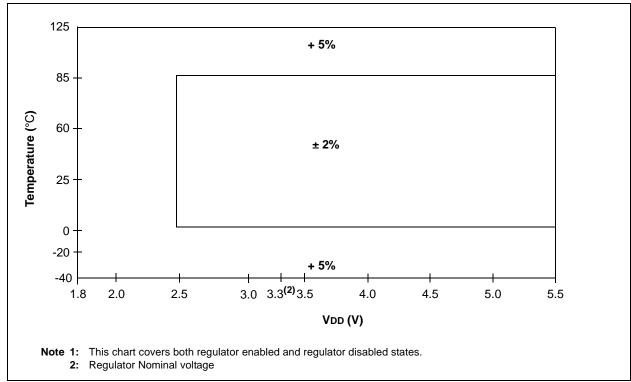

FIGURE 23-6: HFINTOSC FREQUENCY ACCURACY OVER DEVICE VDD AND TEMPERATURE

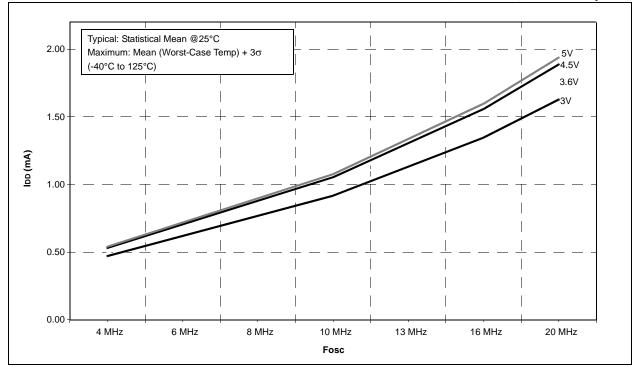

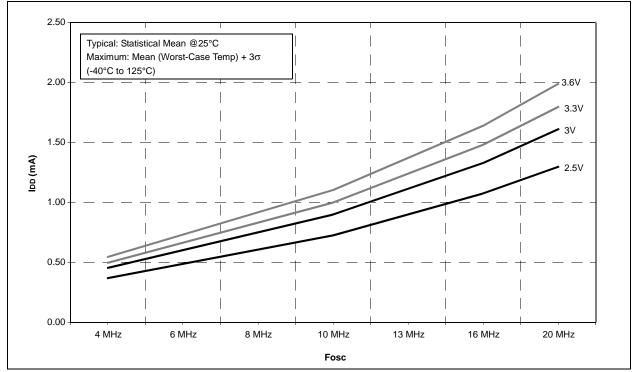

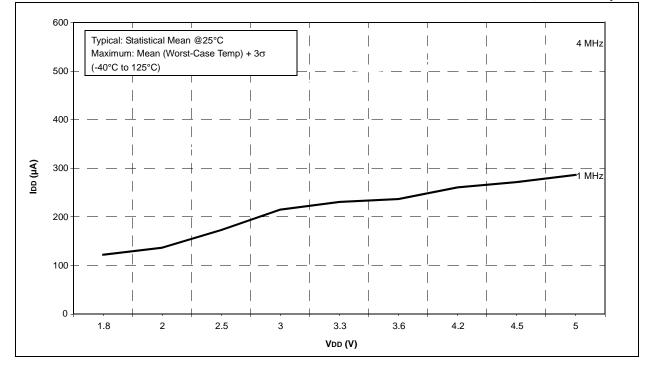

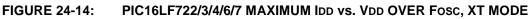

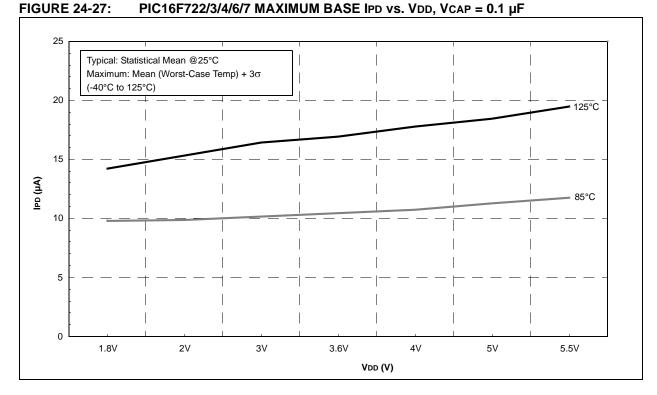

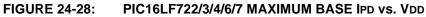

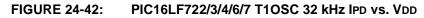

#### FIGURE 24-13: PIC16F722/3/4/6/7 MAXIMUM IDD vs. VDD OVER Fosc, XT MODE, VCAP = 0.1 µF

#### © 2007-2015 Microchip Technology Inc.

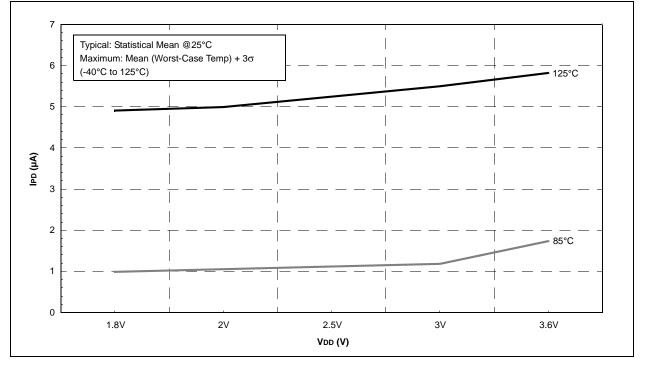

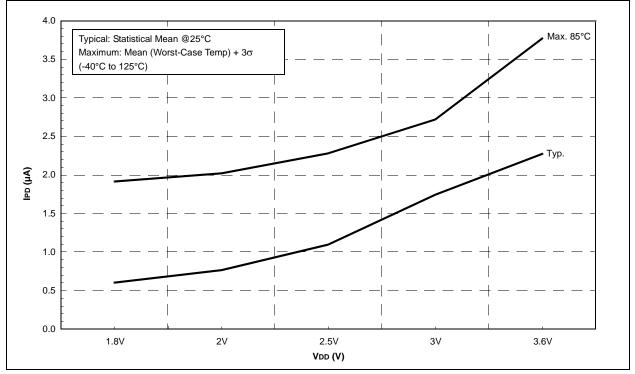

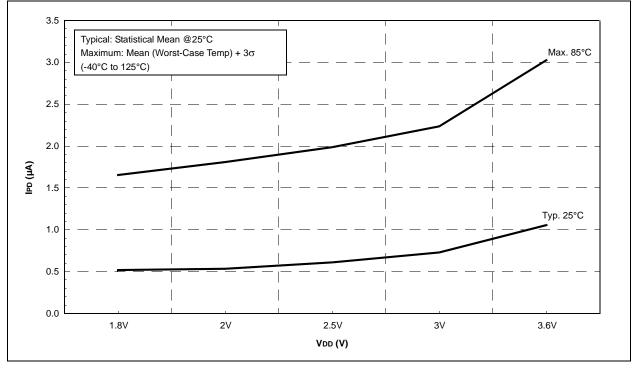

#### FIGURE 24-47: PIC16F722/3/4/6/7 WDT IPD vs. VDD, VCAP = 0.1 µF

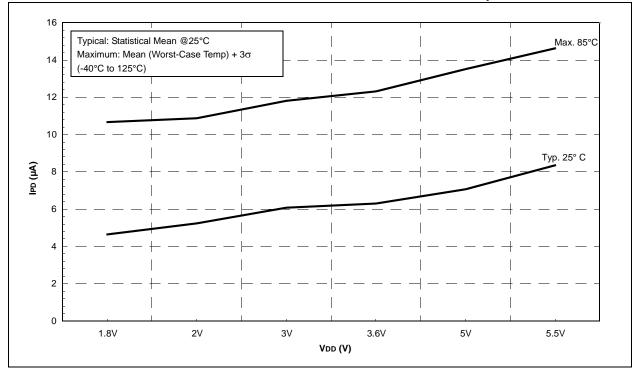

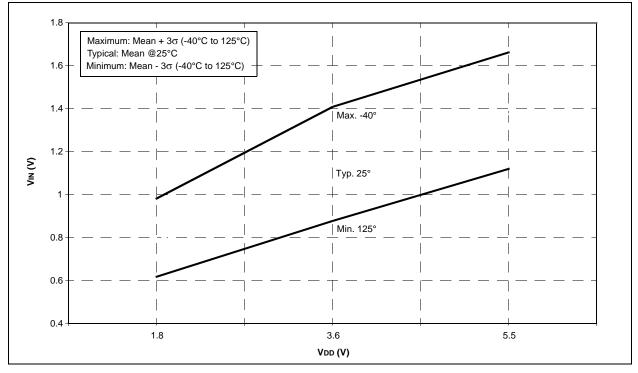

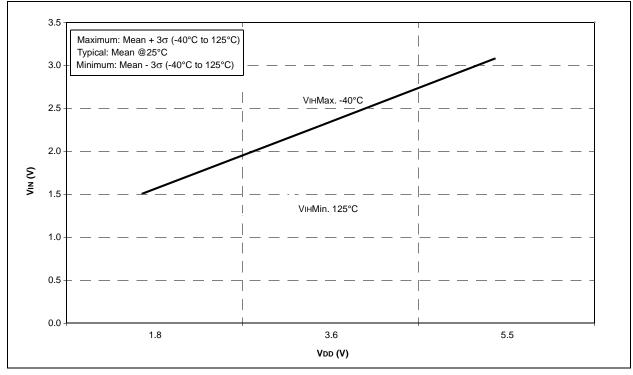

#### FIGURE 24-49: TTL INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

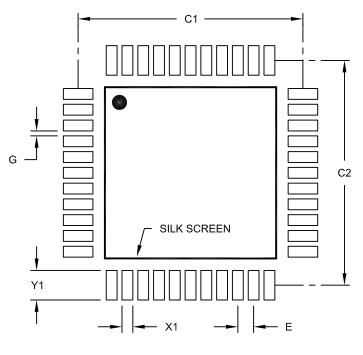

# 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**RECOMMENDED LAND PATTERN**

|                          | MILLIMETERS |      |          |      |  |

|--------------------------|-------------|------|----------|------|--|

| Dimension                | MIN         | NOM  | MAX      |      |  |

| Contact Pitch            | E           |      | 0.80 BSC |      |  |

| Contact Pad Spacing      | C1          |      | 11.40    |      |  |

| Contact Pad Spacing      | C2          |      | 11.40    |      |  |

| Contact Pad Width (X44)  | X1          |      |          | 0.55 |  |

| Contact Pad Length (X44) | Y1          |      |          | 1.50 |  |

| Distance Between Pads    | G           | 0.25 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076A