Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014.110                   |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f723t-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| FIGURE 2-5: | PIC16F723/LF723 AND PIC16F724/LF724 SPECIAL FUNCTION REGISTERS |

|-------------|----------------------------------------------------------------|

|             |                                                                |

| Indirect addr. <sup>(*)</sup> | 00h     | Indirect addr. <sup>(*)</sup>   | 80h    | Indirect addr. <sup>(*)</sup>           | 100h         | Indirect addr.(*)     | 180h |

|-------------------------------|---------|---------------------------------|--------|-----------------------------------------|--------------|-----------------------|------|

| TMR0                          | 01h     | OPTION                          | 81h    | TMR0                                    | 101h         | OPTION                | 181h |

| PCL                           | 02h     | PCL                             | 82h    | PCL                                     | 102h         | PCL                   | 182h |

| STATUS                        | 03h     | STATUS                          | 83h    | STATUS                                  | 103h         | STATUS                | 183h |

| FSR                           | 04h     | FSR                             | 84h    | FSR                                     | 104h         | FSR                   | 184h |

| PORTA                         | 05h     | TRISA                           | 85h    |                                         | 105h         | ANSELA                | 185h |

| PORTB                         | 06h     | TRISB                           | 86h    |                                         | 106h         | ANSELB                | 186h |

| PORTC                         | 07h     | TRISC                           | 87h    |                                         | 107h         |                       | 187h |

| PORTD <sup>(1)</sup>          | 08h     | TRISD <sup>(1)</sup>            | 88h    | CPSCON0                                 | 108h         | ANSELD <sup>(1)</sup> | 188h |

| PORTE                         | 09h     | TRISE                           | 89h    | CPSCON1                                 | 109h         | ANSELE <sup>(1)</sup> | 189h |

| PCLATH                        | 0Ah     | PCLATH                          | 8Ah    | PCLATH                                  | 10Ah         | PCLATH                | 18Ah |

| INTCON                        | 0Bh     | INTCON                          | 8Bh    | INTCON                                  | 10Bh         | INTCON                | 18Bh |

| PIR1                          | 0Ch     | PIE1                            | 8Ch    | PMDATL                                  | 10Ch         | PMCON1                | 18Ch |

| PIR2                          | 0Dh     | PIE2                            | 8Dh    | PMADRL                                  | 10Dh         | Reserved              | 18Dh |

| TMR1L                         | 0Eh     | PCON                            | 8Eh    | PMDATH                                  | 10Eh         | Reserved              | 18Eh |

| TMR1H                         | 0Fh     | T1GCON                          | 8Fh    | PMADRH                                  | 10Fh         | Reserved              | 18Fh |

| T1CON                         | 10h     | OSCCON                          | 90h    |                                         | 110h         |                       | 190h |

| TMR2                          | 11h     | OSCTUNE                         | 91h    |                                         | 111h         |                       | 191h |

| T2CON                         | 12h     | PR2                             | 92h    |                                         | 112h         |                       | 192h |

| SSPBUF                        | 13h     | SSPADD/SSPMSK                   | 93h    |                                         | 113h         |                       | 193h |

| SSPCON                        | 14h     | SSPSTAT                         | 94h    |                                         | 114h         |                       | 194h |

| CCPR1L                        | 15h     | WPUB                            | 95h    |                                         | 115h         |                       | 195h |

| CCPR1H                        | 16h     | IOCB                            | 96h    | -                                       | 116h         |                       | 196h |

| CCP1CON                       | 17h     |                                 | 97h    | -                                       | 117h         |                       | 197h |

| RCSTA                         | 18h     | TXSTA                           | 98h    | -                                       | 118h         |                       | 198h |

| TXREG                         | 19h     | SPBRG                           | 99h    |                                         | 119h         |                       | 199h |

| RCREG                         | 1Ah     |                                 | 9Ah    |                                         | 11Ah         |                       | 19Ah |

| CCPR2L                        | 1Bh     |                                 | 9Bh    |                                         | 11Bh         |                       | 19Bh |

| CCPR2H                        | 1Ch     | APFCON                          | 9Ch    |                                         | 11Ch         |                       | 19Ch |

| CCP2CON                       | 1Dh     | FVRCON                          | 9Dh    |                                         | 11Dh         |                       | 19Dh |

| ADRES                         | 1Eh     |                                 | 9Eh    |                                         | 11Eh         |                       | 19Eh |

| ADCON0                        | 1Fh     | ADCON1                          | 9Fh    |                                         | 11Fh         |                       | 19Fh |

|                               | 20h     | General                         | A0h    | General Purpose<br>Register             | 120h         |                       | 1A0h |

| General<br>Purpose            |         | Purpose<br>Register<br>80 Bytes |        | 16 Bytes                                | 12Fh<br>130h |                       |      |

| Register                      |         |                                 | EFh    |                                         | 16Fh         |                       | 1EFh |

| 96 Bytes                      |         | Accesses<br>70h-7Fh             | F0h    | Accesses<br>70h-7Fh                     | 170h         | Accesses<br>70h-7Fh   | 1F0h |

|                               | 7Fh     | 701-7111                        | FFh    | / ///////////////////////////////////// | 17Fh         | 701-7111              | 1FFh |

| Bank 0                        | ],      | Bank 1                          | l      | Bank 2                                  | ]            | Bank 3                | J    |

| nd: = Unimple                 | emented | data memory locatio             | ns rea | d as '0'                                |              |                       |      |

| Address               | Name                  | Bit 7         | Bit 6                                                        | Bit 5                   | Bit 4          | Bit 3                   | Bit 2                 | Bit 1                 | Bit 0                 | Value on:<br>POR, BOR | Page   |

|-----------------------|-----------------------|---------------|--------------------------------------------------------------|-------------------------|----------------|-------------------------|-----------------------|-----------------------|-----------------------|-----------------------|--------|

| Bank 1                |                       |               |                                                              |                         |                |                         |                       |                       |                       |                       |        |

| 80h <sup>(2)</sup>    | INDF                  | Addressing    | this location                                                | uses conten             | ts of FSR to a | ddress data             | memory (not           | a physical re         | gister)               | xxxx xxxx             | 29,37  |

| 81h                   | OPTION_REG            | RBPU          | INTEDG                                                       | TOCS                    | TOSE           | PSA                     | PS2                   | PS1                   | PS0                   | 1111 1111             | 26,37  |

| 82h <sup>(2)</sup>    | PCL                   | Program Co    | Program Counter (PC) Least Significant Byte                  |                         |                |                         |                       |                       |                       |                       |        |

| 83h <sup>(2)</sup>    | STATUS                | IRP           | RP1                                                          | RP0                     | TO             | PD                      | Z                     | DC                    | С                     | 0001 1xxx             | 25,37  |

| 84h <sup>(2)</sup>    | FSR                   | Indirect Data | Indirect Data Memory Address Pointer                         |                         |                |                         |                       |                       |                       |                       | 29,37  |

| 85h                   | TRISA                 | TRISA7        | TRISA6                                                       | TRISA5                  | TRISA4         | TRISA3                  | TRISA2                | TRISA1                | TRISA0                | 1111 1111             | 51,37  |

| 86h                   | TRISB                 | TRISB7        | TRISB6                                                       | TRISB5                  | TRISB4         | TRISB3                  | TRISB2                | TRISB1                | TRISB0                | 1111 1111             | 60,37  |

| 87h                   | TRISC                 | TRISC7        | TRISC6                                                       | TRISC5                  | TRISC4         | TRISC3                  | TRISC2                | TRISC1                | TRISC0                | 1111 1111             | 70,37  |

| 88h <sup>(3)</sup>    | TRISD                 | TRISD7        | TRISD6                                                       | TRISD5                  | TRISD4         | TRISD3                  | TRISD2                | TRISD1                | TRISD0                | 1111 1111             | 78,37  |

| 89h                   | TRISE                 | _             | _                                                            | _                       | _              | TRISE3 <sup>(6)</sup>   | TRISE2 <sup>(3)</sup> | TRISE1 <sup>(3)</sup> | TRISE0 <sup>(3)</sup> | 1111                  | 81,37  |

| 8Ah <sup>(1, 2)</sup> | PCLATH                | _             | — — Write Buffer for the upper 5 bits of the Program Counter |                         |                |                         |                       |                       |                       |                       | 28,37  |

| 8Bh <sup>(2)</sup>    | INTCON                | GIE           | PEIE                                                         | TOIE                    | INTE           | RBIE                    | T0IF                  | INTF                  | RBIF                  | 0000 000x             | 44,37  |

| 8Ch                   | PIE1                  | TMR1GIE       | ADIE                                                         | RCIE                    | TXIE           | SSPIE                   | CCP1IE                | TMR2IE                | TMR1IE                | 0000 0000             | 45,37  |

| 8Dh                   | PIE2                  | _             | —                                                            | —                       | _              | —                       | _                     | _                     | CCP2IE                | 0                     | 46,37  |

| 8Eh                   | PCON                  | _             | _                                                            | _                       | _              | _                       | _                     | POR                   | BOR                   | qq                    | 27,38  |

| 8Fh                   | T1GCON                | TMR1GE        | T1GPOL                                                       | T1GTM                   | T1GSPM         | T <u>1GGO</u> /<br>DONE | T1GVAL                | T1GSS1                | T1GSS0                | 0000 0x00             | 118,38 |

| 90h                   | OSCCON                | _             | _                                                            | IRCF1                   | IRCF0          | ICSL                    | ICSS                  | _                     | _                     | 10 qq                 | 87,38  |

| 91h                   | OSCTUNE               | _             | _                                                            | TUN5                    | TUN4           | TUN3                    | TUN2                  | TUN1                  | TUN0                  | 00 0000               | 88,38  |

| 92h                   | PR2                   | Timer2 Perio  | od Register                                                  |                         |                |                         |                       |                       |                       | 1111 1111             | 120,38 |

| 93h                   | SSPADD <sup>(5)</sup> | Synchronou    | s Serial Port                                                | (I <sup>2</sup> C mode) | Address Regi   | ster                    |                       |                       |                       | 0000 0000             | 169,38 |

| 93h                   | SSPMSK <sup>(4)</sup> | Synchronou    | s Serial Port                                                | (I <sup>2</sup> C mode) | Address Mas    | k Register              |                       |                       |                       | 1111 1111             | 180,38 |

| 94h                   | SSPSTAT               | SMP           | CKE                                                          | D/A                     | Р              | S                       | R/W                   | UA                    | BF                    | 0000 0000             | 179,38 |

| 95h                   | WPUB                  | WPUB7         | WPUB6                                                        | WPUB5                   | WPUB4          | WPUB3                   | WPUB2                 | WPUB1                 | WPUB0                 | 1111 1111             | 61,38  |

| 96h                   | IOCB                  | IOCB7         | IOCB6                                                        | IOCB5                   | IOCB4          | IOCB3                   | IOCB2                 | IOCB1                 | IOCB0                 | 0000 0000             | 61,38  |

| 97h                   | —                     | Unimplemer    | nted                                                         |                         |                |                         |                       |                       |                       | _                     | —      |

| 98h                   | TXSTA                 | CSRC          | TX9                                                          | TXEN                    | SYNC           | _                       | BRGH                  | TRMT                  | TX9D                  | 0000 -010             | 147,38 |

| 99h                   | SPBRG                 | BRG7          | BRG6                                                         | BRG5                    | BRG4           | BRG3                    | BRG2                  | BRG1                  | BRG0                  | 0000 0000             | 149,38 |

| 9Ah                   | _                     | Unimplemer    | nted                                                         |                         |                |                         |                       |                       |                       | —                     | —      |

| 9Bh                   | _                     | Unimplemer    | nted                                                         |                         |                |                         |                       |                       |                       | —                     | —      |

| 9Ch                   | APFCON                | _             | —                                                            | —                       | _              | —                       | —                     | SSSEL                 | CCP2SEL               | 00                    | 50,38  |

| 9Dh                   | FVRCON                | FVRRDY        | FVREN                                                        | —                       | —              | —                       | —                     | ADFVR1                | ADFVR0                | q000                  | 104,38 |

| 9Eh                   | _                     | Unimplemer    | nted                                                         |                         |                |                         |                       |                       |                       | —                     | —      |

| 9Fh                   | ADCON1                | _             | ADCS2                                                        | ADCS1                   | ADCS0          | _                       | _                     | ADREF1                | ADREF0                | 000000                | 100,38 |

#### **TABLE 2-1:** PIC16(L)F722/3/4/6/7 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are 1: transferred to the upper byte of the program counter.

2:

These registers/bits are not implemented on PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'. 3:

Accessible only when SSPM<3:0>  $\pm$  1001. Accessible only when SSPM<3:0>  $\pm$  1001. This bit is always '1' as RE3 is input-only. 4:

5: 6:

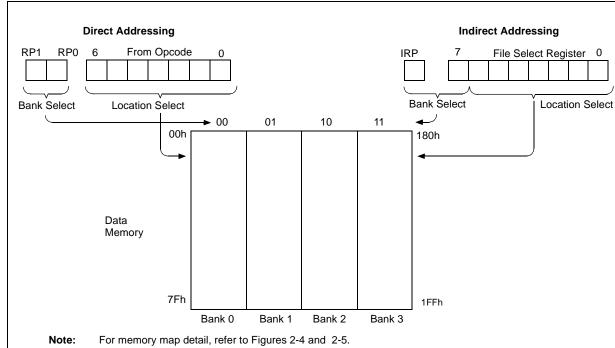

#### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit of the STATUS register, as shown in Figure 2-8.

A simple program to clear RAM location 020h-02Fh using indirect addressing is shown in Example 2-2.

#### EXAMPLE 2-2: INDIRECT ADDRESSING

|      | MOVLW<br>MOVWF<br>BANKISEL | 020h<br>FSR<br>020h | ;initialize pointer<br>;to RAM       |

|------|----------------------------|---------------------|--------------------------------------|

| NEXT | CLRF<br>INCF               | INDF<br>FSR         | ;clear INDF register<br>;inc pointer |

|      | BTFSS                      | FSR,4               | ;all done?                           |

|      | GOTO                       | NEXT                | ;no clear next                       |

| CONT | INUE                       |                     | ;yes continue                        |

|      |                            |                     |                                      |

#### FIGURE 2-8: DIRECT/INDIRECT ADDRESSING

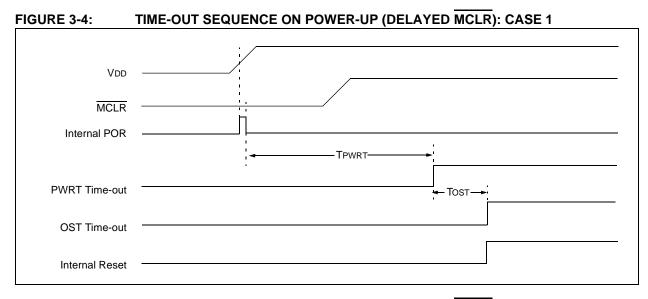

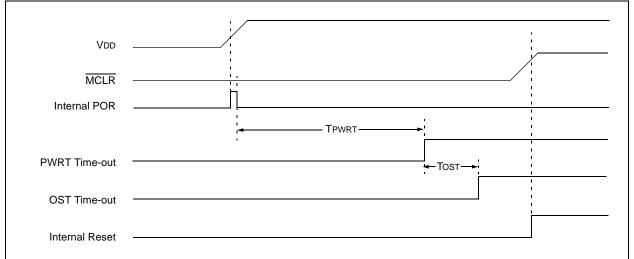

#### FIGURE 3-5: TIME-OUT SEQUENCE ON POWER-UP (DELAYED MCLR): CASE 2

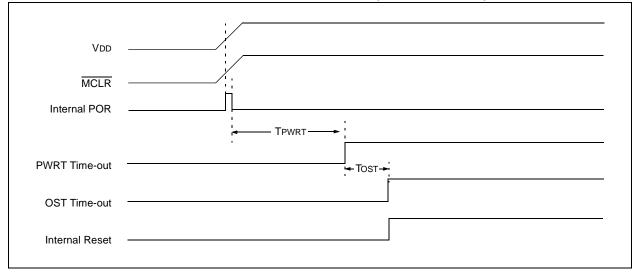

#### FIGURE 3-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR WITH VDD): CASE 3

| Name       | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3                   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------|--------|--------|--------|--------|-------------------------|---------|---------|---------|----------------------|---------------------------------|

| ADCON0     | —      | _      | CHS3   | CHS2   | CHS1                    | CHS0    | GO/DONE | ADON    | 00 0000              | 00 0000                         |

| ANSELB     | —      | _      | ANSB5  | ANSB4  | ANSB3                   | ANSB2   | ANSB1   | ANSB0   | 11 1111              | 11 1111                         |

| APFCON     | —      | _      | _      | —      | —                       | _       | SSSEL   | CCP2SEL | 00                   | 00                              |

| CCP2CON    | —      | _      | DC2B1  | DC2B0  | CCP2M3                  | CCP2M2  | CCP2M1  | CCP2M0  | 00 0000              | 00 0000                         |

| CPSCON0    | CPSON  | _      | _      | —      | CPSRNG1                 | CPSRNG0 | CPSOUT  | TOXCS   | 0 0000               | 0 0000                          |

| CPSCON1    | —      | _      | _      | —      | CPSCH3                  | CPSCH2  | CPSCH1  | CPSCH0  | 0000                 | 0000                            |

| INTCON     | GIE    | PEIE   | T0IE   | INTE   | RBIE                    | T0IF    | INTF    | RBIF    | 0000 000x            | 0000 000x                       |

| IOCB       | IOCB7  | IOCB6  | IOCB5  | IOCB4  | IOCB3                   | IOCB2   | IOCB1   | IOCB0   | 0000 0000            | 0000 0000                       |

| OPTION_REG | RBPU   | INTEDG | TOCS   | TOSE   | PSA                     | PS2     | PS1     | PS0     | 1111 1111            | 1111 1111                       |

| PORTB      | RB7    | RB6    | RB5    | RB4    | RB3                     | RB2     | RB1     | RB0     | XXXX XXXX            | XXXX XXXX                       |

| T1GCON     | TMR1GE | T1GPOL | T1GTM  | T1GSPM | T <u>1GGO</u> /<br>DONE | T1GVAL  | T1GSS1  | T1GSS0  | 0000 0x00            | uuuu uxuu                       |

| TRISB      | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3                  | TRISB2  | TRISB1  | TRISB0  | 1111 1111            | 1111 1111                       |

| WPUB       | WPUB7  | WPUB6  | WPUB5  | WPUB4  | WPUB3                   | WPUB2   | WPUB1   | WPUB0   | 1111 1111            | 1111 1111                       |

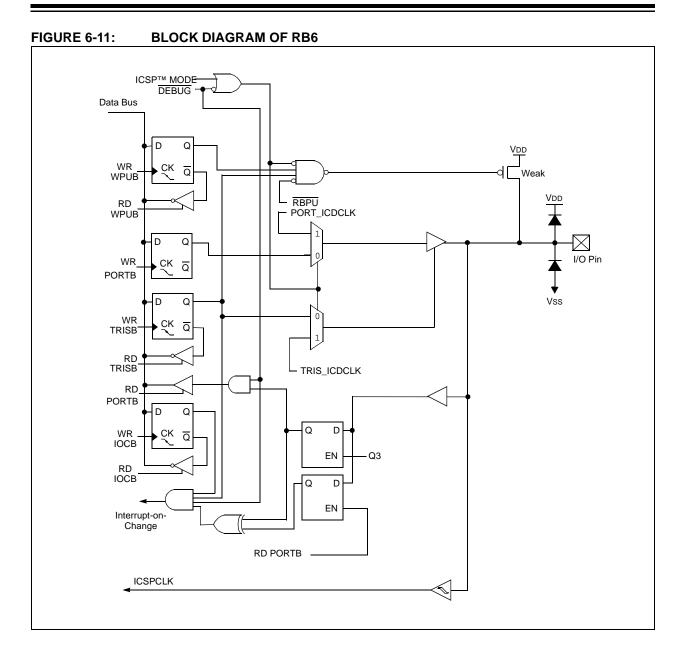

TABLE 6-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

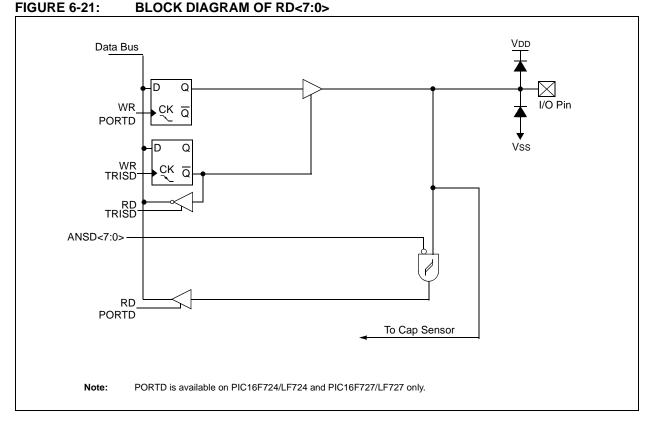

#### 6.5.6 RD4/CPS12

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### 6.5.7 RD5/CPS13

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- a capacitive sensing input

#### 6.5.8 RD6/CPS14

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### 6.5.9 RD7/CPS15

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

| TABLE 6-4: SUMM | IARY OF REGISTERS ASSOCIATED WITH PORTD <sup>(1)</sup> |

|-----------------|--------------------------------------------------------|

|-----------------|--------------------------------------------------------|

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|--------|--------|--------|---------|---------|--------|--------|----------------------|---------------------------------|

| ANSELD  | ANSD7  | ANSD6  | ANSD5  | ANSD4  | ANSD3   | ANSD2   | ANSD1  | ANSD0  | 1111 1111            | 1111 1111                       |

| CPSCON0 | CPSON  | —      | —      | —      | CPSRNG1 | CPSRNG0 | CPSOUT | TOXCS  | 0 0000               | 0 0000                          |

| CPSCON1 |        | —      | —      | _      | CPSCH3  | CPSCH2  | CPSCH1 | CPSCH0 | 0000                 | 0000                            |

| PORTD   | RD7    | RD6    | RD5    | RD4    | RD3     | RD2     | RD1    | RD0    | XXXX XXXX            | xxxx xxxx                       |

| TRISD   | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3  | TRISD2  | TRISD1 | TRISD0 | 1111 1111            | 1111 1111                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTD.**Note 1:**These registers are not implemented on the PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'.

#### © 2007-2015 Microchip Technology Inc.

#### DS40001341F-page 79

#### REGISTER 8-1: CONFIG1: CONFIGURATION WORD REGISTER 1 (CONTINUED)

- bit 4 **PWRTE:** Power-up Timer Enable bit 1 = PWRT disabled

- 1 = PWRT disabled0 = PWRT enabled

- bit 3 WDTE: Watchdog Timer Enable bit 1 = WDT enabled

- 1 = WDT enabled0 = WDT disabled

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = RC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, RC on RA7/OSC1/CLKIN

- 110 = RCIO oscillator: I/O function on RA6/OSC2/CLKOUT pin, RC on RA7/OSC1/CLKIN

- 101 = INTOSC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN

- 100 = INTOSCIO oscillator: I/O function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN

- 011 = EC: I/O function on RA6/OSC2/CLKOUT pin, CLKIN on RA7/OSC1/CLKIN

- 010 = HS oscillator: High-speed crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN

- 001 = XT oscillator: Crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN

- 000 = LP oscillator: Low-power crystal on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN

Note 1: Enabling Brown-out Reset does not automatically enable Power-up Timer.

- 2: The entire program memory will be erased when the code protection is turned off.

- 3: When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.

- 4: MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

#### REGISTER 8-2: CONFIG2: CONFIGURATION WORD REGISTER 2

|        |   |   | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> |

|--------|---|---|--------------------|--------------------|--------------------|--------------------|

|        | — | _ | _                  | —                  | —                  | —                  |

| bit 15 |   |   |                    |                    |                    | bit 8              |

| U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | R/P-1   | R/P-1   | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> |

|--------------------|--------------------|---------|---------|--------------------|--------------------|--------------------|--------------------|

| —                  | —                  | VCAPEN1 | VCAPEN0 | —                  | —                  | _                  | —                  |

| bit 7              |                    |         |         |                    |                    |                    | bit 0              |

| Legend:           | P = Programmable bit |                             |                    |

|-------------------|----------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared        | x = Bit is unknown |

bit 13-6 Unimplemented: Read as '1'

bit 5-4 VCAPEN<1:0>: Voltage Regulator Capacitor Enable bits For the PIC16LF72X: These bits are ignored. All VCAP pin functions are disabled. For the PIC16F72X: 00 = VCAP functionality is enabled on RA0 01 = VCAP functionality is enabled on RA5 10 = VCAP functionality is enabled on RA6 11 = All VCAP functions are disabled (not recommended) bit 3-0 Unimplemented: Read as '1'

**Note 1:** MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

### 12.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR1ON bit of the T1CON register

- TMR1IE bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

### 12.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- PEIE bit of the INTCON register must be set

- TISYNC bit of the T1CON register must be set

- TMR1CS bits of the T1CON register must be configured

- T1OSCEN bit of the T1CON register must be configured

- TMR1GIE bit of the T1GCON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine (0004h).

#### 12.9 CCP Capture/Compare Time Base

The CCP module uses the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Special Event Trigger.

For more information, see Section 15.0 "Capture/Compare/PWM (CCP) Module".

### 12.10 CCP Special Event Trigger

When the CCP is configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair becomes the period register for Timer1.

Timer1 should be synchronized to the Fosc/4 to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the CCP, the write will take precedence.

For more information, see Section 9.2.5 "Special Event Trigger".

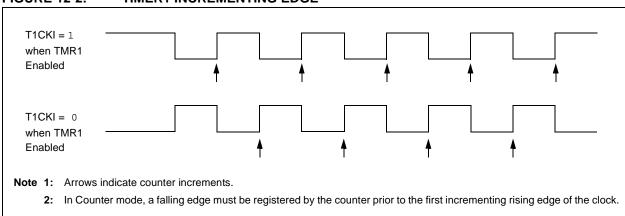

#### FIGURE 12-2: TIMER1 INCREMENTING EDGE

#### 14.5 Software Control

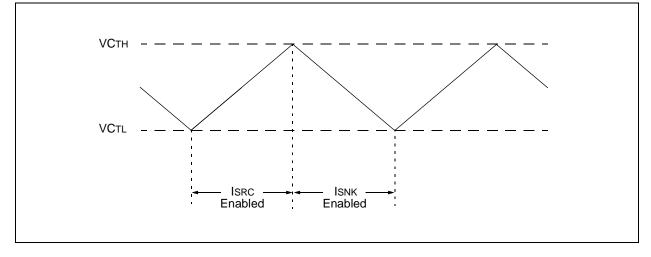

The software portion of the capacitive sensing module is required to determine the change in frequency of the capacitive sensing oscillator. This is accomplished by the following:

- Setting a fixed time base to acquire counts on Timer0 or Timer1

- Establishing the nominal frequency for the capacitive sensing oscillator

- Establishing the reduced frequency for the capacitive sensing oscillator due to an additional capacitive load

- Set the frequency threshold

#### 14.5.1 NOMINAL FREQUENCY (NO CAPACITIVE LOAD)

To determine the nominal frequency of the capacitive sensing oscillator:

- Remove any extra capacitive load on the selected CPSx pin

- At the start of the fixed time base, clear the timer resource

- At the end of the fixed time base save the value in the timer resource

The value of the timer resource is the number of oscillations of the capacitive sensing oscillator for the given time base. The frequency of the capacitive sensing oscillator is equal to the number of counts on in the timer divided by the period of the fixed time base.

#### 14.5.2 REDUCED FREQUENCY (ADDITIONAL CAPACITIVE LOAD)

The extra capacitive load will cause the frequency of the capacitive sensing oscillator to decrease. To determine the reduced frequency of the capacitive sensing oscillator:

- Add a typical capacitive load on the selected CPSx pin

- Use the same fixed-time base as the nominal frequency measurement

- At the start of the fixed-time base, clear the timer resource

- At the end of the fixed-time base save the value in the timer resource

The value of the timer resource is the number of oscillations of the capacitive sensing oscillator with an additional capacitive load. The frequency of the capacitive sensing oscillator is equal to the number of counts on in the timer divided by the period of the fixed time base. This frequency should be less than the value obtained during the nominal frequency measurement.

#### 14.5.3 FREQUENCY THRESHOLD

The frequency threshold should be placed midway between the value of nominal frequency and the reduced frequency of the capacitive sensing oscillator. Refer to Application Note AN1103, *Software Handling for Capacitive Sensing* (DS01103) for more detailed information the software required for capacitive sensing module.

| Note: | For           | more | inform  | ation | 0  | n general   |

|-------|---------------|------|---------|-------|----|-------------|

|       | Capa<br>Notes |      | Sensing | refer | to | Application |

- AN1101, Introduction to Capacitive Sensing (DS01101)

- AN1102, Layout and Physical Design Guidelines for Capacitive Sensing (DS01102).

#### REGISTER 14-2: CPSCON1: CAPACITIVE SENSING CONTROL REGISTER 1

| U-0          | U-0 | U-0            | U-0 | R/W-0 <sup>(2)</sup> | R/W-0            | R/W-0    | R/W-0  |

|--------------|-----|----------------|-----|----------------------|------------------|----------|--------|

| —            | —   | —              | _   | CPSCH3               | CPSCH2           | CPSCH1   | CPSCH0 |

| bit 7        |     |                |     |                      |                  |          | bit 0  |

| Legend:      |     |                |     |                      |                  |          |        |

|              |     |                |     |                      |                  |          |        |

| R = Readable | bit | W = Writable I | oit | U = Unimplen         | nented bit, read | l as '0' |        |

| bit 7-4 | Unimplemented: Read as '0'                         |  |  |  |

|---------|----------------------------------------------------|--|--|--|

| bit 3-0 | CPSCH<3:0>: Capacitive Sensing Channel Select bits |  |  |  |

|         | If CPSON = 0:                                      |  |  |  |

|         | These bits are ignored. No channel is selected.    |  |  |  |

|         | <u>If CPSON = 1</u> :                              |  |  |  |

|         | 0000 = channel 0, (CPS0)                           |  |  |  |

|         | 0001 = channel 1, (CPS1)                           |  |  |  |

|         | 0010 = channel 2, (CPS2)                           |  |  |  |

|         | 0011 = channel 3, (CPS3)                           |  |  |  |

|         | 0100 = channel 4, (CPS4)                           |  |  |  |

|         | 0101 = channel 5, (CPS5)                           |  |  |  |

|         | 0110 = channel 6, (CPS6)                           |  |  |  |

|         | 0111 =  channel 7, (CPS7)                          |  |  |  |

|         | 1000 = channel 8, (CPS8 <sup>(1)</sup> )           |  |  |  |

|         | 1001 = channel 9, (CPS9 <sup>(1)</sup> )           |  |  |  |

|         | 1010 = channel 10, (CPS10 <sup>(1)</sup> )         |  |  |  |

|         | 1011 = channel 11, (CPS11 <sup>(1)</sup> )         |  |  |  |

|         | 1100 =  channel 12, (CPS12(1))                     |  |  |  |

|         | $1101 = \text{ channel } 13, (CPS13^{(1)})$        |  |  |  |

|         | 1110 = channel 14, (CPS14(1))                      |  |  |  |

|         | 1111 = channel 15, (CPS15 <sup>(1)</sup> )         |  |  |  |

**Note 1:** These channels are not implemented on the PIC16F722/723/726/PIC16LF722/723/726.

2: This bit is not implemented on PIC16F722/723/726/PIC16LF722/723/726, Read as '0'

| TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH CAPACITIVE SENSIN | G |

|--------------------------------------------------------------------|---|

|--------------------------------------------------------------------|---|

| Name       | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|---------|---------|---------|---------|---------|--------|---------|---------|----------------------|---------------------------------|

| ANSELA     | _       | _       | ANSA5   | ANSA4   | ANSA3   | ANSA2  | ANSA1   | ANSA0   | 11 1111              | 11 1111                         |

| ANSELB     | _       | _       | ANSB5   | ANSB4   | ANSB3   | ANSB2  | ANSB1   | ANSB0   | 11 1111              | 11 1111                         |

| ANSELD     | ANSD7   | ANSD6   | ANSD5   | ANSD4   | ANSD3   | ANSD2  | ANSD1   | ANSD0   | 1111 1111            | 1111 1111                       |

| OPTION_REG | RBPU    | INTEDG  | TOCS    | T0SE    | PSA     | PS2    | PS1     | PS0     | 1111 1111            | 1111 1111                       |

| PIE1       | TMR1GIE | ADIE    | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIR1       | TMR1GIF | ADIF    | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| T1CON      | TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | _       | TMR10N  | 0000 00-0            | 0000 00-0                       |

| T2CON      |         | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

| TRISA      | TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2 | TRISA1  | TRISA0  | 1111 1111            | 1111 1111                       |

| TRISB      | TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2 | TRISB1  | TRISB0  | 1111 1111            | 1111 1111                       |

| TRISD      | TRISD7  | TRISD6  | TRISD5  | TRISD4  | TRISD3  | TRISD2 | TRISD1  | TRISD0  | 1111 1111            | 1111 1111                       |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the capacitive sensing module.

| U-0                                                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0            | R/W-0 | R/W-0                           | R/W-0           | R/W-0           | R/W-0  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|---------------------------------|-----------------|-----------------|--------|

| _                                                                                                                                                                                                                            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DCxB1            | DCxB0 | CCPxM3                          | CCPxM2          | CCPxM1          | CCPxM0 |

| bit 7                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |       |                                 |                 |                 | bit 0  |

|                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |       |                                 |                 |                 |        |

| Legend:                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |       |                                 |                 |                 |        |

| R = Readable bit                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | W = Writable bit |       | U = Unimpler                    | nented bit, rea | d as '0'        |        |

| -n = Value at F                                                                                                                                                                                                              | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | '1' = Bit is set |       | '0' = Bit is cle                | ared            | x = Bit is unkr | nown   |

|                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |       |                                 |                 |                 |        |

| bit 7-6                                                                                                                                                                                                                      | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ted: Read as '   | 0'    |                                 |                 |                 |        |

| bit 5-4 DCxB<1:0>: PWM Duty Cycle Least Significant bits<br>Capture mode:<br>Unused<br>Compare mode:<br>Unused<br><u>PWM mode:</u><br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  | RxL.  |                                 |                 |                 |        |

| bit 3-0                                                                                                                                                                                                                      | <pre>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.<br/>CCPxM&lt;3:0&gt;: CCP Mode Select bits<br/>0000 = Capture/Compare/PWM off (resets CCP module)<br/>0011 = Unused (reserved)<br/>0010 = Compare mode, toggle output on match (CCPxIF bit of the PIRx register is set)<br/>0011 = Unused (reserved)<br/>0100 = Capture mode, every falling edge<br/>0101 = Capture mode, every falling edge<br/>0110 = Capture mode, every fising edge<br/>0111 = Capture mode, every 16th rising edge<br/>0111 = Capture mode, every 16th rising edge<br/>1000 = Compare mode, clear output on match (CCPxIF bit of the PIRx register is set)<br/>1001 = Compare mode, clear output on match (CCPxIF bit of the PIRx register is set)<br/>1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set of the PIRx register<br/>CCPx pin is unaffected)<br/>1011 = Compare mode, trigger special event (CCPxIF bit of the PIRx register is set, TMR1 is rese<br/>and A/D conversion<sup>(1)</sup> is started if the ADC module is enabled. CCPx pin is unaffected.)<br/>11xx = PWM mode.</pre> |                  |       | PIRx register,<br>TMR1 is reset |                 |                 |        |

### REGISTER 15-1: CCPxCON: CCPx CONTROL REGISTER

#### 17.2.7 CLOCK STRETCHING

During any SCL low phase, any device on the  $I^2C$  bus may hold the SCL line low and delay, or pause, the transmission of data. This "stretching" of a transmission allows devices to slow down communication on the bus. The SCL line must be constantly sampled by the master to ensure that all devices on the bus have released SCL for more data.

Stretching usually occurs after an ACK bit of a transmission, delaying the first bit of the next byte. The SSP module hardware automatically stretches for two conditions:

- After a 10-bit address byte is received (update SSPADD register)

- Anytime the CKP bit of the SSPCON register is cleared by hardware

The module will hold SCL low until the CKP bit is set. This allows the user slave software to update SSPBUF with data that may not be readily available. In 10-bit addressing modes, the SSPADD register must be updated after receiving the first and second address bytes. The SSP module will hold the SCL line low until the SSPADD has a byte written to it. The UA bit of the SSPSTAT register will be set, along with SSPIF, indicating an address update is needed.

#### 17.2.8 FIRMWARE MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits of the SSPSTAT register are cleared from a Reset or when the SSP module is disabled (SSPEN cleared). The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set or the bus is Idle and both the S and P bits are clear.

In Firmware Master mode, the SCL and SDA lines are manipulated by setting/clearing the corresponding TRIS bit(s). The output level is always low, irrespective of the value(s) in the corresponding PORT register bit(s). When transmitting a '1', the TRIS bit must be set (input) and a '0', the TRIS bit must be clear (output).

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt will occur if enabled):

- Start condition

- Stop condition

- Data transfer byte transmitted/received

Firmware Master Mode of operation can be done with either the Slave mode Idle (SSPM<3:0 > = 1011), or with either of the Slave modes in which interrupts are enabled. When both master and slave functionality is enabled, the software needs to differentiate the source(s) of the interrupt. Refer to Application Note AN554, Software Implementation of  $l^2 C^{TM}$  Bus Master (DS00554) for more information.

#### 17.2.9 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allow the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSPSTAT register is set or when the bus is Idle, and both the S and P bits are clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the Stop condition occurs.

In Multi-Master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRIS bits). There are two stages where this arbitration of the bus can be lost. They are the Address Transfer and Data Transfer stages.

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an  $\overrightarrow{ACK}$  pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

Refer to Application Note AN578, Use of the SSP Module in the  $l^2 C^{TM}$  Multi-Master Environment (DS00578) for more information.

| ADDLW            | Add literal and W                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDLW k                                                                                                        |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | $(W) + k \to (W)$                                                                                                      |

| Status Affected: | C, DC, Z                                                                                                               |

| Description:     | The contents of the W register<br>are added to the 8-bit literal 'k'<br>and the result is placed in the<br>W register. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ADDWF            | Add W and f                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |

| Status Affected: | C, DC, Z                                                                                                                                                                           |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND literal with W                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                             |

| Operands:        | $0 \leq k \leq 255$                                                                                                  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                      |

| Status Affected: | Z                                                                                                                    |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'.<br>The result is placed in the W reg-<br>ister. |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the<br>next instruction is discarded, and<br>a NOP is executed instead, making<br>this a 2-cycle instruction. |

| ANDWF            | AND W with f                                                                                                                                                    |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                               |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |  |  |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |  |  |  |  |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                                      |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                |  |  |  |  |  |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                            |  |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>2-cycle instruction. |  |  |  |  |  |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                                |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] CLRWDT                                                                                                                                                                      |  |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                |  |  |  |  |  |  |  |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT} \\ 0 \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}} \\ 1 \rightarrow \overline{\text{PD}} \end{array}$ |  |  |  |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                              |  |  |  |  |  |  |  |

| Description:     | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT.<br>Status bits TO and PD are set.                                                      |  |  |  |  |  |  |  |

| CALL             | Call Subroutine                                                                                                                                                                                                                         |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                 |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                    |  |  |  |  |  |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC < 10:0>, \\ (PCLATH < 4:3>) \rightarrow PC < 12:11> \end{array}$                                                                                                          |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                    |  |  |  |  |  |

| Description:     | Call Subroutine. First, return<br>address (PC + 1) is pushed onto<br>the stack. The 11-bit immediate<br>address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a 2-cycle instruction. |  |  |  |  |  |

| COMF             | Complement f                                                                                                                                                   |  |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ label ] COMF f,d                                                                                                                                             |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                |  |  |  |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                     |  |  |  |  |  |  |  |