Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 36                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 192 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                             |

| Data Converters            | A/D 14x8b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f724-i-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to the **Section 19.0** "**Power-Down Mode (Sleep)**" for more details.

#### 4.4 INT Pin

The external interrupt, INT pin, causes an asynchronous, edge-triggered interrupt. The INTEDG bit of the OPTION register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector. This interrupt is disabled by clearing the INTE bit of the INTCON register.

### 4.5 Context Saving

When an interrupt occurs, only the return PC value is saved to the stack. If the ISR modifies or uses an instruction that modifies key registers, their values must be saved at the beginning of the ISR and restored when the ISR completes. This prevents instructions following the ISR from using invalid data. Examples of key registers include the W, STATUS, FSR and PCLATH registers.

The code shown in Example 4-1 can be used to do the following.

- Save the W register

- Save the STATUS register

- Save the PCLATH register

- Execute the ISR program

- Restore the PCLATH register

- Restore the STATUS register

- Restore the W register

Since most instructions modify the W register, it must be saved immediately upon entering the ISR. The SWAPF instruction is used when saving and restoring the W and STATUS registers because it will not affect any bits in the STATUS register. It is useful to place  $W_{TEMP}$  in shared memory because the ISR cannot predict which bank will be selected when the interrupt occurs.

The processor will branch to the interrupt vector by loading the PC with 0004h. The PCLATH register will remain unchanged. This requires the ISR to ensure that the PCLATH register is set properly before using an instruction that causes PCLATH to be loaded into the PC. See **Section 2.3 "PCL and PCLATH"** for details on PC operation.

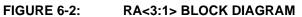

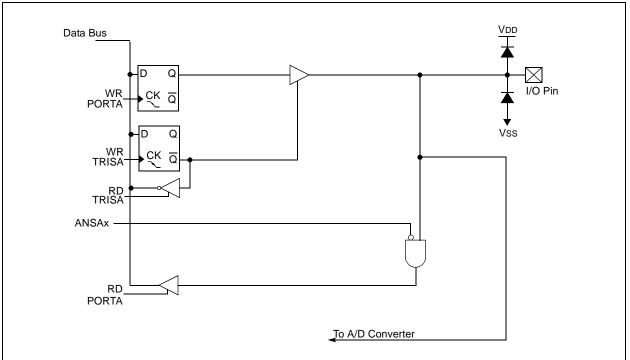

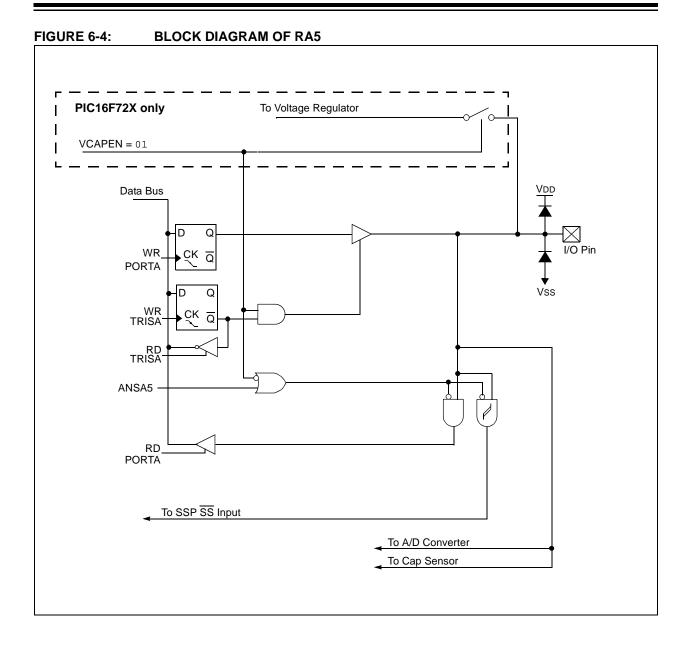

#### 6.2.1 ANSELA REGISTER

The ANSELA register (Register 6-4) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

### REGISTER 6-4: ANSELA: PORTA ANALOG SELECT REGISTER

| U-0                                | U-0 | R/W-1                                   | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|------------------------------------|-----|-----------------------------------------|-------|-------|-------|-------|-------|

| —                                  | —   | ANSA5                                   | ANSA4 | ANSA3 | ANSA2 | ANSA1 | ANSA0 |

| bit 7                              |     |                                         |       |       |       |       | bit 0 |

|                                    |     |                                         |       |       |       |       |       |

| Legend:                            |     |                                         |       |       |       |       |       |

| R = Readable bit W = Writable bit  |     | U = Unimplemented bit, read as '0'      |       |       |       |       |       |

| -n = Value at POR '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |       |       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **ANSA<5:0>**: Analog Select between Analog or Digital Function on pins RA<5:0>, respectively 0 = Digital I/O. Pin is assigned to port or Digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital Input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

# PIC16(L)F722/3/4/6/7

# PIC16(L)F722/3/4/6/7

#### TABLE 6-1: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name                   | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|--------|---------|---------|---------|---------|---------|---------|----------------------|---------------------------------|

| ADCON0                 | _      | _      | CHS3    | CHS2    | CHS1    | CHS0    | GO/DONE | ADON    | 0000 0000            | 0000 0000                       |

| ADCON1                 | _      | ADCS2  | ADCS1   | ADCS0   | _       | _       | ADREF1  | ADREF0  | -00000               | -00000                          |

| ANSELA                 | _      | _      | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   | 11 1111              | 11 1111                         |

| APFCON                 | _      | _      | _       | _       | _       | _       | SSSEL   | CCP2SEL | 00                   | 00                              |

| CPSCON0                | CPSON  | _      | _       | _       | CPSRNG1 | CPSRNG0 | CPSOUT  | TOXCS   | 0 0000               | 0 0000                          |

| CPSCON1                | _      | _      | _       | _       | CPSCH3  | CPSCH2  | CPSCH1  | CPSCH0  | 0000                 | 0000                            |

| CONFIG2 <sup>(1)</sup> | _      | _      | VCAPEN1 | VCAPEN0 | _       | _       | _       | _       | —                    | —                               |

| OPTION_REG             | RBPU   | INTEDG | TOCS    | T0SE    | PSA     | PS2     | PS1     | PS0     | 1111 1111            | 1111 1111                       |

| PORTA                  | RA7    | RA6    | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | xxxx xxxx            | xxxx xxxx                       |

| SSPCON                 | WCOL   | SSPOV  | SSPEN   | CKP     | SSPM3   | SSPM2   | SSPM1   | SSPM0   | 0000 0000            | 0000 0000                       |

| TRISA                  | TRISA7 | TRISA6 | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 1111 1111            | 1111 1111                       |

$\label{eq:Legend: x = unknown, u = unchanged, - = unimplemented locations read as `0'. Shaded cells are not used by PORTA.$

Note 1: PIC16F72X only.

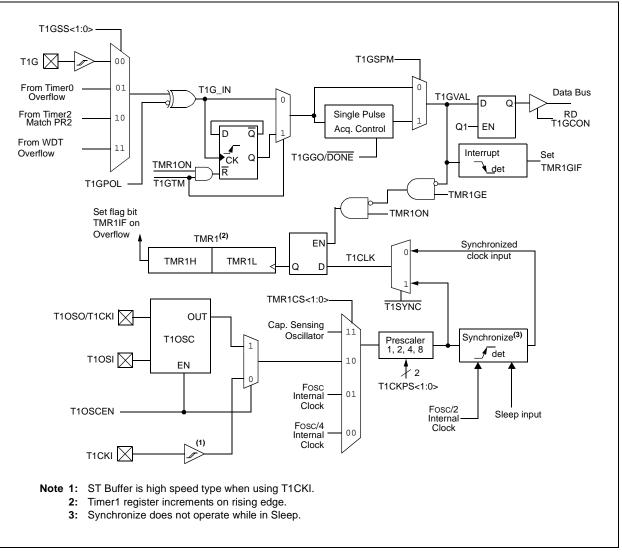

# 12.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- 3-bit prescaler

- Dedicated LP oscillator circuit

- Synchronous or asynchronous operation

- Multiple Timer1 gate (count enable) sources

- Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Time base for the Capture/Compare function

- Special Event Trigger (with CCP)

- Gate Single-pulse mode

- Gate Value StatusGate Event Interrupt

· Gate Toggle mode

Selectable Gate Source Polarity

Figure 12-1 is a block diagram of the Timer1 module.

#### FIGURE 12-1: TIMER1 BLOCK DIAGRAM

#### TABLE 12-5: WDT/TIMER1 GATE INTERACTION

| WDTE | TMR1GE = 1<br>and<br>T1GSS = 11 | WDT Oscillator<br>Enable | WDT Reset | Wake-up | WDT Available for<br>T1G Source |

|------|---------------------------------|--------------------------|-----------|---------|---------------------------------|

| 1    | N                               | Y                        | Y         | Y       | N                               |

| 1    | Y                               | Y                        | Y         | Y       | Y                               |

| 0    | Y                               | Y                        | N         | N       | Y                               |

| 0    | Ν                               | N                        | N         | N       | N                               |

#### 12.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 Gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 12-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

**Note:** Enabling Toggle mode at the same time as changing the gate polarity may result in indeterminate operation.

# 12.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software.

Clearing the T1GSPM <u>bit of the T1GCON</u> register will also clear the T1GGO/DONE bit. See Figure 12-5 for timing details.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 Gate source to be measured. See Figure 12-6 for timing details.

#### 12.6.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 Gate is not enabled (TMR1GE bit is cleared).

#### 12.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 Gate is not enabled (TMR1GE bit is cleared).

# 14.6 Operation during Sleep

The capacitive sensing oscillator will continue to run as long as the module is enabled, independent of the part being in Sleep. In order for the software to determine if a frequency change has occurred, the part must be awake. However, the part does not have to be awake when the timer resource is acquiring counts. One way to acquire the Timer1 counts while in Sleep is to have Timer1 gated with the overflow of the Watchdog Timer. This can be accomplished using the following steps:

- 1. Configure the Watchdog Time-out overflow as the Timer1's gate source T1GSS<1:0> = 11.

- 2. Set Timer1 Gate to toggle mode by setting the T1GTM bit of the T1GCON register.

- 3. Set the TMR1GE bit of the T1GCON register.

- 4. Set TMR1ON bit of the T1CON register.

- 5. Enable capacitive sensing module with the appropriate current settings and pin selection.

- 6. Clear Timer1.

- 7. Put the part to Sleep.

- 8. On the first WDT overflow, the capacitive sensing oscillator will begin to increment Timer1. Then put the part to Sleep.

- 9. On the second WDT overflow Timer1 will stop incrementing. Then run the software routine to determine if a frequency change has occurred.

Refer to Section 12.0 "Timer1 Module with Gate Control" for additional information.

- Note 1: When using the WDT to set the interval on Timer1, any other source that wakes the part up early will cause the WDT overflow to be delayed, affecting the value captured by Timer1.

- 2: Timer0 does not operate when in Sleep, and therefore cannot be used for capacitive sense measurements in Sleep.

#### 16.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (refer to Section 16.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Enable reception by setting the CREN bit.

- 6. The RCIF interrupt flag bit of the PIR1 register will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE bit of the PIE1 register was also set.

- 7. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 8. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 9. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 16.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (refer to Section 16.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. Enable 9-bit reception by setting the RX9 bit.

- 5. Enable address detection by setting the ADDEN bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit of the PIR1 register will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit of the PIE1 register was also set.

- 8. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

| RX/DT pin                          | Start<br>bit / bit 0 / bit 1 / ( / ybit 7/8/ Stop / bit / bit 0 / ( / ybit 7/8/ Stop / bit / / / ybit 7/8/ Stop                                           |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rcv Shift<br>Reg<br>Rcv Buffer Reg | → → → → → → → → → → → → → → → → → → →                                                                                                                     |

| Read Rcv<br>Buffer Reg –<br>RCREG  |                                                                                                                                                           |

| RCIF<br>(Interrupt Flag)           |                                                                                                                                                           |

| OERR bit _<br>CREN _               |                                                                                                                                                           |

|                                    | timing diagram shows three words appearing on the RX input. The RCREG (receive buffer) is read after the third word, ng the OERR (overrun) bit to be set. |

### FIGURE 16-5: ASYNCHRONOUS RECEPTION

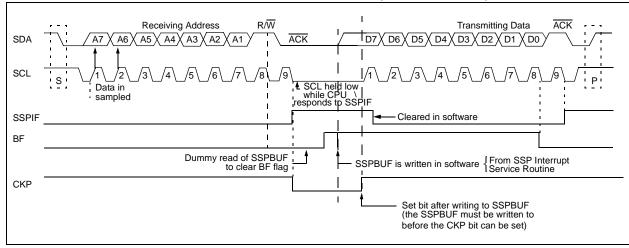

### 17.2.6 TRANSMISSION

When the R/W bit of the received address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set and the slave will respond to the master by reading out data. After the address match, an ACK pulse is generated by the slave hardware and the SCL pin is held low (clock is automatically stretched) until the slave is ready to respond. See **Section 17.2.7 "Clock Stretching"**. The data the slave will transmit must be loaded into the SSPBUF register, which sets the BF bit. The SCL line is released by setting the CKP bit of the SSPCON register.

An SSP interrupt is generated for each transferred data byte. The SSPIF flag bit of the PIR1 register initiates an SSP interrupt, and must be cleared by software before the next byte is transmitted. The BF bit of the SSPSTAT register is cleared on the falling edge of the eighth received clock pulse. The SSPIF flag bit is set on the falling edge of the ninth clock pulse. Following the eighth falling clock edge, control of the SDA line is released back to the master so that the master can acknowledge or not acknowledge the response. If the master sends a not acknowledge, the slave's transmission is complete and the slave must monitor for the next Start condition. If the master acknowledges, control of the bus is returned to the slave to transmit another byte of data. Just as with the previous byte, the clock is stretched by the slave, data must be loaded into the SSPBUF and CKP must be set to release the clock line (SCL).

#### FIGURE 17-12: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

# REGISTER 17-4: SSPSTAT: SYNCHRONOUS SERIAL PORT STATUS REGISTER (I<sup>2</sup>C MODE)

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                      | R-0                                                                                                 | R-0                        | R-0                                                              | R-0                             | R-0                     | R-0   |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------|---------------------------------|-------------------------|-------|

| SMP             | CKE                                                                                                                                                                                                                                                                        | D/A                                                                                                 | Р                          | S                                                                | R/W                             | UA                      | BF    |

| bit 7           |                                                                                                                                                                                                                                                                            |                                                                                                     |                            |                                                                  |                                 |                         | bit 0 |

|                 |                                                                                                                                                                                                                                                                            |                                                                                                     |                            |                                                                  |                                 |                         |       |

| Legend:         |                                                                                                                                                                                                                                                                            |                                                                                                     |                            |                                                                  |                                 | (0)                     |       |

| R = Readable    |                                                                                                                                                                                                                                                                            | W = Writable bi                                                                                     | t                          |                                                                  | ented bit, read                 |                         |       |

| -n = Value at F | POR                                                                                                                                                                                                                                                                        | '1' = Bit is set                                                                                    |                            | '0' = Bit is clea                                                | ired                            | x = Bit is unkno        | own   |

| bit 7           | 1 = Slew Rate                                                                                                                                                                                                                                                              | Input Sample Pl<br>Control (limiting)<br>Control (limiting)                                         | disabled. Oper             | ating in I <sup>2</sup> C Star<br>ating in I <sup>2</sup> C Fast | dard Mode (100<br>Mode (400 kHz | ) kHz and 1 MHz).<br>). |       |

| bit 6           |                                                                                                                                                                                                                                                                            | <b>CKE</b> : SPI Clock Edge Select bit<br>This bit must be maintained clear. Used in SPI mode only. |                            |                                                                  |                                 |                         |       |

| bit 5           | <b>D/A</b> : DATA/ADDRESS bit (I <sup>2</sup> C mode only)<br>1 = Indicates that the last byte received or transmitted was data<br>0 = Indicates that the last byte received or transmitted was address                                                                    |                                                                                                     |                            |                                                                  |                                 |                         |       |

| bit 4           | <ul> <li>P: Stop bit</li> <li>This bit is cleared when the SSP module is disabled, or when the Start bit is detected last.</li> <li>1 = Indicates that a Stop bit has been detected last (this bit is '0' on Reset)</li> <li>0 = Stop bit was not detected last</li> </ul> |                                                                                                     |                            |                                                                  |                                 |                         |       |

| bit 3           | <ul> <li>Start bit</li> <li>This bit is cleared when the SSP module is disabled, or when the Stop bit is detected last.</li> <li>1 = Indicates that a Start bit has been detected last (this bit is '0' on Reset)</li> <li>0 = Start bit was not detected last</li> </ul>  |                                                                                                     |                            |                                                                  |                                 |                         |       |

| bit 2           | <b>R/W</b> : READ/WRITE bit Information<br>This bit holds the R/W bit information following the last address match. This bit is only valid from the address ma<br>to the next Start bit, Stop bit or ACK bit.<br>1 = Read<br>0 = Write                                     |                                                                                                     |                            |                                                                  |                                 | address match           |       |

| bit 1           | <b>UA</b> : Update Address bit (10-bit I <sup>2</sup> C mode only)<br>1 = Indicates that the user needs to update the address in the SSPADD register<br>0 = Address does not need to be updated                                                                            |                                                                                                     |                            |                                                                  |                                 |                         |       |

| bit 0           | 0 = Receive no<br><u>Transmit:</u><br>1 = Transmit in                                                                                                                                                                                                                      | Status bit<br>mplete, SSPBUF<br>t complete, SSP<br>progress, SSPB<br>mplete, SSPBU                  | BUF is empty<br>UF is full |                                                                  |                                 |                         |       |

# PIC16(L)F722/3/4/6/7

| ADDLW            | Add literal and W                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDLW k                                                                                                        |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | $(W) + k \to (W)$                                                                                                      |

| Status Affected: | C, DC, Z                                                                                                               |

| Description:     | The contents of the W register<br>are added to the 8-bit literal 'k'<br>and the result is placed in the<br>W register. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ADDWF            | Add W and f                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |

| Status Affected: | C, DC, Z                                                                                                                                                                           |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND literal with W                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                             |

| Operands:        | $0 \leq k \leq 255$                                                                                                  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                      |

| Status Affected: | Z                                                                                                                    |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'.<br>The result is placed in the W reg-<br>ister. |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the<br>next instruction is discarded, and<br>a NOP is executed instead, making<br>this a 2-cycle instruction. |

| ANDWF            | AND W with f                                                                                                                                                    |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                               |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |  |

### 22.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 22.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 22.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 22.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

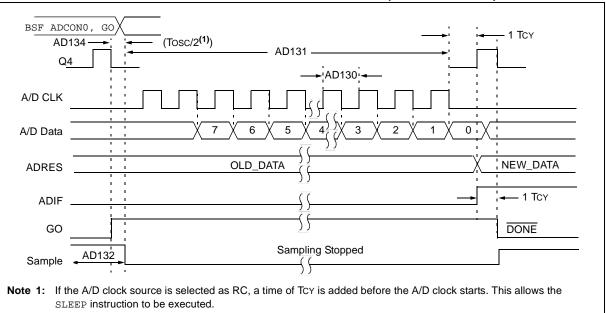

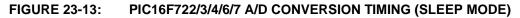

Note 1: If the A/D clock source is selected as RC, a time of TcY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.

| Param.<br>No.                       | Symbol                    | Characteristic         |              | Min.       | Max. | Units                                       | Conditions                                  |  |

|-------------------------------------|---------------------------|------------------------|--------------|------------|------|---------------------------------------------|---------------------------------------------|--|

| SP100*                              | Тнідн                     | Clock high time        | 100 kHz mode | 4.0        | —    | μs                                          | Device must operate at a minimum of 1.5 MHz |  |

|                                     |                           |                        | 400 kHz mode | 0.6        | _    | μs                                          | Device must operate at a minimum of 10 MHz  |  |

|                                     |                           |                        | SSP Module   | 1.5Tcy     | _    |                                             |                                             |  |

| SP101*                              | P101* TLOW Clock low time | 100 kHz mode           | 4.7          | _          | μs   | Device must operate at a minimum of 1.5 MHz |                                             |  |

|                                     |                           | 400 kHz mode           | 1.3          | _          | μS   | Device must operate at a minimum of 10 MHz  |                                             |  |

|                                     |                           | SSP Module             | 1.5Tcy       | _          |      |                                             |                                             |  |

| SP102*                              | P102* TR SDA and SCL rise | 100 kHz mode           | —            | 1000       | ns   |                                             |                                             |  |

| time                                | time                      | 400 kHz mode           | 20 + 0.1CB   | 300        | ns   | CB is specified to be from 10-400 pF        |                                             |  |

| SP103*                              | TF                        | SDA and SCL fall time  | 100 kHz mode | —          | 250  | ns                                          |                                             |  |

|                                     |                           |                        | 400 kHz mode | 20 + 0.1CB | 250  | ns                                          | CB is specified to be from 10-400 pF        |  |

| SP106*                              | THD:DAT                   | Data input hold time   | 100 kHz mode | 0          |      | ns                                          |                                             |  |

|                                     |                           | 400 kHz mode           | 0            | 0.9        | μs   | -                                           |                                             |  |

| SP107* TSU:DAT D                    | Data input setup time     | 100 kHz mode           | 250          |            | ns   | (Note 2)                                    |                                             |  |

|                                     |                           | 400 kHz mode           | 100          |            | ns   | -                                           |                                             |  |

| SP109* TAA Output valid fr<br>clock | Output valid from         | 100 kHz mode           | —            | 3500       | ns   | (Note 1)                                    |                                             |  |

|                                     | clock                     | 400 kHz mode           | _            |            | ns   |                                             |                                             |  |

| SP110* TBUF Bu                      | Bus free time             | 100 kHz mode           | 4.7          | _          | μs   | Time the bus must be free                   |                                             |  |

|                                     |                           | 400 kHz mode           | 1.3          | —          | μs   | before a new transmission can start         |                                             |  |

| SP111                               | Св                        | Bus capacitive loading |              | —          | 400  | pF                                          |                                             |  |

# TABLE 23-13: I<sup>2</sup>C BUS DATA REQUIREMENTS

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement TsU:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

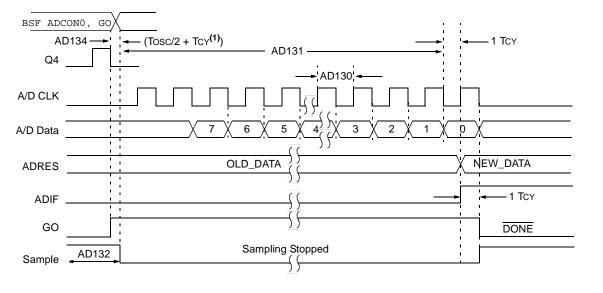

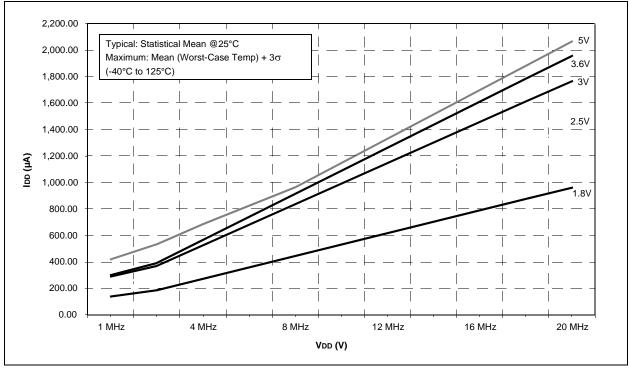

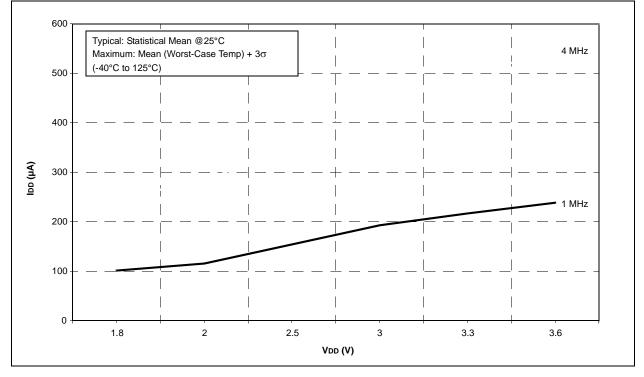

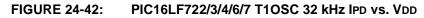

# 24.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

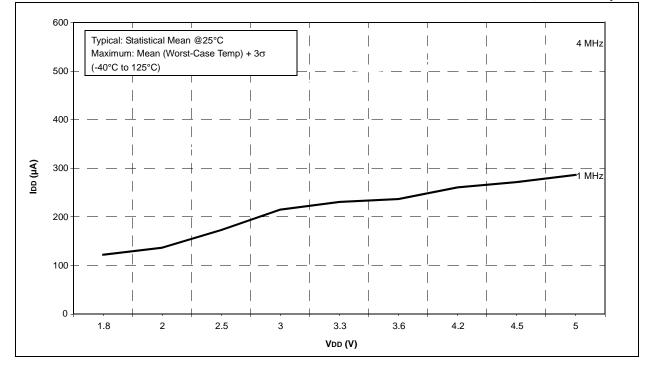

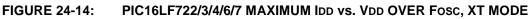

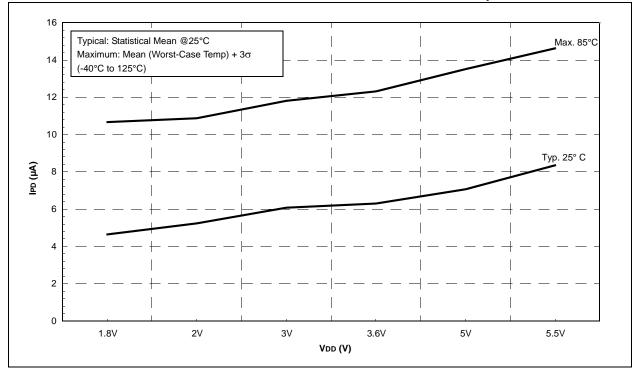

#### FIGURE 24-13: PIC16F722/3/4/6/7 MAXIMUM IDD vs. VDD OVER Fosc, XT MODE, VCAP = 0.1 µF

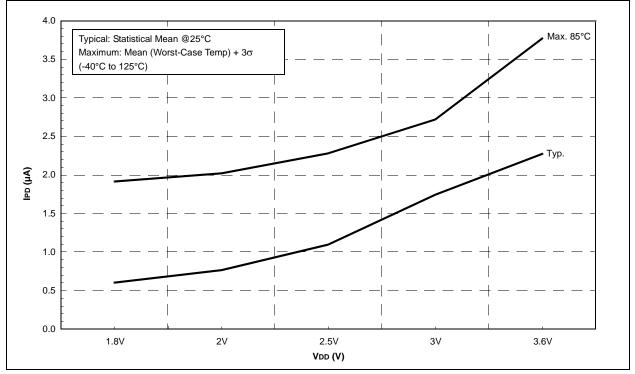

#### 25.2 Package Details

The following sections give the technical details of the packages.

## 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | INCHES           |          |       |       |

|----------------------------|------------------|----------|-------|-------|

|                            | Dimension Limits |          | NOM   | MAX   |

| Number of Pins             | N                | 28       |       |       |

| Pitch                      | е                | .100 BSC |       |       |

| Top to Seating Plane       | А                | 200      |       |       |

| Molded Package Thickness   | A2               | .120     | .135  | .150  |

| Base to Seating Plane      | A1               | .015     | -     | -     |

| Shoulder to Shoulder Width | E                | .290     | .310  | .335  |

| Molded Package Width       | E1               | .240     | .285  | .295  |

| Overall Length             | D                | 1.345    | 1.365 | 1.400 |

| Tip to Seating Plane       | L                | .110     | .130  | .150  |

| Lead Thickness             | С                | .008     | .010  | .015  |

| Upper Lead Width           | b1               | .040     | .050  | .070  |

| Lower Lead Width           | b                | .014     | .018  | .022  |

| Overall Row Spacing §      | eB               | -        | -     | .430  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

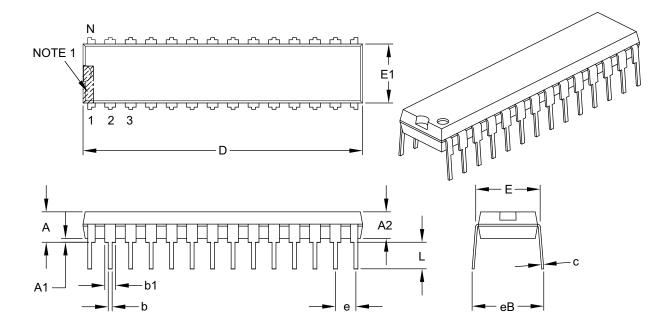

# 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |          |      |      |

|----------------------------|-------------|----------|------|------|

| Dimension Limits           |             | MIN      | NOM  | MAX  |

| Contact Pitch              | E           | 0.65 BSC |      |      |

| Optional Center Pad Width  | W2          |          |      | 6.80 |

| Optional Center Pad Length | T2          |          |      | 6.80 |

| Contact Pad Spacing        | C1          |          | 8.00 |      |

| Contact Pad Spacing        | C2          |          | 8.00 |      |

| Contact Pad Width (X44)    | X1          |          |      | 0.35 |

| Contact Pad Length (X44)   | Y1          |          |      | 0.80 |

| Distance Between Pads      | G           | 0.25     |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103A