Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 14x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f724t-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F722/3/4/6/7

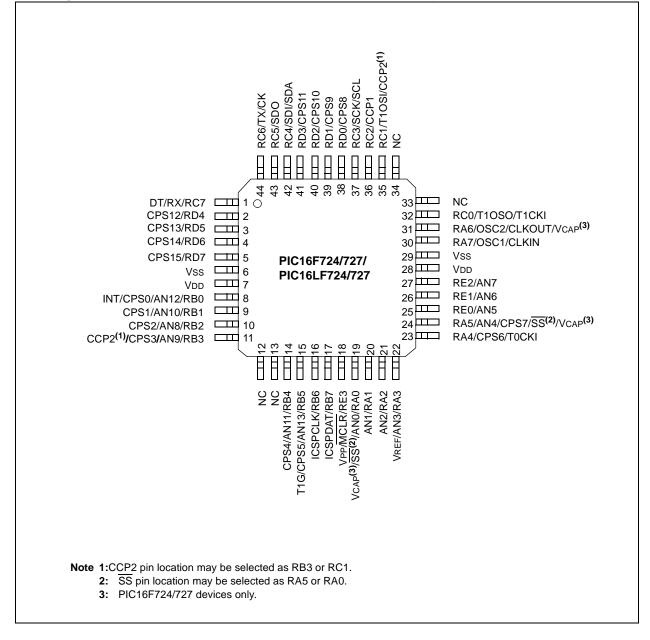

#### Pin Diagrams – 44-PIN TQFP (PIC16F724/727/PIC16LF724/727)

### TABLE 1-1: PIC16(L)F722/3/4/6/7 PINOUT DESCRIPTION

| Name                 | Function | Input<br>Type | Output<br>Type | Description                                                                                          |  |  |

|----------------------|----------|---------------|----------------|------------------------------------------------------------------------------------------------------|--|--|

| RA0/AN0/SS/VCAP      | RA0      | TTL           | CMOS           | General purpose I/O.                                                                                 |  |  |

|                      | AN0      | AN            |                | A/D Channel 0 input.                                                                                 |  |  |

|                      | SS       | ST            | _              | Slave Select input.                                                                                  |  |  |

|                      | VCAP     | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F72X only).                                             |  |  |

| RA1/AN1              | RA1      | TTL           | CMOS           | General purpose I/O.                                                                                 |  |  |

|                      | AN1      | AN            | _              | A/D Channel 1 input.                                                                                 |  |  |

| RA2/AN2              | RA2      | TTL           | CMOS           | General purpose I/O.                                                                                 |  |  |

|                      | AN2      | AN            | —              | A/D Channel 2 input.                                                                                 |  |  |

| RA3/AN3/Vref         | RA3      | TTL           | CMOS           | General purpose I/O.                                                                                 |  |  |

|                      | AN3      | AN            | _              | A/D Channel 3 input.                                                                                 |  |  |

|                      | Vref     | AN            | —              | A/D Voltage Reference input.                                                                         |  |  |

| RA4/CPS6/T0CKI       | RA4      | TTL           | CMOS           | General purpose I/O.                                                                                 |  |  |

|                      | CPS6     | AN            | _              | Capacitive sensing input 6.                                                                          |  |  |

|                      | T0CKI    | ST            | _              | Timer0 clock input.                                                                                  |  |  |

| RA5/AN4/CPS7/SS/VCAP | RA5      | TTL           | CMOS           | General purpose I/O.                                                                                 |  |  |

|                      | AN4      | AN            |                | A/D Channel 4 input.                                                                                 |  |  |

|                      | CPS7     | AN            | —              | Capacitive sensing input 7.                                                                          |  |  |

|                      | SS       | ST            | _              | Slave Select input.                                                                                  |  |  |

|                      | VCAP     | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F72X only).                                             |  |  |

| RA6/OSC2/CLKOUT/VCAP | RA6      | TTL           | CMOS           | General purpose I/O.                                                                                 |  |  |

|                      | OSC2     | —             | XTAL           | Crystal/Resonator (LP, XT, HS modes).                                                                |  |  |

|                      | CLKOUT   | _             | CMOS           | Fosc/4 output.                                                                                       |  |  |

|                      | VCAP     | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F72X only).                                             |  |  |

| RA7/OSC1/CLKIN       | RA7      | TTL           | CMOS           | General purpose I/O.                                                                                 |  |  |

|                      | OSC1     | XTAL          | _              | Crystal/Resonator (LP, XT, HS modes).                                                                |  |  |

|                      | CLKIN    | CMOS          | _              | External clock input (EC mode).                                                                      |  |  |

|                      | CLKIN    | ST            | _              | RC oscillator connection (RC mode).                                                                  |  |  |

| RB0/AN12/CPS0/INT    | RB0      | TTL           | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |  |  |

|                      | AN12     | AN            | _              | A/D Channel 12 input.                                                                                |  |  |

|                      | CPS0     | AN            | _              | Capacitive sensing input 0.                                                                          |  |  |

|                      | INT      | ST            | _              | External interrupt.                                                                                  |  |  |

| RB1/AN10/CPS1        | RB1      | TTL           | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |  |  |

|                      | AN10     | AN            | —              | A/D Channel 10 input.                                                                                |  |  |

|                      | CPS1     | AN            | —              | Capacitive sensing input 1.                                                                          |  |  |

| RB2/AN8/CPS2         | RB2      | TTL           | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |  |  |

|                      | AN8      | AN            | —              | A/D Channel 8 input.                                                                                 |  |  |

|                      | CPS2     | AN            |                | Capacitive sensing input 2.                                                                          |  |  |

| RB3/AN9/CPS3/CCP2    | RB3      | TTL           | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |  |  |

|                      | AN9      | AN            |                | A/D Channel 9 input.                                                                                 |  |  |

|                      | CPS3     | AN            | _              | Capacitive sensing input 3.                                                                          |  |  |

|                      |          |               | CMOS           | Capture/Compare/PWM2.                                                                                |  |  |

| R/W-0                  | R/W-0                           | R/W-0                                                     | R/W-0          | R/W-0               | R/W-0               | R/W-0           | R/W-x        |

|------------------------|---------------------------------|-----------------------------------------------------------|----------------|---------------------|---------------------|-----------------|--------------|

| GIE                    | PEIE                            | TOIE                                                      | INTE           | RBIE <sup>(1)</sup> | T0IF <sup>(2)</sup> | INTF            | RBIF         |

| bit 7                  |                                 |                                                           |                |                     |                     |                 | bit C        |

|                        |                                 |                                                           |                |                     |                     |                 |              |

| Legend:<br>R = Readabl | o hit                           | W = Writable I                                            | nit            | II – I Inimpler     | nented bit, read    | 1 26 '0'        |              |

| -n = Value at          |                                 | '1' = Bit is set                                          | JIL            | '0' = Bit is cle    |                     | x = Bit is unkr | NOWD         |

|                        |                                 | 1 – Dit 13 Set                                            |                |                     | areu                |                 | IOWIT        |

| bit 7                  | GIE: Global Ir                  | nterrupt Enable                                           | bit            |                     |                     |                 |              |

|                        | 1 = Enables a<br>0 = Disables a | all unmasked in all interrupts                            | terrupts       |                     |                     |                 |              |

| bit 6                  | 1 = Enables a                   | eral Interrupt Er<br>all unmasked pe<br>all peripheral in | eripheral inte | rrupts              |                     |                 |              |

| bit 5                  | 1 = Enables t                   | Overflow Interr<br>he Timer0 inter<br>the Timer0 inter    | rupt           | it                  |                     |                 |              |

| bit 4                  | 1 = Enables t                   | IT External Inte<br>he RB0/INT ext<br>the RB0/INT ex      | ernal interru  | ot                  |                     |                 |              |

| bit 3                  | 1 = Enables t                   | B Change Intern<br>he PORTB cha<br>the PORTB cha          | nge interrupt  |                     |                     |                 |              |

| bit 2                  | 1 = TMR0 reg                    | Overflow Interr<br>gister has overfl<br>gister did not ov | owed (must l   |                     | oftware)            |                 |              |

| bit 1                  | 1 = The RB0/                    | T External Inte<br>INT external int<br>INT external int   | errupt occuri  | ed (must be cle     | eared in softwa     | re)             |              |

| bit 0                  |                                 |                                                           |                | eneral purpose      | I/O pins chang      | jed state (must | be cleared i |

|                        | 0 = None of t                   |                                                           |                |                     | h                   |                 |              |

#### **REGISTER 4-1:** INTCON: INTERRUPT CONTROL REGISTER

- The appropriate bits in the IOCB register must also be set. Note 1:

- 2: T0IF bit is set when Timer0 rolls over. Timer0 is unchanged on Reset and should be initialized before clearing T0IF bit.

# PIC16(L)F722/3/4/6/7

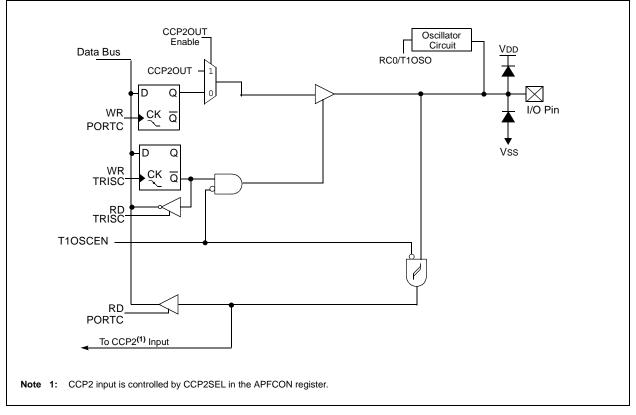

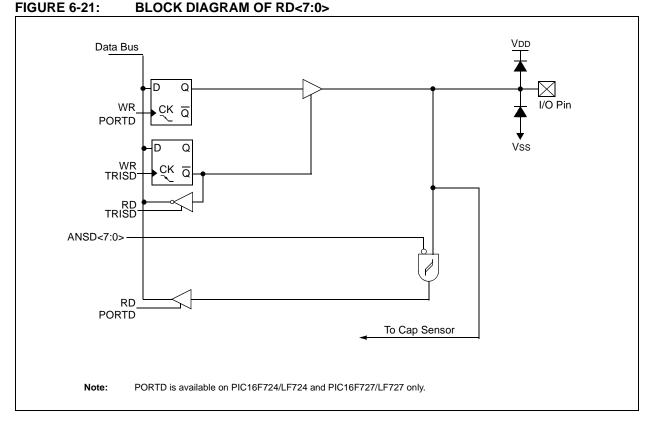

#### 6.5.6 RD4/CPS12

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### 6.5.7 RD5/CPS13

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- a capacitive sensing input

#### 6.5.8 RD6/CPS14

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### 6.5.9 RD7/CPS15

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

| TABLE 6-4: SUMM | IARY OF REGISTERS ASSOCIATED WITH PORTD <sup>(1)</sup> |

|-----------------|--------------------------------------------------------|

|-----------------|--------------------------------------------------------|

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|--------|--------|--------|---------|---------|--------|--------|----------------------|---------------------------------|

| ANSELD  | ANSD7  | ANSD6  | ANSD5  | ANSD4  | ANSD3   | ANSD2   | ANSD1  | ANSD0  | 1111 1111            | 1111 1111                       |

| CPSCON0 | CPSON  | —      | —      | —      | CPSRNG1 | CPSRNG0 | CPSOUT | TOXCS  | 0 0000               | 0 0000                          |

| CPSCON1 |        | —      | —      | _      | CPSCH3  | CPSCH2  | CPSCH1 | CPSCH0 | 0000                 | 0000                            |

| PORTD   | RD7    | RD6    | RD5    | RD4    | RD3     | RD2     | RD1    | RD0    | XXXX XXXX            | xxxx xxxx                       |

| TRISD   | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3  | TRISD2  | TRISD1 | TRISD0 | 1111 1111            | 1111 1111                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTD.**Note 1:**These registers are not implemented on the PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'.

#### © 2007-2015 Microchip Technology Inc.

#### DS40001341F-page 79

### 7.6 External Clock Modes

#### 7.6.1 OSCILLATOR START-UP TIMER (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations on the OSC1 pin before the device is released from Reset. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

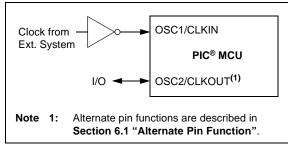

#### 7.6.2 EC MODE

The External Clock (EC) mode allows an externally generated logic level as the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input and the OSC2 is available for general purpose I/O. Figure 7-2 shows the pin connections for EC mode.

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### FIGURE 7-2: EXTERNAL CLOCK (EC) MODE OPERATION

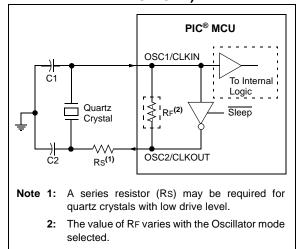

#### 7.6.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 7-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

LP Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is best suited to drive resonators with a low drive level specification, for example, tuning fork type crystals.

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 7-3 and Figure 7-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

#### FIGURE 7-3: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices (DS00826)

- AN849, Basic PIC<sup>®</sup> Oscillator Design (DS00849)

- AN943, Practical PIC<sup>®</sup> Oscillator Analysis and Design (DS00943)

- AN949, Making Your Oscillator Work (DS00949).

# PIC16(L)F722/3/4/6/7

#### 9.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- 2. Configure the ADC module:

- Select ADC conversion clock

- Configure voltage reference

- Select ADC input channel

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- Enable ADC interrupt

- Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

**Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

2: Refer to Section 9.3 "A/D Acquisition Requirements".

#### EXAMPLE 9-1: A/D CONVERSION

;This code block configures the ADC ;for polling, Vdd reference, Frc clock ;and ANO input. ;

;Conversion start & polling for completion ; are included.

| ;       |             |                      |

|---------|-------------|----------------------|

| BANKSEL | ADCON1      | ;                    |

| MOVLW   | B'01110000' | ;ADC Frc clock,      |

|         |             | ;VDD reference       |

| MOVWF   | ADCON1      | ;                    |

| BANKSEL | TRISA       | ;                    |

| BSF     | TRISA,0     | ;Set RAO to input    |

| BANKSEL | ANSELA      | ;                    |

| BSF     | ANSELA,0    | ;Set RA0 to analog   |

| BANKSEL | ADCON0      | ;                    |

| MOVLW   | B'0000001'  | ;AN0, On             |

| MOVWF   | ADCON0      | ;                    |

| CALL    | SampleTime  | ;Acquisiton delay    |

| BSF     | ADCON0,GO   | ;Start conversion    |

| BTFSC   | ADCON0,GO   | ;Is conversion done? |

| GOTO    | \$-1        | ;No, test again      |

| BANKSEL | ADRES       | i                    |

| MOVF    | ADRES,W     | ;Read result         |

| MOVWF   | RESULT      | ;store in GPR space  |

|         |             |                      |

| R/W-1           | R/W-1                     | R/W-1                                                                                                                                                                | R/W-1                                                                                  | R/W-1            | R/W-1            | R/W-1           | R/W-1 |

|-----------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------|------------------|-----------------|-------|

| RBPU            | INTEDG                    | TOCS                                                                                                                                                                 | TOSE                                                                                   | PSA              | PS2              | PS1             | PS0   |

| bit 7           |                           |                                                                                                                                                                      |                                                                                        |                  |                  |                 | bit ( |

|                 |                           |                                                                                                                                                                      |                                                                                        |                  |                  |                 |       |

| Legend:         |                           |                                                                                                                                                                      |                                                                                        |                  |                  |                 |       |

| R = Readable    | bit                       | W = Writable                                                                                                                                                         | bit                                                                                    | U = Unimpler     | nented bit, read | d as '0'        |       |

| -n = Value at F | POR                       | '1' = Bit is se                                                                                                                                                      | t                                                                                      | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

| bit 7           |                           | ull-ups are dis                                                                                                                                                      | abled                                                                                  | dual port latch  | values           |                 |       |

| bit 6           | •                         | errupt Edge Se<br>on rising edge<br>on falling edge                                                                                                                  | of INT pin                                                                             |                  |                  |                 |       |

| bit 5           | 1 = Transition            | Clock Source<br>on T0CKI pin<br>astruction cycle                                                                                                                     | or CPSOSC s                                                                            |                  |                  |                 |       |

| bit 4           |                           | Source Edge<br>t on high-to-lov<br>t on low-to-hig                                                                                                                   | w transition or                                                                        |                  |                  |                 |       |

| bit 3           |                           | er Assignmen<br>is assigned to<br>is assigned to                                                                                                                     | the WDT                                                                                | nodule           |                  |                 |       |

| bit 2-0         | <b>PS&lt;2:0&gt;:</b> Pre | escaler Rate S                                                                                                                                                       | elect bits                                                                             |                  |                  |                 |       |

|                 | BIT                       | VALUE TMR0 R                                                                                                                                                         | ATE WDT RA                                                                             | TE               |                  |                 |       |

|                 | 0<br>0<br>1<br>1<br>1     | 00         1:2           01         1:4           10         1:8           11         1:1           00         1:3           01         1:6           10         1:1 | 1:2           1:4           1:8           1:16           4           1:32           28 |                  |                  |                 |       |

| TABLE 11-1:     |                           |                                                                                                                                                                      | TERS ASSO                                                                              |                  | H TIMERO         |                 |       |

#### REGISTER 11-1: OPTION\_REG: OPTION REGISTER

| Name       | Bit 7     | Bit 6         | Bit 5  | Bit 4     | Bit 3     | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|-----------|---------------|--------|-----------|-----------|---------|--------|--------|----------------------|---------------------------------|

| CPSCON0    | CPSON     |               |        |           | CPSRNG1   | CPSRNG0 | CPSOUT | T0XCS  | 0 0000               | 0 0000                          |

| INTCON     | GIE       | PEIE          | TOIE   | INTE      | RBIE      | T0IF    | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| OPTION_REG | RBPU      | INTEDG        | TOCS   | TOSE      | PSA       | PS2     | PS1    | PS0    | 1111 1111            | 1111 1111                       |

| TMR0       | Timer0 Mo | dule Register |        | XXXX XXXX | uuuu uuuu |         |        |        |                      |                                 |

| TRISA      | TRISA7    | TRISA6        | TRISA5 | TRISA4    | TRISA3    | TRISA2  | TRISA1 | TRISA0 | 1111 1111            | 1111 1111                       |

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Timer0 module.

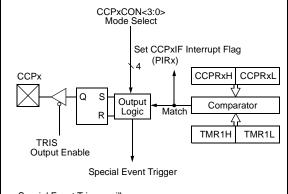

### 15.2 Compare Mode

In Compare mode, the 16-bit CCPRx register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCPx module may:

- Toggle the CCPx output

- Set the CCPx output

- · Clear the CCPx output

- Generate a Special Event Trigger

- Generate a Software Interrupt

The action on the pin is based on the value of the CCPxM<3:0> control bits of the CCPxCON register.

All Compare modes can generate an interrupt.

#### FIGURE 15-2: COMPARE MODE OPERATION BLOCK DIAGRAM

- Special Event Trigger will:

- Clear TMR1H and TMR1L registers.

- NOT set interrupt flag bit TMR1IF of the PIR1 register.

Set the GO/DONE bit to start the ADC conversion

- (CCP2 only).

#### 15.2.1 CCPx PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

Either RC1 or RB3 can be selected as the CCP2 pin. Refer to **Section 6.1** "Alternate Pin Function" for more information.

| Note: | Clearing the CCPxCON register will force    |

|-------|---------------------------------------------|

|       | the CCPx compare output latch to the        |

|       | default low level. This is not the PORT I/O |

|       | data latch.                                 |

#### 15.2.2 TIMER1 MODE SELECTION

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode. Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. For the Compare operation of the TMR1 register to the CCPRx register to occur, Timer1 must be clocked from the Instruction Clock (Fosc/4) or from an external clock source.

#### 15.2.3 SOFTWARE INTERRUPT MODE

When Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPxIF bit in the PIRx register is set and the CCPx module does not assert control of the CCPx pin (refer to the CCPxCON register).

#### 15.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is chosen (CCPxM<3:0> = 1011), the CCPx module does the following:

- Resets Timer1

- Starts an ADC conversion if ADC is enabled (CCP2 only)

The CCPx module does not assert control of the CCPx pin in this mode (refer to the CCPxCON register).

The Special Event Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPRxH, CCPRxL register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. This allows the CCPRxH, CCPRxL register pair to effectively provide a 16-bit programmable period register for Timer1.

Note 1: The Special Event Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

2: Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Special Event Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

#### 15.2.5 COMPARE DURING SLEEP

The Compare Mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

| Name    | Bit 7        | Bit 6          | Bit 5          | Bit 4          | Bit 3                   | Bit 2    | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------------|----------------|----------------|----------------|-------------------------|----------|---------|---------|----------------------|---------------------------------|

| ADCON0  | _            |                | CHS3           | CHS2           | CHS1                    | CHS0     | GO/DONE | ADON    | 00 0000              | 00 0000                         |

| ANSELB  | _            | _              | ANSB5          | ANSB4          | ANSB3                   | ANSB2    | ANSB1   | ANSB0   | 11 1111              | 11 1111                         |

| APFCON  | _            | _              | _              | _              | _                       | _        | SSSEL   | CCP2SEL | 00                   | 00                              |

| CCP1CON | _            | _              | DC1B1          | DC1B0          | CCP1M3                  | CCP1M2   | CCP1M1  | CCP1M0  | 00 0000              | 00 0000                         |

| CCP2CON | _            | _              | DC2B1          | DC2B0          | CCP2M3                  | CCP2M2   | CCP2M1  | CCP2M0  | 00 0000              | 00 0000                         |

| CCPRxL  | Capture/Com  | npare/PWM R    | egister X Lov  | v Byte         |                         |          |         |         | xxxx xxxx            | uuuu uuuu                       |

| CCPRxH  | Capture/Com  | npare/PWM R    | egister X Hig  | h Byte         |                         |          |         |         | xxxx xxxx            | uuuu uuuu                       |

| INTCON  | GIE          | PEIE           | TOIE           | INTE           | RBIE                    | T0IF     | INTF    | RBIF    | 0000 000x            | 0000 000x                       |

| PIE1    | TMR1GIE      | ADIE           | RCIE           | TXIE           | SSPIE                   | CCP1IE   | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIE2    | —            | -              | —              | -              | —                       | —        | —       | CCP2IE  | 0                    | 0                               |

| PIR1    | TMR1GIF      | ADIF           | RCIF           | TXIF           | SSPIF                   | CCP1IF   | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| PIR2    | —            | -              | —              | -              | —                       | —        | —       | CCP2IF  | 0                    | 0                               |

| T1CON   | TMR1CS1      | TMR1CS0        | T1CKPS1        | T1CKPS0        | T1OSCEN                 | T1SYNC   | _       | TMR10N  | 0000 00-0            | uuuu uu-u                       |

| T1GCON  | TMR1GE       | T1GPOL         | T1GTM          | T1GSPM         | T <u>1GGO</u> /<br>DONE | T1GVAL   | T1GSS1  | T1GSS0  | 0000 0x00            | 00x0 0x00                       |

| TMR1L   | Holding Regi | ster for the L | east Significa | nt Byte of the | 16-bit TMR1 I           | Register |         |         | xxxx xxxx            | uuuu uuuu                       |

| TMR1H   | Holding Regi | ster for the M | ost Significar | nt Byte of the | 16-bit TMR1 F           | Register |         |         | xxxx xxxx            | uuuu uuuu                       |

| TRISB   | TRISB7       | TRISB6         | TRISB5         | TRISB4         | TRISB3                  | TRISB2   | TRISB1  | TRISB0  | 1111 1111            | 1111 1111                       |

| TRISC   | TRISC7       | TRISC6         | TRISC5         | TRISC4         | TRISC3                  | TRISC2   | TRISC1  | TRISC0  | 1111 1111            | 1111 1111                       |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Compare.

| R/W-0         | R/W-0                                                                                                                                              | R/W-0                                                                               | R/W-0            | R/W-0            | R-0               | R-0               | R-x          |  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------|------------------|-------------------|-------------------|--------------|--|--|--|--|--|

| SPEN          | RX9                                                                                                                                                | SREN                                                                                | CREN             | ADDEN            | FERR              | OERR              | RX9D         |  |  |  |  |  |

| bit 7         |                                                                                                                                                    |                                                                                     |                  | •<br>•           |                   |                   | bit (        |  |  |  |  |  |

|               |                                                                                                                                                    |                                                                                     |                  |                  |                   |                   |              |  |  |  |  |  |

| Legend:       |                                                                                                                                                    |                                                                                     |                  |                  |                   | ( <b>a</b> )      |              |  |  |  |  |  |

| R = Readable  |                                                                                                                                                    | W = Writable                                                                        |                  | -                | mented bit, read  |                   |              |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                                | '1' = Bit is set                                                                    |                  | '0' = Bit is cle | ared              | x = Bit is unkn   | lown         |  |  |  |  |  |

| bit 7         | SPEN: Serial Port Enable bit <sup>(1)</sup>                                                                                                        |                                                                                     |                  |                  |                   |                   |              |  |  |  |  |  |

|               |                                                                                                                                                    |                                                                                     |                  | T and TX/CK n    | ins as serial por | rt nine)          |              |  |  |  |  |  |

|               |                                                                                                                                                    | rt disabled (be                                                                     |                  |                  | ins as senai poi  | t pins)           |              |  |  |  |  |  |

| bit 6         | <b>RX9:</b> 9-bit Re                                                                                                                               | ceive Enable b                                                                      | oit              |                  |                   |                   |              |  |  |  |  |  |

|               | 1 = Selects 9                                                                                                                                      | -bit reception                                                                      |                  |                  |                   |                   |              |  |  |  |  |  |

|               | 0 = Selects 8                                                                                                                                      | -bit reception                                                                      |                  |                  |                   |                   |              |  |  |  |  |  |

| bit 5         | -                                                                                                                                                  | Receive Enal                                                                        | ole bit          |                  |                   |                   |              |  |  |  |  |  |

|               | Asynchronous                                                                                                                                       | <u>s mode</u> :                                                                     |                  |                  |                   |                   |              |  |  |  |  |  |

|               | Don't care                                                                                                                                         | mode – Maste                                                                        | vr.              |                  |                   |                   |              |  |  |  |  |  |

|               | -                                                                                                                                                  |                                                                                     | <u>.</u> .       |                  |                   |                   |              |  |  |  |  |  |

|               |                                                                                                                                                    | <ul> <li>1 = Enables single receive</li> <li>0 = Disables single receive</li> </ul> |                  |                  |                   |                   |              |  |  |  |  |  |

|               | This bit is cleared after reception is complete.                                                                                                   |                                                                                     |                  |                  |                   |                   |              |  |  |  |  |  |

|               | <u>Synchronous mode – Slave:</u><br>Don't care                                                                                                     |                                                                                     |                  |                  |                   |                   |              |  |  |  |  |  |

| L:1 1         |                                                                                                                                                    |                                                                                     | Enchla hit       |                  |                   |                   |              |  |  |  |  |  |

| bit 4         | CREN: Continuous Receive Enable bit                                                                                                                |                                                                                     |                  |                  |                   |                   |              |  |  |  |  |  |

|               | Asynchronous mode:<br>1 = Enables receiver                                                                                                         |                                                                                     |                  |                  |                   |                   |              |  |  |  |  |  |

|               | 0 = Disables                                                                                                                                       |                                                                                     |                  |                  |                   |                   |              |  |  |  |  |  |

|               | Synchronous mode:                                                                                                                                  |                                                                                     |                  |                  |                   |                   |              |  |  |  |  |  |

|               | <ul> <li>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)</li> <li>0 = Disables continuous receive</li> </ul> |                                                                                     |                  |                  |                   |                   |              |  |  |  |  |  |

| bit 3         |                                                                                                                                                    |                                                                                     |                  |                  |                   |                   |              |  |  |  |  |  |

| DIL J         | ADDEN: Address Detect Enable bit<br>Asynchronous mode 9-bit ( $RX9 = 1$ ):                                                                         |                                                                                     |                  |                  |                   |                   |              |  |  |  |  |  |

|               | 1 = Enables address detection, enable interrupt and load the receive buffer when RSR<8> is set                                                     |                                                                                     |                  |                  |                   |                   |              |  |  |  |  |  |

|               | 0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit                                                     |                                                                                     |                  |                  |                   |                   |              |  |  |  |  |  |

|               | <u>Asynchronous mode 8-bit (RX9 = 0)</u> :                                                                                                         |                                                                                     |                  |                  |                   |                   |              |  |  |  |  |  |

|               | Don't care<br>Synchronous                                                                                                                          | modo:                                                                               |                  |                  |                   |                   |              |  |  |  |  |  |

|               | Must be set to                                                                                                                                     |                                                                                     |                  |                  |                   |                   |              |  |  |  |  |  |

| bit 2         | FERR: Frami                                                                                                                                        |                                                                                     |                  |                  |                   |                   |              |  |  |  |  |  |

|               |                                                                                                                                                    | -                                                                                   | updated by rea   | adina RCREG I    | edister and rec   | eive next valid l | ovte)        |  |  |  |  |  |

|               | <ul> <li>1 = Framing error (can be updated by reading RCREG register and receive next valid byte)</li> <li>0 = No framing error</li> </ul>         |                                                                                     |                  |                  |                   |                   |              |  |  |  |  |  |

| bit 1         | OERR: Overr                                                                                                                                        | un Error bit                                                                        |                  |                  |                   |                   |              |  |  |  |  |  |

|               | 1 = Overrun<br>0 = No overr                                                                                                                        |                                                                                     | leared by clea   | aring bit CREN   | )                 |                   |              |  |  |  |  |  |

| bit 0         | RX9D: Ninth                                                                                                                                        | bit of Received                                                                     | l Data           |                  |                   |                   |              |  |  |  |  |  |

|               | This can be a                                                                                                                                      | ddress/data bi                                                                      | t or a parity bi | t and must be o  | calculated by us  | er firmware.      |              |  |  |  |  |  |

|               | he AUSART m<br>RISx = 1.                                                                                                                           | odule automa                                                                        | tically change   | es the pin fro   | m tri-state to o  | drive as neede    | ed. Configur |  |  |  |  |  |

#### REGISTER 16-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

#### 17.1.1 MASTER MODE

In Master mode, data transfer can be initiated at any time because the master controls the SCK line. Master mode determines when the slave (Figure 17-1, Processor 2) transmits data via control of the SCK line.

#### 17.1.1.1 Master Mode Operation

The SSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR register shifts the data in and out of the device, MSb first. The SSPBUF register holds the data that is written out of the master until the received data is ready. Once the eight bits of data have been received, the byte is moved to the SSPBUF register. The Buffer Full Status bit, BF of the SSPSTAT register, and the SSP Interrupt Flag bit, SSPIF of the PIR1 register, are then set.

Any write to the SSPBUF register during transmission/reception of data will be ignored and the Write Collision Detect bit, WCOL of the SSPCON register, will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data is written to the SSPBUF. The BF bit of the SSPSTAT register is set when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. The SSP interrupt may be used to determine when the transmission/reception is complete and the SSPBUF must be read and/or written. If interrupts are not used, then software polling can be done to ensure that a write collision does not occur. Example 17-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

Note: The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register.

#### 17.1.1.2 Enabling Master I/O

To enable the serial port, the SSPEN bit of the SSPCON register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCON register and then set the SSPEN bit. If a Master mode of operation is selected in the SSPM bits of the SSPCON register, the SDI, SDO and SCK pins will be assigned as serial port pins.

For these pins to function as serial port pins, they must have their corresponding data direction bits set or cleared in the associated TRIS register as follows:

- · SDI configured as input

- SDO configured as output

- SCK configured as output

### 17.1.1.3 Master Mode Setup

In Master mode, the data is transmitted/received as soon as the SSPBUF register is loaded with a byte value. If the master is only going to receive, SDO output could be disabled (programmed and used as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate.

When initializing SPI Master mode operation, several options need to be specified. This is accomplished by programming the appropriate control bits in the SSPCON and SSPSTAT registers. These control bits allow the following to be specified:

- SCK as clock output

- Idle state of SCK (CKP bit)

- Data input sample phase (SMP bit)

- Output data on rising/falling edge of SCK (CKE bit)

- Clock bit rate

In Master mode, the SPI clock rate (bit rate) is user selectable to be one of the following:

- Fosc/4 (or TCY)

- Fosc/16 (or 4 TCY)

- Fosc/64 (or 16 TCY)

- (Timer2 output)/2

This allows a maximum data rate of 5 Mbps (at Fosc = 20 MHz).

Figure 17-3 shows the waveforms for Master mode. The clock polarity is selected by appropriately programming the CKP bit of the SSPCON register. When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The sample time of the input data is shown based on the state of the SMP bit and can occur at the middle or end of the data output time. The time when the SSPBUF is loaded with the received data is shown.

#### 17.1.1.4 Sleep in Master Mode

In Master mode, all module clocks are halted and the transmission/reception will remain in their current state, paused, until the device wakes from Sleep. After the device wakes up from Sleep, the module will continue to transmit/receive data.

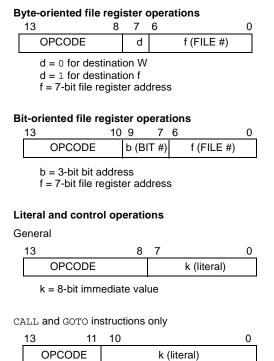

## 21.0 INSTRUCTION SET SUMMARY

The PIC16(L)F722/3/4/6/7 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 21-1, while the various opcode fields are summarized in Table 21-1.

Table 21-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8-bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

### 21.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF PORTB instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended consequence of clearing the condition that set the RBIF flag.

#### TABLE 21-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ . It is<br>the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                  |

| PC    | Program Counter                                                                                                                                                                   |

| TO    | Time-out bit                                                                                                                                                                      |

| С     | Carry bit                                                                                                                                                                         |

| DC    | Digit carry bit                                                                                                                                                                   |

| Z     | Zero bit                                                                                                                                                                          |

| PD    | Power-down bit                                                                                                                                                                    |

## FIGURE 21-1: GENERAL FORMAT FOR INSTRUCTIONS

## 23.0 ELECTRICAL SPECIFICATIONS

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                         | 40°C to +125°C                        |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Storage temperature                                                                                                    | 65°C to +150°C                        |

| Voltage on VDD with respect to Vss, PIC16F72X                                                                          | 0.3V to +6.5V                         |

| Voltage on VCAP pin with respect to Vss, PIC16F72X                                                                     | 0.3V to +4.0V                         |

| Voltage on VDD with respect to Vss, PIC16LF72X                                                                         | 0.3V to +4.0V                         |

| Voltage on MCLR with respect to Vss                                                                                    | 0.3V to +9.0V                         |

| Voltage on all other pins with respect to Vss                                                                          | 0.3V to (VDD + 0.3V)                  |

| Total power dissipation <sup>(1)</sup>                                                                                 | 800 mW                                |

| Maximum current out of Vss pin                                                                                         | 95 mA                                 |

| Maximum current into VDD pin                                                                                           | 70 mA                                 |

| Clamp current, IK (VPIN < 0 or VPIN > VDD)                                                                             | ± 20 mA                               |

| Maximum output current sunk by any I/O pin                                                                             | 25 mA                                 |

| Maximum output current sourced by any I/O pin                                                                          | 25 mA                                 |

| Maximum current sunk by all ports (2), -40°C $\leq$ TA $\leq$ +85°C for industrial                                     | 200 mA                                |

| Maximum current sunk by all ports (2), -40°C $\leq$ TA $\leq$ +125°C for extended                                      | 90 mA                                 |

| Maximum current sourced by all ports <sup>(2)</sup> , $40^{\circ}C \le TA \le +85^{\circ}C$ for industrial             | 140 mA                                |

| Maximum current sourced by all ports <sup>(2)</sup> , -40°C $\leq$ TA $\leq$ +125°C for extended                       | 65 mA                                 |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $-\Sigma$ IOH} + $\Sigma$ {(VDD $-\Sigma$ | · VOH) x IOH} + $\Sigma$ (VOI x IOL). |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

### 23.2 DC Characteristics: PIC16(L)F722/3/4/6/7-I/E (Industrial, Extended)

| PIC16LF722/3/4/6/7<br>PIC16F722/3/4/6/7 |                                    |         |      |      |       |            |                                                                                |  |  |

|-----------------------------------------|------------------------------------|---------|------|------|-------|------------|--------------------------------------------------------------------------------|--|--|

|                                         |                                    |         |      |      |       |            | less otherwise stated)<br>A ≤ +85°C for industrial<br>A ≤ +125°C for extended  |  |  |

| Param                                   | Device                             | Min.    | Typt | Max. | Units | Conditions |                                                                                |  |  |

| No.                                     | Characteristics                    | IVIIII. | Тур† |      |       | VDD        | Note                                                                           |  |  |

|                                         | Supply Current (IDD) <sup>(1</sup> | , 2)    |      |      |       |            |                                                                                |  |  |

| D009                                    | LDO Regulator                      | -       | 350  | —    | μΑ    | —          | HS, EC OR INTOSC/INTOSCIO (8-16 MHz<br>Clock modes with all VCAP pins disabled |  |  |

|                                         |                                    | _       | 50   | —    | μΑ    |            | All VCAP pins disabled                                                         |  |  |

|                                         |                                    | —       | 30   | —    | μΑ    | —          | VCAP enabled on RA0, RA5 or RA6                                                |  |  |

|                                         |                                    | _       | 5    | _    | μΑ    | —          | LP Clock mode and Sleep (requires FVR and BOR to be disabled)                  |  |  |

| D010                                    |                                    | _       | 7.0  | 12   | μΑ    | 1.8        | Fosc = 32 kHz                                                                  |  |  |

|                                         |                                    |         | 9.0  | 14   | μΑ    | 3.0        | LP Oscillator mode (Note 4),<br>-40°C $\leq$ TA $\leq$ +85°C                   |  |  |

| D010                                    |                                    | —       | 11   | 20   | μΑ    | 1.8        | Fosc = 32 kHz                                                                  |  |  |

|                                         |                                    | —       | 14   | 22   | μΑ    | 3.0        | LP Oscillator mode (Note 4),                                                   |  |  |

|                                         |                                    | —       | 15   | 24   | μΑ    | 5.0        | $-40^{\circ}C \le TA \le +85^{\circ}C$                                         |  |  |

| D011                                    |                                    | —       | 7.0  | 12   | μΑ    | 1.8        | Fosc = 32 kHz                                                                  |  |  |

|                                         |                                    | —       | 9.0  | 18   | μΑ    | 3.0        | LP Oscillator mode<br>-40°C $\leq$ TA $\leq$ +125°C                            |  |  |

| D011                                    |                                    |         | 11   | 21   | μΑ    | 1.8        | Fosc = 32 kHz                                                                  |  |  |

|                                         |                                    | _       | 14   | 25   | μΑ    | 3.0        | LP Oscillator mode (Note 4)<br>-40°C $\leq$ TA $\leq$ +125°C                   |  |  |

|                                         |                                    | —       | 15   | 27   | μΑ    | 5.0        | -40 C \sec 1A \sec +125 C                                                      |  |  |

| D011                                    |                                    | _       | 110  | 150  | μΑ    | 1.8        | Fosc = 1 MHz                                                                   |  |  |

|                                         |                                    |         | 150  | 215  | μΑ    | 3.0        | XT Oscillator mode                                                             |  |  |

| D011                                    |                                    |         | 120  | 175  | μΑ    | 1.8        | Fosc = 1 MHz                                                                   |  |  |

|                                         |                                    |         | 180  | 250  | μΑ    | 3.0        | XT Oscillator mode (Note 5)                                                    |  |  |

| <b>B</b> 4 4 5                          |                                    | —       | 240  | 300  | μA    | 5.0        | -                                                                              |  |  |

| D012                                    |                                    |         | 230  | 300  | μΑ    | 1.8        | Fosc = 4 MHz<br>XT Oscillator mode                                             |  |  |

| Data                                    |                                    | -       | 400  | 600  | μΑ    | 3.0        |                                                                                |  |  |

| D012                                    |                                    |         | 250  | 350  | μΑ    | 1.8        | Fosc = 4 MHz<br>XT Oscillator mode (Note 5)                                    |  |  |

|                                         |                                    |         | 420  | 650  | μΑ    | 3.0        | -                                                                              |  |  |

| D012                                    |                                    |         | 500  | 750  | μΑ    | 5.0        |                                                                                |  |  |

| D013                                    |                                    |         | 125  | 180  | μΑ    | 1.8        | Fosc = 1 MHz<br>EC Oscillator mode                                             |  |  |

| D012                                    |                                    | _       | 230  | 270  | μΑ    | 3.0        |                                                                                |  |  |

| D013                                    |                                    |         | 150  | 205  | μΑ    | 1.8        | Fosc = 1 MHz<br>EC Oscillator mode (Note 5)                                    |  |  |

|                                         |                                    |         | 225  | 320  | μΑ    | 3.0        |                                                                                |  |  |

|                                         |                                    | _       | 250  | 410  | μA    | 5.0        |                                                                                |  |  |

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

4: FVR and BOR are disabled.

5: 0.1 μF capacitor on VCAP (RA0).

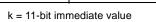

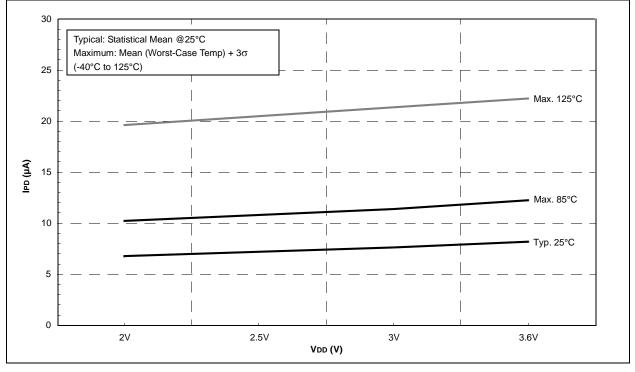

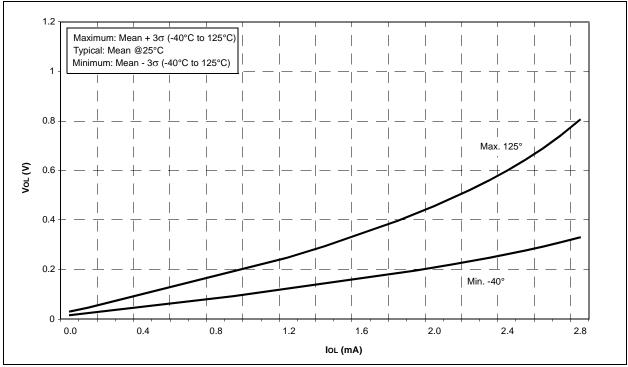

#### FIGURE 24-33: PIC16F722/3/4/6/7 BOR IPD vs. VDD, VCAP = 0.1 µF

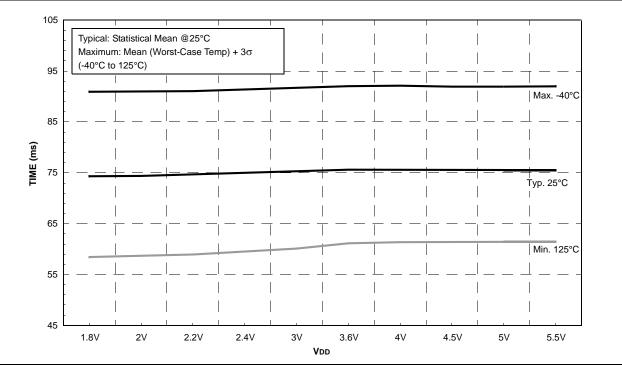

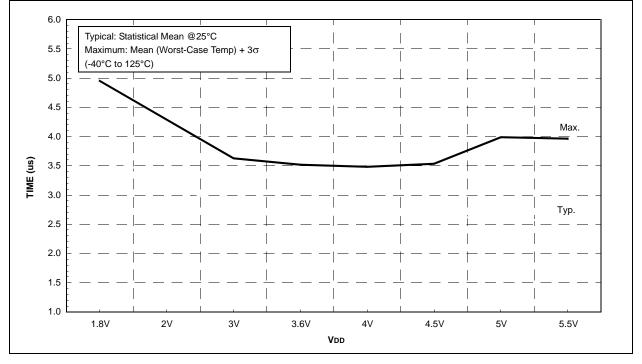

#### FIGURE 24-59: PIC16F722/3/4/6/7 WDT TIME-OUT PERIOD

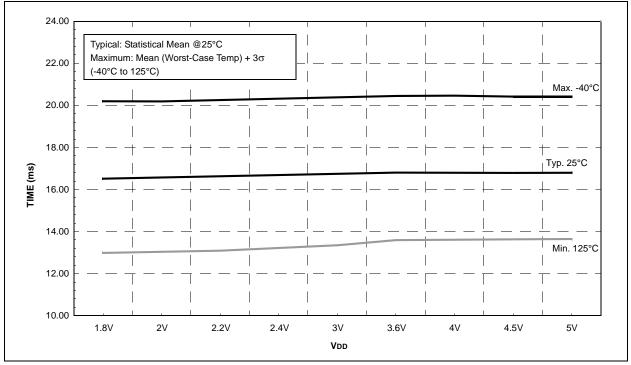

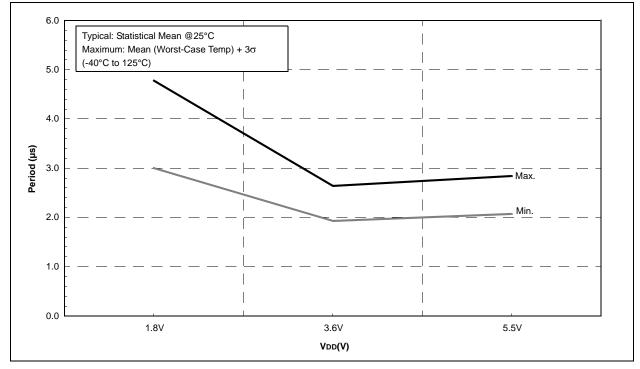

#### FIGURE 24-61: PIC16F722/3/4/6/7 A/D INTERNAL RC OSCILLATOR PERIOD

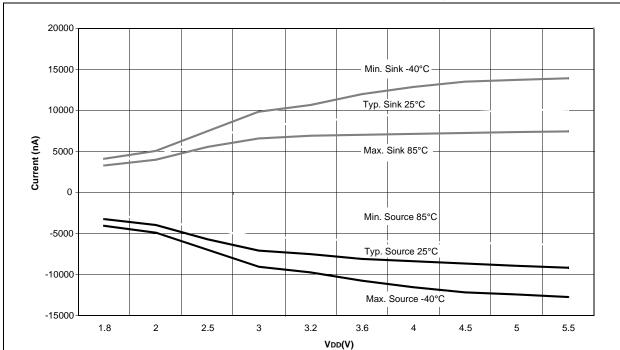

FIGURE 24-62: PIC16F722/3/4/6/7 CAP SENSE OUTPUT CURRENT, POWER MODE = HIGH

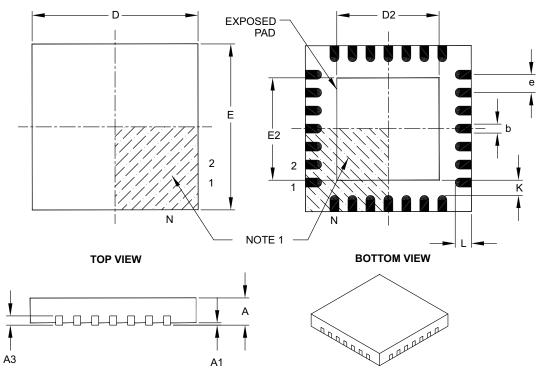

## 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            | MILLIMETERS |      |      |  |

|------------------------|------------------|-------------|------|------|--|

|                        | Dimension Limits | MIN         | NOM  | MAX  |  |

| Number of Pins         | N                |             | 28   |      |  |

| Pitch                  | е                | 0.65 BSC    |      |      |  |

| Overall Height         | A                | 0.80        | 0.90 | 1.00 |  |

| Standoff               | A1               | 0.00        | 0.02 | 0.05 |  |

| Contact Thickness      | A3               | 0.20 REF    |      |      |  |

| Overall Width          | E                | 6.00 BSC    |      |      |  |

| Exposed Pad Width      | E2               | 3.65        | 3.70 | 4.20 |  |

| Overall Length         | D                | 6.00 BSC    |      |      |  |

| Exposed Pad Length     | D2               | 3.65        | 3.70 | 4.20 |  |

| Contact Width          |                  | 0.23        | 0.30 | 0.35 |  |

| Contact Length         |                  | 0.50        | 0.55 | 0.70 |  |

| Contact-to-Exposed Pad |                  | 0.20        | -    | -    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B