Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 25                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 11x8b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-UFQFN Exposed Pad                                                     |

| Supplier Device Package    | 28-UQFN (4x4)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f726-e-mv |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address               | Name    | Bit 7        | Bit 6          | Bit 5         | Bit 4           | Bit 3         | Bit 2              | Bit 1              | Bit 0              | Value on:<br>POR, BOR | Page   |

|-----------------------|---------|--------------|----------------|---------------|-----------------|---------------|--------------------|--------------------|--------------------|-----------------------|--------|

| Bank 0                |         |              |                |               |                 |               |                    |                    |                    |                       |        |

| 00h <sup>(2)</sup>    | INDF    | Addressing   | this location  | uses conten   | ts of FSR to a  | address data  | memory (not        | a physical re      | gister)            | xxxx xxxx             | 29,37  |

| 01h                   | TMR0    | Timer0 Mod   | ule Register   |               |                 |               |                    |                    |                    | xxxx xxxx             | 105,37 |

| 02h <sup>(2)</sup>    | PCL     | Program Co   | ounter (PC) L  | east Signific | ant Byte        |               |                    |                    |                    | 0000 0000             | 28,37  |

| 03h <sup>(2)</sup>    | STATUS  | IRP          | RP1            | RP0           | TO              | PD            | Z                  | DC                 | С                  | 0001 1xxx             | 25,37  |

| 04h <sup>(2)</sup>    | FSR     | Indirect Dat | a Memory Ad    | dress Point   | er              |               |                    |                    |                    | xxxx xxxx             | 29,37  |

| 05h                   | PORTA   | RA7          | RA6            | RA5           | RA4             | RA3           | RA2                | RA1                | RA0                | xxxx xxxx             | 51,37  |

| 06h                   | PORTB   | RB7          | RB6            | RB5           | RB4             | RB3           | RB2                | RB1                | RB0                | xxxx xxxx             | 60,37  |

| 07h                   | PORTC   | RC7          | RC6            | RC5           | RC4             | RC3           | RC2                | RC1                | RC0                | XXXX XXXX             | 70,37  |

| 08h <sup>(3)</sup>    | PORTD   | RD7          | RD6            | RD5           | RD4             | RD3           | RD2                | RD1                | RD0                | XXXX XXXX             | 77,37  |

| 09h                   | PORTE   | —            | _              | _             | _               | RE3           | RE2 <sup>(3)</sup> | RE1 <sup>(3)</sup> | RE0 <sup>(3)</sup> | xxxx                  | 81,37  |

| 0Ah <sup>(1, 2)</sup> | PCLATH  | —            | _              | _             | Write Buffer    | for the upper | 5 bits of the F    | Program Cou        | nter               | 0 0000                | 28,37  |

| 0Bh <b>(2)</b>        | INTCON  | GIE          | PEIE           | T0IE          | INTE            | RBIE          | T0IF               | INTF               | RBIF               | 0000 000x             | 44,37  |

| 0Ch                   | PIR1    | TMR1GIF      | ADIF           | RCIF          | TXIF            | SSPIF         | CCP1IF             | TMR2IF             | TMR1IF             | 0000 0000             | 47,37  |

| 0Dh                   | PIR2    | —            | _              | _             | _               | _             | _                  | _                  | CCP2IF             | 0                     | 48,37  |

| 0Eh                   | TMR1L   | Holding Reg  | gister for the | Least Signifi | cant Byte of t  | he 16-bit TMI | R1 Register        |                    | •                  | XXXX XXXX             | 113,37 |

| 0Fh                   | TMR1H   | Holding Reg  | gister for the | Most Signific | cant Byte of th | ne 16-bit TMR | R1 Register        |                    |                    | XXXX XXXX             | 113,37 |

| 10h                   | T1CON   | TMR1CS1      | TMR1CS0        | T1CKPS1       | T1CKPS0         | T1OSCEN       | T1SYNC             | _                  | TMR10N             | 0000 00-0             | 117,37 |

| 11h                   | TMR2    | Timer2 Mod   | ule Register   |               |                 |               |                    |                    |                    | 0000 0000             | 120,37 |

| 12h                   | T2CON   | —            | TOUTPS3        | TOUTPS2       | TOUTPS1         | TOUTPS0       | TMR2ON             | T2CKPS1            | T2CKPS0            | -000 0000             | 121,37 |

| 13h                   | SSPBUF  | Synchronou   | s Serial Port  | Receive Bu    | ffer/Transmit   | Register      |                    |                    |                    | xxxx xxxx             | 161,37 |

| 14h                   | SSPCON  | WCOL         | SSPOV          | SSPEN         | CKP             | SSPM3         | SSPM2              | SSPM1              | SSPM0              | 0000 0000             | 178,37 |

| 15h                   | CCPR1L  | Capture/Co   | mpare/PWM      | Register (L   | SB)             |               |                    |                    |                    | xxxx xxxx             | 130,37 |

| 16h                   | CCPR1H  | Capture/Co   | mpare/PWM      | Register (M   | SB)             |               |                    |                    |                    | xxxx xxxx             | 130,37 |

| 17h                   | CCP1CON | —            | —              | DC1B1         | DC1B0           | CCP1M3        | CCP1M2             | CCP1M1             | CCP1M0             | 00 0000               | 129,37 |

| 18h                   | RCSTA   | SPEN         | RX9            | SREN          | CREN            | ADDEN         | FERR               | OERR               | RX9D               | 0000 000x             | 148,37 |

| 19h                   | TXREG   | USART Tra    | nsmit Data R   | egister       | •               |               | •                  |                    | •                  | 0000 0000             | 147,37 |

| 1Ah                   | RCREG   | USART Red    | eive Data R    | egister       |                 |               |                    |                    |                    | 0000 0000             | 145,37 |

| 1Bh                   | CCPR2L  | Capture/Co   | mpare/PWM      | Register 2 (  | LSB)            |               |                    |                    |                    | xxxx xxxx             | 130,37 |

| 1Ch                   | CCPR2H  | Capture/Co   | mpare/PWM      | Register 2 (  | MSB)            |               |                    |                    |                    | xxxx xxxx             | 130,37 |

| 1Dh                   | CCP2CON | _            | —              | DC2B1         | DC2B0           | CCP2M3        | CCP2M2             | CCP2M1             | CCP2M0             | 00 0000               | 129,37 |

| 1Eh                   | ADRES   | A/D Result   | Register       |               |                 |               |                    |                    | •                  | xxxx xxxx             | 100,37 |

| 1Fh                   | ADCON0  | _            | _              | CHS3          | CHS2            | CHS1          | CHS0               | GO/DONE            | ADON               | 00 0000               | 99,37  |

#### **TABLE 2-1:** PIC16(L)F722/3/4/6/7 SPECIAL FUNCTION REGISTER SUMMARY

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter. These registers can be addressed from any bank. These registers/bits are not implemented on PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'. Accessible only when SSPM<3:0> = 1001. Accessible only when SSPM<3:0>  $\neq$  1001. This bit is always '1' as RE3 is input-only. Note 1:

2:

3:

4:

5:

6:

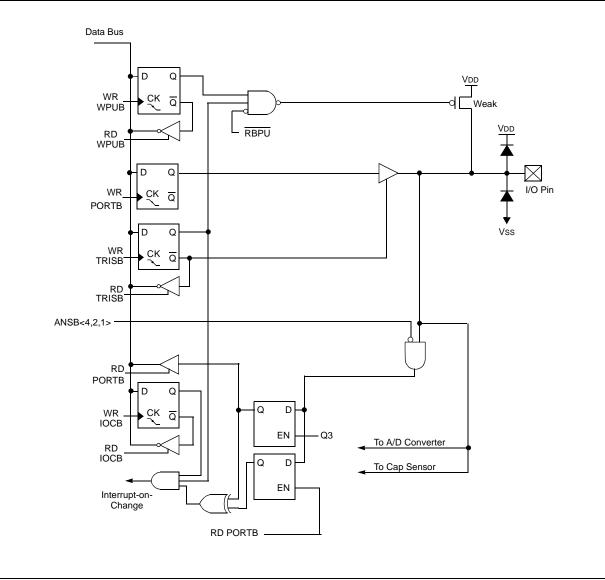

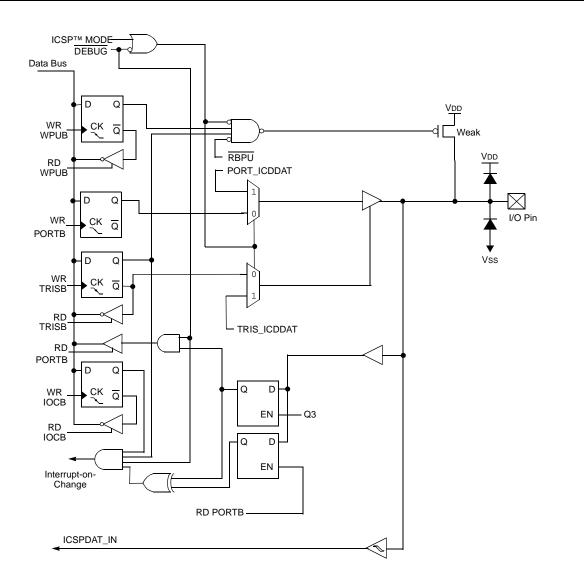

#### FIGURE 6-12: BLOCK DIAGRAM OF RB7

| Name       | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3                   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------|--------|--------|--------|--------|-------------------------|---------|---------|---------|----------------------|---------------------------------|

| ADCON0     | —      | _      | CHS3   | CHS2   | CHS1                    | CHS0    | GO/DONE | ADON    | 00 0000              | 00 0000                         |

| ANSELB     | —      | _      | ANSB5  | ANSB4  | ANSB3                   | ANSB2   | ANSB1   | ANSB0   | 11 1111              | 11 1111                         |

| APFCON     | —      | _      | _      | —      | —                       | _       | SSSEL   | CCP2SEL | 00                   | 00                              |

| CCP2CON    | —      | _      | DC2B1  | DC2B0  | CCP2M3                  | CCP2M2  | CCP2M1  | CCP2M0  | 00 0000              | 00 0000                         |

| CPSCON0    | CPSON  | _      | _      | —      | CPSRNG1                 | CPSRNG0 | CPSOUT  | TOXCS   | 0 0000               | 0 0000                          |

| CPSCON1    | —      | _      | _      | —      | CPSCH3                  | CPSCH2  | CPSCH1  | CPSCH0  | 0000                 | 0000                            |

| INTCON     | GIE    | PEIE   | T0IE   | INTE   | RBIE                    | T0IF    | INTF    | RBIF    | 0000 000x            | 0000 000x                       |

| IOCB       | IOCB7  | IOCB6  | IOCB5  | IOCB4  | IOCB3                   | IOCB2   | IOCB1   | IOCB0   | 0000 0000            | 0000 0000                       |

| OPTION_REG | RBPU   | INTEDG | TOCS   | TOSE   | PSA                     | PS2     | PS1     | PS0     | 1111 1111            | 1111 1111                       |

| PORTB      | RB7    | RB6    | RB5    | RB4    | RB3                     | RB2     | RB1     | RB0     | XXXX XXXX            | XXXX XXXX                       |

| T1GCON     | TMR1GE | T1GPOL | T1GTM  | T1GSPM | T <u>1GGO</u> /<br>DONE | T1GVAL  | T1GSS1  | T1GSS0  | 0000 0x00            | uuuu uxuu                       |

| TRISB      | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3                  | TRISB2  | TRISB1  | TRISB0  | 1111 1111            | 1111 1111                       |

| WPUB       | WPUB7  | WPUB6  | WPUB5  | WPUB4  | WPUB3                   | WPUB2   | WPUB1   | WPUB0   | 1111 1111            | 1111 1111                       |

TABLE 6-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

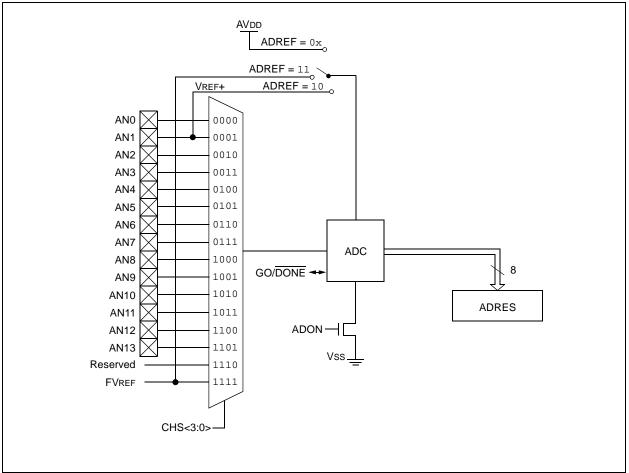

### 9.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 8-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 8-bit binary result via successive approximation and stores the conversion result into the ADC result register (ADRES). Figure 9-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

#### FIGURE 9-1: ADC BLOCK DIAGRAM

| REGISTER      | <b>19-2.</b> ADCO              |                        | ITROL REG        |                    |                    |                  |        |

|---------------|--------------------------------|------------------------|------------------|--------------------|--------------------|------------------|--------|

| U-0           | R/W-0                          | R/W-0                  | R/W-0            | U-0                | U-0                | R/W-0            | R/W-0  |

| _             | ADCS2                          | ADCS1                  | ADCS0            | _                  | _                  | ADREF1           | ADREF0 |

| bit 7         |                                |                        |                  |                    |                    |                  | bit 0  |

| Legend:       |                                |                        |                  |                    |                    |                  |        |

| R = Readabl   | le bit                         | W = Writable bi        | t                | U = Unimpleme      | ented bit, read as | s 'O'            |        |

| -n = Value at | t POR                          | '1' = Bit is set       |                  | '0' = Bit is clear | red                | x = Bit is unkno | wn     |

|               |                                |                        |                  |                    |                    |                  |        |

| bit 7         | Unimplemente                   | ed: Read as '0'        |                  |                    |                    |                  |        |

| bit 6-4       | ADCS<2:0>: A                   | /D Conversion C        | lock Select bits |                    |                    |                  |        |

|               | 000 = Fosc/2                   |                        |                  |                    |                    |                  |        |

|               | 001 = Fosc/8                   |                        |                  |                    |                    |                  |        |

|               | 010 = Fosc/32                  | -                      |                  |                    |                    |                  |        |

|               | · · ·                          | ock supplied from      | a dedicated RC   | Coscillator)       |                    |                  |        |

|               | 100 = Fosc/4<br>101 = Fosc/16  |                        |                  |                    |                    |                  |        |

|               | 101 = FOSC/10<br>110 = FOSC/64 | -                      |                  |                    |                    |                  |        |

|               |                                | ,<br>ock supplied from | a dedicated RC   | coscillator)       |                    |                  |        |

| bit 3-2       | Unimplemente                   | ••                     |                  | ,                  |                    |                  |        |

| bit 1-0       | ADREF<1:0>:                    | Voltage Referend       | e Configuration  | bits               |                    |                  |        |

|               |                                | connected to VDD       | 0                |                    |                    |                  |        |

|               | 10 = VREF is c                 | connected to exte      | rnal VREF (RA3   | /AN3)              |                    |                  |        |

|               |                                |                        | nal Fixed Voltag |                    |                    |                  |        |

#### REGISTER 9-2: ADCON1: A/D CONTROL REGISTER 1

#### REGISTER 9-3: ADRES: ADC RESULT REGISTER

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 | ADRES1 | ADRES0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 **ADRES<7:0>**: ADC Result Register bits 8-bit conversion result.

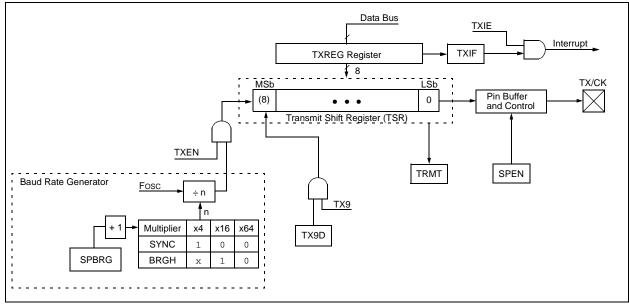

### 16.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (AUSART)

The Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The AUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The AUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- Address detection in 9-bit mode

- Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- · Half-duplex synchronous slave

- Sleep operation

Block diagrams of the AUSART transmitter and receiver are shown in Figure 16-1 and Figure 16-2.

#### FIGURE 16-1: AUSART TRANSMIT BLOCK DIAGRAM

| Name   | Bit 7    | Bit 6       | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|-------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE        | TOIE       | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE  | ADIE        | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF  | ADIF        | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCREG  | AUSART R | eceive Data | a Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN     | RX9         | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7     | BRG6        | BRG5       | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7   | TRISC6      | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC     | TX9         | TXEN       | SYNC   | _      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

#### TABLE 16-2: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Asynchronous Reception.

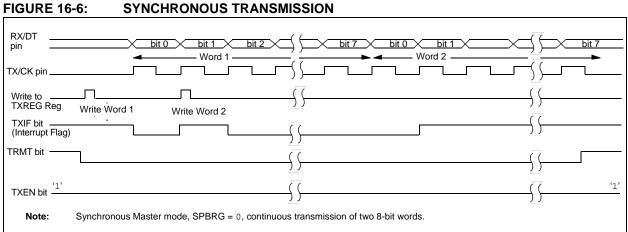

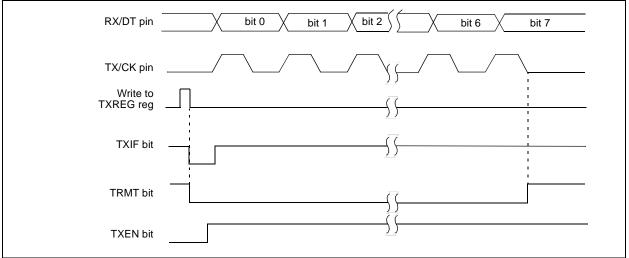

#### FIGURE 16-7: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

#### TABLE 16-6: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name   | Bit 7    | Bit 6       | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|-------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE        | TOIE       | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE  | ADIE        | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF  | ADIF        | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN     | RX9         | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7     | BRG6        | BRG5       | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7   | TRISC6      | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXREG  | AUSART T | ransmit Dat | a Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA  | CSRC     | TX9         | TXEN       | SYNC   |        | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Transmission.

| FIGURE 16-8:                | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                                 |

|-----------------------------|-------------------------------------------------------------------------------------------|

| RX/DT<br>pin                | bit 0         bit 2         bit 3         bit 4         bit 5         bit 6         bit 7 |

| TX/CK pin                   |                                                                                           |

| Write to<br>bit SREN        |                                                                                           |

| SREN bit                    |                                                                                           |

| CREN bit                    | ʻ0'                                                                                       |

| RCIF bit<br>(Interrupt) ——— |                                                                                           |

| Read<br>RCREG               |                                                                                           |

| Note: Timing d              | iagram demonstrates Synchronous Master mode with bit SREN = $1$ and bit BRGH = $0$ .      |

| Name   | Bit 7    | Bit 6       | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|-------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE        | TOIE       | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE  | ADIE        | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF  | ADIF        | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCREG  | AUSART R | eceive Data | a Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN     | RX9         | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| TRISC  | TRISC7   | TRISC6      | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC     | TX9         | TXEN       | SYNC   | _      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

#### TABLE 16-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Reception.

### 16.3.2.3 AUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 16.3.1.4 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never Idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE interrupt enable bit of the PIE1 register is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 16.3.2.4 Synchronous Slave Reception Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 3. If 9-bit reception is desired, set the RX9 bit.

- 4. Verify address detection is disabled by clearing the ADDEN bit of the RCSTA register.

- 5. Set the CREN bit to enable reception.

- The RCIF bit of the PIR1 register will be set when reception is complete. An interrupt will be generated if the RCIE bit of the PIE1 register was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register.

| Name   | Bit 7    | Bit 6       | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|-------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE        | TOIE       | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE  | ADIE        | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF  | ADIF        | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCREG  | AUSART R | eceive Data | a Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN     | RX9         | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000X            | 0000 000X                       |

| TRISC  | TRISC7   | TRISC6      | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC     | TX9         | TXEN       | SYNC   | —      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

#### TABLE 16-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Reception.

#### REGISTER 17-5: SSPMSK: SSP MASK REGISTER

| R/W-1           | R/W-1 | R/W-1                                               | R/W-1                                         | R/W-1 | R/W-1 | R/W-1 | R/W-1 |  |  |  |  |  |

|-----------------|-------|-----------------------------------------------------|-----------------------------------------------|-------|-------|-------|-------|--|--|--|--|--|

| MSK7            | MSK6  | MSK5                                                | MSK4                                          | MSK3  | MSK2  | MSK1  | MSK0  |  |  |  |  |  |

| bit 7           |       |                                                     |                                               |       | -     |       | bit   |  |  |  |  |  |

| Legend:         |       |                                                     |                                               |       |       |       |       |  |  |  |  |  |

| R = Readable    | bit   | W = Writable bit U = Unimplemented bit, read as '0' |                                               |       |       |       |       |  |  |  |  |  |

| -n = Value at F | POR   | '1' = Bit is set                                    | s set '0' = Bit is cleared x = Bit is unknown |       |       |       |       |  |  |  |  |  |

|       | 0 = 110 received address bit instructused to detect i C address match                              |

|-------|----------------------------------------------------------------------------------------------------|

| bit 0 | MSK<0>: Mask bit for I <sup>2</sup> C Slave Mode, 10-bit Address                                   |

|       | I <sup>2</sup> C Slave Mode, 10-bit Address (SSPM<3:0> = 0111):                                    |

|       | 1 = The received address bit '0' is compared to SSPADD<0> to detect I <sup>2</sup> C address match |

|       | $0 =$ The received address bit '0' is not used to detect $1^2$ C address match                     |

|       | All other SSP modes: this bit has no effect.                                                       |

|       |                                                                                                    |

### REGISTER 17-6: SSPADD: SSP I<sup>2</sup>C ADDRESS REGISTER

| R/W-0       | R/W-0 R/W-0 R/W-0 |      | R/W-0 R/W-0 R/W-0 R/W-0 |      | R/W-0 | R/W-0 | R/W-0 |

|-------------|-------------------|------|-------------------------|------|-------|-------|-------|

| ADD7 ADD6 A |                   | ADD5 | ADD4                    | ADD3 | ADD2  | ADD1  | ADD0  |

| bit 7 bit 0 |                   |      |                         |      |       |       |       |

|             |                   |      |                         |      |       |       |       |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | ʻ0'                |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-0 **ADD<7:0>:** Address bits Received address

#### TABLE 17-7: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bit 7                                                                 | Bit 6              | Bit 5                   | Bit 4      | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------|-------------------------|------------|------------|--------|--------|--------|----------------------|---------------------------------|

| INTCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | GIE                                                                   | PEIE               | TOIE                    | INTE       | RBIE       | TOIF   | INTF   | RBIF   | x000 0000x           | 0000 000u                       |

| PIR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TMR1GIF                                                               | ADIF               | RCIF                    | TXIF       | SSPIF      | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TMR1GIE                                                               | ADIE               | RCIE                    | TXIE       | SSPIE      | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| SSPBUF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Synchronous Serial Port Receive Buffer/Transmit Register              |                    |                         |            |            |        |        |        | xxxx xxxx            | uuuu uuuu                       |

| SSPADD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Synchronous                                                           | Serial Por         | t (I <sup>2</sup> C mod | e) Address | s Register |        |        |        | 0000 0000            | 0000 0000                       |

| SSPCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | WCOL                                                                  | SSPOV              | SSPEN                   | CKP        | SSPM3      | SSPM2  | SSPM1  | SSPM0  | 0000 0000            | 0000 0000                       |

| SSPMSK <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Synchronous Serial Port (I <sup>2</sup> C mode) Address Mask Register |                    |                         |            |            |        |        |        | 1111 1111            | 1111 1111                       |

| SSPSTAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SMP <sup>(1)</sup>                                                    | CKE <sup>(1)</sup> | D/A                     | Р          | S          | R/W    | UA     | BF     | 0000 0000            | 0000 0000                       |

| TRISC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TRISC7                                                                | TRISC6             | TRISC5                  | TRISC4     | TRISC3     | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| is a second s |                                                                       |                    |                         |            |            |        |        |        |                      |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in I<sup>2</sup>C mode.

**Note 1:** Maintain these bits clear in  $I^2C$  mode.

**2:** Accessible only when SSPM<3:0> = 1001.

### 18.0 PROGRAM MEMORY READ

The Flash program memory is readable during normal operation over the full VDD range of the device. To read data from Program Memory, five Special Function Registers (SFRs) are used:

- PMCON1

- PMDATL

- PMDATH

- PMADRL

- PMADRH

The value written to the PMADRH:PMADRL register pair determines which program memory location is read. The read operation will be initiated by setting the RD bit of the PMCON1 register. The program memory flash controller takes two instructions to complete the read, causing the second instruction after the setting the RD bit will be ignored. To avoid conflict with program execution, it is recommended that the two instructions following the setting of the RD bit are NOP. When the read completes, the result is placed in the PMDATLH:PMDATL register pair. Refer to Example 18-1 for sample code.

**Note:** Code-protect does not effect the CPU from performing a read operation on the program memory. For more information, refer to **Section 8.2 "Code Protection"**.

|                      | BANKSEL<br>MOVF | PMADRL<br>MS PROG ADDR, | ;                                             |

|----------------------|-----------------|-------------------------|-----------------------------------------------|

|                      | MOVWF           | PMADRH                  | ;MS Byte of Program Address to read           |

|                      | MOVF            | LS PROG ADDR,           |                                               |

|                      | MOVWF           | PMADRL                  | iLS Byte of Program Address to read           |

|                      | BANKSEL         | PMCON1                  | ;                                             |

| be es                | BSF             | PMCON1, RD              | ;Initiate Read                                |

| Required<br>Sequence | NOP             |                         |                                               |

| Rec                  | NOP             |                         | ;Any instructions here are ignored as program |

| <u> </u>             |                 |                         | ;memory is read in second cycle after BSF     |

|                      | BANKSEL         | PMDATL                  | ;                                             |

|                      | MOVF            | PMDATL, W               | ;W = LS Byte of Program Memory Read           |

|                      | MOVWF           | LOWPMBYTE               | ;                                             |

|                      | MOVF            | PMDATH, W               | ;W = MS Byte of Program Memory Read           |

|                      | MOVWF           | HIGHPMBYTE              | ;                                             |

| 1                    |                 |                         |                                               |

#### EXAMPLE 18-1: PROGRAM MEMORY READ

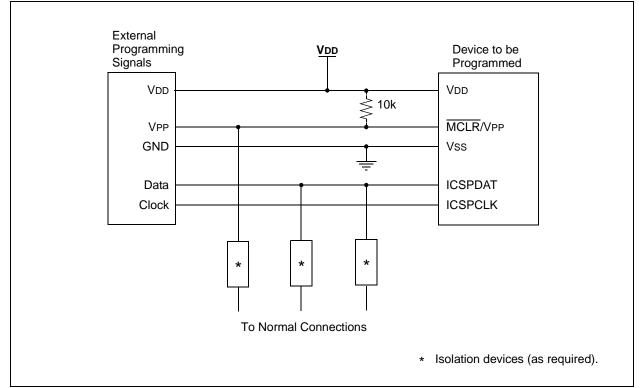

#### 20.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- Vdd

- Vss

The device is placed into Program/Verify mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP from 0v to VPP. In Program/Verify mode the program memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ISCPCLK pin is the clock input. For more information on ICSP, refer to the "*PIC16(L)F72x Memory Programming Specification*" (DS41332).

**Note:** The ICD 2 produces a VPP voltage greater than the maximum VPP specification of the PIC16(L)F722/3/4/6/7. When using this programmer, an external circuit, such as the AC164112 MPLAB ICD 2 VPP voltage limiter, is required to keep the VPP voltage within the device specifications.

#### FIGURE 20-1: TYPICAL CONNECTION FOR ICSP™ PROGRAMMING

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Description:     | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.<br>If the result is '1', the next instruction is executed. If the result is '0', then a NOP is executed instead, making it a 2-cycle instruction. |  |  |  |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a 2-cycle<br>instruction. |  |  |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                       |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                    |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                         |  |  |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                            |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                       |  |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The 11-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>2-cycle instruction. |  |  |  |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                           |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                              |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                   |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                          |  |  |  |  |  |

| Status Affected: | Z                                                                                                                     |  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the 8-bit literal 'k'. The<br>result is placed in the<br>W register. |  |  |  |  |  |

| INCF             | Increment f                                                                                                                                                                |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] INCF f,d                                                                                                                                                           |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                            |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                          |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                                         |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                    |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |  |

#### 23.4 DC Characteristics: PIC16(L)F722/3/4/6/7-I/E (Continued)

|              |                                      |                                           | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |      |       |                                                                         |  |

|--------------|--------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------------------------------------------------------------------------|--|

| Param<br>No. | Sym.                                 | Characteristic                            | Min.                                                                                                                                                                                           | Тур† | Max. | Units | Conditions                                                              |  |

| D130         | Eр                                   | Cell Endurance                            | 100                                                                                                                                                                                            | 1k   | —    | E/W   | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |

| D131         |                                      | VDD for Read                              | Vmin                                                                                                                                                                                           | —    | _    | V     |                                                                         |  |

|              | Voltage on MCLR/VPP<br>Erase/Program |                                           | 8.0                                                                                                                                                                                            | _    | 9.0  | V     | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |

|              |                                      | VDD for Bulk Erase                        | 2.7                                                                                                                                                                                            | 3    | _    | V     | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |

| D132         | VPEW                                 | VDD for Write or Row Erase                | 2.7                                                                                                                                                                                            | _    | —    | V     | VMIN = Minimum operating voltage<br>VMAX = Maximum operating<br>voltage |  |

|              | IPPPGM                               | Current on MCLR/VPP during<br>Erase/Write | —                                                                                                                                                                                              | -    | 5.0  | mA    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |

|              | IDDPGM                               | Current on VDD during Erase/<br>Write     | —                                                                                                                                                                                              |      | 5.0  | mA    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |

| D133         | TPEW                                 | Erase/Write cycle time                    | _                                                                                                                                                                                              |      | 2.8  | ms    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |

| D134         | TRETD                                | Characteristic Retention                  | 40                                                                                                                                                                                             | —    | —    | Year  | Provided no other specifications<br>are violated                        |  |

|              |                                      | VCAP Capacitor Charging                   |                                                                                                                                                                                                | •    |      | •     | •                                                                       |  |

| D135         |                                      | Charging current                          | —                                                                                                                                                                                              | 200  | _    | μΑ    |                                                                         |  |

| D135A        |                                      |                                           | —                                                                                                                                                                                              | 0.0  | —    | mA    |                                                                         |  |

Legend: TBD = To Be Determined

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

**3:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: Including OSC2 in CLKOUT mode.

#### © 2007-2015 Microchip Technology Inc.

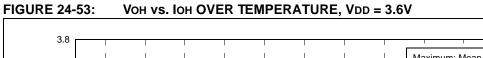

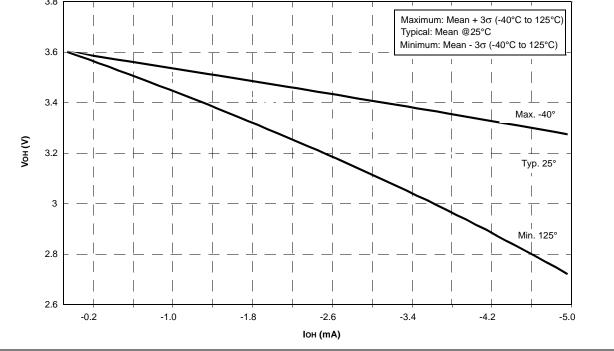

FIGURE 24-54: VOH vs. IOH OVER TEMPERATURE, VDD = 1.8V