#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Dectano                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I²C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 25                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 11x8b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f726-e-sp |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

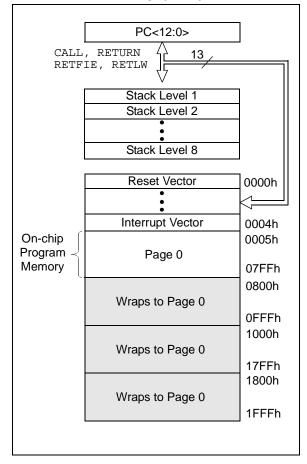

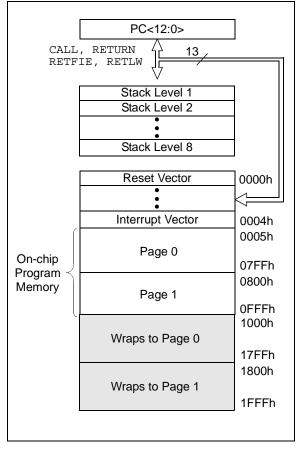

# 2.0 MEMORY ORGANIZATION

# 2.1 Program Memory Organization

The PIC16(L)F722/3/4/6/7 has a 13-bit program counter capable of addressing a 2K x 14 program memory space for the PIC16F722/LF722 (0000h-07FFh), a 4K x 14 program memory space for PIC16F723/LF723 and PIC16F724/LF724 the (0000h-0FFFh) and an 8K x 14 program memory space for the PIC16F726/LF726 and PIC16F727/LF727 (0000h-1FFFh). Accessing a location above the memory boundaries for the PIC16F722/LF722 will cause a wrap-around within the first 2K x 14 program memory space. Accessing a location above the memory boundaries for the PIC16F723/LF723 and PIC16F724/LF724 will cause a wrap-around within the first 4K x 14 program memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16F722/LF722

### FIGURE 2-2:

# PROGRAM MEMORY MAP AND STACK FOR THE PIC16F723/LF723 AND PIC16F724/LF724

#### EXAMPLE 4-1: SAVING W, STATUS AND PCLATH REGISTERS IN RAM

| MOVWF<br>SWAPF          | W_TEMP<br>STATUS,W                                      | ;Copy W to W_TEMP register<br>;Swap status to be saved into W<br>;Swaps are used because they do not affect the status bits                           |

|-------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVWF<br>MOVF           | STATUS_TEMP<br>STATUS_TEMP<br>PCLATH,W<br>PCLATH_TEMP   | ;Select regardless of current bank<br>;Copy status to bank zero STATUS_TEMP register<br>;Copy PCLATH to W register<br>;Copy W register to PCLATH_TEMP |

| :(ISR)<br>:             |                                                         | ;Insert user code here                                                                                                                                |

| MOVF                    | STATUS_TEMP<br>PCLATH_TEMP,W<br>PCLATH<br>STATUS_TEMP,W | ;Select regardless of current bank<br>;<br>;Restore PCLATH<br>;Swap STATUS_TEMP register into W<br>;(sets bank to original state)                     |

| MOVWF<br>SWAPF<br>SWAPF | STATUS<br>W_TEMP,F<br>W_TEMP,W                          | ;Move W into STATUS register<br>;Swap W_TEMP<br>;Swap W_TEMP into W                                                                                   |

### 4.5.1 INTCON REGISTER

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, PORTB change and external RB0/INT/SEG0 pin interrupts.

```

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

```

# REGISTER 6-5: PORTB: PORTB REGISTER

| R/W-x                              | R/W-x | R/W-x                                   | R/W-x | R/W-x                              | R/W-x | R/W-x | R/W-x |  |

|------------------------------------|-------|-----------------------------------------|-------|------------------------------------|-------|-------|-------|--|

| RB7                                | RB6   | RB5                                     | RB4   | RB3                                | RB2   | RB1   | RB0   |  |

| bit 7                              |       |                                         |       |                                    |       |       | bit 0 |  |

|                                    |       |                                         |       |                                    |       |       |       |  |

| Legend:                            |       |                                         |       |                                    |       |       |       |  |

| R = Readable bit W = Writable bit  |       |                                         | bit   | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at POR (1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |                                    |       |       |       |  |

bit 7-0 **RB<7:0>**: PORTB I/O Pin bit 1 = Port pin is > VIH 0 = Port pin is < VIL

# REGISTER 6-6: TRISB: PORTB TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 7-0 TRISB<7:0>: PORTB Tri-State Control bit

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

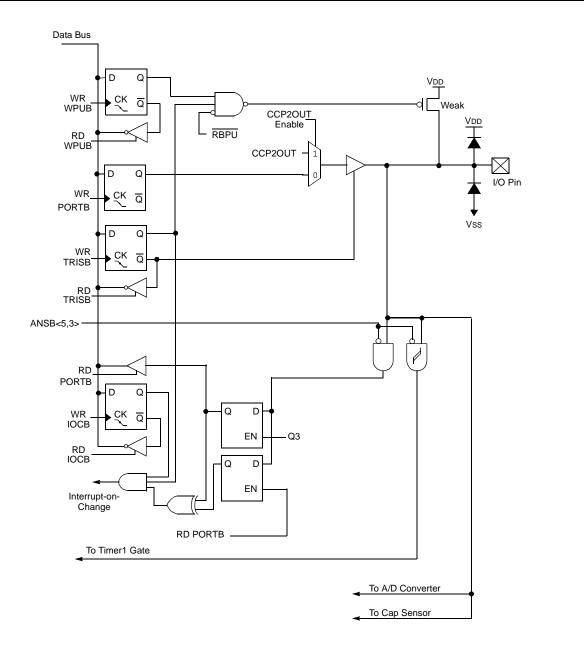

# FIGURE 6-10: BLOCK DIAGRAM OF RB5

# 6.5 **PORTD and TRISD Registers**

PORTD is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISD (Register 6-13). Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 6-4 shows how to initialize PORTD.

Reading the PORTD register (Register 6-12) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

Note: PORTD is available on PIC16F724/LF724 and PIC16F727/LF727 only.

The TRISD register (Register 6-13) controls the PORTD pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISD register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### EXAMPLE 6-4: INITIALIZING PORTD

| BANKSEL | PORTD       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTD       | ;Init PORTD            |

| BANKSEL | ANSELD      |                        |

| CLRF    | ANSELD      | ;Make PORTD digital    |

| BANKSEL | TRISD       | ;                      |

| MOVLW   | B`00001100′ | ;Set RD<3:2> as inputs |

| MOVWF   | TRISD       | ;and set RD<7:4,1:0>   |

|         |             | ;as outputs            |

|         |             |                        |

#### 6.5.1 ANSELD REGISTER

The ANSELD register (Register 6-9) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELD bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELD bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELD register must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

# **REGISTER 6-12: PORTD: PORTD REGISTER<sup>(1)</sup>**

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RD7   | RD6   | RD5   | RD4   | RD3   | RD2   | RD1   | RD0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 7-0 RD<7:0>: PORTD General Purpose I/O Pin bits

1 = Port pin is > VIH

0 = Port pin is < VIL

Note 1: PORTD is not implemented on PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'.

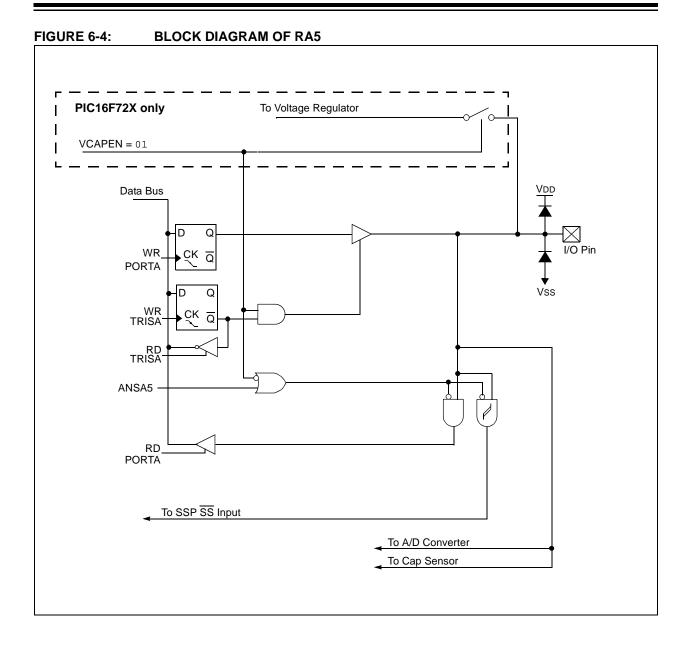

# 6.6.1 RE0/AN5<sup>(1)</sup>

Figure 6-22 shows the diagram for this pin. This pin is configurable to function as one of the following:

• a general purpose I/O

• an analog input for the ADC

| Note 1: | RE0/AN5 is available on |

|---------|-------------------------|

|         | PIC16F724/LF724 and     |

|         | PIC16F727/LF727 only.   |

# 6.6.2 RE1/AN6<sup>(1)</sup>

Figure 6-22 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

| Note 1: | RE0/AN5 is available on |

|---------|-------------------------|

|         | PIC16F724/LF724 and     |

|         | PIC16F727/LF727 only.   |

### 6.6.3 RE2/AN7<sup>(1)</sup>

Figure 6-22 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

Note 1: RE0/AN5 is available on PIC16F724/LF724 and PIC16F727/LF727 only.

#### 6.6.4 RE3/MCLR/VPP

Figure 6-23 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose input

- as Master Clear Reset with weak pull-up

- · a programming voltage reference input

# 8.0 DEVICE CONFIGURATION

Device Configuration consists of Configuration Word 1 and Configuration Word 2 registers, Code Protection and Device ID.

# 8.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 register at 2007h and Configuration Word 2 register at 2008h. These registers are only accessible during programming.

#### REGISTER 8-1: CONFIG1: CONFIGURATION WORD REGISTER 1

|        |   | R/P-1 | R/P-1 | U-1 <sup>(4)</sup> | R/P-1 | R/P-1  | R/P-1  |

|--------|---|-------|-------|--------------------|-------|--------|--------|

| —      | _ | DEBUG | PLLEN | _                  | BORV  | BOREN1 | BOREN0 |

| bit 15 |   |       |       |                    |       |        | bit 8  |

| U-1 <sup>(4)</sup> | R/P-1 |

|--------------------|-------|-------|-------|-------|-------|-------|-------|

| _                  | CP    | MCLRE | PWRTE | WDTE  | FOSC2 | FOSC1 | FOSC0 |

| bit 7              |       |       |       |       |       |       | bit 0 |

| Legend:           | P = Programmable bit |                             |                    |  |  |

|-------------------|----------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read | l as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared        | x = Bit is unknown |  |  |

| bit 13              | <b>DEBUG:</b> In-Circuit Debugger Mode bit<br>1 = In-Circuit Debugger disabled, RB6/ICSPCLK and RB7/ICSPDAT are general purpose I/O pins<br>0 = In-Circuit Debugger enabled, RB6/ICSPCLK and RB7/ICSPDAT are dedicated to the debugger                            |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bit 12              | PLLEN: INTOSC PLL Enable bit<br>0 = INTOSC Frequency is 500 kHz<br>1 = INTOSC Frequency is 16 MHz (32x)                                                                                                                                                           |  |

| bit 11              | Unimplemented: Read as '1'                                                                                                                                                                                                                                        |  |

| bit 10              | <b>BORV:</b> Brown-out Reset Voltage selection bit<br>0 = Brown-out Reset Voltage (VBOR) set to 2.5 V nominal<br>1 = Brown-out Reset Voltage (VBOR) set to 1.9 V nominal                                                                                          |  |

| bit 9-8             | <b>BOREN&lt;1:0&gt;:</b> Brown-out Reset Selection bits <sup>(1)</sup><br>0x = BOR disabled (Preconditioned State)<br>10 = BOR enabled during operation and disabled in Sleep<br>11 = BOR enabled                                                                 |  |

| bit 7               | Unimplemented: Read as '1'                                                                                                                                                                                                                                        |  |

| bit 6               | <b>CP</b> : Code Protection bit <sup>(2)</sup><br>1 = Program memory code protection is disabled<br>0 = Program memory code protection is enabled                                                                                                                 |  |

| bit 5               | MCLRE: <u>RE3/MCLR</u> pin function select bit <sup>(3)</sup><br>1 = RE3/ <u>MCLR</u> pin function is MCLR<br>0 = RE3/MCLR pin function is digital input, MCLR internally tied to VDD                                                                             |  |

| Note 1:<br>2:<br>3: | Enabling Brown-out Reset does not automatically enable Power-up Timer.<br>The entire program memory will be erased when the code protection is turned off.<br>When $\overline{MCLR}$ is asserted in INTOSC or RC mode, the internal clock oscillator is disabled. |  |

**4:** MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

# 9.1 ADC Configuration

When configuring and using the ADC, the following functions must be considered:

- Port configuration

- Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- Interrupt control

- Results formatting

# 9.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 6.0 "I/O Ports"** for more information.

**Note:** Analog voltages on any pin that is defined as a digital input may cause the input buffer to conduct excess current.

# 9.1.2 CHANNEL SELECTION

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 9.2 "ADC Operation"** for more information.

# 9.1.3 ADC VOLTAGE REFERENCE

The ADREF bits of the ADCON1 register provides control of the positive voltage reference. The positive voltage reference can be either VDD, an external voltage source or the internal Fixed Voltage Reference. The negative voltage reference is always connected to the ground reference. See **Section 10.0** "**Fixed Voltage Reference**" for more details on the Fixed Voltage Reference.

# 9.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal oscillator)

The time to complete one bit conversion is defined as TAD. One full 8-bit conversion requires 10 TAD periods as shown in Figure 9-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the A/D conversion requirements in **Section 23.0** "**Electrical Specifications**" for more information. Table 9-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

| R/W-0                                                                                                                                                                                 | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                | U-0              | U-0 | R/W-0            | R/W-0            | R-0             | R/W-0 |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|------------------|------------------|-----------------|-------|--|

| CPSON                                                                                                                                                                                 | —                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                | _   | CPSRNG1          | CPSRNG0          | CPSOUT          | TOXCS |  |

| bit 7                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |     |                  |                  |                 | bit 0 |  |

|                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |     |                  |                  |                 |       |  |

| Legend:                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |     |                  |                  |                 |       |  |

| R = Readable I                                                                                                                                                                        | bit                                                                                                                                                                                                                                                                                                                                                                                                                                | W = Writable I   | oit | U = Unimpler     | nented bit, read | l as '0'        |       |  |

| -n = Value at P                                                                                                                                                                       | OR                                                                                                                                                                                                                                                                                                                                                                                                                                 | '1' = Bit is set |     | '0' = Bit is cle | ared             | x = Bit is unkn | own   |  |

| bit 7 <b>CPSON:</b> Capacitive Sensing Module Enable bit<br>1 = Capacitive sensing module is operating<br>0 = Capacitive sensing module is shut off and consumes no operating current |                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |     |                  |                  |                 |       |  |

| bit 6-4                                                                                                                                                                               | Unimplement                                                                                                                                                                                                                                                                                                                                                                                                                        | ted: Read as 'd  | )'  |                  |                  |                 |       |  |

| bit 3-2                                                                                                                                                                               | •                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |     |                  |                  |                 |       |  |

| bit 1                                                                                                                                                                                 | <b>CPSOUT:</b> Capacitive Sensing Oscillator Status bit<br>1 = Oscillator is sourcing current (Current flowing out the pin)<br>0 = Oscillator is sinking current (Current flowing into the pin)                                                                                                                                                                                                                                    |                  |     |                  |                  |                 |       |  |

| bit 0                                                                                                                                                                                 | <b>TOXCS:</b> Timer0 External Clock Source Select bit<br>$\frac{\text{If TOCS} = 1}{\text{The TOXCS}}$ The TOXCS bit controls which clock external to the core/Timer0 module supplies Timer0:<br>1 = Timer0 Clock Source is the capacitive sensing oscillator<br>0 = Timer0 Clock Source is the TOCKI pin<br>$\frac{\text{If TOCS} = 0}{\text{Timer0}}$ Timer0 clock source is controlled by the core/Timer0 module and is Fosc/4. |                  |     |                  |                  |                 |       |  |

# REGISTER 14-1: CPSCON0: CAPACITIVE SENSING CONTROL REGISTER 0

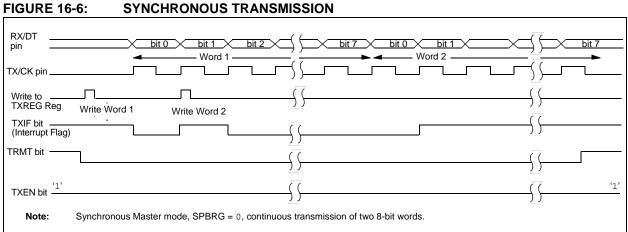

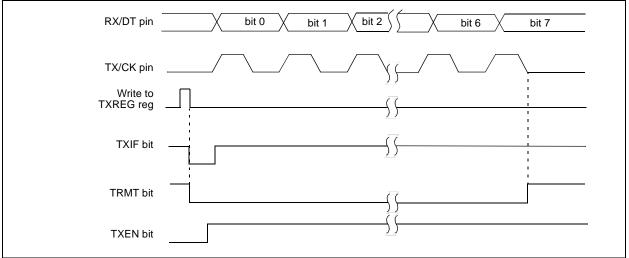

# FIGURE 16-7: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

### TABLE 16-6: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name   | Bit 7    | Bit 6                         | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|-------------------------------|--------|--------|--------|--------|--------|-----------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE                          | TOIE   | INTE   | RBIE   | T0IF   | INTF   | RBIF      | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE  | ADIE                          | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE    | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF  | ADIF                          | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF    | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN     | RX9                           | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D      | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7     | BRG6                          | BRG5   | BRG4   | BRG3   | BRG2   | BRG1   | BRG0      | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7   | TRISC6                        | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0    | 1111 1111            | 1111 1111                       |

| TXREG  | AUSART T | AUSART Transmit Data Register |        |        |        |        |        | 0000 0000 | 0000 0000            |                                 |

| TXSTA  | CSRC     | TX9                           | TXEN   | SYNC   |        | BRGH   | TRMT   | TX9D      | 0000 -010            | 0000 -010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Transmission.

# 18.0 PROGRAM MEMORY READ

The Flash program memory is readable during normal operation over the full VDD range of the device. To read data from Program Memory, five Special Function Registers (SFRs) are used:

- PMCON1

- PMDATL

- PMDATH

- PMADRL

- PMADRH

The value written to the PMADRH:PMADRL register pair determines which program memory location is read. The read operation will be initiated by setting the RD bit of the PMCON1 register. The program memory flash controller takes two instructions to complete the read, causing the second instruction after the setting the RD bit will be ignored. To avoid conflict with program execution, it is recommended that the two instructions following the setting of the RD bit are NOP. When the read completes, the result is placed in the PMDATLH:PMDATL register pair. Refer to Example 18-1 for sample code.

**Note:** Code-protect does not effect the CPU from performing a read operation on the program memory. For more information, refer to **Section 8.2 "Code Protection"**.

|                      | BANKSEL<br>MOVF | PMADRL<br>MS PROG ADDR, | ;                                             |

|----------------------|-----------------|-------------------------|-----------------------------------------------|

|                      | MOVWF           | PMADRH                  | ;MS Byte of Program Address to read           |

|                      | MOVF            | LS PROG ADDR,           |                                               |

|                      | MOVWF           | PMADRL                  | iLS Byte of Program Address to read           |

|                      | BANKSEL         | PMCON1                  | ;                                             |

| be es                | BSF             | PMCON1, RD              | ;Initiate Read                                |

| Required<br>Sequence | NOP             |                         |                                               |

| Rec                  | NOP             |                         | ;Any instructions here are ignored as program |

| <u> </u>             |                 |                         | ;memory is read in second cycle after BSF     |

|                      | BANKSEL         | PMDATL                  | ;                                             |

|                      | MOVF            | PMDATL, W               | ;W = LS Byte of Program Memory Read           |

|                      | MOVWF           | LOWPMBYTE               | ;                                             |

|                      | MOVF            | PMDATH, W               | ;W = MS Byte of Program Memory Read           |

|                      | MOVWF           | HIGHPMBYTE              | ;                                             |

| 1                    |                 |                         |                                               |

### EXAMPLE 18-1: PROGRAM MEMORY READ

# REGISTER 18-4: PMADRH: PROGRAM MEMORY ADDRESS HIGH REGISTER

| U-0   | U-0      | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|----------|-----|-------|-------|-------|-------|-------|

| —     | — — PMA1 |     | PMA12 | PMA11 | PMA10 | PMA9  | PMA8  |

| bit 7 |          |     |       |       |       |       | bit 0 |

| Legend:   |           |                  |                             |                    |

|-----------|-----------|------------------|-----------------------------|--------------------|

| R = Rea   | dable bit | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Valu | e at POR  | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 PMA<12:8>: Program Memory Read Address bits

#### REGISTER 18-5: PMADRL: PROGRAM MEMORY ADDRESS LOW REGISTER

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PMA7  | PMA6  | PMA5  | PMA4  | PMA3  | PMA2  | PMA1  | PMA0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0 PMA<7:0>: Program Memory Read Address bits

#### TABLE 18-1: SUMMARY OF REGISTERS ASSOCIATED WITH PROGRAM MEMORY READ

| Name   | Bit 7     | Bit 6                                                             | Bit 5 | Bit 4                                          | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on all other Resets |

|--------|-----------|-------------------------------------------------------------------|-------|------------------------------------------------|-------|-------|-------|-------|----------------------|---------------------------|

| PMCON1 | Reserved  | _                                                                 | _     | —                                              | —     | —     | -     | RD    | 1 0                  | 10                        |

| PMADRH | —         | _                                                                 | —     | Program Memory Read Address Register High Byte |       |       |       |       | x xxxx               | x xxxx                    |

| PMADRL | Program M | Program Memory Read Address Register Low Byte xxxx xxxx xxxx xxxx |       |                                                |       |       |       |       |                      | XXXX XXXX                 |

| PMDATH | —         | — Program Memory Read Data Register High Byte                     |       |                                                |       |       |       |       | xx xxxx              | xx xxxx                   |

| PMDATL | Program M | Program Memory Read Data Register Low Byte                        |       |                                                |       |       |       |       | xxxx xxxx            | xxxx xxxx                 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Program Memory Read.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                  |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                                                                                                             |

| Description:     | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.<br>If the result is '1', the next instruction is executed. If the result is '0', then a NOP is executed instead, making it a 2-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                     |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                          |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a 2-cycle<br>instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                       |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                    |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                       |  |  |  |  |  |

| Operation:       | $k \rightarrow PC < 10:0>$<br>PCLATH<4:3> $\rightarrow PC < 12:11>$                                                                                                                        |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                       |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The 11-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>2-cycle instruction. |  |  |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                           |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                              |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                   |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                          |  |  |  |  |  |

| Status Affected: | Z                                                                                                                     |  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the 8-bit literal 'k'. The<br>result is placed in the<br>W register. |  |  |  |  |  |

| INCF             | Increment f                                                                                                                                                                |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] INCF f,d                                                                                                                                                           |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                            |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                          |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                                         |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                    |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |  |

| PIC16LF722/3/4/6/7 |        |                                                        | $ \begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array} $ |      |                          |                  |                                                                                                                                                                                                                                                              |  |

|--------------------|--------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PIC16F722/3/4/6/7  |        |                                                        | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                        |      |                          |                  |                                                                                                                                                                                                                                                              |  |

| Param.<br>No.      | Sym.   | Characteristic                                         | Min.                                                                                                                                                                                                                                                        | Тур† | Max.                     | Units            | Conditions                                                                                                                                                                                                                                                   |  |

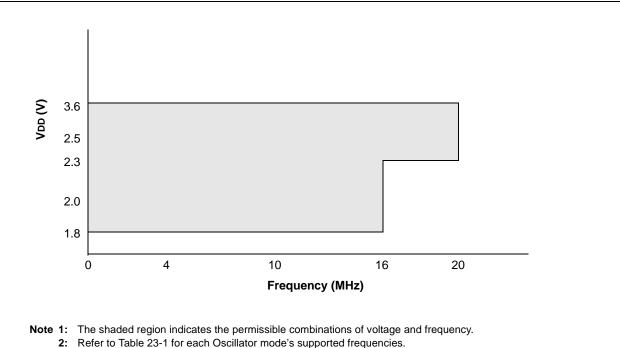

| D001               | Vdd    | Supply Voltage                                         |                                                                                                                                                                                                                                                             |      |                          |                  |                                                                                                                                                                                                                                                              |  |

|                    |        | PIC16LF722/3/4/6/7                                     | 1.8<br>1.8<br>2.3<br>2.5                                                                                                                                                                                                                                    |      | 3.6<br>3.6<br>3.6<br>3.6 | V<br>V<br>V<br>V | Fosc $\leq$ 16 MHz: HFINTOSC, EC<br>Fosc $\leq$ 4 MHz<br>Fosc $\leq$ 20 MHz, EC<br>Fosc $\leq$ 20 MHz, HS                                                                                                                                                    |  |

| D001               |        | PIC16F722/3/4/6/7                                      | 1.8<br>1.8<br>2.3<br>2.5                                                                                                                                                                                                                                    |      | 5.5<br>5.5<br>5.5<br>5.5 | V<br>V<br>V<br>V | Fosc $\leq$ 16 MHz: HFINTOSC, EC<br>Fosc $\leq$ 4 MHz<br>Fosc $\leq$ 20 MHz, EC<br>Fosc $\leq$ 20 MHz, HS                                                                                                                                                    |  |

| D002*              | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>              |                                                                                                                                                                                                                                                             |      |                          |                  |                                                                                                                                                                                                                                                              |  |

|                    |        | PIC16LF722/3/4/6/7                                     | 1.5                                                                                                                                                                                                                                                         |      | _                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |

| D002*              |        | PIC16F722/3/4/6/7                                      | 1.7                                                                                                                                                                                                                                                         | _    | _                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |

|                    | VPOR*  | Power-on Reset Release Voltage                         | _                                                                                                                                                                                                                                                           | 1.6  | _                        | V                |                                                                                                                                                                                                                                                              |  |

|                    | VPORR* | Power-on Reset Rearm Voltage                           |                                                                                                                                                                                                                                                             |      |                          |                  |                                                                                                                                                                                                                                                              |  |

|                    |        | PIC16LF722/3/4/6/7                                     | _                                                                                                                                                                                                                                                           | 0.8  | _                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |

|                    |        | PIC16F722/3/4/6/7                                      |                                                                                                                                                                                                                                                             | 1.7  | —                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |

| D003               | Vfvr   | Fixed Voltage Reference Voltage,<br>Initial Accuracy   | -8<br>-8<br>-8                                                                                                                                                                                                                                              | <br> | 6<br>6<br>6              | %<br>%<br>%      | $ \begin{array}{l} {\sf VFVR} = 1.024{\sf V},  {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 2.048{\sf V},  {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 4.096{\sf V},  {\sf VDD} \geq 4.75{\sf V}; \\ {\sf -40} \leq {\sf TA} \leq 85^{\circ}{\sf C} \end{array} $ |  |

|                    |        |                                                        | -8<br>-8<br>-8                                                                                                                                                                                                                                              |      | 6<br>6<br>6              | %<br>%<br>%      | $ \begin{array}{l} V{\sf FVR} = 1.024V, \ V{\sf DD} \geq 2.5V \\ V{\sf FVR} = 2.048V, \ V{\sf DD} \geq 2.5V \\ V{\sf FVR} = 4.096V, \ V{\sf DD} \geq 4.75V; \\ -40 \leq {\sf TA} \leq 125^{\circ}{\sf C} \end{array} $                                       |  |

| D004*              | SVDD   | VDD Rise Rate to ensure internal Power-on Reset signal | 0.05                                                                                                                                                                                                                                                        | —    | —                        | V/ms             | See Section 3.2 "Power-on Reset (POR)" for details.                                                                                                                                                                                                          |  |

# 23.1 DC Characteristics: PIC16(L)F722/3/4/6/7-I/E (Industrial, Extended)

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

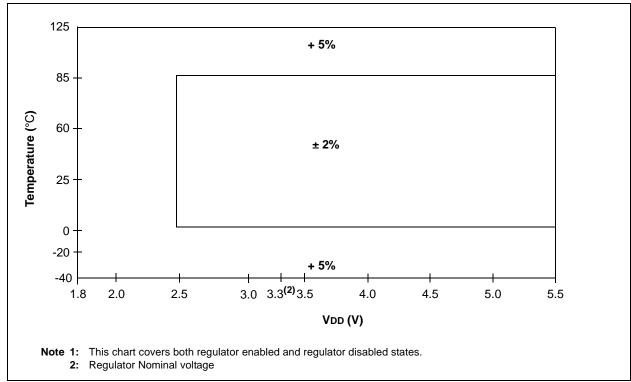

FIGURE 23-6: HFINTOSC FREQUENCY ACCURACY OVER DEVICE VDD AND TEMPERATURE

# 25.2 Package Details

The following sections give the technical details of the packages.

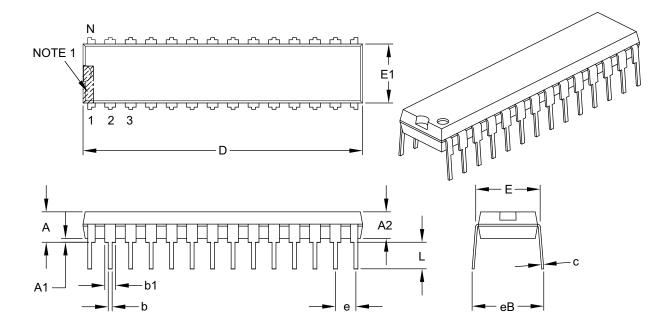

# 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |          |       | INCHES |  |  |  |

|----------------------------|------------------|----------|-------|--------|--|--|--|

|                            | Dimension Limits | MIN      | NOM   | MAX    |  |  |  |

| Number of Pins             | N                |          | 28    |        |  |  |  |

| Pitch                      | е                | .100 BSC |       |        |  |  |  |

| Top to Seating Plane       | А                | -        | -     | .200   |  |  |  |

| Molded Package Thickness   | A2               | .120     | .135  | .150   |  |  |  |

| Base to Seating Plane      | A1               | .015     | -     | -      |  |  |  |

| Shoulder to Shoulder Width | E                | .290     | .310  | .335   |  |  |  |

| Molded Package Width       | E1               | .240     | .285  | .295   |  |  |  |

| Overall Length             | D                | 1.345    | 1.365 | 1.400  |  |  |  |

| Tip to Seating Plane       | L                | .110     | .130  | .150   |  |  |  |

| Lead Thickness             | С                | .008     | .010  | .015   |  |  |  |

| Upper Lead Width           | b1               | .040     | .050  | .070   |  |  |  |

| Lower Lead Width           | b                | .014     | .018  | .022   |  |  |  |

| Overall Row Spacing §      | eB               | -        | -     | .430   |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

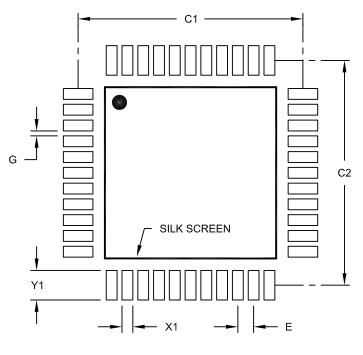

# 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**RECOMMENDED LAND PATTERN**

| Units                    |    | MILLIM | -        |      |

|--------------------------|----|--------|----------|------|

| Dimension Limits         |    | MIN    | NOM      | MAX  |

| Contact Pitch            | E  |        | 0.80 BSC |      |

| Contact Pad Spacing      | C1 |        | 11.40    |      |

| Contact Pad Spacing      | C2 |        | 11.40    |      |

| Contact Pad Width (X44)  | X1 |        |          | 0.55 |

| Contact Pad Length (X44) | Y1 |        |          | 1.50 |

| Distance Between Pads    | G  | 0.25   |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076A