Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 25                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 11x8b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f726-i-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     |                                  | 726)                   |          |            |             |                     |        |                   |           | _       |                                 |

|-----|----------------------------------|------------------------|----------|------------|-------------|---------------------|--------|-------------------|-----------|---------|---------------------------------|

| I/O | 28-Pin<br>PDIP,<br>SOIC,<br>SSOP | 28-Pin<br>QFN,<br>UQFN | A/D      | Cap Sensor | Timers      | ССР                 | AUSART | SSP               | Interrupt | Pull-Up | Basic                           |

| RA0 | 2                                | 27                     | AN0      | _          | _           | _                   | _      | SS <sup>(3)</sup> | _         |         | VCAP <sup>(4)</sup>             |

| RA1 | 3                                | 28                     | AN1      |            |             | _                   |        | —                 |           | —       | —                               |

| RA2 | 4                                | 1                      | AN2      |            |             | _                   | —      | _                 |           | _       | -                               |

| RA3 | 5                                | 2                      | AN3/VREF |            |             | _                   | _      | _                 |           | _       | _                               |

| RA4 | 6                                | 3                      | _        | CPS6       | TOCKI       |                     | _      | _                 | _         | _       | —                               |

| RA5 | 7                                | 4                      | AN4      | CPS7       | _           |                     | _      | SS <sup>(3)</sup> | _         | _       | VCAP <sup>(4)</sup>             |

| RA6 | 10                               | 7                      |          |            |             | _                   | —      | —                 |           | —       | OSC2/CLKOUT/VCAP <sup>(4)</sup> |

| RA7 | 9                                | 6                      |          |            |             | _                   |        | —                 |           | —       | OSC1/CLKIN                      |

| RB0 | 21                               | 18                     | AN12     | CPS0       |             | _                   | —      | _                 | IOC/INT   | Y       | -                               |

| RB1 | 22                               | 19                     | AN10     | CPS1       |             | _                   | _      | —                 | IOC       | Y       | —                               |

| RB2 | 23                               | 20                     | AN8      | CPS2       |             | _                   | —      |                   | IOC       | Y       | —                               |

| RB3 | 24                               | 21                     | AN9      | CPS3       |             | CCP2 <sup>(2)</sup> | _      | -                 | IOC       | Y       | —                               |

| RB4 | 25                               | 22                     | AN11     | CPS4       | _           | —                   | —      | —                 | IOC       | Y       | —                               |

| RB5 | 26                               | 23                     | AN13     | CPS5       | T1G         | _                   | _      | _                 | IOC       | Y       | —                               |

| RB6 | 27                               | 24                     | -        | -          | _           | —                   | —      | —                 | IOC       | Y       | ICSPCLK/ICDCLK                  |

| RB7 | 28                               | 25                     | -        | -          | _           | _                   | _      | _                 | IOC       | Y       | ICSPDAT/ICDDAT                  |

| RC0 | 11                               | 8                      | -        | -          | T1OSO/T1CKI | —                   | —      | —                 | -         | _       | —                               |

| RC1 | 12                               | 9                      |          |            | T1OSI       | CCP2 <sup>(2)</sup> | _      | -                 |           | _       | —                               |

| RC2 | 13                               | 10                     | -        | -          | _           | CCP1                | —      | —                 | -         | _       | —                               |

| RC3 | 14                               | 11                     | -        | -          | _           | _                   | _      | SCK/SCL           | -         | _       | —                               |

| RC4 | 15                               | 12                     | -        | -          |             | —                   | —      | SDI/SDA           | -         | _       | —                               |

| RC5 | 16                               | 13                     |          | -          | -           | _                   | _      | SDO               |           | _       | —                               |

| RC6 | 17                               | 14                     |          |            | -           | _                   | TX/CK  | _                 |           | _       | —                               |

| RC7 | 18                               | 15                     | _        | _          | _           | —                   | RX/DT  | —                 | _         | —       | —                               |

| RE3 | 1                                | 26                     | _        | _          | _           | —                   | _      | —                 | —         | Y(1)    | MCLR/Vpp                        |

| _   | 20                               | 17                     |          | -          | -           | _                   | _      | _                 |           | _       | Vdd                             |

|     | 8,19                             | 5,16                   | _        |            | _           | —                   | _      | —                 | _         | —       | Vss                             |

# TABLE 1:28-PIN PDIP/SOIC/SSOP/QFN/UQFN SUMMARY (PIC16F722/723/726/PIC16LF722/723/726)

**Note 1:** Pull-up enabled only with external MCLR Configuration.

2: RC1 is the default pin location for CCP2. RB3 may be selected by changing the CCP2SEL bit in the APFCON register.

3: RA5 is the default pin location for SS. RA0 may be selected by changing the SSSEL bit in the APFCON register.

4: PIC16F724/727/PIC16LF724/727 devices only.

Note: The PIC16F722/3/4/6/7 devices have an internal low dropout voltage regulator. An external capacitor must be connected to one of the available VCAP pins to stabilize the regulator. For more information, see Section 5.0 "Low Dropout (LDO) Voltage Regulator". The PIC16LF722/3/4/6/7 devices do not have the voltage regulator and therefore no external capacitor is required.

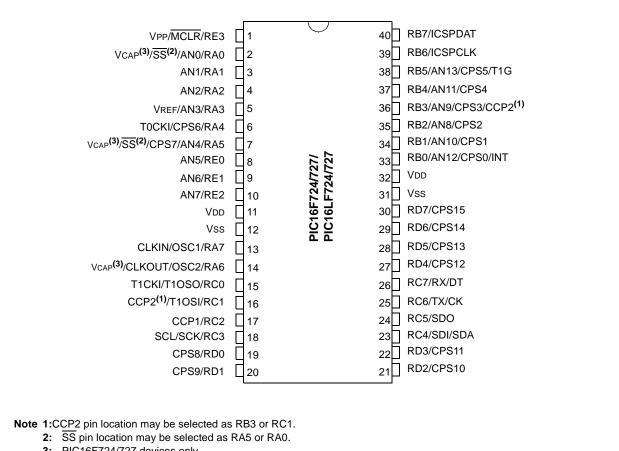

#### Pin Diagrams - 40-PIN PDIP (PIC16F724/727/PIC16LF724/727)

3: PIC16F724/727 devices only.

#### 2.2.2.3 PCON Register

The Power Control (PCON) register contains flag bits (refer to Table 3-2) to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the software enable of the BOR.

The PCON register bits are shown in Register 2-3.

#### REGISTER 2-3: PCON: POWER CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-q | R/W-q |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | _   | _   | _   | _   | _   | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:                 |                  |                        |                    |

|-------------------------|------------------|------------------------|--------------------|

| R = Readable bit        | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR       | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| q = Value depends on co | ondition         |                        |                    |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                        |

|---------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | POR: Power-on Reset Status bit                                                                                                    |

|         | 1 = No Power-on Reset occurred                                                                                                    |

|         | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                                             |

| bit 0   | BOR: Brown-out Reset Status bit                                                                                                   |

|         | 1 = No Brown-out Reset occurred                                                                                                   |

|         | <ul> <li>0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset<br/>occurs)</li> </ul> |

|         |                                                                                                                                   |

**Note 1:** Set BOREN<1:0> = 01 in the Configuration Word register for this bit to control the  $\overline{\text{BOR}}$ .

# 5.0 LOW DROPOUT (LDO) VOLTAGE REGULATOR

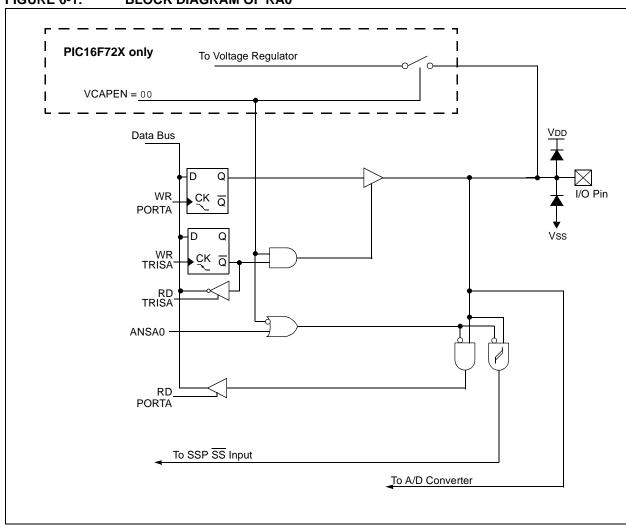

The PIC16F722/3/4/6/7 devices differ from the PIC16LF722/3/4/6/7 devices due to an internal Low Dropout (LDO) voltage regulator. The PIC16F722/3/4/6/7 devices contain an internal LDO, while the PIC16LF722/3/4/6/7 ones do not.

The lithography of the die allows a maximum operating voltage of 3.6V on the internal digital logic. In order to continue to support 5.0V designs, a LDO voltage regulator is integrated on the die. The LDO voltage regulator allows for the internal digital logic to operate at 3.2V, while I/O's operate at 5.0V (VDD).

The LDO voltage regulator requires an external bypass capacitor for stability. One of three pins, denoted as VCAP, can be configured for the external bypass capacitor. It is recommended that the capacitor be a ceramic cap between 0.1 to  $1.0 \,\mu$ F. The VCAP pin is not intended to supply power to external loads. An external voltage regulator should be used if this functionality is required. In addition, external devices should not supply power to the VCAP pin.

On power-up, the external capacitor will look like a large load on the LDO voltage regulator. To prevent erroneous operation, the device is held in Reset while a constant current source charges the external capacitor. After the cap is fully charged, the device is released from Reset. For more information, refer to **Section 23.0 "Electrical Specifications"**.

See Configuration Word 2 register (Register 8-2) for VCAP enable bits.

#### FIGURE 6-1: BLOCK DIAGRAM OF RA0

#### REGISTER 8-1: CONFIG1: CONFIGURATION WORD REGISTER 1 (CONTINUED)

- bit 4 **PWRTE:** Power-up Timer Enable bit 1 = PWRT disabled

- 1 = PWRT disabled0 = PWRT enabled

- bit 3 WDTE: Watchdog Timer Enable bit 1 = WDT enabled

- 1 = WDT enabled0 = WDT disabled

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = RC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, RC on RA7/OSC1/CLKIN

- 110 = RCIO oscillator: I/O function on RA6/OSC2/CLKOUT pin, RC on RA7/OSC1/CLKIN

- 101 = INTOSC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN

- 100 = INTOSCIO oscillator: I/O function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN

- 011 = EC: I/O function on RA6/OSC2/CLKOUT pin, CLKIN on RA7/OSC1/CLKIN

- 010 = HS oscillator: High-speed crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN

- 001 = XT oscillator: Crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN

- 000 = LP oscillator: Low-power crystal on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN

Note 1: Enabling Brown-out Reset does not automatically enable Power-up Timer.

- 2: The entire program memory will be erased when the code protection is turned off.

- 3: When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.

- 4: MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

#### REGISTER 8-2: CONFIG2: CONFIGURATION WORD REGISTER 2

|        |   |   | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> |

|--------|---|---|--------------------|--------------------|--------------------|--------------------|

|        | — | _ | _                  | —                  | —                  | —                  |

| bit 15 |   |   |                    |                    |                    | bit 8              |

| U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | R/P-1   | R/P-1   | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> |

|--------------------|--------------------|---------|---------|--------------------|--------------------|--------------------|--------------------|

| —                  | —                  | VCAPEN1 | VCAPEN0 | —                  | —                  | _                  | —                  |

| bit 7              |                    |         |         |                    |                    |                    | bit 0              |

| Legend:           | P = Programmable bit |                             |                    |  |

|-------------------|----------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read | 1 as '0'           |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared        | x = Bit is unknown |  |

bit 13-6 Unimplemented: Read as '1'

bit 5-4 VCAPEN<1:0>: Voltage Regulator Capacitor Enable bits For the PIC16LF72X: These bits are ignored. All VCAP pin functions are disabled. For the PIC16F72X: 00 = VCAP functionality is enabled on RA0 01 = VCAP functionality is enabled on RA5 10 = VCAP functionality is enabled on RA6 11 = All VCAP functions are disabled (not recommended) bit 3-0 Unimplemented: Read as '1'

**Note 1:** MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

#### 9.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

- **Note 1:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

- **2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the GIE and PEIE bits of the INTCON register must be disabled. If the GIE and PEIE bits of the INT-CON register are enabled, execution will switch to the Interrupt Service Routine.

Please refer to **Section 9.1.5** "Interrupts" for more information.

### 9.2 ADC Operation

#### 9.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

Note: The GO/DONE bit should not be set in the same instruction that turns on the ADC. Refer to Section 9.2.6 "A/D Conversion Procedure".

### 9.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRES register with new conversion result

#### 9.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRES register will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

| Note: | A device Reset forces all registers to their |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|

|       | Reset state. Thus, the ADC module is         |  |  |  |  |

|       | turned off and any pending conversion is     |  |  |  |  |

|       | terminated.                                  |  |  |  |  |

#### 9.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 9.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCP module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 15.0 "Capture/Compare/PWM (CCP) Module" for more information.

### 9.3 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 9-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 9-3. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the source

impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 9-1 may be used. This equation assumes that 1/2 LSb error is used (256 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 9-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V VDD$

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

$V_{APPLIED}\left(1 - \frac{1}{1-1}\right) = V_{CHOLD}$  :[11 VCHOLD charged to within 1/2 lsb

$$(2^{n+1}) - 1'$$

$$V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{CHOLD}$$

;[2] V\_{CHOLD charge response to V\_{APPLIED}}

$$V_{APPLIED}\left(1-e^{\frac{-ic}{RC}}\right) = V_{APPLIED}\left(1-\frac{1}{(2^{n+1})-l}\right) \quad (combining [1] and [2])$$

*Note:* Where n = number of bits of the ADC.

Solving for TC:

$$T_{C} = -C_{HOLD}(R_{IC} + R_{SS} + R_{S}) \ln(1/511)$$

=  $-10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.001957)$

=  $1.12\mu s$

$$c_{O} = 2M_{S} + 1.12M_{S} + [(50^{\circ}C - 25^{\circ}C)(0.05M_{S}/^{\circ}C)]$$

Therefore:

$$TACQ = 2MS + 1.12MS + [(50°C-25°C)(0.05MS/°C)]$$

= 4.42MS

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

### 12.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 12-1 displays the Timer1 enable selections.

# TABLE 12-1: TIMER1 ENABLE SELECTIONS

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

## 12.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 12-2 displays the clock source selections.

#### 12.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

#### 12.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI or the capacitive sensing oscillator signal. Either of these external clock sources can be synchronized to the microcontroller system clock or they can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

| Note: | In Counter mode, a falling edge must be      |

|-------|----------------------------------------------|

|       | registered by the counter prior to the first |

|       | incrementing rising edge after any one or    |

|       | more of the following conditions:            |

- Timer1 enabled after POR reset

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON= 1) when T1CKI is low.

| TMR1CS1 | TMR1CS0 | T10SCEN | Clock Source                           |

|---------|---------|---------|----------------------------------------|

| 0       | 1       | x       | System Clock (Fosc)                    |

| 0       | 0       | x       | Instruction Clock (Fosc/4)             |

| 1       | 1       | x       | Capacitive Sensing Oscillator          |

| 1       | 0       | 0       | External Clocking on T1CKI Pin         |

| 1       | 0       | 1       | Oscillator Circuit on T1OSI/T1OSO Pins |

#### TABLE 12-2: CLOCK SOURCE SELECTIONS

#### 12.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

### 12.4 Timer1 Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

| Note: | The oscillator requires a start-up and   |

|-------|------------------------------------------|

|       | stabilization time before use. Thus,     |

|       | T1OSCEN should be set and a suitable     |

|       | delay observed prior to enabling Timer1. |

### 12.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 12.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

#### 12.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

| Name    | Bit 7        | Bit 6          | Bit 5          | Bit 4          | Bit 3                   | Bit 2    | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------------|----------------|----------------|----------------|-------------------------|----------|---------|---------|----------------------|---------------------------------|

| ADCON0  | _            |                | CHS3           | CHS2           | CHS1                    | CHS0     | GO/DONE | ADON    | 00 0000              | 00 0000                         |

| ANSELB  | _            | _              | ANSB5          | ANSB4          | ANSB3                   | ANSB2    | ANSB1   | ANSB0   | 11 1111              | 11 1111                         |

| APFCON  | _            | _              | _              | _              | _                       | _        | SSSEL   | CCP2SEL | 00                   | 00                              |

| CCP1CON | _            | _              | DC1B1          | DC1B0          | CCP1M3                  | CCP1M2   | CCP1M1  | CCP1M0  | 00 0000              | 00 0000                         |

| CCP2CON | _            | _              | DC2B1          | DC2B0          | CCP2M3                  | CCP2M2   | CCP2M1  | CCP2M0  | 00 0000              | 00 0000                         |

| CCPRxL  | Capture/Com  | npare/PWM R    | egister X Lov  | v Byte         |                         |          |         |         | xxxx xxxx            | uuuu uuuu                       |

| CCPRxH  | Capture/Com  | npare/PWM R    | egister X Hig  | h Byte         |                         |          |         |         | xxxx xxxx            | uuuu uuuu                       |

| INTCON  | GIE          | PEIE           | TOIE           | INTE           | RBIE                    | T0IF     | INTF    | RBIF    | 0000 000x            | 0000 000x                       |

| PIE1    | TMR1GIE      | ADIE           | RCIE           | TXIE           | SSPIE                   | CCP1IE   | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIE2    | —            | -              | —              | -              | —                       | —        | —       | CCP2IE  | 0                    | 0                               |

| PIR1    | TMR1GIF      | ADIF           | RCIF           | TXIF           | SSPIF                   | CCP1IF   | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| PIR2    | —            | -              | —              | -              | —                       | —        | —       | CCP2IF  | 0                    | 0                               |

| T1CON   | TMR1CS1      | TMR1CS0        | T1CKPS1        | T1CKPS0        | T1OSCEN                 | T1SYNC   | _       | TMR10N  | 0000 00-0            | uuuu uu-u                       |

| T1GCON  | TMR1GE       | T1GPOL         | T1GTM          | T1GSPM         | T <u>1GGO</u> /<br>DONE | T1GVAL   | T1GSS1  | T1GSS0  | 0000 0x00            | 00x0 0x00                       |

| TMR1L   | Holding Regi | ster for the L | east Significa | nt Byte of the | 16-bit TMR1 I           | Register |         |         | xxxx xxxx            | uuuu uuuu                       |

| TMR1H   | Holding Regi | ster for the M | ost Significar | nt Byte of the | 16-bit TMR1 F           | Register |         |         | xxxx xxxx            | uuuu uuuu                       |

| TRISB   | TRISB7       | TRISB6         | TRISB5         | TRISB4         | TRISB3                  | TRISB2   | TRISB1  | TRISB0  | 1111 1111            | 1111 1111                       |

| TRISC   | TRISC7       | TRISC6         | TRISC5         | TRISC4         | TRISC3                  | TRISC2   | TRISC1  | TRISC0  | 1111 1111            | 1111 1111                       |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Compare.

#### 16.2 AUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit timer that is dedicated to the support of both the asynchronous and synchronous AUSART operation.

The SPBRG register determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by the BRGH bit of the TXSTA register. In Synchronous mode, the BRGH bit is ignored.

Table 16-3 contains the formulas for determining the baud rate. Example 16-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various asynchronous modes have been computed for your convenience and are shown in Table 16-3. It may be advantageous to use the high baud rate (BRGH = 1), to reduce the baud rate error.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

#### EXAMPLE 16-1: CALCULATING BAUD RATE ERROR

For a device with FOSC of 16 MHz, desired baud rate of 9600, and Asynchronous mode with SYNC = 0 and BRGH = 0 (as seen in Table 16-3):

Desired Baud Rate =

$$\frac{FOSC}{64(SPBRG+1)}$$

Solving for SPBRG:

$$SPBRG = \left(\frac{FOSC}{64(Desired Baud Rate)}\right) - 1$$

$$= \left(\frac{16000000}{64(9600)}\right) - 1$$

$$= [25.042] = 25$$

$$Actual Baud Rate = \frac{16000000}{64(25+1)}$$

$$= 9615$$

% Error =  $\left(\frac{Actual Baud Rate - Desired Baud Rate}{Desired Baud Rate}\right) 100$

$$= \left(\frac{9615 - 9600}{9600}\right) 100 = 0.16\%$$

| Configur | ation Bits |              | Baud Rate Formula |  |  |

|----------|------------|--------------|-------------------|--|--|

| SYNC     | BRGH       | AUSART Mode  | Baud Rate Formula |  |  |

| 0        | 0          | Asynchronous | Fosc/[64 (n+1)]   |  |  |

| 0        | 1          | Asynchronous | Fosc/[16 (n+1)]   |  |  |

| 1        | x          | Synchronous  | Fosc/[4 (n+1)]    |  |  |

#### TABLE 16-3:BAUD RATE FORMULAS

Legend: x = Don't care, n = value of SPBRG register

#### TABLE 16-4: REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| RCSTA | SPEN  | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | x000 000x            | 0000 000x                       |

| SPBRG | BRG7  | BRG6  | BRG5  | BRG4  | BRG3  | BRG2  | BRG1  | BRG0  | 0000 0000            | 0000 0000                       |

| TXSTA | CSRC  | TX9   | TXEN  | SYNC  | _     | BRGH  | TRMT  | TX9D  | 0000 -010            | 0000 -010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for the Baud Rate Generator.

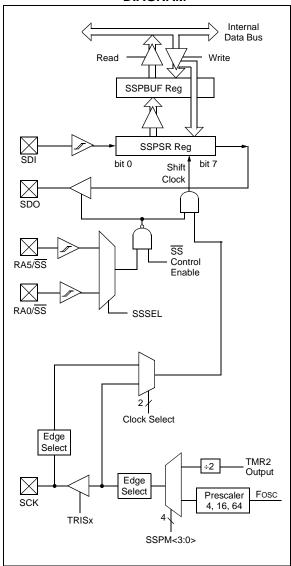

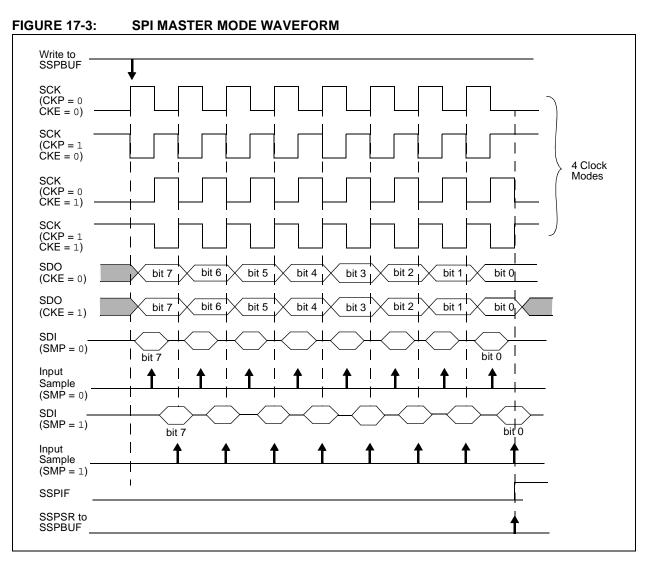

FIGURE 17-2: SPI MODE BLOCK DIAGRAM

#### EXAMPLE 17-1: LOADING THE SSPBUF (SSPSR) REGISTER

|      | BANKSEL | SSPSTAT     | i                                           |

|------|---------|-------------|---------------------------------------------|

| LOOP | BTFSS   | SSPSTAT, BF | ;Has data been received(transmit complete)? |

|      | GOTO    | LOOP        | ;No                                         |

|      | BANKSEL | SSPBUF      | ;                                           |

|      | MOVF    | SSPBUF, W   | ;WREG reg = contents of SSPBUF              |

|      | MOVWF   | RXDATA      | ;Save in user RAM, if data is meaningful    |

|      | MOVF    | TXDATA, W   | ;W reg = contents of TXDATA                 |

|      | MOVWF   | SSPBUF      | ;New data to xmit                           |

|      |         |             |                                             |

#### 17.2.4 ADDRESSING

Once the SSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the eight bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock line (SCL).

#### 17.2.4.1 7-bit Addressing

In 7-bit Addressing mode (Figure 17-10), the value of register SSPSR<7:1> is compared to the value of register SSPADD<7:1>. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- The SSPSR register value is loaded into the SSPBUF register.

- The BF bit is set.

- An ACK pulse is generated.

- SSP interrupt flag bit, SSPIF of the PIR1 register, is set (interrupt is generated if enabled) on the falling edge of the ninth SCL pulse.

#### 17.2.4.2 10-bit Addressing

In 10-bit Address mode, two address bytes need to be received by the slave (Figure 17-11). The five Most Significant bits (MSbs) of the first address byte specify if it is a 10-bit address. The R/W bit of the SSPSTAT register must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address.

The sequence of events for 10-bit address is as follows for reception:

- 1. Load SSPADD register with high byte of address.

- 2. Receive first (high) byte of address (bits SSPIF, BF and UA of the SSPSTAT register are set).

- 3. Read the SSPBUF register (clears bit BF).

- 4. Clear the SSPIF flag bit.

- 5. Update the SSPADD register with second (low) byte of address (clears UA bit and releases the SCL line).

- 6. Receive low byte of address (bits SSPIF, BF and UA are set).

- 7. Update the SSPADD register with the high byte of address. If match releases SCL line, this will clear bit UA.

- 8. Read the SSPBUF register (clears bit BF).

- 9. Clear flag bit SSPIF.

If data is requested by the master, once the slave has been addressed:

- 1. Receive repeated Start condition.

- 2. Receive repeat of high byte address with  $R/\overline{W} = 1$ , indicating a read.

- 3. BF bit is set and the CKP bit is cleared, stopping SCL and indicating a read request.

- 4. SSPBUF is written, setting BF, with the data to send to the master device.

- 5. CKP is set in software, releasing the SCL line.

#### 17.2.4.3 Address Masking

The Address Masking register (SSPMSK) is only accessible while the SSPM bits of the SSPCON register are set to '1001'. In this register, the user can select which bits of a received address the hardware will compare when determining an address match. Any bit that is set to a zero in the SSPMSK register, the corresponding bit in the received address byte and SSPADD register are ignored when determining an address match. By default, the register is set to all ones, requiring a complete match of a 7-bit address or the lower eight bits of a 10-bit address.

# 19.0 POWER-DOWN MODE (SLEEP)

The Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If the Watchdog Timer is enabled:

- WDT will be cleared but keeps running.

- PD bit of the STATUS register is cleared.

- TO bit of the STATUS register is set.

- Oscillator driver is turned off.

- Timer1 oscillator is unaffected

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSs, with no external circuitry drawing current from the I/O pin. I/O pins that are high-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level when external  $\overline{\text{MCLR}}$  is enabled.

**Note:** A Reset generated by a WDT time out does not drive MCLR pin low.

#### 19.1 Wake-up from Sleep

The device can wake up from Sleep through one of the following events:

- 1. External Reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer wake-up (if WDT was enabled).

- 3. Interrupt from RB0/INT pin, PORTB change or a peripheral interrupt.

The first event will cause a device Reset. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. TO bit is cleared if WDT wake-up occurred.

The following peripheral interrupts can wake the device from Sleep:

- 1. TMR1 Interrupt. Timer1 must be operating as an asynchronous counter.

- USART Receive Interrupt (Synchronous Slave mode only)

- 3. A/D conversion (when A/D clock source is RC)

- 4. Interrupt-on-change

- 5. External Interrupt from INT pin

- 6. Capture event on CCP1 or CCP2

- 7. SSP Interrupt in SPI or I<sup>2</sup>C Slave mode

Other peripherals cannot generate interrupts since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction, then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

**Note:** If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from Sleep. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>2-cycle instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                                                                      |

| Operands:        | None                                                                                                                                                                                |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT} \\ 0 \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}} \\ 1 \rightarrow \overline{\text{PD}} \end{array}$ |

| Status Affected: | TO, PD                                                                                                                                                                              |

| Description:     | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT.<br>Status bits TO and PD are set.                                                      |

| CALL             | Call Subroutine                                                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                 |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                    |

| Operation:       | $(PC)+ 1 \rightarrow TOS,$<br>$k \rightarrow PC<10:0>,$<br>$(PCLATH<4:3>) \rightarrow PC<12:11>$                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                                    |

| Description:     | Call Subroutine. First, return<br>address (PC + 1) is pushed onto<br>the stack. The 11-bit immediate<br>address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a 2-cycle instruction. |

| COMF             | Complement f                                                                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] COMF f,d                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                     |

| Status Affected: | Z                                                                                                                                                              |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the<br>result is stored in W. If 'd' is '1',<br>the result is stored back in<br>register 'f'. |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |

| Operands:        | $0 \le f \le 127$                                                     |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are<br>cleared and the Z bit is set.     |

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECF f,d                                                                                                                                |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                 |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is '0',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

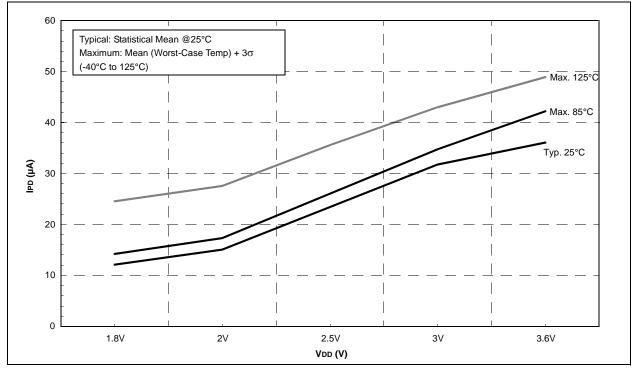

#### FIGURE 24-61: PIC16F722/3/4/6/7 A/D INTERNAL RC OSCILLATOR PERIOD

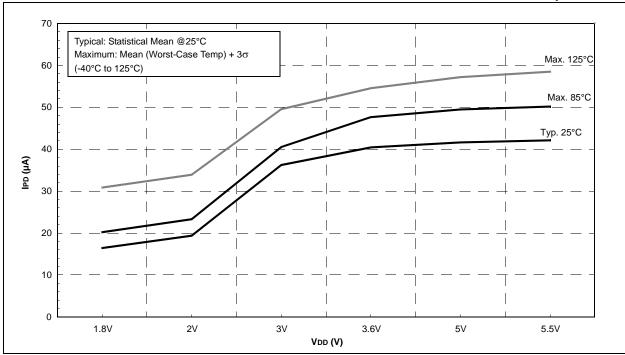

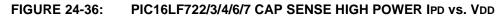

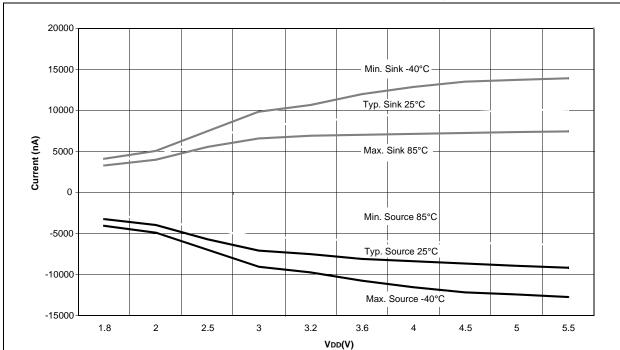

FIGURE 24-62: PIC16F722/3/4/6/7 CAP SENSE OUTPUT CURRENT, POWER MODE = HIGH

# THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Micro-chip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://www.microchip.com/support