Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-UQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f726t-i-mv |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### PIC16(L)F72X Family Types

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data SRAM<br>(bytes) | High-Endurance Flash<br>Memory (bytes) | I/O's <sup>(2)</sup> | 8-bit ADC (ch) | CapSense (ch) | Timers<br>(8/16-bit) | AUSART | SSP (I <sup>2</sup> C/SPI) | ССР | Debug <sup>(1)</sup> | ХГР |

|---------------|------------------|---------------------------------|----------------------|----------------------------------------|----------------------|----------------|---------------|----------------------|--------|----------------------------|-----|----------------------|-----|

| PIC16(L)F707  | (1)              | 8192                            | 363                  | 0                                      | 36                   | 14             | 32            | 4/2                  | 1      | 1                          | 2   |                      | Y   |

| PIC16(L)F720  | (2)              | 2048                            | 128                  | 128                                    | 18                   | 12             | _             | 2/1                  | 1      | 1                          | 1   | I                    | Y   |

| PIC16(L)F721  | (2)              | 4096                            | 256                  | 128                                    | 18                   | 12             | _             | 2/1                  | 1      | 1                          | 1   | I                    | Y   |

| PIC16(L)F722  | (4)              | 2048                            | 128                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | -                    | Y   |

| PIC16(L)F722A | (3)              | 2048                            | 128                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

| PIC16(L)F723  | (4)              | 4096                            | 192                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | Ι                    | Y   |

| PIC16(L)F723A | (3)              | 4096                            | 192                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | -                    | Y   |

| PIC16(L)F724  | (4)              | 4096                            | 192                  | 0                                      | 36                   | 14             | 16            | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

| PIC16(L)F726  | (4)              | 8192                            | 368                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | Ι                    | Y   |

| PIC16(L)F727  | (4)              | 8192                            | 368                  | 0                                      | 36                   | 14             | 16            | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

**Note 1:** I - Debugging, Integrated on Chip; H - Debugging, Requires Debug Header.

2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

- 1: DS41418 PIC16(L)F707 Data Sheet, 40/44-Pin Flash, 8-bit Microcontrollers

- 2: DS41430 PIC16(L)F720/721 Data Sheet, 20-Pin Flash, 8-bit Microcontrollers

- 3: DS41417 PIC16(L)F722A/723A Data Sheet, 28-Pin Flash, 8-bit Microcontrollers

- 4: DS41341 PIC16(L)F72X Data Sheet, 28/40/44-Pin Flash, 8-bit Microcontrollers

## TABLE 1-1: PIC16(L)F722/3/4/6/7 PINOUT DESCRIPTION

| Name                 | Function | Input<br>Type | Output<br>Type | Description                                                                                          |

|----------------------|----------|---------------|----------------|------------------------------------------------------------------------------------------------------|

| RA0/AN0/SS/VCAP      | RA0      | TTL           | CMOS           | General purpose I/O.                                                                                 |

|                      | AN0      | AN            |                | A/D Channel 0 input.                                                                                 |

|                      | SS       | ST            | _              | Slave Select input.                                                                                  |

|                      | VCAP     | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F72X only).                                             |

| RA1/AN1              | RA1      | TTL           | CMOS           | General purpose I/O.                                                                                 |

|                      | AN1      | AN            | _              | A/D Channel 1 input.                                                                                 |

| RA2/AN2              | RA2      | TTL           | CMOS           | General purpose I/O.                                                                                 |

|                      | AN2      | AN            | —              | A/D Channel 2 input.                                                                                 |

| RA3/AN3/Vref         | RA3      | TTL           | CMOS           | General purpose I/O.                                                                                 |

|                      | AN3      | AN            | _              | A/D Channel 3 input.                                                                                 |

|                      | Vref     | AN            | —              | A/D Voltage Reference input.                                                                         |

| RA4/CPS6/T0CKI       | RA4      | TTL           | CMOS           | General purpose I/O.                                                                                 |

|                      | CPS6     | AN            | _              | Capacitive sensing input 6.                                                                          |

|                      | T0CKI    | ST            | _              | Timer0 clock input.                                                                                  |

| RA5/AN4/CPS7/SS/VCAP | RA5      | TTL           | CMOS           | General purpose I/O.                                                                                 |

|                      | AN4      | AN            |                | A/D Channel 4 input.                                                                                 |

|                      | CPS7     | AN            | —              | Capacitive sensing input 7.                                                                          |

|                      | SS       | ST            | _              | Slave Select input.                                                                                  |

|                      | VCAP     | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F72X only).                                             |

| RA6/OSC2/CLKOUT/VCAP | RA6      | TTL           | CMOS           | General purpose I/O.                                                                                 |

|                      | OSC2     | —             | XTAL           | Crystal/Resonator (LP, XT, HS modes).                                                                |

|                      | CLKOUT   | _             | CMOS           | Fosc/4 output.                                                                                       |

|                      | VCAP     | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F72X only).                                             |

| RA7/OSC1/CLKIN       | RA7      | TTL           | CMOS           | General purpose I/O.                                                                                 |

|                      | OSC1     | XTAL          | _              | Crystal/Resonator (LP, XT, HS modes).                                                                |

|                      | CLKIN    | CMOS          | _              | External clock input (EC mode).                                                                      |

|                      | CLKIN    | ST            | _              | RC oscillator connection (RC mode).                                                                  |

| RB0/AN12/CPS0/INT    | RB0      | TTL           | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |

|                      | AN12     | AN            | _              | A/D Channel 12 input.                                                                                |

|                      | CPS0     | AN            | _              | Capacitive sensing input 0.                                                                          |

|                      | INT      | ST            | _              | External interrupt.                                                                                  |

| RB1/AN10/CPS1        | RB1      | TTL           | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |

|                      | AN10     | AN            | —              | A/D Channel 10 input.                                                                                |

|                      | CPS1     | AN            | —              | Capacitive sensing input 1.                                                                          |

| RB2/AN8/CPS2         | RB2      | TTL           | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |

|                      | AN8      | AN            | —              | A/D Channel 8 input.                                                                                 |

|                      | CPS2     | AN            |                | Capacitive sensing input 2.                                                                          |

| RB3/AN9/CPS3/CCP2    | RB3      | TTL           | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |

|                      | AN9      | AN            |                | A/D Channel 9 input.                                                                                 |

|                      | CPS3     | AN            | _              | Capacitive sensing input 3.                                                                          |

|                      |          |               | CMOS           | Capture/Compare/PWM2.                                                                                |

## 6.0 I/O PORTS

There are as many as 35 general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

## 6.1 Alternate Pin Function

The Alternate Pin Function Control (APFCON) register is used to steer specific peripheral input and output functions between different pins. The APFCON register is shown in Register 6-1. For this device family, the following functions can be moved between different pins.

- SS (Slave Select)

- CCP2

## REGISTER 6-1: APFCON: ALTERNATE PIN FUNCTION CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0   |

|-------|-----|-----|-----|-----|-----|-------|---------|

| —     | —   | —   | _   | —   | —   | SSSEL | CCP2SEL |

| bit 7 |     |     |     |     |     |       | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-2 | Unimplemented: Read as '0'.                                                                                                       |

|---------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | SSSEL: SS Input Pin Selection bit                                                                                                 |

|         | $0 = \overline{SS}$ function is on RA5/AN4/CPS7/SS/VCAP<br>1 = SS function is on RA0/AN0/SS/VCAP                                  |

| bit 0   | <b>CCP2SEL:</b> CCP2 Input/Output Pin Selection bit<br>0 = CCP2 function is on RC1/T1OSI/CCP2<br>1 = CCP2 function is on RB3/CCP2 |

| R/W-1                                                                | R/W-1                           | R/W-1 | R/W-1 | R/W-1                                   | R/W-1 | R/W-1 | R/W-1 |  |

|----------------------------------------------------------------------|---------------------------------|-------|-------|-----------------------------------------|-------|-------|-------|--|

| WPUB7                                                                | WPUB6                           | WPUB5 | WPUB4 | WPUB3                                   | WPUB2 | WPUB1 | WPUB0 |  |

| bit 7                                                                |                                 |       | •     |                                         |       | •     | bit 0 |  |

|                                                                      |                                 |       |       |                                         |       |       |       |  |

| Legend:                                                              |                                 |       |       |                                         |       |       |       |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                 |       |       |                                         |       |       |       |  |

| -n = Value at P                                                      | = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |

#### REGISTER 6-7: WPUB: WEAK PULL-UP PORTB REGISTER

bit 7-0 WPUB<7:0>: Weak Pull-up Register bits

- 1 = Pull-up enabled

- 0 = Pull-up disabled

**Note 1:** Global RBPU bit of the OPTION register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

#### REGISTER 6-8: IOCB: INTERRUPT-ON-CHANGE PORTB REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IOCB7 | IOCB6 | IOCB5 | IOCB4 | IOCB3 | IOCB2 | IOCB1 | IOCB0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 **IOCB<7:0>:** Interrupt-on-Change PORTB Control bits

1 = Interrupt-on-change enabled

0 = Interrupt-on-change disabled

#### REGISTER 6-9: ANSELB: PORTB ANALOG SELECT REGISTER

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | ANSB5 | ANSB4 | ANSB3 | ANSB2 | ANSB1 | ANSB0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 ANSB<5:0>: Analog Select between Analog or Digital Function on Pins RB<5:0>, respectively

0 = Digital I/O. Pin is assigned to port or Digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital Input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### REGISTER 6-17: ANSELE: PORTE ANALOG SELECT REGISTER

| U-0             | U-0 | U-0              | U-0 | U-0                                      | R/W-1                | R/W-1                | R/W-1                |

|-----------------|-----|------------------|-----|------------------------------------------|----------------------|----------------------|----------------------|

| _               | _   |                  | _   | _                                        | ANSE2 <sup>(2)</sup> | ANSE1 <sup>(2)</sup> | ANSE0 <sup>(2)</sup> |

| bit 7           |     |                  |     |                                          |                      |                      | bit 0                |

|                 |     |                  |     |                                          |                      |                      |                      |

| Legend:         |     |                  |     |                                          |                      |                      |                      |

| R = Readable    | bit | W = Writable     | bit | U = Unimpler                             | mented bit, read     | 1 as '0'             |                      |

| -n = Value at F | POR | '1' = Bit is set |     | 0' = Bit is cleared $x = Bit is unknown$ |                      |                      |                      |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 **ANSE<2:0>:** Analog Select between Analog or Digital Function on Pins RE<2:0>, respectively 0 = Digital I/O. Pin is assigned to port or Digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital Input buffer disabled.

2: ANSELE register is not implemented on the PIC16F722/723/726/PIC16LF722/723/726. Read as '0'

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3                 | Bit 2                 | Bit 1                 | Bit 0                 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-------|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|----------------------|---------------------------------|

| ADCON0 |       |       | CHS3  | CHS2  | CHS1                  | CHS0                  | GO/DONE               | ADON                  | 00 0000              | 00 0000                         |

| ANSELE | _     |       | _     | _     | _                     | ANSE2                 | ANSE1                 | ANSE0                 | 111                  | 111                             |

| PORTE  | _     | _     | _     | _     | RE3                   | RE2                   | RE1                   | RE0                   | xxxx                 | xxxx                            |

| TRISE  | _     |       | _     | _     | TRISE3 <sup>(2)</sup> | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> | 1111                 | 1111                            |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE

Note 1: These registers are not implemented on the PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'.

**2:** This bit is always '1' as RE3 is input only.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

## 7.2 Clock Source Modes

Clock source modes can be classified as external or internal.

- Internal clock source (INTOSC) is contained within the oscillator module and derived from a 500 kHz high precision oscillator. The oscillator module has eight selectable output frequencies, with a maximum internal frequency of 16 MHz.

- External clock modes rely on external circuitry for the clock source. Examples are: oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

The system clock can be selected between external or internal clock sources via the FOSC bits of the Configuration Word 1.

## 7.3 Internal Clock Modes

The oscillator module has eight output frequencies derived from a 500 kHz high precision oscillator. The IRCF bits of the OSCCON register select the postscaler applied to the clock source dividing the frequency by 1, 2, 4 or 8. Setting the PLLEN bit of the Configuration Word 1 locks the internal clock source to 16 MHz before the postscaler is selected by the IRCF bits. The PLLEN bit must be set or cleared at the time of programming; therefore, only the upper or low four clock source frequencies are selectable in software.

## 7.3.1 INTOSC AND INTOSCIO MODES

The INTOSC and INTOSCIO modes configure the internal oscillators as the system clock source when the device is programmed using the oscillator selection or the FOSC<2:0> bits in the CONFIG1 register. See **Section 8.0** "**Device Configuration**" for more information.

In INTOSC mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT outputs the selected internal oscillator frequency divided by 4. The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

In INTOSCIO mode, OSC1/CLKIN and OSC2/CLKOUT are available for general purpose I/O.

## 7.3.2 FREQUENCY SELECT BITS (IRCF)

The output of the 500 kHz INTOSC and 16 MHz INTOSC, with Phase-Locked Loop enabled, connect to a postscaler and multiplexer (see Figure 7-1). The Internal Oscillator Frequency Select bits (IRCF) of the OSCCON register select the frequency output of the internal oscillator. Depending upon the PLLEN bit, one of four frequencies of two frequency sets can be selected via software:

If PLLEN = 1, frequency selection is as follows:

- 16 MHz

- 8 MHz (default after Reset)

- 4 MHz

- 2 MHz

- If PLLEN = 0, frequency selection is as follows:

- 500 kHz

- 250 kHz (default after Reset)

- 125 kHz

- 62.5 kHz

Note: Following any Reset, the IRCF<1:0> bits of the OSCCON register are set to '10' and the frequency selection is set to 8 MHz or 250 kHz. The user can modify the IRCF bits to select a different frequency.

There is no start-up delay before a new frequency selected in the IRCF bits takes effect. This is because the old and new frequencies are derived from INTOSC via the postscaler and multiplexer.

Start-up delay specifications are located in the Table 23-2 in Section 23.0 "Electrical Specifications".

## 7.6 External Clock Modes

#### 7.6.1 OSCILLATOR START-UP TIMER (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations on the OSC1 pin before the device is released from Reset. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

#### 7.6.2 EC MODE

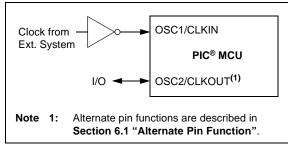

The External Clock (EC) mode allows an externally generated logic level as the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input and the OSC2 is available for general purpose I/O. Figure 7-2 shows the pin connections for EC mode.

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### FIGURE 7-2: EXTERNAL CLOCK (EC) MODE OPERATION

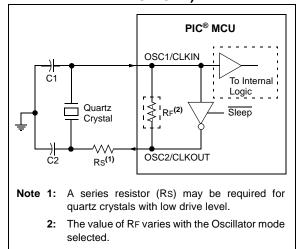

#### 7.6.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 7-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

LP Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is best suited to drive resonators with a low drive level specification, for example, tuning fork type crystals.

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 7-3 and Figure 7-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

#### FIGURE 7-3: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices (DS00826)

- AN849, Basic PIC<sup>®</sup> Oscillator Design (DS00849)

- AN943, Practical PIC<sup>®</sup> Oscillator Analysis and Design (DS00943)

- AN949, Making Your Oscillator Work (DS00949).

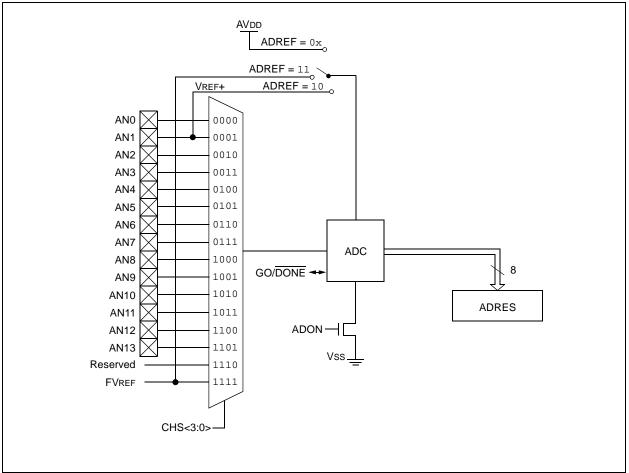

## 9.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 8-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 8-bit binary result via successive approximation and stores the conversion result into the ADC result register (ADRES). Figure 9-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

#### FIGURE 9-1: ADC BLOCK DIAGRAM

#### 9.2.7 ADC REGISTER DEFINITIONS

The following registers are used to control the operation of the ADC.

#### REGISTER 9-1: ADCON0: A/D CONTROL REGISTER 0

| U-0   | U-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 |

|-------|-----------|-------|-------|-------|-------|---------|-------|

| —     | — CHS3 CH |       | CHS2  | CHS1  | CHS0  | GO/DONE | ADON  |

| bit 7 |           |       |       |       |       |         | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-2 CHS<3:0>: Analog Channel Select bits

|       | 0000 = ANO                                                                                                                                                                                               |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 0001 = AN1                                                                                                                                                                                               |

|       | 0010 = AN2                                                                                                                                                                                               |

|       | 0011 = AN3                                                                                                                                                                                               |

|       | 0100 = AN4                                                                                                                                                                                               |

|       | 0101 = AN5                                                                                                                                                                                               |

|       | 0110 = AN6                                                                                                                                                                                               |

|       | 0111 = AN7                                                                                                                                                                                               |

|       | 1000 = AN8                                                                                                                                                                                               |

|       | 1001 = AN9                                                                                                                                                                                               |

|       | 1010 = AN10                                                                                                                                                                                              |

|       | 1011 = AN11                                                                                                                                                                                              |

|       | 1100 = AN12                                                                                                                                                                                              |

|       | 1101 = AN13                                                                                                                                                                                              |

|       | 1110 = Reserved                                                                                                                                                                                          |

|       | 1111 = Fixed Voltage Reference (FVREF)                                                                                                                                                                   |

| bit 1 | GO/DONE: A/D Conversion Status bit                                                                                                                                                                       |

|       | <ul> <li>1 = A/D conversion cycle in progress. Setting this bit starts an A/D conversion cycle.</li> <li>This bit is automatically cleared by hardware when the A/D conversion has completed.</li> </ul> |

|       | 0 = A/D conversion completed/not in progress                                                                                                                                                             |

| bit 0 | ADON: ADC Enable bit                                                                                                                                                                                     |

|       | 1 = ADC is enabled                                                                                                                                                                                       |

0 = ADC is disabled and consumes no operating current

## 12.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 12-1 displays the Timer1 enable selections.

## TABLE 12-1: TIMER1 ENABLE SELECTIONS

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

## 12.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 12-2 displays the clock source selections.

#### 12.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

#### 12.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI or the capacitive sensing oscillator signal. Either of these external clock sources can be synchronized to the microcontroller system clock or they can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

| Note: | In Counter mode, a falling edge must be      |

|-------|----------------------------------------------|

|       | registered by the counter prior to the first |

|       | incrementing rising edge after any one or    |

|       | more of the following conditions:            |

- Timer1 enabled after POR reset

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON= 1) when T1CKI is low.

| TMR1CS1 | TMR1CS0 | T10SCEN | Clock Source                           |

|---------|---------|---------|----------------------------------------|

| 0       | 1       | x       | System Clock (Fosc)                    |

| 0       | 0       | x       | Instruction Clock (Fosc/4)             |

| 1       | 1       | x       | Capacitive Sensing Oscillator          |

| 1       | 0       | 0       | External Clocking on T1CKI Pin         |

| 1       | 0       | 1       | Oscillator Circuit on T1OSI/T1OSO Pins |

#### TABLE 12-2: CLOCK SOURCE SELECTIONS

| Name    | Bit 7                                                                       | Bit 6       | Bit 5         | Bit 4   | Bit 3                   | Bit 2  | Bit 1  | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-----------------------------------------------------------------------------|-------------|---------------|---------|-------------------------|--------|--------|---------|----------------------|---------------------------------|

| ANSELB  | —                                                                           | —           | ANSB5         | ANSB4   | ANSB3                   | ANSB2  | ANSB1  | ANSB0   | 11 1111              | 11 1111                         |

| APFCON  | _                                                                           | _           | _             | _       | _                       | _      | SSSEL  | CCP2SEL | 00                   | 00                              |

| CCP1CON | _                                                                           | _           | DC1B1         | DC1B0   | CCP1M3                  | CCP1M2 | CCP1M1 | CCP1M0  | 00 0000              | 00 0000                         |

| CCP2CON | _                                                                           | _           | DC2B1         | DC2B0   | CCP2M3                  | CCP2M2 | CCP2M1 | CCP2M0  | 00 0000              | 00 0000                         |

| CCPRxL  | Capture/Con                                                                 | npare/PWM R | egister X Lov | v Byte  |                         |        |        |         | xxxx xxxx            | uuuu uuuu                       |

| CCPRxH  | Capture/Con                                                                 | npare/PWM R | egister X Hig | h Byte  |                         |        |        |         | xxxx xxxx            | uuuu uuuu                       |

| INTCON  | GIE                                                                         | PEIE        | TOIE          | INTE    | RBIE                    | T0IF   | INTF   | RBIF    | 0000 000x            | 0000 000x                       |

| PIE1    | TMR1GIE                                                                     | ADIE        | RCIE          | TXIE    | SSPIE                   | CCP1IE | TMR2IE | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIE2    | —                                                                           | _           |               |         | —                       |        |        | CCP2IE  | 0                    | 0                               |

| PIR1    | TMR1GIF                                                                     | ADIF        | RCIF          | TXIF    | SSPIF                   | CCP1IF | TMR2IF | TMR1IF  | 0000 0000            | 0000 0000                       |

| PIR2    | —                                                                           | —           | -             | -       | —                       | -      | —      | CCP2IF  | 0                    | 0                               |

| T1CON   | TMR1CS1                                                                     | TMR1CS0     | T1CKPS1       | T1CKPS0 | T1OSCEN                 | T1SYNC | —      | TMR10N  | 0000 00-0            | uuuu uu-u                       |

| T1GCON  | TMR1GE                                                                      | T1GPOL      | T1GTM         | T1GSPM  | T <u>1GGO</u> /<br>DONE | T1GVAL | T1GSS1 | T1GSS0  | 00x0 0x00            | 0000 0x00                       |

| TMR1L   | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |             |               |         |                         |        |        |         | xxxx xxxx            | uuuu uuuu                       |

| TMR1H   | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |             |               |         |                         |        |        |         | xxxx xxxx            | uuuu uuuu                       |

| TRISB   | TRISB7                                                                      | TRISB6      | TRISB5        | TRISB4  | TRISB3                  | TRISB2 | TRISB1 | TRISB0  | 1111 1111            | 1111 1111                       |

| TRISC   | TRISC7                                                                      | TRISC6      | TRISC5        | TRISC4  | TRISC3                  | TRISC2 | TRISC1 | TRISC0  | 1111 1111            | 1111 1111                       |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Capture.

| Name    | Bit 7                                                                       | Bit 6          | Bit 5          | Bit 4          | Bit 3                   | Bit 2    | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-----------------------------------------------------------------------------|----------------|----------------|----------------|-------------------------|----------|---------|---------|----------------------|---------------------------------|

| ADCON0  | _                                                                           |                | CHS3           | CHS2           | CHS1                    | CHS0     | GO/DONE | ADON    | 00 0000              | 00 0000                         |

| ANSELB  | _                                                                           | _              | ANSB5          | ANSB4          | ANSB3                   | ANSB2    | ANSB1   | ANSB0   | 11 1111              | 11 1111                         |

| APFCON  | _                                                                           | _              | _              | _              | _                       | _        | SSSEL   | CCP2SEL | 00                   | 00                              |

| CCP1CON | _                                                                           | _              | DC1B1          | DC1B0          | CCP1M3                  | CCP1M2   | CCP1M1  | CCP1M0  | 00 0000              | 00 0000                         |

| CCP2CON | _                                                                           | _              | DC2B1          | DC2B0          | CCP2M3                  | CCP2M2   | CCP2M1  | CCP2M0  | 00 0000              | 00 0000                         |

| CCPRxL  | Capture/Com                                                                 | npare/PWM R    | egister X Lov  | v Byte         |                         |          |         |         | xxxx xxxx            | uuuu uuuu                       |

| CCPRxH  | Capture/Com                                                                 | npare/PWM R    | egister X Hig  | h Byte         |                         |          |         |         | xxxx xxxx            | uuuu uuuu                       |

| INTCON  | GIE                                                                         | PEIE           | TOIE           | INTE           | RBIE                    | T0IF     | INTF    | RBIF    | 0000 000x            | 0000 000x                       |

| PIE1    | TMR1GIE                                                                     | ADIE           | RCIE           | TXIE           | SSPIE                   | CCP1IE   | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIE2    | —                                                                           | -              | —              | -              | —                       | —        | —       | CCP2IE  | 0                    | 0                               |

| PIR1    | TMR1GIF                                                                     | ADIF           | RCIF           | TXIF           | SSPIF                   | CCP1IF   | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| PIR2    | —                                                                           | -              | —              | -              | —                       | —        | —       | CCP2IF  | 0                    | 0                               |

| T1CON   | TMR1CS1                                                                     | TMR1CS0        | T1CKPS1        | T1CKPS0        | T1OSCEN                 | T1SYNC   | _       | TMR10N  | 0000 00-0            | uuuu uu-u                       |

| T1GCON  | TMR1GE                                                                      | T1GPOL         | T1GTM          | T1GSPM         | T <u>1GGO</u> /<br>DONE | T1GVAL   | T1GSS1  | T1GSS0  | 0000 0x00            | 00x0 0x00                       |

| TMR1L   | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                |                |                |                         |          |         |         | xxxx xxxx            | uuuu uuuu                       |

| TMR1H   | Holding Regi                                                                | ster for the M | ost Significar | nt Byte of the | 16-bit TMR1 F           | Register |         |         | xxxx xxxx            | uuuu uuuu                       |

| TRISB   | TRISB7                                                                      | TRISB6         | TRISB5         | TRISB4         | TRISB3                  | TRISB2   | TRISB1  | TRISB0  | 1111 1111            | 1111 1111                       |

| TRISC   | TRISC7                                                                      | TRISC6         | TRISC5         | TRISC4         | TRISC3                  | TRISC2   | TRISC1  | TRISC0  | 1111 1111            | 1111 1111                       |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Compare.

## 16.4 AUSART Operation During Sleep

The AUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 16.4.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (refer to Section 16.3.2.4 "Synchronous Slave Reception Setup:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE global interrupt enable bit of the INTCON register is also set, then the Interrupt Service Routine at address 0004h will be called.

#### 16.4.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Transmission (refer to Section 16.3.2.2 "Synchronous Slave Transmission Setup:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE global interrupt enable bit is also set then the Interrupt Service Routine at address 0004h will be called.

| R/W-0                                 | R/W-0                                                                                                                                                                                      | R/W-0                                                                                                      | R/W-0                                                           | R/W-0                                                                         | R/W-0                               | R/W-0                         | R/W-0                         |  |  |  |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------|-------------------------------|-------------------------------|--|--|--|

| WCOL                                  | SSPOV                                                                                                                                                                                      | SSPEN                                                                                                      | СКР                                                             | SSPM3                                                                         | SSPM2                               | SSPM1                         | SSPM0                         |  |  |  |

| bit 7                                 | ·                                                                                                                                                                                          |                                                                                                            |                                                                 |                                                                               |                                     |                               | bit (                         |  |  |  |

| Lovende                               |                                                                                                                                                                                            |                                                                                                            |                                                                 |                                                                               |                                     |                               |                               |  |  |  |

| Legend:                               | ala hit                                                                                                                                                                                    | W = Writable                                                                                               | hit                                                             |                                                                               | monted hit rea                      | d oo '0'                      |                               |  |  |  |

| R = Readable bit<br>-n = Value at POR |                                                                                                                                                                                            | '1' = Bit is set                                                                                           |                                                                 | U = Unimplemented bit, read as '0'<br>'0' = Bit is cleared x = Bit is unknown |                                     |                               |                               |  |  |  |

| -n = value at POR                     |                                                                                                                                                                                            |                                                                                                            |                                                                 |                                                                               | aleu                                | X = DILIS UNK                 | IUWII                         |  |  |  |

| bit 7                                 | WCOL: Writ                                                                                                                                                                                 | te Collision Dete                                                                                          | ct bit                                                          |                                                                               |                                     |                               |                               |  |  |  |

|                                       | 1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared i                                                                                     |                                                                                                            |                                                                 |                                                                               |                                     |                               |                               |  |  |  |

|                                       | software)                                                                                                                                                                                  |                                                                                                            |                                                                 |                                                                               |                                     |                               |                               |  |  |  |

|                                       | 0 = No colli                                                                                                                                                                               |                                                                                                            |                                                                 |                                                                               |                                     |                               |                               |  |  |  |

| bit 6                                 | SSPOV: Receive Overflow Indicator bit                                                                                                                                                      |                                                                                                            |                                                                 |                                                                               |                                     |                               |                               |  |  |  |

|                                       | overflow<br>the SS<br>overflow<br>SSPBL                                                                                                                                                    | byte is received<br>w, the data in SS<br>PBUF, even if o<br>w bit is not set s<br>JF register.             | PSR is lost. C                                                  | Overflow can or<br>ing data, to a                                             | nly occur in Sla<br>void setting ov | ve mode. The uverflow. In Mas | iser must rea<br>ter mode, th |  |  |  |

|                                       | 0 = No ove                                                                                                                                                                                 |                                                                                                            |                                                                 |                                                                               |                                     |                               |                               |  |  |  |

| bit 5                                 | SSPEN: Synchronous Serial Port Enable bit                                                                                                                                                  |                                                                                                            |                                                                 |                                                                               |                                     |                               |                               |  |  |  |

|                                       | <ul> <li>1 = Enables serial port and configures SCK, SDO and SDI as serial port pins<sup>(1)</sup></li> <li>0 = Disables serial port and configures these pins as I/O port pins</li> </ul> |                                                                                                            |                                                                 |                                                                               |                                     |                               |                               |  |  |  |

| bit 4                                 | CKP: Clock                                                                                                                                                                                 | Polarity Select b                                                                                          | bit                                                             |                                                                               |                                     |                               |                               |  |  |  |

|                                       | <ul> <li>1 = Idle state for clock is a high level</li> <li>0 = Idle state for clock is a low level</li> </ul>                                                                              |                                                                                                            |                                                                 |                                                                               |                                     |                               |                               |  |  |  |

| bit 3-0                               | SSPM<3:0>: Synchronous Serial Port Mode Select bits                                                                                                                                        |                                                                                                            |                                                                 |                                                                               |                                     |                               |                               |  |  |  |

|                                       | 0001 = SPI<br>0010 = SPI<br>0011 = SPI<br>0100 = SPI                                                                                                                                       | Master mode, c<br>Master mode, c<br>Master mode, c<br>Master mode, c<br>Slave mode, clo<br>Slave mode, clo | lock = Fosc/1<br>lock = Fosc/6<br>lock = TMR2<br>lock = SCK pin | 6<br>4<br>o <u>utp</u> ut/2<br>. SS pin contro                                |                                     | can be used as                | I/O pin.                      |  |  |  |

| Note 1: V                             | When enabled, t                                                                                                                                                                            | hese pins must b                                                                                           | be properly co                                                  | nfigured as inp                                                               | out or output.                      |                               |                               |  |  |  |

|                                       | ,                                                                                                                                                                                          | •                                                                                                          | ,                                                               | - I                                                                           | •                                   |                               |                               |  |  |  |

## REGISTER 17-1: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (SPI MODE)

# PIC16(L)F722/3/4/6/7

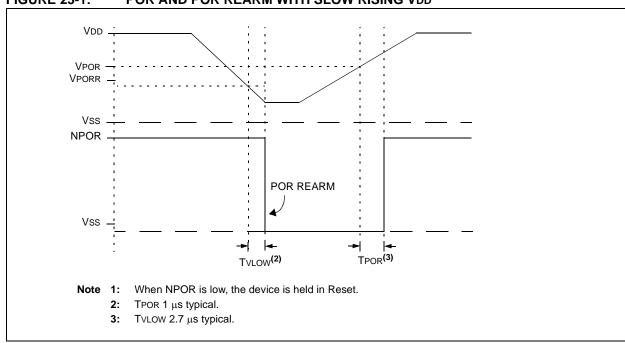

#### FIGURE 23-1: POR AND POR REARM WITH SLOW RISING VDD

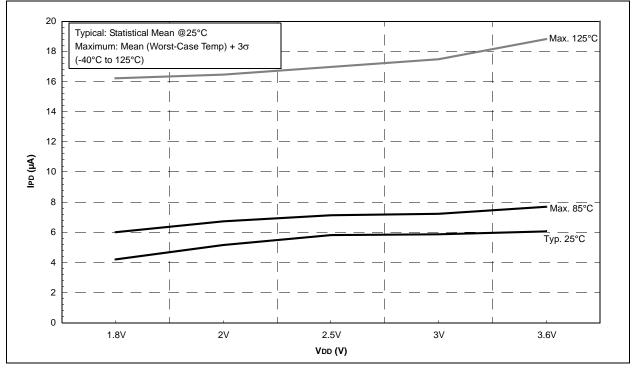

## 23.3 DC Characteristics: PIC16(L)F722/3/4/6/7-I/E (Power-Down)

| PIC16LF722/3/4/6/7<br>PIC16F722/3/4/6/7 |                            |          | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                          |      |                |       |                        |                                    |  |

|-----------------------------------------|----------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------|-------|------------------------|------------------------------------|--|

|                                         |                            |          | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |      |                |       |                        | °C for industrial                  |  |

| Param<br>No.                            | Device Characteristics Min |          | Typ† Max.<br>+85°C                                                                                                                                                                                                                                             |      | Max.<br>+125°C | Units | Conditions<br>VDD Note |                                    |  |

| -                                       | Power-down Base Current    |          |                                                                                                                                                                                                                                                                |      |                | VDD   | Note                   |                                    |  |

| D020                                    | rower-down base current    | (IFD). / | 0.02                                                                                                                                                                                                                                                           | 0.7  | 3.9            | μA    | 1.8                    | WDT, BOR, FVR, and T1OSC           |  |

|                                         |                            |          | 0.02                                                                                                                                                                                                                                                           | 1.0  | 4.3            | μΑ    | 3.0                    | disabled, all Peripherals Inactive |  |

| D020                                    |                            |          | 4.3                                                                                                                                                                                                                                                            | 10.2 | 17             | μΑ    | 1.8                    | WDT, BOR, FVR, and T1OSC           |  |

| 0020                                    |                            | _        | 5                                                                                                                                                                                                                                                              | 10.5 | 18             | μΑ    | 3.0                    | disabled, all Peripherals Inactive |  |

|                                         |                            |          | 5.5                                                                                                                                                                                                                                                            | 11.8 | 21             | μA    | 5.0                    |                                    |  |

| D021                                    |                            |          | 0.5                                                                                                                                                                                                                                                            | 1.7  | 4.1            | μΑ    | 1.8                    | LPWDT Current (Note 1)             |  |

|                                         |                            | _        | 0.8                                                                                                                                                                                                                                                            | 2.5  | 4.8            | μA    | 3.0                    |                                    |  |

| D021                                    |                            | _        | 6                                                                                                                                                                                                                                                              | 13.5 | 18             | μA    | 1.8                    | LPWDT Current (Note 1)             |  |

|                                         |                            | _        | 6.5                                                                                                                                                                                                                                                            | 14.5 | 19             | μΑ    | 3.0                    |                                    |  |

|                                         |                            | _        | 7.5                                                                                                                                                                                                                                                            | 16   | 22             | μΑ    | 5.0                    | 1                                  |  |

| D021A                                   |                            | —        | 8.5                                                                                                                                                                                                                                                            | 14   | 19             | μΑ    | 1.8                    | FVR current (Note 1. Note 3)       |  |

|                                         |                            | _        | 8.5                                                                                                                                                                                                                                                            | 14   | 20             | μA    | 3.0                    |                                    |  |

| D021A                                   |                            | —        | 23                                                                                                                                                                                                                                                             | 44   | 48             | μΑ    | 1.8                    | FVR current (Note 1, Note 3,       |  |

|                                         |                            |          | 25                                                                                                                                                                                                                                                             | 45   | 55             | μA    | 3.0                    | Note 5)                            |  |

|                                         |                            |          | 26                                                                                                                                                                                                                                                             | 60   | 70             | μA    | 5.0                    |                                    |  |

| D022                                    |                            | _        | —                                                                                                                                                                                                                                                              |      |                | μΑ    | 1.8                    | BOR Current (Note 1, Note 3)       |  |

|                                         |                            | —        | 7.5                                                                                                                                                                                                                                                            | 12   | 22             | μA    | 3.0                    |                                    |  |

| D022                                    |                            | —        | —                                                                                                                                                                                                                                                              | —    | —              | μA    | 1.8                    | BOR Current (Note 1, Note 3        |  |

|                                         |                            |          | 23                                                                                                                                                                                                                                                             | 42   | 49             | μΑ    | 3.0                    | Note 5)                            |  |

|                                         |                            | —        | 25                                                                                                                                                                                                                                                             | 46   | 50             | μΑ    | 5.0                    |                                    |  |

| D026                                    |                            | _        | 0.6                                                                                                                                                                                                                                                            | 2    |                | μΑ    | 1.8                    | T1OSC Current (Note 1)             |  |