Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

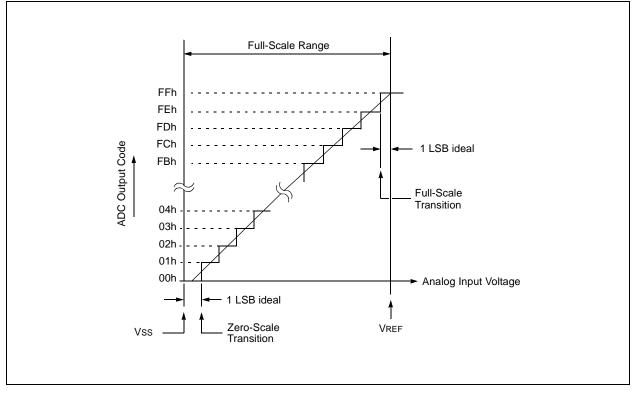

| Data Converters            | A/D 14x8b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 44-QFN (8x8)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f727-e-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 6.6.1 RE0/AN5<sup>(1)</sup>

Figure 6-22 shows the diagram for this pin. This pin is configurable to function as one of the following:

• a general purpose I/O

• an analog input for the ADC

| Note 1: | RE0/AN5 is available on |

|---------|-------------------------|

|         | PIC16F724/LF724 and     |

|         | PIC16F727/LF727 only.   |

#### 6.6.2 RE1/AN6<sup>(1)</sup>

Figure 6-22 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

| Note 1: | RE0/AN5 is available on |

|---------|-------------------------|

|         | PIC16F724/LF724 and     |

|         | PIC16F727/LF727 only.   |

#### 6.6.3 RE2/AN7<sup>(1)</sup>

Figure 6-22 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

Note 1: RE0/AN5 is available on PIC16F724/LF724 and PIC16F727/LF727 only.

#### 6.6.4 RE3/MCLR/VPP

Figure 6-23 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose input

- as Master Clear Reset with weak pull-up

- · a programming voltage reference input

#### 7.6 External Clock Modes

#### 7.6.1 OSCILLATOR START-UP TIMER (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations on the OSC1 pin before the device is released from Reset. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

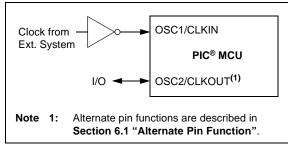

#### 7.6.2 EC MODE

The External Clock (EC) mode allows an externally generated logic level as the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input and the OSC2 is available for general purpose I/O. Figure 7-2 shows the pin connections for EC mode.

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### FIGURE 7-2: EXTERNAL CLOCK (EC) MODE OPERATION

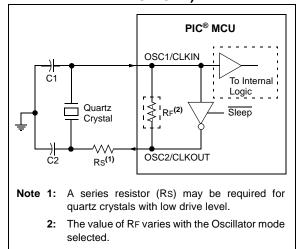

#### 7.6.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 7-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

LP Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is best suited to drive resonators with a low drive level specification, for example, tuning fork type crystals.

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 7-3 and Figure 7-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

#### FIGURE 7-3: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices (DS00826)

- AN849, Basic PIC<sup>®</sup> Oscillator Design (DS00849)

- AN943, Practical PIC<sup>®</sup> Oscillator Analysis and Design (DS00943)

- AN949, Making Your Oscillator Work (DS00949).

#### REGISTER 8-1: CONFIG1: CONFIGURATION WORD REGISTER 1 (CONTINUED)

- bit 4 **PWRTE:** Power-up Timer Enable bit 1 = PWRT disabled

- 1 = PWRT disabled0 = PWRT enabled

- bit 3 WDTE: Watchdog Timer Enable bit 1 = WDT enabled

- 1 = WDT enabled0 = WDT disabled

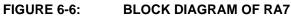

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = RC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, RC on RA7/OSC1/CLKIN

- 110 = RCIO oscillator: I/O function on RA6/OSC2/CLKOUT pin, RC on RA7/OSC1/CLKIN

- 101 = INTOSC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN

- 100 = INTOSCIO oscillator: I/O function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN

- 011 = EC: I/O function on RA6/OSC2/CLKOUT pin, CLKIN on RA7/OSC1/CLKIN

- 010 = HS oscillator: High-speed crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN

- 001 = XT oscillator: Crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN

- 000 = LP oscillator: Low-power crystal on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN

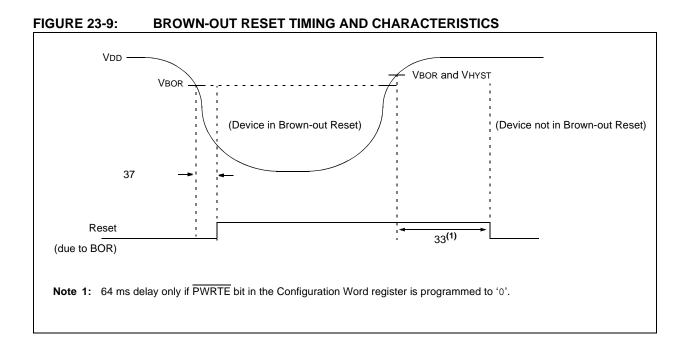

Note 1: Enabling Brown-out Reset does not automatically enable Power-up Timer.

- 2: The entire program memory will be erased when the code protection is turned off.

- 3: When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.

- 4: MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

#### REGISTER 8-2: CONFIG2: CONFIGURATION WORD REGISTER 2

|        | U-1 <sup>(1)</sup> U-1 <sup>(1)</sup> |  | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> |

|--------|---------------------------------------|--|--------------------|--------------------|--------------------|--------------------|

|        |                                       |  | _                  | —                  | —                  | —                  |

| bit 15 |                                       |  |                    |                    |                    | bit 8              |

| U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | R/P-1   | R/P-1   | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> U-1 <sup>(1)</sup> |       |

|--------------------|--------------------|---------|---------|--------------------|--------------------|---------------------------------------|-------|

| —                  | —                  | VCAPEN1 | VCAPEN0 | —                  | —                  | _                                     | —     |

| bit 7              |                    |         |         |                    |                    |                                       | bit 0 |

| Legend:           | P = Programmable bit |                                    |                    |  |  |  |

|-------------------|----------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 13-6 Unimplemented: Read as '1'

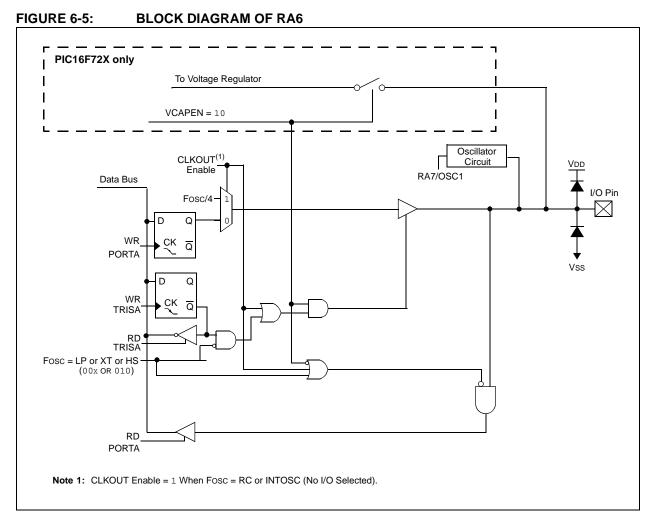

bit 5-4 VCAPEN<1:0>: Voltage Regulator Capacitor Enable bits For the PIC16LF72X: These bits are ignored. All VCAP pin functions are disabled. For the PIC16F72X: 00 = VCAP functionality is enabled on RA0 01 = VCAP functionality is enabled on RA5 10 = VCAP functionality is enabled on RA6 11 = All VCAP functions are disabled (not recommended) bit 3-0 Unimplemented: Read as '1'

**Note 1:** MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

#### 8.2 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out using  $ICSP^{TM}$  for verification purposes.

| Note: | The entire Flash program memory will be   |  |  |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | erased when the code protection is turned |  |  |  |  |  |  |  |  |  |  |

|       | off. See the "PIC16(L)F72X Memory         |  |  |  |  |  |  |  |  |  |  |

|       | Programming Specification" (DS41332)      |  |  |  |  |  |  |  |  |  |  |

|       | for more information.                     |  |  |  |  |  |  |  |  |  |  |

#### 8.3 User ID

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify mode. Only the Least Significant seven bits of the ID locations are reported when using MPLAB IDE. See the "*PIC16(L)F72X Memory Programming Specification*" (DS41332) for more information.

| U-0             | R/W-0                        | R/W-0                 | R/W-0          | R/W-0             | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |

|-----------------|------------------------------|-----------------------|----------------|-------------------|-----------------|-----------------|---------|--|--|--|--|

|                 | TOUTPS3                      | TOUTPS2               | TOUTPS1        | TOUTPS0           | TMR2ON          | T2CKPS1         | T2CKPS0 |  |  |  |  |

| bit 7           |                              |                       |                |                   |                 |                 | bit 0   |  |  |  |  |

|                 |                              |                       |                |                   |                 |                 |         |  |  |  |  |

| Legend:         |                              |                       |                |                   |                 |                 |         |  |  |  |  |

| R = Readable    | bit                          | W = Writable          | bit            | U = Unimplen      | nented bit, rea | d as '0'        |         |  |  |  |  |

| -n = Value at P | POR                          | '1' = Bit is set      |                | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |  |  |  |  |

| bit 7           | Unimplemen                   | ted: Read as '        | 0'             |                   |                 |                 |         |  |  |  |  |

| bit 6-3         | TOUTPS<3:0                   | >: Timer2 Out         | out Postscaler | Select bits       |                 |                 |         |  |  |  |  |

|                 | 0000 = 1:1 P                 | -                     |                |                   |                 |                 |         |  |  |  |  |

|                 | 0001 = 1:2 P                 | ostscaler             |                |                   |                 |                 |         |  |  |  |  |

|                 | 0010 = 1:3 P                 | ostscaler             |                |                   |                 |                 |         |  |  |  |  |

|                 |                              | 0011 = 1:4 Postscaler |                |                   |                 |                 |         |  |  |  |  |

|                 | 0100 = 1:5 Postscaler        |                       |                |                   |                 |                 |         |  |  |  |  |

|                 | 0101 = 1:6 P                 |                       |                |                   |                 |                 |         |  |  |  |  |

|                 | 0110 = 1:7 P<br>0111 = 1:8 P |                       |                |                   |                 |                 |         |  |  |  |  |

|                 | 1000 = 1:9 P                 |                       |                |                   |                 |                 |         |  |  |  |  |

|                 | 1000 = 1.31                  |                       |                |                   |                 |                 |         |  |  |  |  |

|                 | 1010 = 1:11                  |                       |                |                   |                 |                 |         |  |  |  |  |

|                 | 1011 = <b>1:12</b>           | Postscaler            |                |                   |                 |                 |         |  |  |  |  |

|                 | 1100 <b>= 1:13</b>           | Postscaler            |                |                   |                 |                 |         |  |  |  |  |

|                 | 1101 <b>= 1:14</b>           |                       |                |                   |                 |                 |         |  |  |  |  |

|                 | 1110 <b>= 1:15</b>           |                       |                |                   |                 |                 |         |  |  |  |  |

|                 | 1111 = 1:16                  |                       |                |                   |                 |                 |         |  |  |  |  |

| bit 2           | TMR2ON: Timer2 On bit        |                       |                |                   |                 |                 |         |  |  |  |  |

|                 | 1 = Timer2 is                |                       |                |                   |                 |                 |         |  |  |  |  |

|                 | 0 = Timer2 is                | s off                 |                |                   |                 |                 |         |  |  |  |  |

| bit 1-0         | T2CKPS<1:0                   | >: Timer2 Cloc        | k Prescale Sel | ect bits          |                 |                 |         |  |  |  |  |

|                 | 00 = Prescale                |                       |                |                   |                 |                 |         |  |  |  |  |

|                 | 01 = Prescale                | -                     |                |                   |                 |                 |         |  |  |  |  |

|                 | 1x = Prescale                | er is 16              |                |                   |                 |                 |         |  |  |  |  |

| TABLE 13-1:     | SUMMAR                       |                       | FRS ASSO       | CIATED WITH       | H TIMER2        |                 |         |  |  |  |  |

#### REGISTER 13-1: T2CON: TIMER2 CONTROL REGISTER

| IADEE  | ABLE 19-1. COMMANY OF REGISTERS ASSOCIATED WITH IMPERZ |         |           |           |         |        |         |         |                      |                                 |  |  |  |

|--------|--------------------------------------------------------|---------|-----------|-----------|---------|--------|---------|---------|----------------------|---------------------------------|--|--|--|

| Name   | Bit 7                                                  | Bit 6   | Bit 5     | Bit 4     | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |  |  |  |

| INTCON | GIE                                                    | PEIE    | T0IE      | INTE      | RBIE    | T0IF   | INTF    | RBIF    | 0000 000x            | 0000 000x                       |  |  |  |

| PIE1   | TMR1GIE                                                | ADIE    | RCIE      | TXIE      | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |  |  |  |

| PIR1   | TMR1GIF                                                | ADIF    | RCIF      | TXIF      | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |  |  |  |

| PR2    | Timer2 Mod                                             |         | 1111 1111 | 1111 1111 |         |        |         |         |                      |                                 |  |  |  |

| TMR2   | Holding Re                                             |         | 0000 0000 | 0000 0000 |         |        |         |         |                      |                                 |  |  |  |

| T2CON  | _                                                      | TOUTPS3 | TOUTPS2   | TOUTPS1   | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |  |  |  |

x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module. Legend:

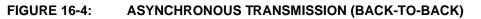

#### TABLE 16-1: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name   | Bit 7     | Bit 6  | Bit 5     | Bit 4     | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-----------|--------|-----------|-----------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE       | PEIE   | TOIE      | INTE      | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE   | ADIE   | RCIE      | TXIE      | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF   | ADIF   | RCIF      | TXIF      | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN      | RX9    | SREN      | CREN      | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7      | BRG6   | BRG5      | BRG4      | BRG3   | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7    | TRISC6 | TRISC5    | TRISC4    | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXREG  | AUSART TI |        | 0000 0000 | 0000 0000 |        |        |        |        |                      |                                 |

| TXSTA  | CSRC      | TX9    | TXEN      | SYNC      | —      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Asynchronous Transmission.

#### 16.2 AUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit timer that is dedicated to the support of both the asynchronous and synchronous AUSART operation.

The SPBRG register determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by the BRGH bit of the TXSTA register. In Synchronous mode, the BRGH bit is ignored.

Table 16-3 contains the formulas for determining the baud rate. Example 16-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various asynchronous modes have been computed for your convenience and are shown in Table 16-3. It may be advantageous to use the high baud rate (BRGH = 1), to reduce the baud rate error.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

#### EXAMPLE 16-1: CALCULATING BAUD RATE ERROR

For a device with FOSC of 16 MHz, desired baud rate of 9600, and Asynchronous mode with SYNC = 0 and BRGH = 0 (as seen in Table 16-3):

Desired Baud Rate =

$$\frac{FOSC}{64(SPBRG+1)}$$

Solving for SPBRG:

$$SPBRG = \left(\frac{FOSC}{64(Desired Baud Rate)}\right) - 1$$

$$= \left(\frac{16000000}{64(9600)}\right) - 1$$

$$= [25.042] = 25$$

$$Actual Baud Rate = \frac{16000000}{64(25+1)}$$

$$= 9615$$

% Error =  $\left(\frac{Actual Baud Rate - Desired Baud Rate}{Desired Baud Rate}\right) 100$

$$= \left(\frac{9615 - 9600}{9600}\right) 100 = 0.16\%$$

| Configur | ation Bits |              | Baud Rate Formula |  |  |

|----------|------------|--------------|-------------------|--|--|

| SYNC     | BRGH       | AUSART Mode  | Baud Rate Formula |  |  |

| 0        | 0          | Asynchronous | Fosc/[64 (n+1)]   |  |  |

| 0        | 1          | Asynchronous | Fosc/[16 (n+1)]   |  |  |

| 1        | x          | Synchronous  | Fosc/[4 (n+1)]    |  |  |

#### TABLE 16-3:BAUD RATE FORMULAS

Legend: x = Don't care, n = value of SPBRG register

#### TABLE 16-4: REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| RCSTA | SPEN  | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | x000 000x            | 0000 000x                       |

| SPBRG | BRG7  | BRG6  | BRG5  | BRG4  | BRG3  | BRG2  | BRG1  | BRG0  | 0000 0000            | 0000 0000                       |

| TXSTA | CSRC  | TX9   | TXEN  | SYNC  | _     | BRGH  | TRMT  | TX9D  | 0000 -010            | 0000 -010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for the Baud Rate Generator.

### 16.3.2.3 AUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 16.3.1.4 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never Idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE interrupt enable bit of the PIE1 register is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 16.3.2.4 Synchronous Slave Reception Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 3. If 9-bit reception is desired, set the RX9 bit.

- 4. Verify address detection is disabled by clearing the ADDEN bit of the RCSTA register.

- 5. Set the CREN bit to enable reception.

- The RCIF bit of the PIR1 register will be set when reception is complete. An interrupt will be generated if the RCIE bit of the PIE1 register was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register.

| Name   | Bit 7    | Bit 6       | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|-------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE        | TOIE       | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE  | ADIE        | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF  | ADIF        | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCREG  | AUSART R | eceive Data | a Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN     | RX9         | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000X            | 0000 000X                       |

| TRISC  | TRISC7   | TRISC6      | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC     | TX9         | TXEN       | SYNC   | _      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

#### TABLE 16-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Reception.

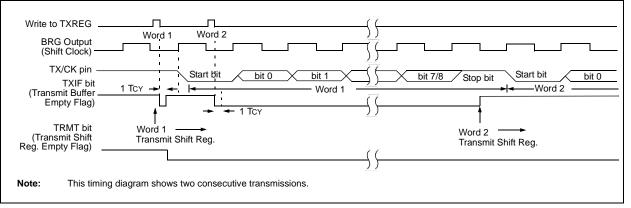

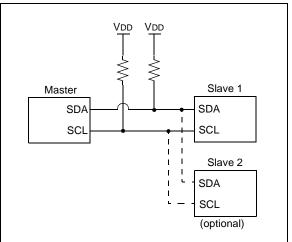

### 17.2 I<sup>2</sup>C Mode

The SSP module, in  $I^2C$  mode, implements all slave functions, except general call support. It provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the  $I^2C$  Standard mode specifications:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- Start and Stop bit interrupts enabled to support firmware Master mode

- Address masking

Two pins are used for data transfer; the SCL pin (clock line) and the SDA pin (data line). The user must configure the two pin's data direction bits as inputs in the appropriate TRIS register. Upon enabling  $I^2C$  mode, the  $I^2C$  slew rate limiters in the I/O pads are controlled by the SMP bit of SSPSTAT register. The SSP module functions are enabled by setting the SSPEN bit of SSPCON register.

Data is sampled on the rising edge and shifted out on the falling edge of the clock. This ensures that the SDA signal is valid during the SCL high time. The SCL clock input must have minimum high and low times for proper operation. Refer to **Section 23.0** "**Electrical Specifications**".

### FIGURE 17-7: I<sup>2</sup>C MODE BLOCK DIAGRAM

### FIGURE 17-8: TYPICAL I<sup>2</sup>C

#### CONNECTIONS

The SSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. They are:

- SSP Control (SSPCON) register

- SSP Status (SSPSTAT) register

- Serial Receive/Transmit Buffer (SSPBUF) register

- SSP Shift Register (SSPSR), not directly accessible

- SSP Address (SSPADD) register

- SSP Address Mask (SSPMSK) register

#### 17.2.1 HARDWARE SETUP

Selection of  $I^2C$  mode, with the SSPEN bit of the SSPCON register set, forces the SCL and SDA pins to be open drain, provided these pins are programmed as inputs by setting the appropriate TRISC bits. The SSP module will override the input state with the output data, when required, such as for Acknowledge and slave-transmitter sequences.

**Note:** Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module

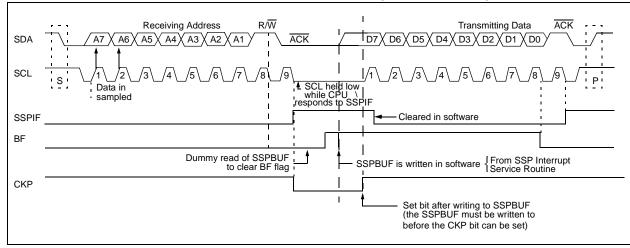

#### 17.2.6 TRANSMISSION

When the R/W bit of the received address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set and the slave will respond to the master by reading out data. After the address match, an ACK pulse is generated by the slave hardware and the SCL pin is held low (clock is automatically stretched) until the slave is ready to respond. See **Section 17.2.7 "Clock Stretching"**. The data the slave will transmit must be loaded into the SSPBUF register, which sets the BF bit. The SCL line is released by setting the CKP bit of the SSPCON register.

An SSP interrupt is generated for each transferred data byte. The SSPIF flag bit of the PIR1 register initiates an SSP interrupt, and must be cleared by software before the next byte is transmitted. The BF bit of the SSPSTAT register is cleared on the falling edge of the eighth received clock pulse. The SSPIF flag bit is set on the falling edge of the ninth clock pulse. Following the eighth falling clock edge, control of the SDA line is released back to the master so that the master can acknowledge or not acknowledge the response. If the master sends a not acknowledge, the slave's transmission is complete and the slave must monitor for the next Start condition. If the master acknowledges, control of the bus is returned to the slave to transmit another byte of data. Just as with the previous byte, the clock is stretched by the slave, data must be loaded into the SSPBUF and CKP must be set to release the clock line (SCL).

#### FIGURE 17-12: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

| MOVF             | Move f                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                      |  |  |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Description:     | The contents of register f is<br>moved to a destination dependent<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                           |  |  |  |  |  |

| MOVWF            | Move W to f                                     |  |  |  |  |  |

|------------------|-------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] MOVWF f                               |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                               |  |  |  |  |  |

| Operation:       | $(W) \to (f)$                                   |  |  |  |  |  |

| Status Affected: | None                                            |  |  |  |  |  |

| Description:     | Move data from W register to register 'f'.      |  |  |  |  |  |

| Words:           | 1                                               |  |  |  |  |  |

| Cycles:          | 1                                               |  |  |  |  |  |

| Example:         | MOVW OPTION<br>F                                |  |  |  |  |  |

|                  | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F |  |  |  |  |  |

|                  | After Instruction<br>OPTION = 0x4F              |  |  |  |  |  |

|                  | W = 0x4F                                        |  |  |  |  |  |

| MOVLW            | Move literal to W                                                                         |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                         |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                       |  |  |  |  |  |

| Status Affected: | None                                                                                      |  |  |  |  |  |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |  |  |  |  |  |

| Words:           | 1                                                                                         |  |  |  |  |  |

| Cycles:          | 1                                                                                         |  |  |  |  |  |

| Example:         | MOVLW 0x5A                                                                                |  |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                             |  |  |  |  |  |

| NOP              | No Operation  |  |  |  |  |

|------------------|---------------|--|--|--|--|

| Syntax:          | [label] NOP   |  |  |  |  |

| Operands:        | None          |  |  |  |  |

| Operation:       | No operation  |  |  |  |  |

| Status Affected: | None          |  |  |  |  |

| Description:     | No operation. |  |  |  |  |

| Words:           | 1             |  |  |  |  |

| Cycles:          | 1             |  |  |  |  |

| Example:         | NOP           |  |  |  |  |

| RLF              | Rotate Left f through Carry                                                                                                                                                                                          |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                             |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                   |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                                |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is stored<br>back in register 'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Example:         | RLF REG1,0                                                                                                                                                                                                           |  |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                                                                                   |  |  |  |  |  |  |

|                  | REG1 = 1110 0110                                                                                                                                                                                                     |  |  |  |  |  |  |

|                  | C = 0                                                                                                                                                                                                                |  |  |  |  |  |  |

|                  | After Instruction                                                                                                                                                                                                    |  |  |  |  |  |  |

|                  | REG1 = 1110 0110                                                                                                                                                                                                     |  |  |  |  |  |  |

|                  | $W = 1100 \ 1100$                                                                                                                                                                                                    |  |  |  |  |  |  |

|                  | C = 1                                                                                                                                                                                                                |  |  |  |  |  |  |

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                                 |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                                    |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                             |  |  |  |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT,} \\ 0 \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \text{PD} \end{array}$                                                                       |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                                           |  |  |  |

| Description:     | The power-down Status bit, $\overline{\text{PD}}$ is<br>cleared. Time-out Status bit, $\overline{\text{TO}}$<br>is set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped. |  |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                              |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                    |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                                 |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                     |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is placed<br>back in register 'f'. |  |  |  |  |  |

|                  | C Register f                                                                                                                                                                                                          |  |  |  |  |  |

| SUBLW            | Subtract W from literal    |                                                                                  |  |  |  |  |

|------------------|----------------------------|----------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k   |                                                                                  |  |  |  |  |

| Operands:        | $0 \le k \le 255$          |                                                                                  |  |  |  |  |

| Operation:       | $k \text{ - } (W) \to (W)$ |                                                                                  |  |  |  |  |

| Status Affected: | C, DC, Z                   |                                                                                  |  |  |  |  |

| Description:     | complemen                  | ster is subtracted (2's<br>t method) from the 8-bit<br>e result is placed in the |  |  |  |  |

|                  | <b>C</b> = 0               | W > k                                                                            |  |  |  |  |

|                  | <b>C</b> = 1               | $W \leq k$                                                                       |  |  |  |  |

DC = 0

**DC** = 1

W<3:0> > k<3:0>

$W < 3:0 > \le k < 3:0 >$

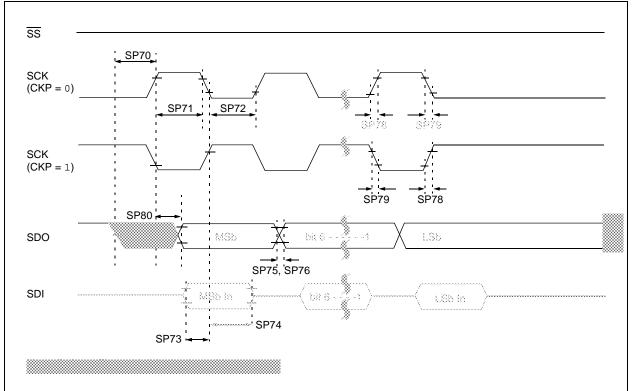

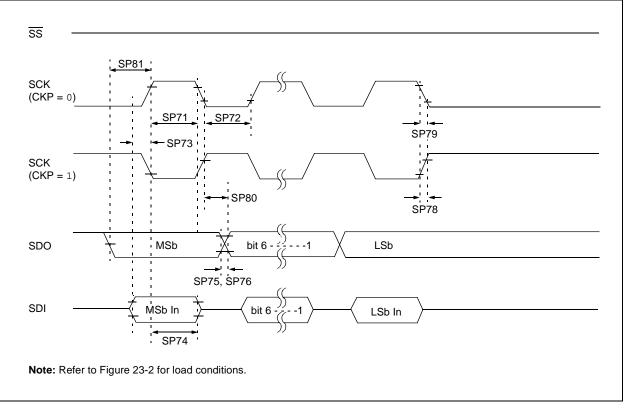

#### FIGURE 23-16: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

| Param.<br>No. | Symbol                | Characte                   | eristic      | Min.       | Max. | Units                                | Conditions                                  |

|---------------|-----------------------|----------------------------|--------------|------------|------|--------------------------------------|---------------------------------------------|

| SP100* Thigh  |                       | Clock high time            | 100 kHz mode | 4.0        | —    | μs                                   | Device must operate at a minimum of 1.5 MHz |

|               |                       |                            | 400 kHz mode | 0.6        | _    | μs                                   | Device must operate at a minimum of 10 MHz  |

|               |                       |                            | SSP Module   | 1.5Tcy     | _    |                                      |                                             |

| SP101* TLOW   |                       | Clock low time             | 100 kHz mode | 4.7        | _    | μs                                   | Device must operate at a minimum of 1.5 MHz |

|               |                       |                            | 400 kHz mode | 1.3        | _    | μS                                   | Device must operate at a minimum of 10 MHz  |

|               |                       |                            | SSP Module   | 1.5Tcy     | _    |                                      |                                             |

| SP102* Tr     | SDA and SCL rise time | 100 kHz mode               | —            | 1000       | ns   |                                      |                                             |

|               |                       | 400 kHz mode               | 20 + 0.1CB   | 300        | ns   | CB is specified to be from 10-400 pF |                                             |

| SP103* TF     | SDA and SCL fall time | 100 kHz mode               | —            | 250        | ns   |                                      |                                             |

|               |                       |                            | 400 kHz mode | 20 + 0.1CB | 250  | ns                                   | CB is specified to be from 10-400 pF        |

| SP106*        | THD:DAT               | Data input hold time       | 100 kHz mode | 0          |      | ns                                   |                                             |

|               |                       |                            | 400 kHz mode | 0          | 0.9  | μs                                   | -                                           |

| SP107*        | TSU:DAT               | Data input setup time      | 100 kHz mode | 250        |      | ns                                   | (Note 2)                                    |

|               |                       |                            | 400 kHz mode | 100        |      | ns                                   | -                                           |

| SP109*        | ΤΑΑ                   | Output valid from<br>clock | 100 kHz mode | —          | 3500 | ns                                   | (Note 1)                                    |

|               |                       |                            | 400 kHz mode | _          |      | ns                                   |                                             |

| SP110*        | TBUF                  | Bus free time              | 100 kHz mode | 4.7        | _    | μs                                   | Time the bus must be free                   |

|               |                       |                            | 400 kHz mode | 1.3        | —    | μs                                   | before a new transmission can start         |

| SP111         | Св                    | Bus capacitive loading     |              | —          | 400  | pF                                   |                                             |

#### TABLE 23-13: I<sup>2</sup>C BUS DATA REQUIREMENTS

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement TsU:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

#### © 2007-2015 Microchip Technology Inc.

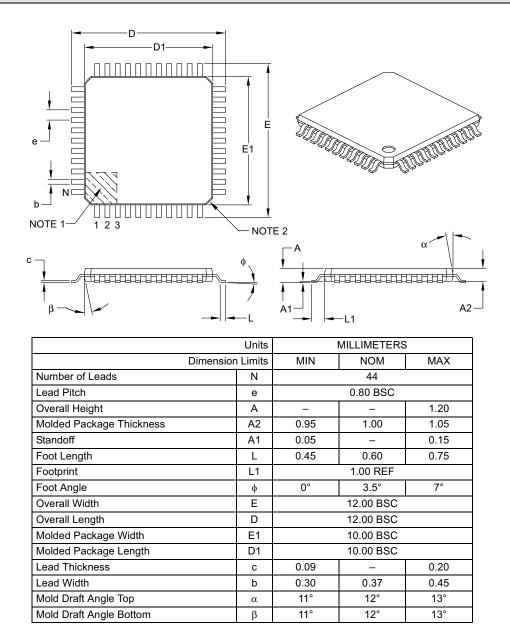

#### 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

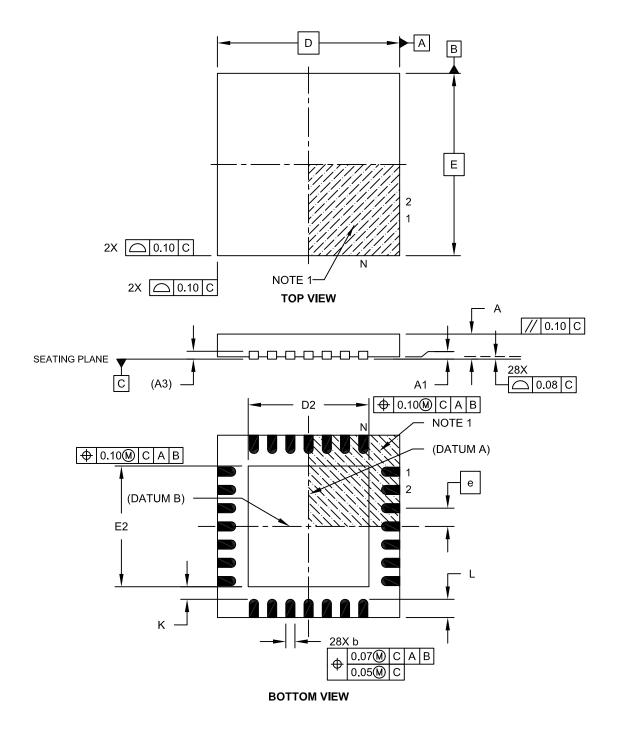

#### 28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-152A Sheet 1 of 2