Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 36                                                                      |

| Program Memory Size        | 14KB (8K x 14)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 368 × 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                             |

| Data Converters            | A/D 14x8b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f727-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

## 2.0 MEMORY ORGANIZATION

## 2.1 Program Memory Organization

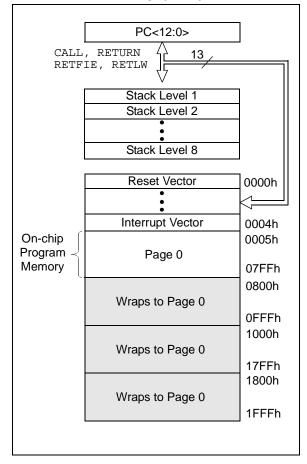

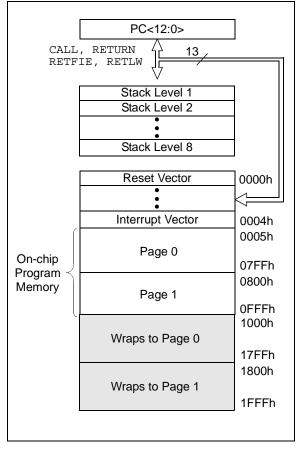

The PIC16(L)F722/3/4/6/7 has a 13-bit program counter capable of addressing a 2K x 14 program memory space for the PIC16F722/LF722 (0000h-07FFh), a 4K x 14 program memory space for PIC16F723/LF723 and PIC16F724/LF724 the (0000h-0FFFh) and an 8K x 14 program memory space for the PIC16F726/LF726 and PIC16F727/LF727 (0000h-1FFFh). Accessing a location above the memory boundaries for the PIC16F722/LF722 will cause a wrap-around within the first 2K x 14 program memory space. Accessing a location above the memory boundaries for the PIC16F723/LF723 and PIC16F724/LF724 will cause a wrap-around within the first 4K x 14 program memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16F722/LF722

## FIGURE 2-2:

## PROGRAM MEMORY MAP AND STACK FOR THE PIC16F723/LF723 AND PIC16F724/LF724

### 4.5.3 PIE2 REGISTER

Γ.

bit 0

The PIE2 register contains the interrupt enable bits, as shown in Register 4-3.

## Note: Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

### REGISTER 4-3: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

| —     | —   | —   | —   | —   | —   |     | CCP2IE |

| bit 7 |     |     |     |     |     |     | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

## bit 7-1 Unimplemented: Read as '0'

CCP2IE: CCP2 Interrupt Enable bit

1 = Enables the CCP2 interrupt

0 = Disables the CCP2 interrupt

## TABLE 6-1: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name                   | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|--------|---------|---------|---------|---------|---------|---------|----------------------|---------------------------------|

| ADCON0                 | _      | _      | CHS3    | CHS2    | CHS1    | CHS0    | GO/DONE | ADON    | 0000 0000            | 0000 0000                       |

| ADCON1                 | _      | ADCS2  | ADCS1   | ADCS0   | _       | _       | ADREF1  | ADREF0  | -00000               | -00000                          |

| ANSELA                 | _      | _      | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   | 11 1111              | 11 1111                         |

| APFCON                 | _      | _      | _       | _       | _       | _       | SSSEL   | CCP2SEL | 00                   | 00                              |

| CPSCON0                | CPSON  | _      | _       | _       | CPSRNG1 | CPSRNG0 | CPSOUT  | TOXCS   | 0 0000               | 0 0000                          |

| CPSCON1                | _      | _      | _       | _       | CPSCH3  | CPSCH2  | CPSCH1  | CPSCH0  | 0000                 | 0000                            |

| CONFIG2 <sup>(1)</sup> | _      | _      | VCAPEN1 | VCAPEN0 | _       | _       | —       | _       | —                    | —                               |

| OPTION_REG             | RBPU   | INTEDG | TOCS    | T0SE    | PSA     | PS2     | PS1     | PS0     | 1111 1111            | 1111 1111                       |

| PORTA                  | RA7    | RA6    | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | xxxx xxxx            | xxxx xxxx                       |

| SSPCON                 | WCOL   | SSPOV  | SSPEN   | CKP     | SSPM3   | SSPM2   | SSPM1   | SSPM0   | 0000 0000            | 0000 0000                       |

| TRISA                  | TRISA7 | TRISA6 | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 1111 1111            | 1111 1111                       |

$\label{eq:Legend: x = unknown, u = unchanged, - = unimplemented locations read as `0'. Shaded cells are not used by PORTA.$

Note 1: PIC16F72X only.

## 6.6.1 RE0/AN5<sup>(1)</sup>

Figure 6-22 shows the diagram for this pin. This pin is configurable to function as one of the following:

• a general purpose I/O

• an analog input for the ADC

| Note 1: | RE0/AN5 is available on |

|---------|-------------------------|

|         | PIC16F724/LF724 and     |

|         | PIC16F727/LF727 only.   |

## 6.6.2 RE1/AN6<sup>(1)</sup>

Figure 6-22 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

| Note 1: | RE0/AN5 is available on |

|---------|-------------------------|

|         | PIC16F724/LF724 and     |

|         | PIC16F727/LF727 only.   |

### 6.6.3 RE2/AN7<sup>(1)</sup>

Figure 6-22 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

Note 1: RE0/AN5 is available on PIC16F724/LF724 and PIC16F727/LF727 only.

### 6.6.4 RE3/MCLR/VPP

Figure 6-23 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose input

- as Master Clear Reset with weak pull-up

- · a programming voltage reference input

## 7.2 Clock Source Modes

Clock source modes can be classified as external or internal.

- Internal clock source (INTOSC) is contained within the oscillator module and derived from a 500 kHz high precision oscillator. The oscillator module has eight selectable output frequencies, with a maximum internal frequency of 16 MHz.

- External clock modes rely on external circuitry for the clock source. Examples are: oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

The system clock can be selected between external or internal clock sources via the FOSC bits of the Configuration Word 1.

## 7.3 Internal Clock Modes

The oscillator module has eight output frequencies derived from a 500 kHz high precision oscillator. The IRCF bits of the OSCCON register select the postscaler applied to the clock source dividing the frequency by 1, 2, 4 or 8. Setting the PLLEN bit of the Configuration Word 1 locks the internal clock source to 16 MHz before the postscaler is selected by the IRCF bits. The PLLEN bit must be set or cleared at the time of programming; therefore, only the upper or low four clock source frequencies are selectable in software.

## 7.3.1 INTOSC AND INTOSCIO MODES

The INTOSC and INTOSCIO modes configure the internal oscillators as the system clock source when the device is programmed using the oscillator selection or the FOSC<2:0> bits in the CONFIG1 register. See **Section 8.0** "**Device Configuration**" for more information.

In INTOSC mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT outputs the selected internal oscillator frequency divided by 4. The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

In INTOSCIO mode, OSC1/CLKIN and OSC2/CLKOUT are available for general purpose I/O.

## 7.3.2 FREQUENCY SELECT BITS (IRCF)

The output of the 500 kHz INTOSC and 16 MHz INTOSC, with Phase-Locked Loop enabled, connect to a postscaler and multiplexer (see Figure 7-1). The Internal Oscillator Frequency Select bits (IRCF) of the OSCCON register select the frequency output of the internal oscillator. Depending upon the PLLEN bit, one of four frequencies of two frequency sets can be selected via software:

If PLLEN = 1, frequency selection is as follows:

- 16 MHz

- 8 MHz (default after Reset)

- 4 MHz

- 2 MHz

- If PLLEN = 0, frequency selection is as follows:

- 500 kHz

- 250 kHz (default after Reset)

- 125 kHz

- 62.5 kHz

Note: Following any Reset, the IRCF<1:0> bits of the OSCCON register are set to '10' and the frequency selection is set to 8 MHz or 250 kHz. The user can modify the IRCF bits to select a different frequency.

There is no start-up delay before a new frequency selected in the IRCF bits takes effect. This is because the old and new frequencies are derived from INTOSC via the postscaler and multiplexer.

Start-up delay specifications are located in the Table 23-2 in Section 23.0 "Electrical Specifications".

| REGISTER      | <b>19-2.</b> ADCO              |                        | ITROL REG        |                    |                    |                  |        |

|---------------|--------------------------------|------------------------|------------------|--------------------|--------------------|------------------|--------|

| U-0           | R/W-0                          | R/W-0                  | R/W-0            | U-0                | U-0                | R/W-0            | R/W-0  |

| _             | ADCS2                          | ADCS1                  | ADCS0            | _                  | _                  | ADREF1           | ADREF0 |

| bit 7         |                                |                        |                  |                    |                    |                  | bit 0  |

| Legend:       |                                |                        |                  |                    |                    |                  |        |

| R = Readabl   | le bit                         | W = Writable bi        | t                | U = Unimpleme      | ented bit, read as | s 'O'            |        |

| -n = Value at | t POR                          | '1' = Bit is set       |                  | '0' = Bit is clear | red                | x = Bit is unkno | wn     |

|               |                                |                        |                  |                    |                    |                  |        |

| bit 7         | Unimplemente                   | ed: Read as '0'        |                  |                    |                    |                  |        |

| bit 6-4       | ADCS<2:0>: A                   | /D Conversion C        | lock Select bits |                    |                    |                  |        |

|               | 000 = Fosc/2                   |                        |                  |                    |                    |                  |        |

|               | 001 = Fosc/8                   |                        |                  |                    |                    |                  |        |

|               | 010 = Fosc/32                  | -                      |                  |                    |                    |                  |        |

|               | · · ·                          | ock supplied from      | a dedicated RC   | Coscillator)       |                    |                  |        |

|               | 100 = Fosc/4<br>101 = Fosc/16  |                        |                  |                    |                    |                  |        |

|               | 101 = FOSC/10<br>110 = FOSC/64 | -                      |                  |                    |                    |                  |        |

|               |                                | ,<br>ock supplied from | a dedicated RC   | coscillator)       |                    |                  |        |

| bit 3-2       | Unimplemente                   | ••                     |                  | ,                  |                    |                  |        |

| bit 1-0       | ADREF<1:0>:                    | Voltage Referend       | e Configuration  | bits               |                    |                  |        |

|               |                                | connected to VDD       | 0                |                    |                    |                  |        |

|               | 10 = VREF is c                 | connected to exte      | rnal VREF (RA3   | /AN3)              |                    |                  |        |

|               |                                |                        | nal Fixed Voltag |                    |                    |                  |        |

## REGISTER 9-2: ADCON1: A/D CONTROL REGISTER 1

#### REGISTER 9-3: ADRES: ADC RESULT REGISTER

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 | ADRES1 | ADRES0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 **ADRES<7:0>**: ADC Result Register bits 8-bit conversion result.

| R/W-1           | R/W-1                     | R/W-1                                                                                                                                                                | R/W-1                                                                                  | R/W-1            | R/W-1            | R/W-1           | R/W-1 |

|-----------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------|------------------|-----------------|-------|

| RBPU            | INTEDG                    | TOCS                                                                                                                                                                 | TOSE                                                                                   | PSA              | PS2              | PS1             | PS0   |

| bit 7           |                           |                                                                                                                                                                      |                                                                                        |                  |                  |                 | bit ( |

|                 |                           |                                                                                                                                                                      |                                                                                        |                  |                  |                 |       |

| Legend:         |                           |                                                                                                                                                                      |                                                                                        |                  |                  |                 |       |

| R = Readable    | bit                       | W = Writable                                                                                                                                                         | bit                                                                                    | U = Unimpler     | nented bit, read | d as '0'        |       |

| -n = Value at F | POR                       | '1' = Bit is se                                                                                                                                                      | t                                                                                      | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

| bit 7           |                           | ull-ups are dis                                                                                                                                                      | abled                                                                                  | dual port latch  | values           |                 |       |

| bit 6           | •                         | errupt Edge Se<br>on rising edge<br>on falling edge                                                                                                                  | of INT pin                                                                             |                  |                  |                 |       |

| bit 5           | 1 = Transition            | Clock Source<br>on T0CKI pin<br>astruction cycle                                                                                                                     | or CPSOSC s                                                                            |                  |                  |                 |       |

| bit 4           |                           | Source Edge<br>t on high-to-lov<br>t on low-to-hig                                                                                                                   | w transition or                                                                        |                  |                  |                 |       |

| bit 3           |                           | er Assignmen<br>is assigned to<br>is assigned to                                                                                                                     | the WDT                                                                                | nodule           |                  |                 |       |

| bit 2-0         | <b>PS&lt;2:0&gt;:</b> Pre | escaler Rate S                                                                                                                                                       | elect bits                                                                             |                  |                  |                 |       |

|                 | BIT                       | VALUE TMR0 R                                                                                                                                                         | ATE WDT RA                                                                             | TE               |                  |                 |       |

|                 | 0<br>0<br>1<br>1<br>1     | 00         1:2           01         1:4           10         1:8           11         1:1           00         1:3           01         1:6           10         1:1 | 1:2           1:4           1:8           1:16           4           1:32           28 |                  |                  |                 |       |

| TABLE 11-1:     |                           |                                                                                                                                                                      | TERS ASSO                                                                              |                  | H TIMERO         |                 |       |

## REGISTER 11-1: OPTION\_REG: OPTION REGISTER

| Name       | Bit 7                  | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|------------------------|--------|--------|--------|---------|---------|--------|--------|----------------------|---------------------------------|

| CPSCON0    | CPSON                  |        |        |        | CPSRNG1 | CPSRNG0 | CPSOUT | T0XCS  | 0 0000               | 0 0000                          |

| INTCON     | GIE                    | PEIE   | TOIE   | INTE   | RBIE    | T0IF    | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| OPTION_REG | RBPU                   | INTEDG | TOCS   | TOSE   | PSA     | PS2     | PS1    | PS0    | 1111 1111            | 1111 1111                       |

| TMR0       | Timer0 Module Register |        |        |        |         |         |        |        | xxxx xxxx            | uuuu uuuu                       |

| TRISA      | TRISA7                 | TRISA6 | TRISA5 | TRISA4 | TRISA3  | TRISA2  | TRISA1 | TRISA0 | 1111 1111            | 1111 1111                       |

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Timer0 module.

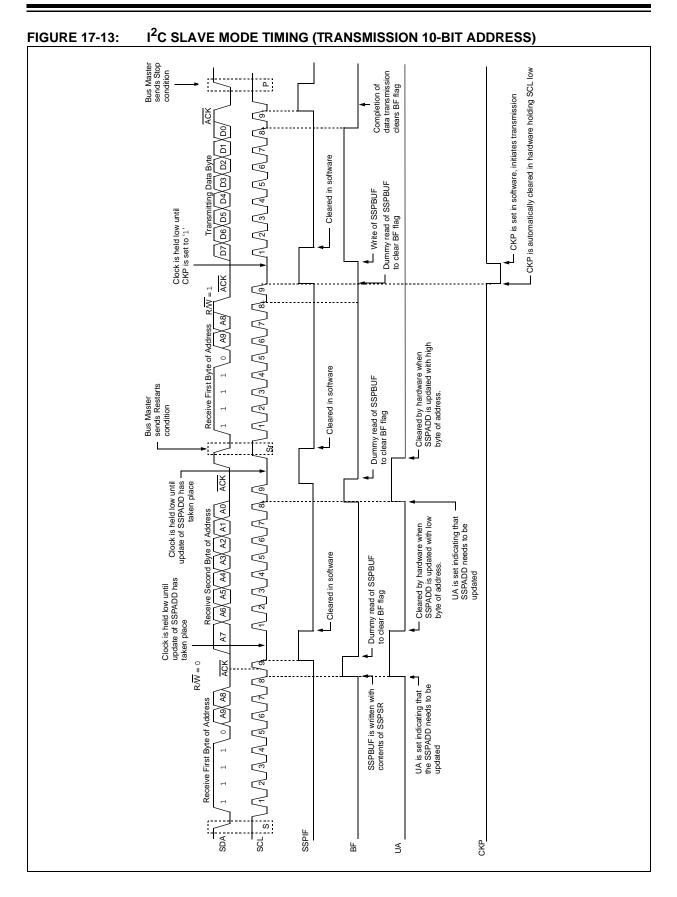

## 17.2.5 RECEPTION

When the  $R/\overline{W}$  bit of the received address byte is clear, the master will write data to the slave. If an address match occurs, the received address is loaded into the SSPBUF register. An address byte overflow will occur if that loaded address is not read from the SSPBUF before the next complete byte is received.

An SSP interrupt is generated for each data transfer byte. The BF,  $R/\overline{W}$  and  $D/\overline{A}$  bits of the SSPSTAT register are used to determine the status of the last received byte.

### FIGURE 17-10: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| R/<br>Receiving Address    | $\overline{W} = 0$<br>$\overline{\Delta C K}$ Receiving Data $\overline{\Delta C K}$ Receiving Data |                                                                 |

|----------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| SDA 1 A7XA6XA5XA4XA3XA2XA1 | ACK Receiving Data ACK Receiving Data<br>/D7/D6/D5/D4/D3/D2/D1/D0//D7/D6/D5/D4/D3/                  |                                                                 |

|                            | 3, 9, 1, 2, 3, 4, 5, 6, 7, 8, 9, 1, 2, 3, 4, 5,                                                     | /6\_/7\_/8 <del>\_</del> /9\_/ <sup>!</sup> ₽ <sup>!</sup><br>I |

| SSPIF                      | Cleared in software                                                                                 | Bus Master<br>sends Stop                                        |

| BF                         | <ul> <li>SSPBUF register is read</li> </ul>                                                         | condition                                                       |

| SSPOV                      |                                                                                                     |                                                                 |

|                            | Bit SSPOV is set because the SSPBUF register is                                                     | s still full. 🗕                                                 |

|                            |                                                                                                     | s not sent.                                                     |

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |          |                                                             |               |          |          |       |                              |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------|---------------|----------|----------|-------|------------------------------|--|--|--|--|

| Param<br>No.                                                                                                         | Sym.     | Characteristic                                              | Min.          | Тур†     | Max.     | Units | Conditions                   |  |  |  |  |

| OS11                                                                                                                 | TosH2ckL | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                             | —             | _        | 70       | ns    | VDD = 3.3-5.0V               |  |  |  |  |

| OS12                                                                                                                 | TosH2ckH | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                             | —             |          | 72       | ns    | VDD = 3.3-5.0V               |  |  |  |  |

| OS13                                                                                                                 | TckL2ioV | CLKOUT↓ to Port out valid <sup>(1)</sup>                    | _             | _        | 20       | ns    |                              |  |  |  |  |

| OS14                                                                                                                 | TioV2ckH | Port input valid before CLKOUT <sup>(1)</sup>               | Tosc + 200 ns | —        |          | ns    |                              |  |  |  |  |

| OS15                                                                                                                 | TosH2ioV | Fosc↑ (Q1 cycle) to Port out valid                          | —             | 50       | 70*      | ns    | VDD = 3.3-5.0V               |  |  |  |  |

| OS16                                                                                                                 | TosH2iol | Fosc↑ (Q2 cycle) to Port input invalid (I/O in hold time)   | 50            | _        | _        | ns    | VDD = 3.3-5.0V               |  |  |  |  |

| OS17                                                                                                                 | TioV2osH | Port input valid to Fosc↑ (Q2 cycle)<br>(I/O in setup time) | 20            |          | _        | ns    |                              |  |  |  |  |

| OS18                                                                                                                 | TioR     | Port output rise time <sup>(2)</sup>                        |               | 40<br>15 | 72<br>32 | ns    | VDD = 2.0V<br>VDD = 3.3-5.0V |  |  |  |  |

| OS19                                                                                                                 | TioF     | Port output fall time <sup>(2)</sup>                        |               | 28<br>15 | 55<br>30 | ns    | VDD = 2.0V<br>VDD = 3.3-5.0V |  |  |  |  |

| OS20*                                                                                                                | Tinp     | INT pin input high or low time                              | 25            | —        | —        | ns    |                              |  |  |  |  |

| OS21*                                                                                                                | Trbp     | PORTB interrupt-on-change new input level time              | Тсү           | —        | _        | ns    |                              |  |  |  |  |

### TABLE 23-3: CLKOUT AND I/O TIMING PARAMETERS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

**Note 1:** Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

2: Includes OSC2 in CLKOUT mode.

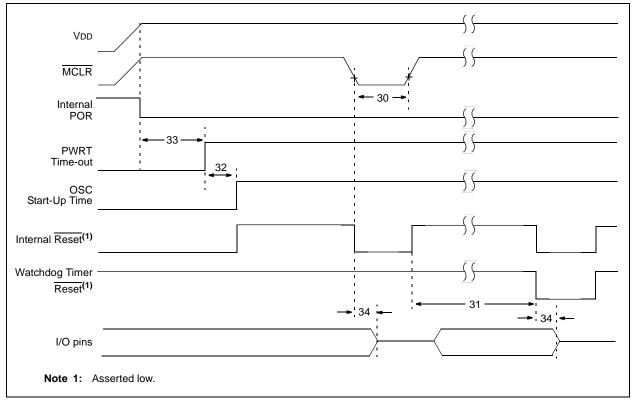

## FIGURE 23-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

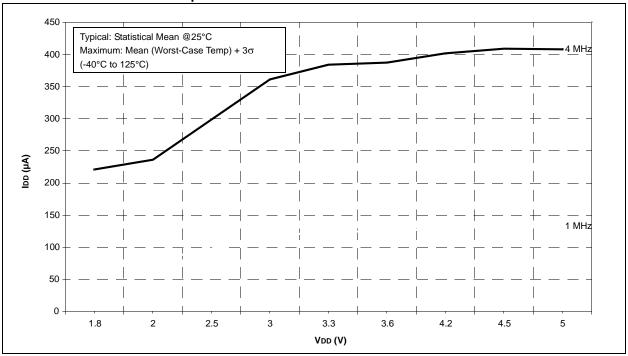

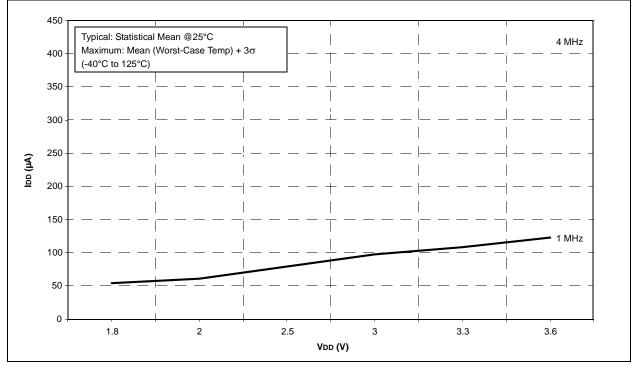

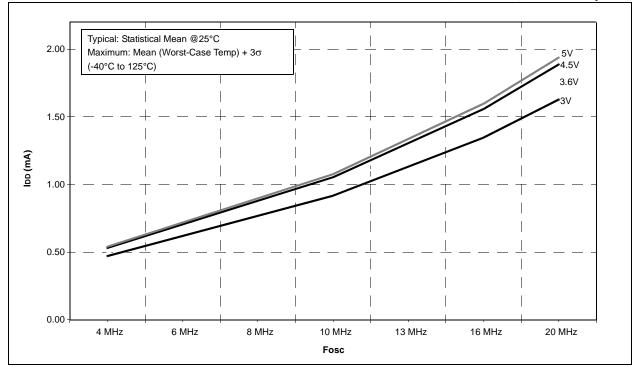

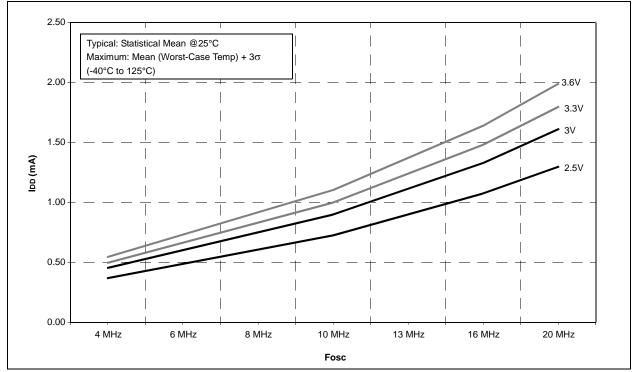

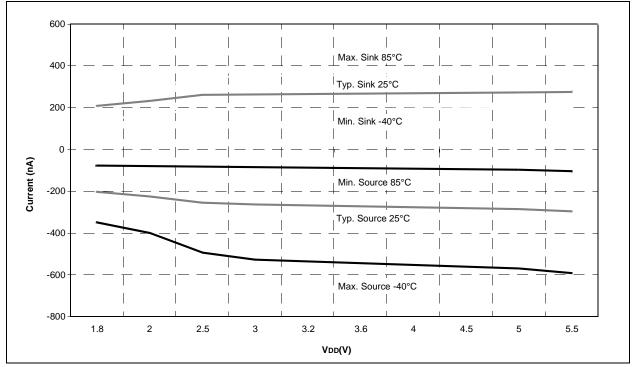

## FIGURE 24-7: PIC16F722/3/4/6/7 TYPICAL IDD vs. VDD OVER Fosc, EXTRC MODE, VCAP = $0.1 \mu$ F

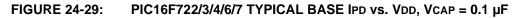

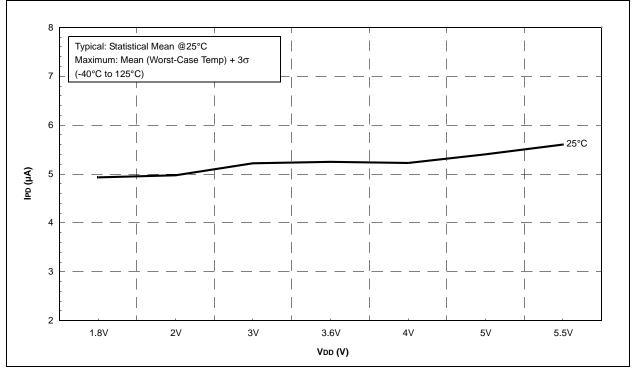

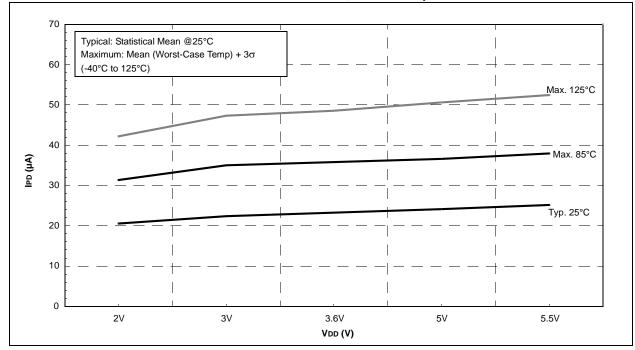

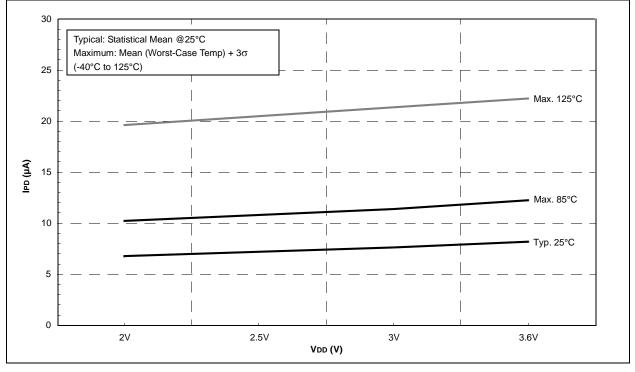

#### FIGURE 24-33: PIC16F722/3/4/6/7 BOR IPD vs. VDD, VCAP = 0.1 µF

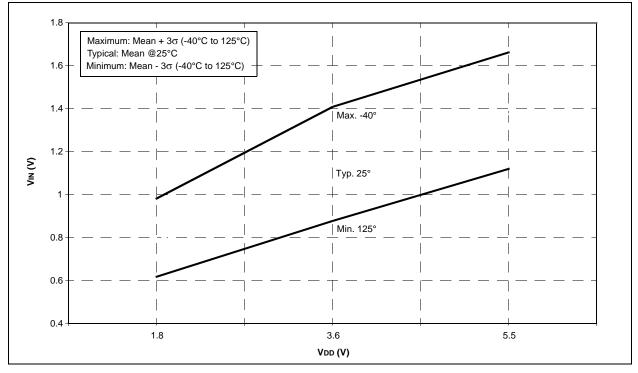

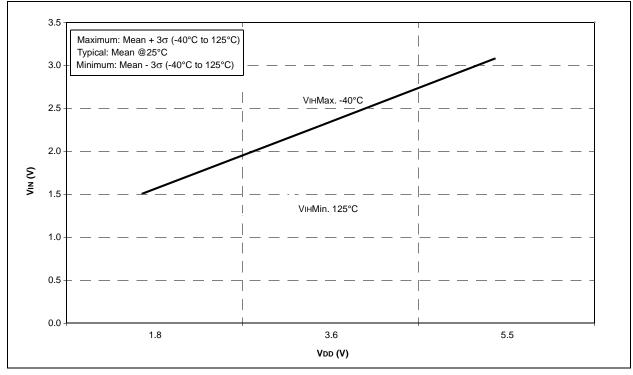

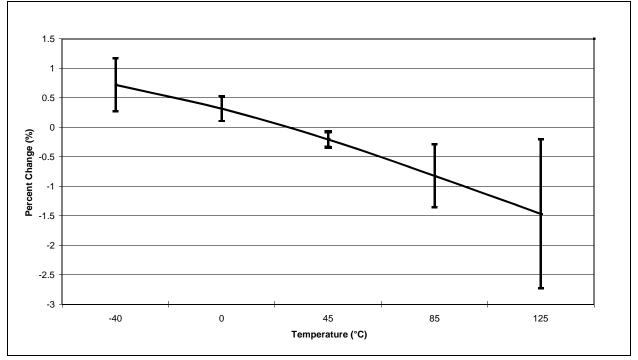

#### FIGURE 24-49: TTL INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

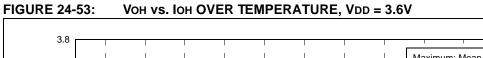

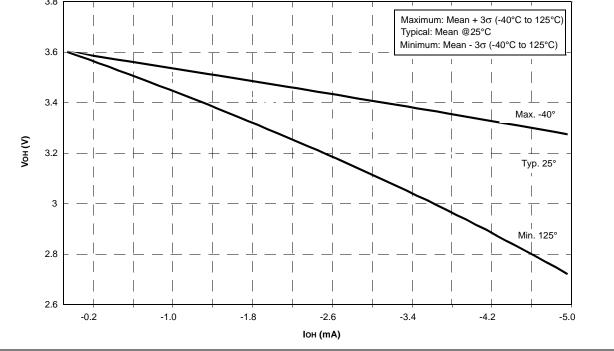

FIGURE 24-54: VOH vs. IOH OVER TEMPERATURE, VDD = 1.8V

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                 | <u>[X]</u> (1)                                                                                                       | ¥                                                           | <u>/xx</u>                                   | <u>xxx</u>                                                     | Exam   | ples:                                                                                                                                                       |

|--------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                   | Tape and Reel<br>Option                                                                                              | Temperature<br>Range                                        | Package                                      | Pattern                                                        | b) F   | IC16F722-E/SP 301 = Extended Temp.,<br>kinny PDIP package, QTP pattern #301<br>IC16F722-I/SO = Industrial Temp., SOIC<br>ackage                             |

| Device:                  | PIC16F722, PIC16<br>PIC16F723, PIC16<br>PIC16F724, PIC16<br>PIC16F726, PIC16<br>PIC16F726, PIC16<br>PIC16F727, PIC16 | LF723, PIC16F723<br>LF724, PIC16F724<br>LF726, PIC16F726    | T, PIC16LF72<br>T, PIC16LF72<br>T, PIC16LF72 | 23T <sup>(1)</sup><br>24T <sup>(1)</sup><br>26T <sup>(1)</sup> |        | uonugo                                                                                                                                                      |

| Tape and Reel<br>Option: | $I = -40^{\circ}C \text{ to}$ $E = -40^{\circ}C \text{ to}$ $MV = \text{Micro Le}$                                   |                                                             |                                              |                                                                |        |                                                                                                                                                             |

| Temperature<br>Range:    |                                                                                                                      | o +85°C (Indus<br>o +125°C (Exten                           |                                              |                                                                | Note 1 | <ul> <li>Tape and Reel identifier only appears in the<br/>catalog part number description. This<br/>identifier is used for ordering purposes and</li> </ul> |

| Package:                 | P = Plastic IPT = TQFP (1SO = SOIC                                                                                   | ead Frame (QFN)<br>DIP<br>Thin Quad Flatpack<br>Plastic DIP | )                                            |                                                                |        | is not printed on the device package. Check<br>with your Microchip Sales Office for package<br>availability with the Tape and Reel option.                  |