Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I²C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 14x8b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-TQFP                                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f727-e-pt |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

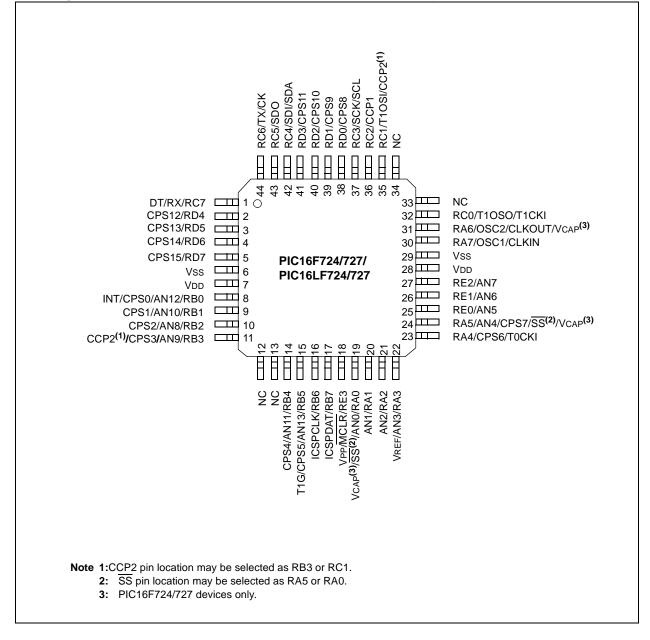

### Pin Diagrams – 44-PIN TQFP (PIC16F724/727/PIC16LF724/727)

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

| Address               | Name                  | Bit 7         | Bit 6                                                            | Bit 5                   | Bit 4          | Bit 3                   | Bit 2                 | Bit 1                 | Bit 0                 | Value on:<br>POR, BOR | Page   |

|-----------------------|-----------------------|---------------|------------------------------------------------------------------|-------------------------|----------------|-------------------------|-----------------------|-----------------------|-----------------------|-----------------------|--------|

| Bank 1                |                       |               |                                                                  |                         |                |                         |                       |                       |                       |                       |        |

| 80h <sup>(2)</sup>    | INDF                  | Addressing    | this location                                                    | uses conten             | ts of FSR to a | ddress data             | memory (not           | a physical re         | gister)               | xxxx xxxx             | 29,37  |

| 81h                   | OPTION_REG            | RBPU          | INTEDG                                                           | TOCS                    | TOSE           | PSA                     | PS2                   | PS1                   | PS0                   | 1111 1111             | 26,37  |

| 82h <sup>(2)</sup>    | PCL                   | Program Co    | ounter (PC) L                                                    | east Signific           | ant Byte       | •                       | •                     |                       | •                     | 0000 0000             | 28,37  |

| 83h <sup>(2)</sup>    | STATUS                | IRP           | RP1                                                              | RP0                     | TO             | PD                      | Z                     | DC                    | С                     | 0001 1xxx             | 25,37  |

| 84h <sup>(2)</sup>    | FSR                   | Indirect Data | a Memory Ad                                                      | dress Point             | er             | •                       | •                     |                       | •                     | xxxx xxxx             | 29,37  |

| 85h                   | TRISA                 | TRISA7        | TRISA6                                                           | TRISA5                  | TRISA4         | TRISA3                  | TRISA2                | TRISA1                | TRISA0                | 1111 1111             | 51,37  |

| 86h                   | TRISB                 | TRISB7        | TRISB6                                                           | TRISB5                  | TRISB4         | TRISB3                  | TRISB2                | TRISB1                | TRISB0                | 1111 1111             | 60,37  |

| 87h                   | TRISC                 | TRISC7        | TRISC6                                                           | TRISC5                  | TRISC4         | TRISC3                  | TRISC2                | TRISC1                | TRISC0                | 1111 1111             | 70,37  |

| 88h <sup>(3)</sup>    | TRISD                 | TRISD7        | TRISD6                                                           | TRISD5                  | TRISD4         | TRISD3                  | TRISD2                | TRISD1                | TRISD0                | 1111 1111             | 78,37  |

| 89h                   | TRISE                 | _             | _                                                                | _                       | _              | TRISE3 <sup>(6)</sup>   | TRISE2 <sup>(3)</sup> | TRISE1 <sup>(3)</sup> | TRISE0 <sup>(3)</sup> | 1111                  | 81,37  |

| 8Ah <sup>(1, 2)</sup> | PCLATH                | _             | _                                                                | _                       | Write Buffer   | for the upper           | 5 bits of the F       | Program Cou           | nter                  | 0 0000                | 28,37  |

| 8Bh <sup>(2)</sup>    | INTCON                | GIE           | PEIE                                                             | TOIE                    | INTE           | RBIE                    | T0IF                  | INTF                  | RBIF                  | 0000 000x             | 44,37  |

| 8Ch                   | PIE1                  | TMR1GIE       | ADIE                                                             | RCIE                    | TXIE           | SSPIE                   | CCP1IE                | TMR2IE                | TMR1IE                | 0000 0000             | 45,37  |

| 8Dh                   | PIE2                  | _             | —                                                                | —                       | _              | —                       | _                     | _                     | CCP2IE                | 0                     | 46,37  |

| 8Eh                   | PCON                  | _             | _                                                                | _                       | _              | _                       | _                     | POR                   | BOR                   | qq                    | 27,38  |

| 8Fh                   | T1GCON                | TMR1GE        | T1GPOL                                                           | T1GTM                   | T1GSPM         | T <u>1GGO</u> /<br>DONE | T1GVAL                | T1GSS1                | T1GSS0                | 0000 0x00             | 118,38 |

| 90h                   | OSCCON                | _             | _                                                                | IRCF1                   | IRCF0          | ICSL                    | ICSS                  | _                     | _                     | 10 qq                 | 87,38  |

| 91h                   | OSCTUNE               | _             | _                                                                | TUN5                    | TUN4           | TUN3                    | TUN2                  | TUN1                  | TUN0                  | 00 0000               | 88,38  |

| 92h                   | PR2                   | Timer2 Perio  | od Register                                                      |                         |                |                         |                       |                       |                       | 1111 1111             | 120,38 |

| 93h                   | SSPADD <sup>(5)</sup> | Synchronou    | Synchronous Serial Port (I <sup>2</sup> C mode) Address Register |                         |                |                         |                       |                       | 0000 0000             | 169,38                |        |

| 93h                   | SSPMSK <sup>(4)</sup> | Synchronou    | s Serial Port                                                    | (I <sup>2</sup> C mode) | Address Mas    | k Register              |                       |                       |                       | 1111 1111             | 180,38 |

| 94h                   | SSPSTAT               | SMP           | CKE                                                              | D/A                     | Р              | S                       | R/W                   | UA                    | BF                    | 0000 0000             | 179,38 |

| 95h                   | WPUB                  | WPUB7         | WPUB6                                                            | WPUB5                   | WPUB4          | WPUB3                   | WPUB2                 | WPUB1                 | WPUB0                 | 1111 1111             | 61,38  |

| 96h                   | IOCB                  | IOCB7         | IOCB6                                                            | IOCB5                   | IOCB4          | IOCB3                   | IOCB2                 | IOCB1                 | IOCB0                 | 0000 0000             | 61,38  |

| 97h                   | —                     | Unimplemer    | nted                                                             |                         |                |                         |                       |                       |                       | _                     | —      |

| 98h                   | TXSTA                 | CSRC          | TX9                                                              | TXEN                    | SYNC           | _                       | BRGH                  | TRMT                  | TX9D                  | 0000 -010             | 147,38 |

| 99h                   | SPBRG                 | BRG7          | BRG6                                                             | BRG5                    | BRG4           | BRG3                    | BRG2                  | BRG1                  | BRG0                  | 0000 0000             | 149,38 |

| 9Ah                   | _                     | Unimplemer    | nted                                                             |                         |                |                         |                       |                       |                       | —                     | —      |

| 9Bh                   | _                     | Unimplemer    | nted                                                             |                         |                |                         |                       |                       |                       | —                     | —      |

| 9Ch                   | APFCON                | _             | —                                                                | —                       | _              | —                       | —                     | SSSEL                 | CCP2SEL               | 00                    | 50,38  |

| 9Dh                   | FVRCON                | FVRRDY        | FVREN                                                            | —                       | —              | —                       | —                     | ADFVR1                | ADFVR0                | q000                  | 104,38 |

| 9Eh                   | _                     | Unimplemer    | nted                                                             |                         |                |                         |                       |                       |                       | —                     | —      |

| 9Fh                   | ADCON1                | _             | ADCS2                                                            | ADCS1                   | ADCS0          | _                       | _                     | ADREF1                | ADREF0                | 000000                | 100,38 |

#### **TABLE 2-1:** PIC16(L)F722/3/4/6/7 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are 1: transferred to the upper byte of the program counter.

2:

These registers/bits are not implemented on PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'. 3:

Accessible only when SSPM<3:0>  $\pm$  1001. Accessible only when SSPM<3:0>  $\pm$  1001. This bit is always '1' as RE3 is input-only. 4:

5: 6:

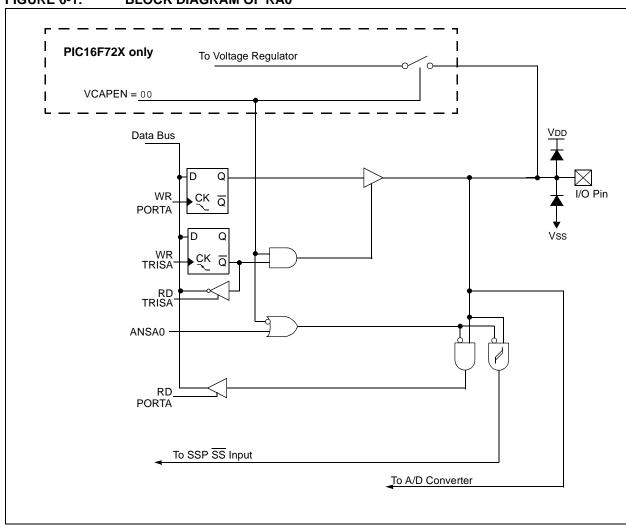

### FIGURE 6-1: BLOCK DIAGRAM OF RA0

### 6.4.1 RC0/T1OSO/T1CKI

Figure 6-13 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 oscillator output

- a Timer1 clock input

### 6.4.2 RC1/T1OSI/CCP2

Figure 6-14 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 oscillator input

- a Capture 2 input, Compare 2 output, and PWM2 output

Note: CCP2 pin location may be selected as RB3 or RC1.

### 6.4.3 RC2/CCP1

Figure 6-15 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a Capture 1 input, Compare 1 output, and PWM1 output

### 6.4.4 RC3/SCK/SCL

Figure 6-16 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a SPI clock

- an I<sup>2</sup>C clock

### 6.4.5 RC4/SDI/SDA

Figure 6-17 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a SPI data input

- an I<sup>2</sup>C data I/O

### 6.4.6 RC5/SDO

Figure 6-18 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a SPI data output

### 6.4.7 RC6/TX/CK

Figure 6-19 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an asynchronous serial output

- a synchronous clock I/O

## 6.4.8 RC7/RX/DT

Figure 6-20 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- · an asynchronous serial input

- a synchronous serial data I/O

## 7.6 External Clock Modes

### 7.6.1 OSCILLATOR START-UP TIMER (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations on the OSC1 pin before the device is released from Reset. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

### 7.6.2 EC MODE

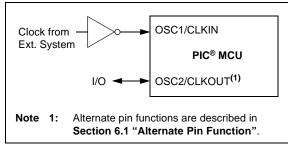

The External Clock (EC) mode allows an externally generated logic level as the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input and the OSC2 is available for general purpose I/O. Figure 7-2 shows the pin connections for EC mode.

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

### FIGURE 7-2: EXTERNAL CLOCK (EC) MODE OPERATION

### 7.6.3 LP, XT, HS MODES

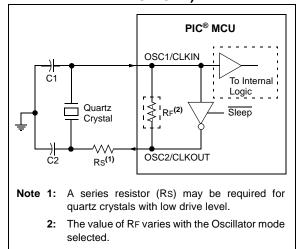

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 7-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

LP Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is best suited to drive resonators with a low drive level specification, for example, tuning fork type crystals.

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 7-3 and Figure 7-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

### FIGURE 7-3: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices (DS00826)

- AN849, Basic PIC<sup>®</sup> Oscillator Design (DS00849)

- AN943, Practical PIC<sup>®</sup> Oscillator Analysis and Design (DS00943)

- AN949, Making Your Oscillator Work (DS00949).

### TABLE 9-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock Period (TAD) |           | Device Frequency (Fosc)     |                             |                                    |                               |                               |  |  |

|------------------------|-----------|-----------------------------|-----------------------------|------------------------------------|-------------------------------|-------------------------------|--|--|

| ADC<br>Clock Source    | ADCS<2:0> | 20 MHz                      | 16 MHz                      | 8 MHz                              | 4 MHz                         | 1 MHz                         |  |  |

| Fosc/2                 | 000       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>              | 500 ns <sup>(2)</sup>         | 2.0 μs                        |  |  |

| Fosc/4                 | 100       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>              | 1.0 μs                        | 4.0 μs                        |  |  |

| Fosc/8                 | 001       | 400 ns <sup>(2)</sup>       | 0.5 μs <b>(2)</b>           | 1.0 μs                             | 2.0 μs                        | 8.0 μs <b>(3)</b>             |  |  |

| Fosc/16                | 101       | 800 ns                      | 1.0 μs                      | 2.0 μs                             | 4.0 μs                        | 16.0 μs <b><sup>(3)</sup></b> |  |  |

| Fosc/32                | 010       | 1.6 μs                      | 2.0 μs                      | 4.0 μs                             | 8.0 μs <sup>(3)</sup>         | 32.0 μs <sup>(3)</sup>        |  |  |

| Fosc/64                | 110       | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>              | 16.0 μs <b><sup>(3)</sup></b> | 64.0 μs <b><sup>(3)</sup></b> |  |  |

| FRC                    | x11       | 1.0-6.0 μs <sup>(1,4)</sup> | 1.0-6.0 μs <sup>(1,4)</sup> | 1.0-6.0 μs <b><sup>(1,4)</sup></b> | 1.0-6.0 μs <b>(1,4)</b>       | 1.0-6.0 μs <sup>(1,4)</sup>   |  |  |

Legend: Shaded cells are outside of recommended range.

**Note 1:** The FRC source has a typical TAD time of 1.6 μs for VDD.

- 2: These values violate the minimum required TAD time.

- **3:** For faster conversion times, the selection of another clock source is recommended.

- 4: When the device frequency is greater than 1 MHz, the FRC clock source is only recommended if the conversion will be performed during Sleep.

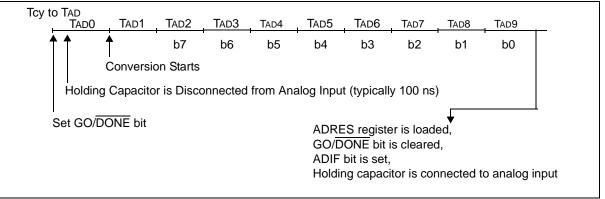

### FIGURE 9-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

### 11.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the OPTION register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

| Note: | When the prescaler is assigned to WDT, a    |

|-------|---------------------------------------------|

|       | CLRWDT instruction will clear the prescaler |

|       | along with the WDT.                         |

### 11.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The T0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The T0IF bit can only be cleared in software. The Timer0 interrupt enable is the T0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |

|-------|-----------------------------------------|

|       | processor from Sleep since the timer is |

|       | frozen during Sleep.                    |

### 11.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 23.0** "**Electrical Specifications**".

| Name   | Bit 7    | Bit 6       | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|-------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE        | TOIE       | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE  | ADIE        | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF  | ADIF        | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCREG  | AUSART R | eceive Data | a Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN     | RX9         | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7     | BRG6        | BRG5       | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7   | TRISC6      | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC     | TX9         | TXEN       | SYNC   | _      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

### TABLE 16-2: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Asynchronous Reception.

## 16.4 AUSART Operation During Sleep

The AUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

### 16.4.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (refer to Section 16.3.2.4 "Synchronous Slave Reception Setup:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE global interrupt enable bit of the INTCON register is also set, then the Interrupt Service Routine at address 0004h will be called.

### 16.4.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Transmission (refer to Section 16.3.2.2 "Synchronous Slave Transmission Setup:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE global interrupt enable bit is also set then the Interrupt Service Routine at address 0004h will be called.

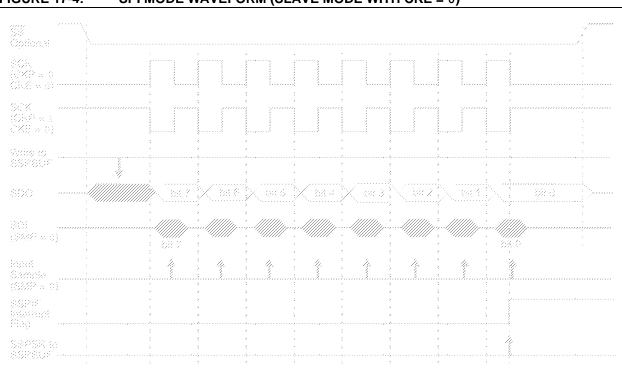

### FIGURE 17-4: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 0)

#### SS SCK (CKP = 0 $\dot{C}KE = 1)$ SCK (CKP = 1 CKE = 1) Write to SSPBUF bit 6 bit 5 bit 4 bit 2 bit 1 bit 0 SDO bit '7 bit 3 ï SDI (SMP = 0)I bit 0 bit 7 Input Sample (SMP = 0)SSPIF Interrupt Flag SSPSR to SSPBUF 1 . i . . . .

### FIGURE 17-5: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

| Name    | Bit 7       | Bit 6          | Bit 5       | Bit 4        | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on all<br>other Resets |

|---------|-------------|----------------|-------------|--------------|----------|--------|---------|---------|----------------------|------------------------------|

| ANSELA  | —           | —              | ANSA5       | ANSA4        | ANSA3    | ANSA2  | ANSA1   | ANSA0   | 11 1111              | 11 1111                      |

| APFCON  | —           | —              | _           | —            | _        | _      | SSSEL   | CCP2SEL | 00                   | 00                           |

| INTCON  | GIE         | PEIE           | T0IE        | INTE         | RBIE     | T0IF   | INTF    | RBIF    | 0000 000x            | 0000 000x                    |

| PIE1    | TMR1GIE     | ADIE           | RCIE        | TXIE         | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                    |

| PIR1    | TMR1GIF     | ADIF           | RCIF        | TXIF         | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                    |

| PR2     | Timer2 Peri | iod Register   | •           | •            |          |        |         | •       | 1111 1111            | 1111 1111                    |

| SSPBUF  | Synchronou  | us Serial Port | Receive But | fer/Transmit | Register |        |         |         | XXXX XXXX            | uuuu uuuu                    |

| SSPCON  | WCOL        | SSPOV          | SSPEN       | CKP          | SSPM3    | SSPM2  | SSPM1   | SSPM0   | 0000 0000            | 0000 0000                    |

| SSPSTAT | SMP         | CKE            | D/A         | Р            | S        | R/W    | UA      | BF      | 0000 0000            | 0000 0000                    |

| TRISA   | TRISA7      | TRISA6         | TRISA5      | TRISA4       | TRISA3   | TRISA2 | TRISA1  | TRISA0  | 1111 1111            | 1111 1111                    |

| TRISC   | TRISC7      | TRISC6         | TRISC5      | TRISC4       | TRISC3   | TRISC2 | TRISC1  | TRISC0  | 1111 1111            | 1111 1111                    |

| T2CON   | _           | TOUTPS3        | TOUTPS2     | TOUTPS1      | TOUTPS0  | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                    |

### TABLE 17-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode.

### 17.2.5 RECEPTION

When the  $R/\overline{W}$  bit of the received address byte is clear, the master will write data to the slave. If an address match occurs, the received address is loaded into the SSPBUF register. An address byte overflow will occur if that loaded address is not read from the SSPBUF before the next complete byte is received.

An SSP interrupt is generated for each data transfer byte. The BF,  $R/\overline{W}$  and  $D/\overline{A}$  bits of the SSPSTAT register are used to determine the status of the last received byte.

### FIGURE 17-10: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| R/<br>Receiving Address    | $\overline{W} = 0$<br>$\overline{\Delta C K}$ Receiving Data $\overline{\Delta C K}$ Receiving Data |                                                                  |

|----------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| SDA 1 A7XA6XA5XA4XA3XA2XA1 | ACK Receiving Data ACK Receiving Data<br>/D7/D6/D5/D4/D3/D2/D1/D0//D7/D6/D5/D4/D3/                  |                                                                  |

|                            | 3\_91\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_                                                      | /6\_/7\_/8 <del>\_</del> _/9\_/ <sup>!</sup> ₽ <sup>!</sup><br>I |

| SSPIF                      | Cleared in software                                                                                 | Bus Master<br>sends Stop                                         |

| BF                         | <ul> <li>SSPBUF register is read</li> </ul>                                                         | condition                                                        |

| SSPOV                      |                                                                                                     |                                                                  |

|                            | Bit SSPOV is set because the SSPBUF register is                                                     | s still full. 🗕                                                  |

|                            |                                                                                                     | s not sent.                                                      |

| SUBWF            | Subtract W                                                      | from f                                                                                                                      |  |  |  |

|------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] SU                                                      | JBWF f,d                                                                                                                    |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$ |                                                                                                                             |  |  |  |

| Operation:       | ation: (f) - (W) $\rightarrow$ (destination)                    |                                                                                                                             |  |  |  |

| Status Affected: | C, DC, Z                                                        |                                                                                                                             |  |  |  |

| Description:     | W register f<br>'0', the resu<br>register. If 'o                | s complement method)<br>rom register 'f'. If 'd' is<br>It is stored in the W<br>d' is '1', the result is<br>in register 'f. |  |  |  |

|                  | <b>C</b> = 0                                                    | W > f                                                                                                                       |  |  |  |

|                  | <b>C</b> = 1                                                    | W≤f                                                                                                                         |  |  |  |

$\overline{DC} = 0$

**DC** = 1

W<3:0> > f<3:0> W<3:0>  $\leq$  f<3:0>

| XORLW            | Exclusive OR literal with W                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] XORLW k                                                                                                        |

| Operands:        | $0 \le k \le 255$                                                                                                      |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                          |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of the W register<br>are XOR'ed with the 8-bit<br>literal 'k'. The result is placed in<br>the W register. |

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                      |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                |

| Status Affected: | None                                                                                                                                                                   |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] XORWF f,d                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                     |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |

| Status Affected: | Z                                                                                                                                                                               |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

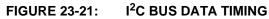

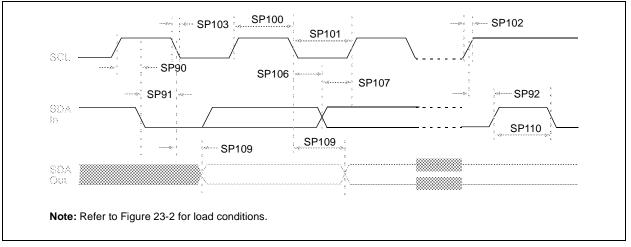

| Param<br>No. | Symbol  | Charact         | Min.         | Тур  | Max. | Units | Conditions |                              |  |

|--------------|---------|-----------------|--------------|------|------|-------|------------|------------------------------|--|

| SP90*        | TSU:STA | Start condition | 100 kHz mode | 4700 |      | _     | ns         | Only relevant for Repeated   |  |

|              |         | Setup time      | 400 kHz mode | 600  | _    | —     |            | Start condition              |  |

| SP91*        | THD:STA | Start condition | 100 kHz mode | 4000 | _    | —     | ns         | After this period, the first |  |

|              |         | Hold time       | 400 kHz mode | 600  | _    | _     |            | clock pulse is generated     |  |

| SP92*        | Tsu:sto | Stop condition  | 100 kHz mode | 4700 | —    | _     | ns         |                              |  |

|              |         | Setup time      | 400 kHz mode | 600  | _    | _     |            |                              |  |

| SP93         | THD:STO | Stop condition  | 100 kHz mode | 4000 | —    | —     | ns         |                              |  |

|              |         | Hold time       | 400 kHz mode | 600  | _    |       |            |                              |  |

## TABLE 23-12: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

\* These parameters are characterized but not tested.

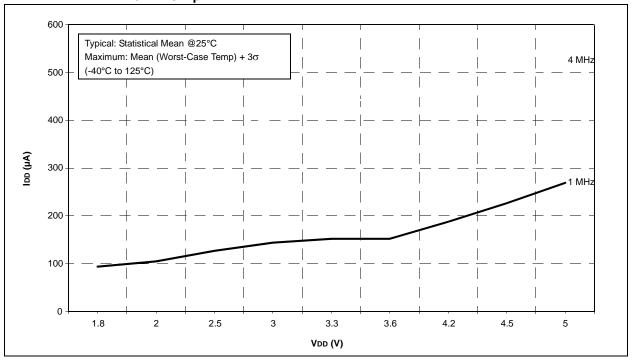

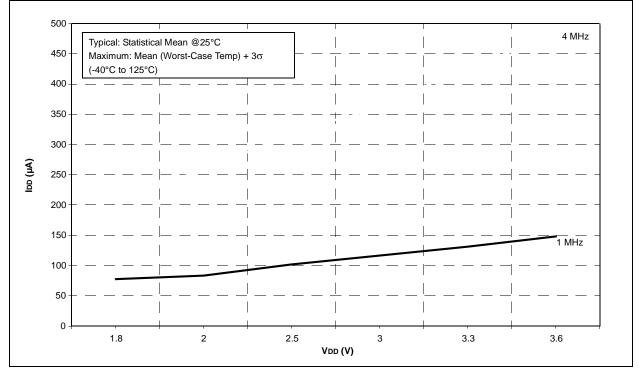

## FIGURE 24-5: PIC16F722/3/4/6/7 MAXIMUM IDD vs. VDD OVER Fosc, EXTRC MODE, VCAP = $0.1 \mu$ F

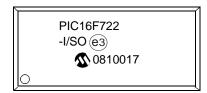

## Package Marking Information (Continued)

44-Lead QFN

### 28-Lead SOIC

### 28-Lead SSOP

### 44-Lead TQFP

Example

### Example

### Example

### Example

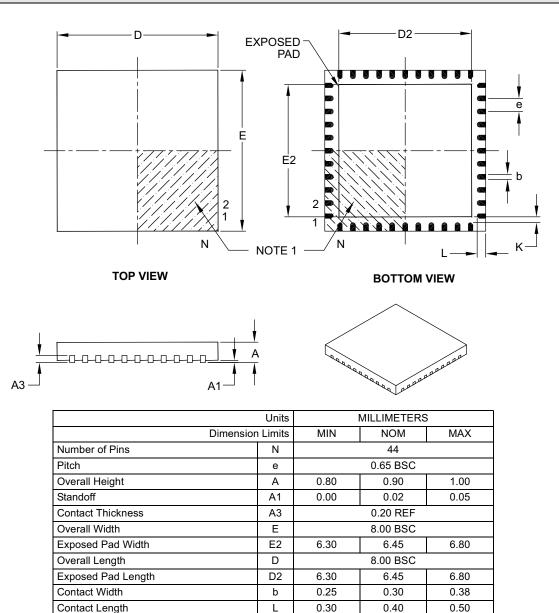

## 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Κ

0.20

\_

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

Contact-to-Exposed Pad

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103B

\_

## APPENDIX A: DATA SHEET REVISION HISTORY

### Revision A (12/2007)

Original release.

### Revision B (08/2008)

Electrical Specification updates; Package Drawings; miscellaneous updates.

### Revision C (04/2009)

Revised data sheet title; Revised Low-Power Features section; Revised Section 6.2.2.4 RA3/AN3/VREF; Revised Figure 16-8 Synchronous Reception.

### Revision D (07/2009)

Removed the Preliminary Label; Updated the "Electrical Characteristics" section; Added charts in the "Char. Data" section; Deleted "Based 8-Bit CMOS" from title; Updated the "Special Microcontroller Features" section and the "Peripheral Features" section; Changed the title of the "Low Power Features" section into "Extreme Low-Power Management PIC16LF72X with nanoWatt XLP" and updated this section; Inserted new section – "Analog Features" (page 1); Changed the title of the "Peripheral Features" section into "Peripheral Highlights" and updated the section.

## **Revision E (10/2009)**

Added paragraph to section 5.0 (LDO Voltage Regulator); Updated the Electrical Specifications section (Added another absolute Maximum Rating; Updated section 23.1 and Table 23-4); Updated the Pin Diagrams with the UQFN package; Updated Table 1, adding UQFN; Updated section 23.5 (Thermal Considerations); Updated the Packaging Information section adding the UQFN Package; Updated the Product Identification System section.

## **Revision F (12/2015)**

Updated Table 2; Updated 23.1, 23.3 and 9.2.4 Sections; Updated Figure 23-9; Other minor corrections.

## APPENDIX B: MIGRATING FROM OTHER PIC® DEVICES

This discusses some of the issues in migrating from other  $\text{PIC}^{\textcircled{B}}$  devices to the PIC16F72X family of devices.

## B.1 PIC16F77 to PIC16F72X

### TABLE B-1: FEATURE COMPARISON

| Feature                               | PIC16F77 | PIC16F727           |  |

|---------------------------------------|----------|---------------------|--|

| Max. Operating Speed                  | 20 MHz   | 20 MHz              |  |

| Max. Program<br>Memory (Words)        | 8K       | 8K                  |  |

| Max. SRAM (Bytes)                     | 368      | 368                 |  |

| A/D Resolution                        | 8-bit    | 8-bit               |  |

| Timers (8/16-bit)                     | 2/1      | 2/1                 |  |

| Oscillator Modes                      | 4        | 8                   |  |

| Brown-out Reset                       | Y        | Y                   |  |

| Internal Pull-ups                     | RB<7:0>  | RB<7:0>             |  |

| Interrupt-on-change                   | RB<7:4>  | RB<7:0>             |  |

| Comparator                            | 0        | 0                   |  |

| USART                                 | Y        | Y                   |  |

| Extended WDT                          | Ν        | N                   |  |

| Software Control<br>Option of WDT/BOR | N        | N                   |  |

| INTOSC Frequencies                    | None     | 500 kHz -<br>16 MHz |  |

| Clock Switching                       | Ν        | Ν                   |  |

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                 | <u>[X]</u> (1)                                                                                                       | ¥                                                           | <u>/xx</u>                                   | <u>xxx</u>                                                     | Exam   | ples:                                                                                                                                      |

|--------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Device                   | Tape and Reel<br>Option                                                                                              | Temperature<br>Range                                        | Package                                      | Pattern                                                        | b) F   | IC16F722-E/SP 301 = Extended Temp.,<br>kinny PDIP package, QTP pattern #301<br>IC16F722-I/SO = Industrial Temp., SOIC<br>ackage            |

| Device:                  | PIC16F722, PIC16<br>PIC16F723, PIC16<br>PIC16F724, PIC16<br>PIC16F726, PIC16<br>PIC16F726, PIC16<br>PIC16F727, PIC16 | LF723, PIC16F723<br>LF724, PIC16F724<br>LF726, PIC16F726    | T, PIC16LF72<br>T, PIC16LF72<br>T, PIC16LF72 | 23T <sup>(1)</sup><br>24T <sup>(1)</sup><br>26T <sup>(1)</sup> |        | uonugo                                                                                                                                     |

| Tape and Reel<br>Option: | $I = -40^{\circ}C \text{ to}$ $E = -40^{\circ}C \text{ to}$ $MV = \text{Micro Le}$                                   |                                                             |                                              |                                                                |        |                                                                                                                                            |

| Temperature<br>Range:    |                                                                                                                      | o +85°C (Indus<br>o +125°C (Exten                           |                                              |                                                                | Note 1 | : Tape and Reel identifier only appears in the<br>catalog part number description. This<br>identifier is used for ordering purposes and    |

| Package:                 | P = Plastic IPT = TQFP (1SO = SOIC                                                                                   | ead Frame (QFN)<br>DIP<br>Thin Quad Flatpack<br>Plastic DIP | )                                            |                                                                |        | is not printed on the device package. Check<br>with your Microchip Sales Office for package<br>availability with the Tape and Reel option. |