Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I²C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 14x8b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-TQFP                                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f727-i-pt |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

The PIC16(L)F722/3/4/6/7 devices are covered by this data sheet. They are available in 28/40/44-pin packages. Figure 1-1 shows a block diagram of the PIC16F722/723/726/PIC16LF722/723/726 devices and Figure 1-2 shows a block diagram of the PIC16F724/727/PIC16LF724/727 devices. Table 1-1 shows the pinout descriptions.

#### 2.2.2.3 PCON Register

The Power Control (PCON) register contains flag bits (refer to Table 3-2) to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the software enable of the BOR.

The PCON register bits are shown in Register 2-3.

### REGISTER 2-3: PCON: POWER CONTROL REGISTER

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-q | R/W-q |

|-------------|-----|-----|-----|-----|-----|-------|-------|

| —           | _   | _   | _   | _   | _   | POR   | BOR   |

| bit 7 bit 0 |     |     |     |     |     |       |       |

| Legend:                        |                  |                        |                    |  |  |  |  |

|--------------------------------|------------------|------------------------|--------------------|--|--|--|--|

| R = Readable bit               | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |  |  |  |

| -n = Value at POR              | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |  |  |  |

| q = Value depends on condition |                  |                        |                    |  |  |  |  |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                        |

|---------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | POR: Power-on Reset Status bit                                                                                                    |

|         | 1 = No Power-on Reset occurred                                                                                                    |

|         | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                                             |

| bit 0   | BOR: Brown-out Reset Status bit                                                                                                   |

|         | 1 = No Brown-out Reset occurred                                                                                                   |

|         | <ul> <li>0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset<br/>occurs)</li> </ul> |

|         |                                                                                                                                   |

**Note 1:** Set BOREN<1:0> = 01 in the Configuration Word register for this bit to control the  $\overline{\text{BOR}}$ .

| IADLE . | J-1. C |    |    | BITS AND THEIR SIGNIFICANCE                             |  |  |  |  |  |

|---------|--------|----|----|---------------------------------------------------------|--|--|--|--|--|

| POR     | BOR    | то | PD | Condition                                               |  |  |  |  |  |

| 0       | x      | 1  | 1  | Power-on Reset or LDO Reset                             |  |  |  |  |  |

| 0       | x      | 0  | x  | Illegal, TO is set on POR                               |  |  |  |  |  |

| 0       | x      | x  | 0  | Illegal, PD is set on POR                               |  |  |  |  |  |

| 1       | 0      | 1  | 1  | Brown-out Reset                                         |  |  |  |  |  |

| 1       | 1      | 0  | 1  | WDT Reset                                               |  |  |  |  |  |

| 1       | 1      | 0  | 0  | WDT Wake-up                                             |  |  |  |  |  |

| 1       | 1      | u  | u  | MCLR Reset during normal operation                      |  |  |  |  |  |

| 1       | 1      | 1  | 0  | MCLR Reset during Sleep or interrupt wake-up from Sleep |  |  |  |  |  |

#### TABLE 3-1: STATUS BITS AND THEIR SIGNIFICANCE

# TABLE 3-2: RESET CONDITION FOR SPECIAL REGISTERS<sup>(2)</sup>

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 0000h                 | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 0000h                 | 0001 Ouuu          | uu               |

| WDT Reset                          | 0000h                 | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | uu               |

| Brown-out Reset                    | 0000h                 | 0001 luuu          | u0               |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

**2:** If a Status bit is not implemented, that bit will be read as '0'.

## 3.6 Time-out Sequence

On power-up, the time-out sequence is as follows: first, PWRT time out is invoked after POR has expired, then OST is activated after the PWRT time out has expired. The total time out will vary based on oscillator configuration and  $\overrightarrow{PWRTE}$  bit status. For example, in EC mode with  $\overrightarrow{PWRTE}$  bit = 1 ( $\overrightarrow{PWRT}$  disabled), there will be no time out at all. Figure 3-4, Figure 3-5 and Figure 3-6 depict time-out sequences.

Since the time outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time outs will expire. Then, bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 3-5). This is useful for testing purposes or to synchronize more than one PIC16(L)F722/3/4/6/7 device operating in parallel.

Table 3-3 shows the Reset conditions for some special registers.

## 3.7 Power Control (PCON) Register

The Power Control (PCON) register has two Status bits to indicate what type of Reset that last occurred.

Bit 0 is  $\overline{\text{BOR}}$  (Brown-out Reset).  $\overline{\text{BOR}}$  is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if  $\overline{\text{BOR}} = 0$ , indicating that a brown-out has occurred. The  $\overline{\text{BOR}}$ Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (BOREN<1:0> = 00 in the Configuration Word register).

Bit 1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent Reset, if POR is '0', it will indicate that a Power-on Reset has occurred (i.e., VDD may have gone too low).

For more information, see Section 3.5 "Brown-Out Reset (BOR)".

| Occillator Configuration  | Power-up               |             | Brown-o                | Wake-up from     |             |

|---------------------------|------------------------|-------------|------------------------|------------------|-------------|

| Oscillator Configuration  | <b>PWRTE</b> = 0       | PWRTE = 1   | <b>PWRTE</b> = 0       | <b>PWRTE</b> = 1 | Sleep       |

| XT, HS, LP <sup>(1)</sup> | TPWRT + 1024 •<br>Tosc | 1024 • Tosc | TPWRT + 1024 •<br>Tosc | 1024 • Tosc      | 1024 • Tosc |

| RC, EC, INTOSC            | TPWRT                  | _           | TPWRT                  | _                | _           |

#### TABLE 3-2: TIME OUT IN VARIOUS SITUATIONS

Note 1: LP mode with T1OSC disabled.

## TABLE 3-3: RESET BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD | Condition                          |  |

|-----|-----|----|----|------------------------------------|--|

| 0   | u   | 1  | 1  | Power-on Reset                     |  |

| 1   | 0   | 1  | 1  | Brown-out Reset                    |  |

| u   | u   | 0  | u  | WDT Reset                          |  |

| u   | u   | 0  | 0  | WDT Wake-up                        |  |

| u   | u   | u  | u  | MCLR Reset during normal operation |  |

| u   | u   | 1  | 0  | MCLR Reset during Sleep            |  |

**Legend:** u = unchanged, x = unknown

| Register             | Address               | Power-on Reset/<br>Brown-out Reset <sup>(1)</sup> | MCLR Reset/<br>WDT Reset | Wake-up from Sleep through<br>Interrupt/Time out |

|----------------------|-----------------------|---------------------------------------------------|--------------------------|--------------------------------------------------|

| W                    | —                     | XXXX XXXX                                         | uuuu uuuu                | <u>uuuu</u> uuuu                                 |

| INDF                 | 00h/80h/<br>100h/180h | XXXX XXXX                                         | XXXX XXXX                | սսսս սսսս                                        |

| TMR0                 | 01h/101h              | XXXX XXXX                                         | uuuu uuuu                | uuuu uuuu                                        |

| PCL                  | 02h/82h/<br>102h/182h | 0000 0000                                         | 0000 0000                | PC + 1 <sup>(3)</sup>                            |

| STATUS               | 03h/83h/<br>103h/183h | 0001 1xxx                                         | 000g guuu <b>(4)</b>     | uuuq quuu <sup>(4)</sup>                         |

| FSR                  | 04h/84h/<br>104h/184h | XXXX XXXX                                         | <u>uuuu</u> uuuu         | սսսս սսսս                                        |

| PORTA                | 05h                   | XXXX XXXX                                         | XXXX XXXX                | <u>uuuu</u> uuuu                                 |

| PORTB                | 06h                   | XXXX XXXX                                         | XXXX XXXX                | uuuu uuuu                                        |

| PORTC                | 07h                   | XXXX XXXX                                         | XXXX XXXX                | uuuu uuuu                                        |

| PORTD <sup>(6)</sup> | 08h                   | XXXX XXXX                                         | XXXX XXXX                | uuuu uuuu                                        |

| PORTE                | 09h                   | xxxx                                              | xxxx                     | uuuu                                             |

| PCLATH               | 0Ah/8Ah/<br>10Ah/18Ah | 0 0000                                            | 0 0000                   | u uuuu                                           |

| INTCON               | 0Bh/8Bh/<br>10Bh/18Bh | 0000 000x                                         | 0000 000x                | uuuu uuuu <sup>(2)</sup>                         |

| PIR1                 | 0Ch                   | 0000 0000                                         | 0000 0000                | uuuu uuuu <sup>(2)</sup>                         |

| PIR2                 | 0Dh                   | 0                                                 | 0                        | u                                                |

| TMR1L                | 0Eh                   | xxxx xxxx                                         | uuuu uuuu                | <u>uuuu</u> uuuu                                 |

| TMR1H                | 0Fh                   | xxxx xxxx                                         | uuuu uuuu                | սսսս սսսս                                        |

| T1CON                | 10h                   | 0000 00-0                                         | uuuu uu-u                | uuuu uu-u                                        |

| TMR2                 | 11h                   | 0000 0000                                         | 0000 0000                | սսսս սսսս                                        |

| T2CON                | 12h                   | -000 0000                                         | -000 0000                | -uuu uuuu                                        |

| SSPBUF               | 13h                   | xxxx xxxx                                         | XXXX XXXX                | սսսս սսսս                                        |

| SSPCON               | 14h                   | 0000 0000                                         | 0000 0000                | սսսս սսսս                                        |

| CCPR1L               | 15h                   | xxxx xxxx                                         | XXXX XXXX                | սսսս սսսս                                        |

| CCPR1H               | 16h                   | xxxx xxxx                                         | XXXX XXXX                | սսսս սսսս                                        |

| CCP1CON              | 17h                   | 00 0000                                           | 00 0000                  | uu uuuu                                          |

| RCSTA                | 18h                   | 0000 000x                                         | x000 0000x               | uuuu uuuu                                        |

| TXREG                | 19h                   | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |

| RCREG                | 1Ah                   | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |

| CCPR2L               | 1Bh                   | XXXX XXXX                                         | XXXX XXXX                | uuuu uuuu                                        |

| CCPR2H               | 1Ch                   | xxxx xxxx                                         | XXXX XXXX                | uuuu uuuu                                        |

| CCP2CON              | 1Dh                   | 00 0000                                           | 00 0000                  | uu uuuu                                          |

| ADRES                | 1Eh                   | XXXX XXXX                                         | uuuu uuuu                | սսսս սսսս                                        |

| ADCON0               | 1Fh                   | 00 0000                                           | 00 0000                  | uu uuuu                                          |

| OPTION_REG           | 81h/181h              | 1111 1111                                         | 1111 1111                | սսսս սսսս                                        |

| TRISA                | 85h                   | 1111 1111                                         | 1111 1111                | սսսս սսսս                                        |

| TRISB                | 86h                   | 1111 1111                                         | 1111 1111                | սսսս սսսս                                        |

| TRISC                | 87h                   | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |

| TRISD <sup>(6)</sup> | 88h                   | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |

| TRISE                | 89h                   | 1111                                              | 1111                     | uuuu                                             |

| PIE1                 | 8Ch                   | 0000 0000                                         | 0000 0000                | սսսս սսսս                                        |

| PIE2                 | 8Dh                   | 0                                                 | 0                        | u                                                |

TABLE 3-4: INITIALIZATION CONDITION FOR REGISTERS

$\label{eq:Legend: Legend: Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as `0', q = value depends on condition.$

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 and PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 3-5 for Reset value for specific condition.

5: If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

6: PIC16F724/727/PIC16LF724/727 only.

# PIC16(L)F722/3/4/6/7

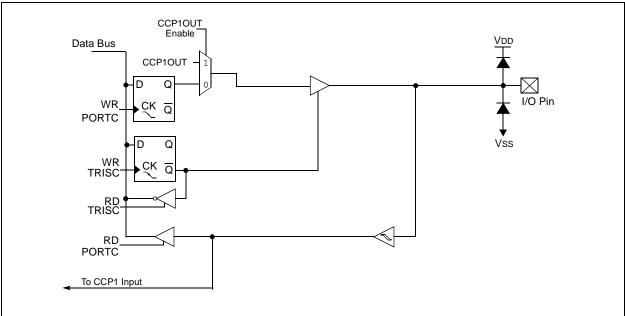

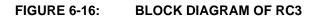

|  | TABLE 6-3: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTC |

|--|------------|--------------------------------------------|

|--|------------|--------------------------------------------|

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|---------|---------|---------|---------|---------|---------|--------|--------|---------|----------------------|---------------------------------|

| APFCON  | —       | —       | _       | —       | -       | _      | SSSEL  | CCP2SEL | 00                   | 00                              |

| CCP1CON | —       | -       | DC1B1   | DC1B0   | CCP1M3  | CCP1M2 | CCP1M1 | CCP1M0  | 00 0000              | 00 0000                         |

| CCP2CON | —       | -       | DC2B1   | DC2B0   | CCP2M3  | CCP2M2 | CCP2M1 | CCP2M0  | 00 0000              | 00 0000                         |

| PORTC   | RC7     | RC6     | RC5     | RC4     | RC3     | RC2    | RC1    | RC0     | xxxx xxxx            | xxxx xxxx                       |

| RCSTA   | SPEN    | RX9     | SREN    | CREN    | ADDEN   | FERR   | OERR   | RX9D    | 0000 000x            | 0000 000x                       |

| SSPCON  | WCOL    | SSPOV   | SSPEN   | CKP     | SSPM3   | SSPM2  | SSPM1  | SSPM0   | 0000 0000            | 0000 0000                       |

| SSPSTAT | SMP     | CKE     | D/A     | Р       | S       | R/W    | UA     | BF      | 0000 0000            | 0000 0000                       |

| T1CON   | TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | _      | TMR1ON  | 0000 00-0            | uuuu uu-u                       |

| TXSTA   | CSRC    | TX9     | TXEN    | SYNC    | —       | BRGH   | TRMT   | TX9D    | 0000 -010            | 0000 -010                       |

| TRISC   | TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2 | TRISC1 | TRISC0  | 1111 1111            | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Port C.

# PIC16(L)F722/3/4/6/7

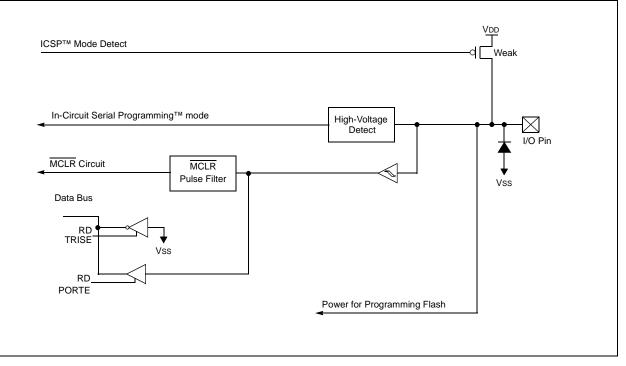

# 12.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- 3-bit prescaler

- Dedicated LP oscillator circuit

- Synchronous or asynchronous operation

- Multiple Timer1 gate (count enable) sources

- Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Time base for the Capture/Compare function

- Special Event Trigger (with CCP)

- Gate Single-pulse mode

- Gate Value StatusGate Event Interrupt

· Gate Toggle mode

Selectable Gate Source Polarity

Figure 12-1 is a block diagram of the Timer1 module.

#### FIGURE 12-1: TIMER1 BLOCK DIAGRAM

# 15.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The Capture/Compare/PWM module is a peripheral which allows the user to time and control different events. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate a pulse-width modulated signal of varying frequency and duty cycle.

The timer resources used by the module are shown in Table 15-1.

Additional information on CCP modules is available in the Application Note AN594, *Using the CCP Modules* (DS00594).

#### TABLE 15-1: CCP MODE – TIMER RESOURCES REQUIRED

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

| CCP1 Mode | CCP2 Mode | Interaction                                                                                                  |

|-----------|-----------|--------------------------------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time base                                                                                          |

| Capture   | Compare   | Same TMR1 time base <sup>(1, 2)</sup>                                                                        |

| Compare   | Compare   | Same TMR1 time base <sup>(1, 2)</sup>                                                                        |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt).<br>The rising edges will be aligned. |

| PWM       | Capture   | None                                                                                                         |

| PWM       | Compare   | None                                                                                                         |

## TABLE 15-2: INTERACTION OF TWO CCP MODULES

Note 1: If CCP2 is configured as a Special Event Trigger, CCP1 will clear Timer1, affecting the value captured on the CCP2 pin.

**2:** If CCP1 is in Capture mode and CCP2 is configured as a Special Event Trigger, CCP2 will clear Timer1, affecting the value captured on the CCP1 pin.

| Note: | CCPRx                                | and | CCPx | throughout | this |  |  |

|-------|--------------------------------------|-----|------|------------|------|--|--|

|       | document refer to CCPR1 or CCPR2 and |     |      |            |      |  |  |

|       | CCP1 or CCP2, respectively           |     |      |            |      |  |  |

| Name                       | Bit 7                                                           | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2     | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on all<br>other Resets |

|----------------------------|-----------------------------------------------------------------|---------|---------|---------|---------|-----------|-----------|-----------|----------------------|------------------------------|

| ANSELA                     | —                                                               | —       | ANSA5   | ANSA4   | ANSA3   | ANSA2     | ANSA1     | ANSA0     | 11 1111              | 11 1111                      |

| APFCON                     | —                                                               | —       | _       | —       | _       | _         | SSSEL     | CCP2SEL   | 00                   | 00                           |

| INTCON                     | GIE                                                             | PEIE    | T0IE    | INTE    | RBIE    | T0IF      | INTF      | RBIF      | 0000 000x            | 0000 000x                    |

| PIE1                       | TMR1GIE                                                         | ADIE    | RCIE    | TXIE    | SSPIE   | CCP1IE    | TMR2IE    | TMR1IE    | 0000 0000            | 0000 0000                    |

| PIR1                       | TMR1GIF                                                         | ADIF    | RCIF    | TXIF    | SSPIF   | CCP1IF    | TMR2IF    | TMR1IF    | 0000 0000            | 0000 0000                    |

| PR2 Timer2 Period Register |                                                                 |         |         |         |         | 1111 1111 | 1111 1111 |           |                      |                              |

| SSPBUF                     | SSPBUF Synchronous Serial Port Receive Buffer/Transmit Register |         |         |         |         |           | XXXX XXXX | uuuu uuuu |                      |                              |

| SSPCON                     | WCOL                                                            | SSPOV   | SSPEN   | CKP     | SSPM3   | SSPM2     | SSPM1     | SSPM0     | 0000 0000            | 0000 0000                    |

| SSPSTAT                    | SMP                                                             | CKE     | D/A     | Р       | S       | R/W       | UA        | BF        | 0000 0000            | 0000 0000                    |

| TRISA                      | TRISA7                                                          | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2    | TRISA1    | TRISA0    | 1111 1111            | 1111 1111                    |

| TRISC                      | TRISC7                                                          | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2    | TRISC1    | TRISC0    | 1111 1111            | 1111 1111                    |

| T2CON                      | _                                                               | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON    | T2CKPS1   | T2CKPS0   | -000 0000            | -000 0000                    |

### TABLE 17-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode.

# 22.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 22.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

- File History and Bug Tracking:

- Local file history feature

- Built-in support for Bugzilla issue tracker

## 23.7 AC Characteristics: PIC16F72X-I/E

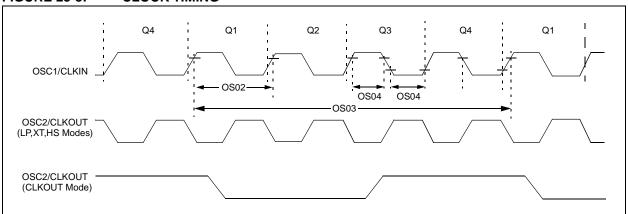

#### FIGURE 23-3: CLOCK TIMING

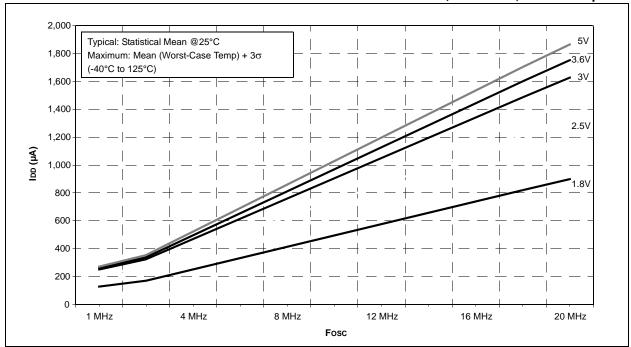

#### FIGURE 24-3: PIC16F722/3/4/6/7 TYPICAL IDD vs. Fosc OVER VDD, EC MODE, VCAP = 0.1 µF

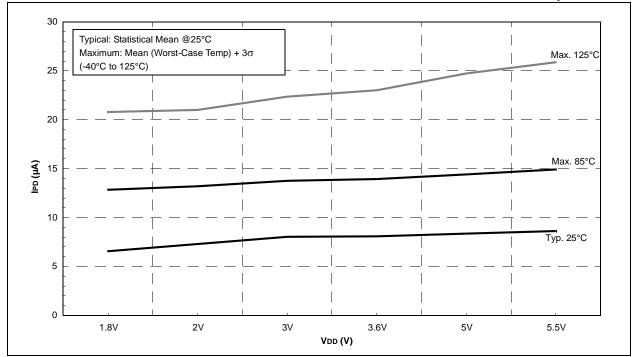

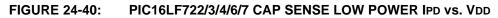

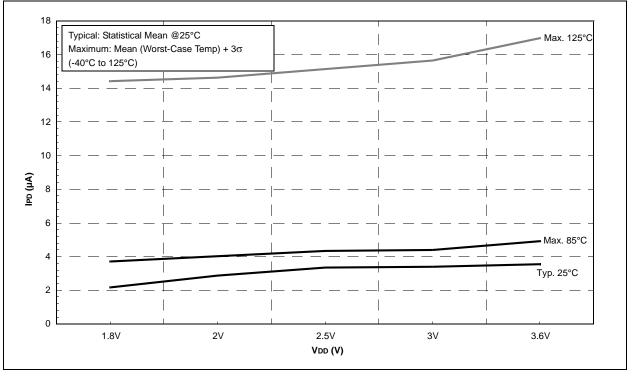

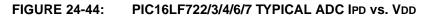

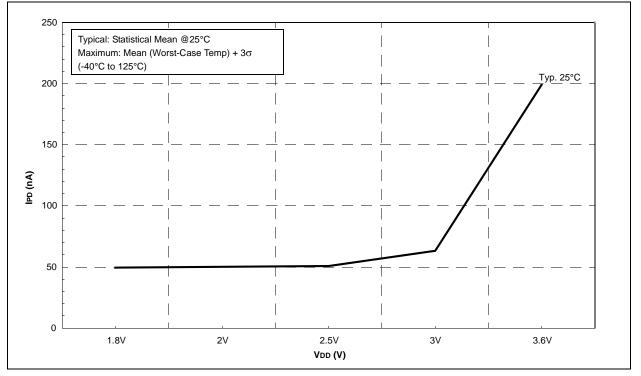

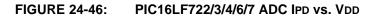

#### FIGURE 24-39: PIC16F722/3/4/6/7 CAP SENSE LOW POWER IPD vs. VDD, VCAP = 0.1 µF

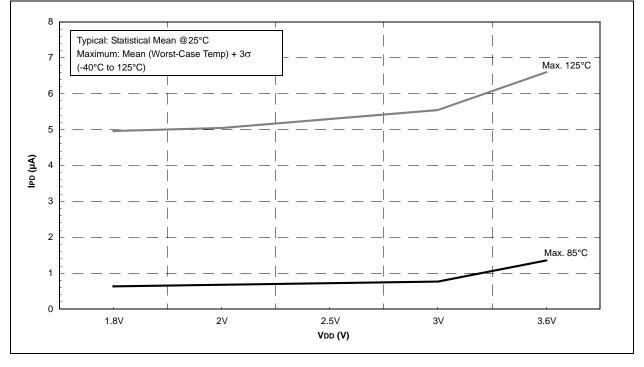

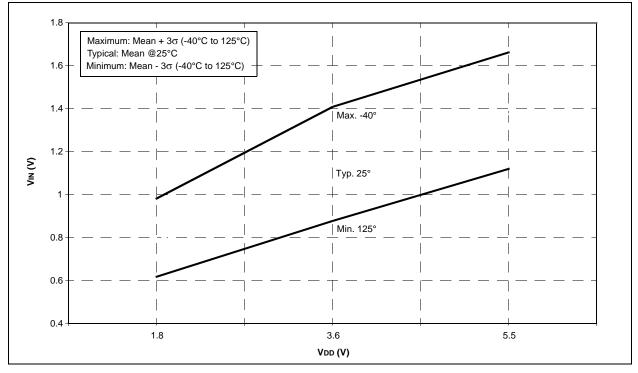

#### FIGURE 24-49: TTL INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

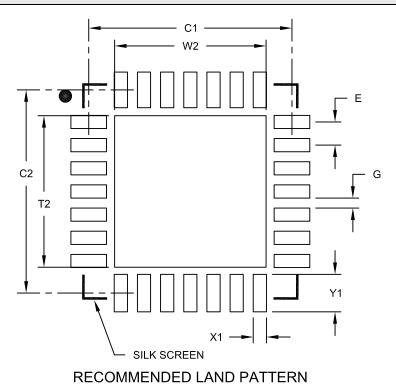

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |          |      |      |

|----------------------------|-------------|----------|------|------|

| Dimensior                  | MIN         | NOM      | MAX  |      |

| Contact Pitch E            |             | 0.65 BSC |      |      |

| Optional Center Pad Width  | W2          |          |      | 4.25 |

| Optional Center Pad Length | T2          |          |      | 4.25 |

| Contact Pad Spacing        | C1          |          | 5.70 |      |

| Contact Pad Spacing        | C2          |          | 5.70 |      |

| Contact Pad Width (X28)    | X1          |          |      | 0.37 |

| Contact Pad Length (X28)   | Y1          |          |      | 1.00 |

| Distance Between Pads      | G           | 0.20     |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A

# APPENDIX A: DATA SHEET REVISION HISTORY

### Revision A (12/2007)

Original release.

### Revision B (08/2008)

Electrical Specification updates; Package Drawings; miscellaneous updates.

### Revision C (04/2009)

Revised data sheet title; Revised Low-Power Features section; Revised Section 6.2.2.4 RA3/AN3/VREF; Revised Figure 16-8 Synchronous Reception.

#### Revision D (07/2009)

Removed the Preliminary Label; Updated the "Electrical Characteristics" section; Added charts in the "Char. Data" section; Deleted "Based 8-Bit CMOS" from title; Updated the "Special Microcontroller Features" section and the "Peripheral Features" section; Changed the title of the "Low Power Features" section into "Extreme Low-Power Management PIC16LF72X with nanoWatt XLP" and updated this section; Inserted new section – "Analog Features" (page 1); Changed the title of the "Peripheral Features" section into "Peripheral Highlights" and updated the section.

## **Revision E (10/2009)**

Added paragraph to section 5.0 (LDO Voltage Regulator); Updated the Electrical Specifications section (Added another absolute Maximum Rating; Updated section 23.1 and Table 23-4); Updated the Pin Diagrams with the UQFN package; Updated Table 1, adding UQFN; Updated section 23.5 (Thermal Considerations); Updated the Packaging Information section adding the UQFN Package; Updated the Product Identification System section.

## **Revision F (12/2015)**

Updated Table 2; Updated 23.1, 23.3 and 9.2.4 Sections; Updated Figure 23-9; Other minor corrections.

# APPENDIX B: MIGRATING FROM OTHER PIC® DEVICES

This discusses some of the issues in migrating from other  $\text{PIC}^{\textcircled{B}}$  devices to the PIC16F72X family of devices.

## B.1 PIC16F77 to PIC16F72X

#### TABLE B-1: FEATURE COMPARISON

| Feature                               | PIC16F77 | PIC16F727           |  |  |

|---------------------------------------|----------|---------------------|--|--|

| Max. Operating Speed                  | 20 MHz   | 20 MHz              |  |  |

| Max. Program<br>Memory (Words)        | 8K       | 8K                  |  |  |

| Max. SRAM (Bytes)                     | 368      | 368                 |  |  |

| A/D Resolution                        | 8-bit    | 8-bit               |  |  |

| Timers (8/16-bit)                     | 2/1      | 2/1                 |  |  |

| Oscillator Modes                      | 4        | 8                   |  |  |

| Brown-out Reset                       | Y        | Y                   |  |  |

| Internal Pull-ups                     | RB<7:0>  | RB<7:0>             |  |  |

| Interrupt-on-change                   | RB<7:4>  | RB<7:0>             |  |  |

| Comparator                            | 0        | 0                   |  |  |

| USART                                 | Y        | Y                   |  |  |

| Extended WDT                          | Ν        | N                   |  |  |

| Software Control<br>Option of WDT/BOR | N        | N                   |  |  |

| INTOSC Frequencies                    | None     | 500 kHz -<br>16 MHz |  |  |

| Clock Switching                       | Ν        | Ν                   |  |  |