Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 14x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f727t-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F722/3/4/6/7

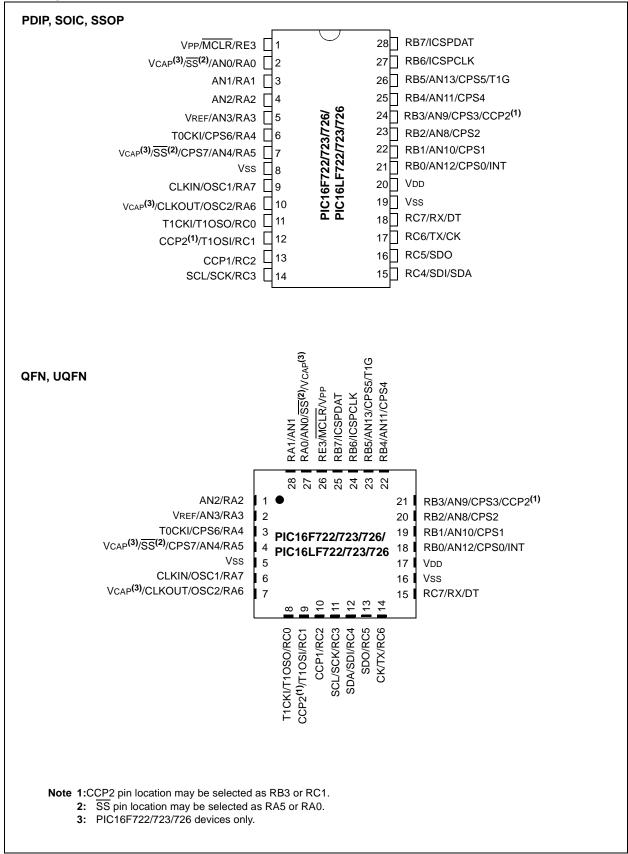

#### Pin Diagrams - 28-PIN PDIP/SOIC/SSOP/QFN/UQFN (PIC16F722/723/726/PIC16LF722/723/726)

#### 2.2.2.2 OPTION register

The OPTION register, shown in Register 2-2, is a readable and writable register, which contains various control bits to configure:

- Timer0/WDT prescaler

- External RB0/INT interrupt

- Timer0

- Weak pull-ups on PORTB

| Note: | To achieve a 1:1 prescaler assignment for |

|-------|-------------------------------------------|

|       | Timer0, assign the prescaler to the WDT   |

|       | by setting the PSA bit of the             |

|       | OPTION_REG register to '1'. Refer to      |

|       | Section 11.1.3 "Software                  |

|       | Programmable Prescaler".                  |

### REGISTER 2-2: OPTION\_REG: OPTION REGISTER

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | <b>RBPU:</b> PORTB Pull-up Enable bit<br>1 = PORTB pull-ups are disabled<br>0 = PORTB pull-ups are enabled by individual bits in the WPUB register                 |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| bit 6   | INTEDG: Interrupt Edge Select bit<br>1 = Interrupt on rising edge of RB0/INT pin<br>0 = Interrupt on falling edge of RB0/INT pin                                   |  |  |  |  |  |

| bit 5   | <b>TOCS:</b> Timer0 Clock Source Select bit<br>1 = Transition on RA4/T0CKI pin<br>0 = Internal instruction cycle clock (Fosc/4)                                    |  |  |  |  |  |

| bit 4   | <b>T0SE:</b> Timer0 Source Edge Select bit<br>1 = Increment on high-to-low transition on RA4/T0CKI pin<br>0 = Increment on low-to-high transition on RA4/T0CKI pin |  |  |  |  |  |

| bit 3   | <b>PSA:</b> Prescaler Assignment bit<br>1 = Prescaler is assigned to the WDT<br>0 = Prescaler is assigned to the Timer0 module                                     |  |  |  |  |  |

| bit 2-0 | PS<2:0>: Prescaler Rate Select bits                                                                                                                                |  |  |  |  |  |

|         | Bit Value Timer0 Rate WDT Rate                                                                                                                                     |  |  |  |  |  |

|         | 000 1:2 1:1   001 1:4 1:2   010 1:8 1:4   011 1:16 1:8   100 1:32 1:16   101 1:64 1:32                                                                             |  |  |  |  |  |

1:128

1:256

1:64

1 : 128

110

111

| R/W-0                  | R/W-0                           | R/W-0                                                     | R/W-0          | R/W-0               | R/W-0               | R/W-0           | R/W-x        |

|------------------------|---------------------------------|-----------------------------------------------------------|----------------|---------------------|---------------------|-----------------|--------------|

| GIE                    | PEIE                            | TOIE                                                      | INTE           | RBIE <sup>(1)</sup> | T0IF <sup>(2)</sup> | INTF            | RBIF         |

| bit 7                  |                                 |                                                           |                |                     |                     |                 | bit C        |

|                        |                                 |                                                           |                |                     |                     |                 |              |

| Legend:<br>R = Readabl | o hit                           | W = Writable I                                            | nit            | II – I Inimpler     | nented bit, read    | 1 26 '0'        |              |

| -n = Value at          |                                 | '1' = Bit is set                                          | JIL            | 0' = Bit is cle     |                     | x = Bit is unkr | NOWD         |

|                        |                                 | 1 – Dit 13 Set                                            |                |                     | areu                |                 | IOWIT        |

| bit 7                  | GIE: Global Ir                  | nterrupt Enable                                           | bit            |                     |                     |                 |              |

|                        | 1 = Enables a<br>0 = Disables a | all unmasked in all interrupts                            | terrupts       |                     |                     |                 |              |

| bit 6                  | 1 = Enables a                   | eral Interrupt Er<br>all unmasked pe<br>all peripheral in | eripheral inte | rrupts              |                     |                 |              |

| bit 5                  | 1 = Enables t                   | Overflow Interr<br>he Timer0 inter<br>the Timer0 inter    | rupt           | it                  |                     |                 |              |

| bit 4                  | 1 = Enables t                   | IT External Inte<br>he RB0/INT ext<br>the RB0/INT ex      | ernal interru  | ot                  |                     |                 |              |

| bit 3                  | 1 = Enables t                   | B Change Intern<br>he PORTB cha<br>the PORTB cha          | nge interrupt  |                     |                     |                 |              |

| bit 2                  | 1 = TMR0 reg                    | Overflow Interr<br>gister has overfl<br>gister did not ov | owed (must l   |                     | oftware)            |                 |              |

| bit 1                  | 1 = The RB0/                    | T External Inte<br>INT external int<br>INT external int   | errupt occuri  | ed (must be cle     | eared in softwa     | re)             |              |

| bit 0                  |                                 |                                                           |                | eneral purpose      | I/O pins chang      | jed state (must | be cleared i |

|                        | 0 = None of t                   |                                                           |                |                     | h                   |                 |              |

#### **REGISTER 4-1:** INTCON: INTERRUPT CONTROL REGISTER

- The appropriate bits in the IOCB register must also be set. Note 1:

- 2: T0IF bit is set when Timer0 rolls over. Timer0 is unchanged on Reset and should be initialized before clearing T0IF bit.

| R/W-1                           | R/W-1 | R/W-1            | R/W-1        | R/W-1            | R/W-1    | R/W-1           | R/W-1 |

|---------------------------------|-------|------------------|--------------|------------------|----------|-----------------|-------|

| WPUB7                           | WPUB6 | WPUB5            | WPUB4        | WPUB3            | WPUB2    | WPUB1           | WPUB0 |

| bit 7                           |       |                  | •            |                  |          | •               | bit 0 |

|                                 |       |                  |              |                  |          |                 |       |

| Legend:                         |       |                  |              |                  |          |                 |       |

| R = Readable bit W = Writable b |       | bit              | U = Unimpler | nented bit, read | l as '0' |                 |       |

| -n = Value at POR               |       | '1' = Bit is set |              | '0' = Bit is cle | ared     | x = Bit is unkr | nown  |

#### REGISTER 6-7: WPUB: WEAK PULL-UP PORTB REGISTER

bit 7-0 WPUB<7:0>: Weak Pull-up Register bits

- 1 = Pull-up enabled

- 0 = Pull-up disabled

**Note 1:** Global RBPU bit of the OPTION register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

#### REGISTER 6-8: IOCB: INTERRUPT-ON-CHANGE PORTB REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IOCB7 | IOCB6 | IOCB5 | IOCB4 | IOCB3 | IOCB2 | IOCB1 | IOCB0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 **IOCB<7:0>:** Interrupt-on-Change PORTB Control bits

1 = Interrupt-on-change enabled

0 = Interrupt-on-change disabled

#### REGISTER 6-9: ANSELB: PORTB ANALOG SELECT REGISTER

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | ANSB5 | ANSB4 | ANSB3 | ANSB2 | ANSB1 | ANSB0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 ANSB<5:0>: Analog Select between Analog or Digital Function on Pins RB<5:0>, respectively

0 = Digital I/O. Pin is assigned to port or Digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital Input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

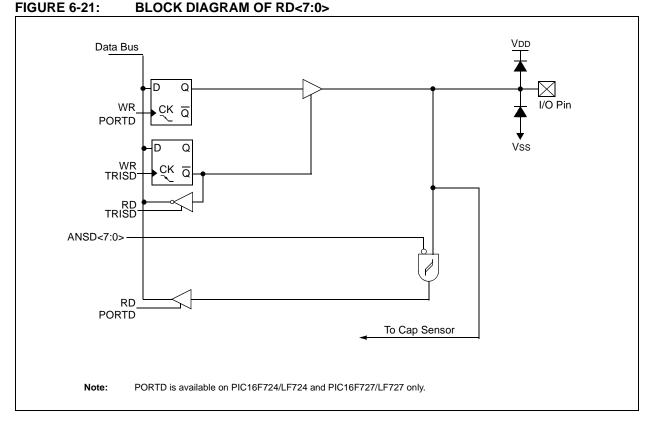

#### 6.5.6 RD4/CPS12

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### 6.5.7 RD5/CPS13

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- a capacitive sensing input

#### 6.5.8 RD6/CPS14

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### 6.5.9 RD7/CPS15

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

| TABLE 6-4: SUMM | IARY OF REGISTERS ASSOCIATED WITH PORTD <sup>(1)</sup> |

|-----------------|--------------------------------------------------------|

|-----------------|--------------------------------------------------------|

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|--------|--------|--------|---------|---------|--------|--------|----------------------|---------------------------------|

| ANSELD  | ANSD7  | ANSD6  | ANSD5  | ANSD4  | ANSD3   | ANSD2   | ANSD1  | ANSD0  | 1111 1111            | 1111 1111                       |

| CPSCON0 | CPSON  | —      | —      | —      | CPSRNG1 | CPSRNG0 | CPSOUT | TOXCS  | 0 0000               | 0 0000                          |

| CPSCON1 |        | —      | —      | _      | CPSCH3  | CPSCH2  | CPSCH1 | CPSCH0 | 0000                 | 0000                            |

| PORTD   | RD7    | RD6    | RD5    | RD4    | RD3     | RD2     | RD1    | RD0    | XXXX XXXX            | xxxx xxxx                       |

| TRISD   | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3  | TRISD2  | TRISD1 | TRISD0 | 1111 1111            | 1111 1111                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTD.**Note 1:**These registers are not implemented on the PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'.

#### © 2007-2015 Microchip Technology Inc.

#### DS40001341F-page 79

## PIC16(L)F722/3/4/6/7

### 8.0 DEVICE CONFIGURATION

Device Configuration consists of Configuration Word 1 and Configuration Word 2 registers, Code Protection and Device ID.

#### 8.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 register at 2007h and Configuration Word 2 register at 2008h. These registers are only accessible during programming.

#### REGISTER 8-1: CONFIG1: CONFIGURATION WORD REGISTER 1

|        |        | R/P-1 | R/P-1 | U-1 <sup>(4)</sup> | R/P-1 | R/P-1  | R/P-1  |

|--------|--------|-------|-------|--------------------|-------|--------|--------|

| —      | — — DE |       | PLLEN | _                  | BORV  | BOREN1 | BOREN0 |

| bit 15 |        |       |       |                    |       |        | bit 8  |

| U-1 <sup>(4)</sup> | R/P-1 | R/P-1 R/P-1 |       | R/P-1 R/P-1 |       | R/P-1 | R/P-1 |

|--------------------|-------|-------------|-------|-------------|-------|-------|-------|

| _                  | CP    | MCLRE       | PWRTE | WDTE        | FOSC2 | FOSC1 | FOSC0 |

| bit 7              |       |             |       |             |       |       | bit 0 |

| Legend:           | P = Programmable bit | P = Programmable bit               |                    |  |  |  |  |  |

|-------------------|----------------------|------------------------------------|--------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |

| bit 13              | <b>DEBUG:</b> In-Circuit Debugger Mode bit<br>1 = In-Circuit Debugger disabled, RB6/ICSPCLK and RB7/ICSPDAT are general purpose I/O pins<br>0 = In-Circuit Debugger enabled, RB6/ICSPCLK and RB7/ICSPDAT are dedicated to the debugger                            |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bit 12              | PLLEN: INTOSC PLL Enable bit<br>0 = INTOSC Frequency is 500 kHz<br>1 = INTOSC Frequency is 16 MHz (32x)                                                                                                                                                           |  |

| bit 11              | Unimplemented: Read as '1'                                                                                                                                                                                                                                        |  |

| bit 10              | <b>BORV:</b> Brown-out Reset Voltage selection bit<br>0 = Brown-out Reset Voltage (VBOR) set to 2.5 V nominal<br>1 = Brown-out Reset Voltage (VBOR) set to 1.9 V nominal                                                                                          |  |

| bit 9-8             | <b>BOREN&lt;1:0&gt;:</b> Brown-out Reset Selection bits <sup>(1)</sup><br>0x = BOR disabled (Preconditioned State)<br>10 = BOR enabled during operation and disabled in Sleep<br>11 = BOR enabled                                                                 |  |

| bit 7               | Unimplemented: Read as '1'                                                                                                                                                                                                                                        |  |

| bit 6               | <b>CP</b> : Code Protection bit <sup>(2)</sup><br>1 = Program memory code protection is disabled<br>0 = Program memory code protection is enabled                                                                                                                 |  |

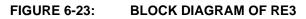

| bit 5               | MCLRE: <u>RE3/MCLR</u> pin function select bit <sup>(3)</sup><br>1 = RE3/ <u>MCLR</u> pin function is MCLR<br>0 = RE3/MCLR pin function is digital input, MCLR internally tied to VDD                                                                             |  |

| Note 1:<br>2:<br>3: | Enabling Brown-out Reset does not automatically enable Power-up Timer.<br>The entire program memory will be erased when the code protection is turned off.<br>When $\overline{MCLR}$ is asserted in INTOSC or RC mode, the internal clock oscillator is disabled. |  |

**4:** MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

| R/W-1           | R/W-1                                                                                                                                      | R/W-1                                                        | R/W-1                                  | R/W-1            | R/W-1            | R/W-1           | R/W-1 |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------|------------------|------------------|-----------------|-------|--|--|--|--|

| RBPU            | INTEDG                                                                                                                                     | TOCS                                                         | TOSE                                   | PSA              | PS2              | PS1             | PS0   |  |  |  |  |

| bit 7           |                                                                                                                                            |                                                              |                                        |                  |                  |                 | bit ( |  |  |  |  |

|                 |                                                                                                                                            |                                                              |                                        |                  |                  |                 |       |  |  |  |  |

| Legend:         |                                                                                                                                            |                                                              |                                        |                  |                  |                 |       |  |  |  |  |

| R = Readable    | bit                                                                                                                                        | W = Writable                                                 | bit                                    | U = Unimpler     | nented bit, read | d as '0'        |       |  |  |  |  |

| -n = Value at F | POR                                                                                                                                        | '1' = Bit is se                                              | t                                      | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |  |

| bit 7           |                                                                                                                                            | ull-ups are dis                                              | abled                                  | dual port latch  | values           |                 |       |  |  |  |  |

| bit 6           | •                                                                                                                                          | errupt Edge Se<br>on rising edge<br>on falling edge          | of INT pin                             |                  |                  |                 |       |  |  |  |  |

| bit 5           | <b>TOCS:</b> TMR0 Clock Source Select bit<br>1 = Transition on T0CKI pin or CPSOSC signal<br>0 = Internal instruction cycle clock (FOSC/4) |                                                              |                                        |                  |                  |                 |       |  |  |  |  |

| bit 4           |                                                                                                                                            | Source Edge<br>t on high-to-lov<br>t on low-to-hig           | w transition or                        |                  |                  |                 |       |  |  |  |  |

| bit 3           |                                                                                                                                            | er Assignmen<br>is assigned to<br>is assigned to             | the WDT                                | nodule           |                  |                 |       |  |  |  |  |

| bit 2-0         | <b>PS&lt;2:0&gt;:</b> Pre                                                                                                                  | escaler Rate S                                               | elect bits                             |                  |                  |                 |       |  |  |  |  |

|                 | BIT                                                                                                                                        | VALUE TMR0 R                                                 | ATE WDT RA                             | TE               |                  |                 |       |  |  |  |  |

|                 | 0<br>0<br>1<br>1<br>1                                                                                                                      | 00 1:2   01 1:4   10 1:8   11 1:1   00 1:3   01 1:6   10 1:1 | 1:2   1:4   1:8   1:16   4   1:32   28 |                  |                  |                 |       |  |  |  |  |

| TABLE 11-1:     |                                                                                                                                            |                                                              | TERS ASSO                              |                  | H TIMERO         |                 |       |  |  |  |  |

#### REGISTER 11-1: OPTION\_REG: OPTION REGISTER

| Name       | Bit 7     | Bit 6         | Bit 5     | Bit 4     | Bit 3   | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|-----------|---------------|-----------|-----------|---------|---------|--------|--------|----------------------|---------------------------------|

| CPSCON0    | CPSON     |               |           |           | CPSRNG1 | CPSRNG0 | CPSOUT | T0XCS  | 0 0000               | 0 0000                          |

| INTCON     | GIE       | PEIE          | TOIE      | INTE      | RBIE    | T0IF    | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| OPTION_REG | RBPU      | INTEDG        | TOCS      | TOSE      | PSA     | PS2     | PS1    | PS0    | 1111 1111            | 1111 1111                       |

| TMR0       | Timer0 Mo | dule Register | xxxx xxxx | uuuu uuuu |         |         |        |        |                      |                                 |

| TRISA      | TRISA7    | TRISA6        | TRISA5    | TRISA4    | TRISA3  | TRISA2  | TRISA1 | TRISA0 | 1111 1111            | 1111 1111                       |

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Timer0 module.

| U-0             | R/W-0                        | R/W-0                  | R/W-0          | R/W-0             | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |

|-----------------|------------------------------|------------------------|----------------|-------------------|-----------------|-----------------|---------|--|--|--|--|

|                 | TOUTPS3                      | TOUTPS2                | TOUTPS1        | TOUTPS0           | TMR2ON          | T2CKPS1         | T2CKPS0 |  |  |  |  |

| bit 7           |                              |                        |                |                   |                 |                 | bit 0   |  |  |  |  |

|                 |                              |                        |                |                   |                 |                 |         |  |  |  |  |

| Legend:         |                              |                        |                |                   |                 |                 |         |  |  |  |  |

| R = Readable    | bit                          | W = Writable bit       |                | U = Unimplen      | nented bit, rea | d as '0'        |         |  |  |  |  |

| -n = Value at P | POR                          | '1' = Bit is set       |                | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |  |  |  |  |

| bit 7           | Unimplemen                   | ted: Read as '         | 0'             |                   |                 |                 |         |  |  |  |  |

| bit 6-3         | TOUTPS<3:0                   | >: Timer2 Out          | out Postscaler | Select bits       |                 |                 |         |  |  |  |  |

|                 | 0000 = 1:1 P                 | -                      |                |                   |                 |                 |         |  |  |  |  |

|                 | 0001 = 1:2 P                 | ostscaler              |                |                   |                 |                 |         |  |  |  |  |

|                 | 0010 = 1:3 P                 | ostscaler              |                |                   |                 |                 |         |  |  |  |  |

|                 | 0011 = 1:4 P                 |                        |                |                   |                 |                 |         |  |  |  |  |

|                 |                              | 1:5 Postscaler         |                |                   |                 |                 |         |  |  |  |  |

|                 |                              | :6 Postscaler          |                |                   |                 |                 |         |  |  |  |  |

|                 | 0110 = 1:7 P<br>0111 = 1:8 P |                        |                |                   |                 |                 |         |  |  |  |  |

|                 | 1000 = 1.9 P                 |                        |                |                   |                 |                 |         |  |  |  |  |

|                 | 1000 = 1.31                  |                        |                |                   |                 |                 |         |  |  |  |  |

|                 | 1010 = 1:11                  |                        |                |                   |                 |                 |         |  |  |  |  |

|                 | 1011 = <b>1:12</b>           | Postscaler             |                |                   |                 |                 |         |  |  |  |  |

|                 | 1100 <b>= 1:13</b>           | 1100 = 1:13 Postscaler |                |                   |                 |                 |         |  |  |  |  |

|                 | 1101 = 1:14 Postscaler       |                        |                |                   |                 |                 |         |  |  |  |  |

|                 | 1110 = 1:15 Postscaler       |                        |                |                   |                 |                 |         |  |  |  |  |

|                 | 1111 = 1:16                  |                        |                |                   |                 |                 |         |  |  |  |  |

| bit 2           | TMR2ON: Tir                  | ner2 On bit            |                |                   |                 |                 |         |  |  |  |  |

|                 | 1 = Timer2 is                |                        |                |                   |                 |                 |         |  |  |  |  |

|                 | 0 = Timer2 is                | s off                  |                |                   |                 |                 |         |  |  |  |  |

| bit 1-0         | T2CKPS<1:0                   | >: Timer2 Cloc         | k Prescale Sel | ect bits          |                 |                 |         |  |  |  |  |

|                 | 00 = Prescale                |                        |                |                   |                 |                 |         |  |  |  |  |

|                 | 01 = Prescale                | -                      |                |                   |                 |                 |         |  |  |  |  |

|                 | 1x = Prescale                | er is 16               |                |                   |                 |                 |         |  |  |  |  |

| TABLE 13-1:     | SUMMAR                       |                        | FRS ASSO       | CIATED WITH       | H TIMER2        |                 |         |  |  |  |  |

#### REGISTER 13-1: T2CON: TIMER2 CONTROL REGISTER

| IADEE  | 10-1.      |                |         |           |           |        |         | 14      |                      |                                 |

|--------|------------|----------------|---------|-----------|-----------|--------|---------|---------|----------------------|---------------------------------|

| Name   | Bit 7      | Bit 6          | Bit 5   | Bit 4     | Bit 3     | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| INTCON | GIE        | PEIE           | T0IE    | INTE      | RBIE      | T0IF   | INTF    | RBIF    | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE    | ADIE           | RCIE    | TXIE      | SSPIE     | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF    | ADIF           | RCIF    | TXIF      | SSPIF     | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| PR2    | Timer2 Mod | dule Period R  | egister |           |           |        |         |         | 1111 1111            | 1111 1111                       |

| TMR2   | Holding Re | gister for the |         | 0000 0000 | 0000 0000 |        |         |         |                      |                                 |

| T2CON  | _          | TOUTPS3        | TOUTPS2 | TOUTPS1   | TOUTPS0   | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module. Legend:

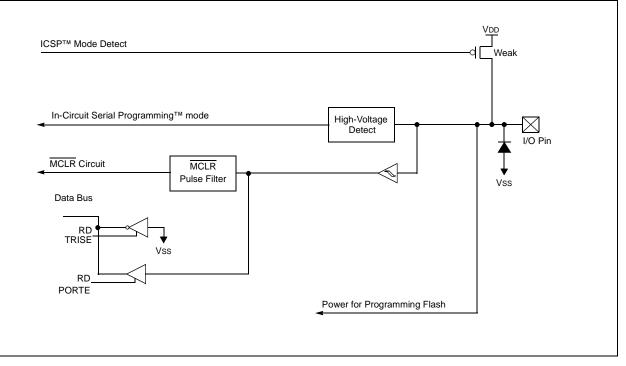

### 14.0 CAPACITIVE SENSING MODULE

The capacitive sensing module allows for an interaction with an end user without a mechanical interface. In a typical application, the capacitive sensing module is attached to a pad on a printed circuit board (PCB), which is electrically isolated from the end user. When the end user places their finger over the PCB pad, a capacitive load is added, causing a frequency shift in the capacitive sensing module. The capacitive sensing module requires software and at least one timer resource to determine the change in frequency. Key features of this module include:

- · Analog MUX for monitoring multiple inputs

- · Capacitive sensing oscillator

- Multiple timer resources

- Software control

- · Operation during Sleep

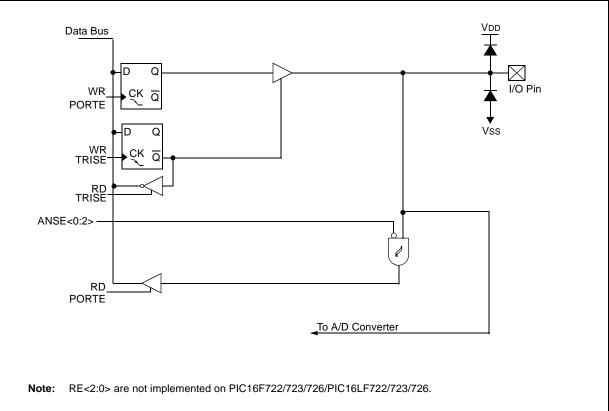

#### FIGURE 14-1: CAPACITIVE SENSING BLOCK DIAGRAM

| Name    | Bit 7                                   | Bit 6                                    | Bit 5          | Bit 4          | Bit 3                   | Bit 2    | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-----------------------------------------|------------------------------------------|----------------|----------------|-------------------------|----------|---------|---------|----------------------|---------------------------------|

| ADCON0  | _                                       |                                          | CHS3           | CHS2           | CHS1                    | CHS0     | GO/DONE | ADON    | 00 0000              | 00 0000                         |

| ANSELB  | _                                       | _                                        | ANSB5          | ANSB4          | ANSB3                   | ANSB2    | ANSB1   | ANSB0   | 11 1111              | 11 1111                         |

| APFCON  | _                                       | _                                        | _              | _              | _                       | _        | SSSEL   | CCP2SEL | 00                   | 00                              |

| CCP1CON | _                                       | _                                        | DC1B1          | DC1B0          | CCP1M3                  | CCP1M2   | CCP1M1  | CCP1M0  | 00 0000              | 00 0000                         |

| CCP2CON | _                                       | _                                        | DC2B1          | DC2B0          | CCP2M3                  | CCP2M2   | CCP2M1  | CCP2M0  | 00 0000              | 00 0000                         |

| CCPRxL  | Capture/Compare/PWM Register X Low Byte |                                          |                |                |                         |          |         |         | xxxx xxxx            | uuuu uuuu                       |

| CCPRxH  | Capture/Com                             | Capture/Compare/PWM Register X High Byte |                |                |                         |          |         |         |                      |                                 |

| INTCON  | GIE                                     | PEIE                                     | TOIE           | INTE           | RBIE                    | T0IF     | INTF    | RBIF    | 0000 000x            | 0000 000x                       |

| PIE1    | TMR1GIE                                 | ADIE                                     | RCIE           | TXIE           | SSPIE                   | CCP1IE   | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIE2    | —                                       | -                                        | —              | -              | —                       | —        | —       | CCP2IE  | 0                    | 0                               |

| PIR1    | TMR1GIF                                 | ADIF                                     | RCIF           | TXIF           | SSPIF                   | CCP1IF   | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| PIR2    | —                                       | -                                        | —              | -              | —                       | —        | —       | CCP2IF  | 0                    | 0                               |

| T1CON   | TMR1CS1                                 | TMR1CS0                                  | T1CKPS1        | T1CKPS0        | T1OSCEN                 | T1SYNC   | _       | TMR10N  | 0000 00-0            | uuuu uu-u                       |

| T1GCON  | TMR1GE                                  | T1GPOL                                   | T1GTM          | T1GSPM         | T <u>1GGO</u> /<br>DONE | T1GVAL   | T1GSS1  | T1GSS0  | 0000 0x00            | 00x0 0x00                       |

| TMR1L   | Holding Regi                            | ster for the L                           | east Significa | nt Byte of the | 16-bit TMR1 I           | Register |         |         | xxxx xxxx            | uuuu uuuu                       |

| TMR1H   | Holding Regi                            | ster for the M                           | ost Significar | nt Byte of the | 16-bit TMR1 F           | Register |         |         | xxxx xxxx            | uuuu uuuu                       |

| TRISB   | TRISB7                                  | TRISB6                                   | TRISB5         | TRISB4         | TRISB3                  | TRISB2   | TRISB1  | TRISB0  | 1111 1111            | 1111 1111                       |

| TRISC   | TRISC7                                  | TRISC6                                   | TRISC5         | TRISC4         | TRISC3                  | TRISC2   | TRISC1  | TRISC0  | 1111 1111            | 1111 1111                       |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Compare.

#### 15.3.4 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 15-4.

#### EQUATION 15-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2+1)]}{\log(2)}$$

bits

Note: If the pulse-width value is greater than the period, the assigned PWM pin(s) will remain unchanged.

#### TABLE 15-5: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 15-6: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 15.3.5 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 15.3.6 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency (Fosc). Any changes in the system clock frequency will result in changes to the PWM frequency. Refer to **Section 7.0** "**Oscillator Module**" for additional details.

#### 15.3.7 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 15.3.8 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Disable the PWM pin (CCPx) output driver(s) by setting the associated TRIS bit(s).

- 2. Load the PR2 register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- Load the CCPRxL register and the DCxBx bits of the CCPxCON register, with the PWM duty cycle value.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register. See Note below.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until Timer2 overflows, TMR2IF bit of the PIR1 register is set. See Note below.

- Enable the PWM pin (CCPx) output driver(s) by clearing the associated TRIS bit(s).

- **Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

#### 17.1.2 SLAVE MODE

For any SPI device acting as a slave, the data is transmitted and received as external clock pulses appear on SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

#### 17.1.2.1 Slave Mode Operation

The SSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready.

The slave has no control as to when data will be clocked in or out of the device. All data that is to be transmitted, to a master or another slave, must be loaded into the SSPBUF register before the first clock pulse is received.

Once eight bits of data have been received:

- · Received byte is moved to the SSPBUF register

- BF bit of the SSPSTAT register is set

- SSPIF bit of the PIR1 register is set

Any write to the SSPBUF register during transmission/reception of data will be ignored and the Write Collision Detect bit, WCOL of the SSPCON register, will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

The user's firmware must read SSPBUF, clearing the BF flag, or the SSPOV bit of the SSPCON register will be set with the reception of the next byte and communication will be disabled.

A SPI module transmits and receives at the same time, occasionally causing dummy data to be transmitted/received. It is up to the user to determine which data is to be used and what can be discarded.

#### 17.1.2.2 Enabling Slave I/O

To enable the serial port, the SSPEN bit of the SSPCON register must be set. If a Slave mode of operation is selected in the SSPM bits of the SSPCON register, the SDI, SDO, SCK pins will be assigned as serial port pins.

For these pins to function as serial port pins, they must have their corresponding data direction bits set or cleared in the associated TRIS register as follows:

- · SDI configured as input

- · SDO configured as output

- · SCK configured as input

Optionally, a fourth pin, Slave Select  $(\overline{SS})$  may be used in Slave mode. Slave Select may be configured to operate on one of the following pins via the SSSEL bit in the APFCON register.

- RA5/AN4/SS

- RA0/AN0/SS

Upon selection of a Slave Select pin, the appropriate bits must be set in the ANSELA and TRISA registers. Slave Select must be set as an input by setting the corresponding bit in TRISA, and digital I/O must be enabled on the SS pin by clearing the corresponding bit of the ANSELA register.

#### 17.1.2.3 Slave Mode Setup

When initializing the SSP module to SPI Slave mode, compatibility must be ensured with the master device. This is done by programming the appropriate control bits of the SSPCON and SSPSTAT registers. These control bits allow the following to be specified:

- · SCK as clock input

- Idle state of SCK (CKP bit)

- Data input sample phase (SMP bit)

- Output data on rising/falling edge of SCK (CKE bit)

Figure 17-4 and Figure 17-5 show example waveforms of Slave mode operation.

#### REGISTER 17-2: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (SPI MODE)

| R/W-0 | R/W-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| SMP   | CKE   | D/A | Р   | S   | R/W | UA  | BF    |

| bit 7 |       |     |     |     |     |     | bit 0 |

| R = Readabl       | le bit                       | W = Writable bit                                     | U = Unimplemented bit | , read as '0'      |

|-------------------|------------------------------|------------------------------------------------------|-----------------------|--------------------|

| -n = Value at POR |                              | '1' = Bit is set                                     | '0' = Bit is cleared  | x = Bit is unknown |

|                   |                              |                                                      |                       |                    |

| bit 7             | SMP: SF                      | PI Data Input Sample Phase                           | bit                   |                    |

|                   |                              | ter mode:                                            |                       |                    |

|                   | •                            | t data sampled at end of data                        | •                     |                    |

|                   | 0 = Input<br><u>SPI Slav</u> | t data sampled at middle of c                        | data output time      |                    |

|                   |                              | ist be cleared when SPI is us                        | sed in Slave mode     |                    |

| bit 6             | CKE: SP                      | PI Clock Edge Select bit                             |                       |                    |

|                   |                              | le, CKP = 0:                                         |                       |                    |

|                   |                              | stable on rising edge of SCI                         |                       |                    |

|                   |                              | stable on falling edge of SC                         | K                     |                    |

|                   |                              | l <u>e, CKP = 1:</u><br>stable on falling edge of SC | ĸ                     |                    |

|                   |                              | stable on rising edge of SCI                         |                       |                    |

| bit 5             |                              | ta/Address bit                                       |                       |                    |

|                   | Used in I                    | l <sup>2</sup> C mode only.                          |                       |                    |

| bit 4             | P: Stop b                    | oit                                                  |                       |                    |

|                   | Used in I                    | I <sup>2</sup> C mode only.                          |                       |                    |

| bit 3             | S: Start I                   | bit                                                  |                       |                    |

|                   | Used in                      | I <sup>2</sup> C mode only.                          |                       |                    |

| bit 2             | R/W: Re                      | ad/Write Information bit                             |                       |                    |

|                   | Used in I                    | l <sup>2</sup> C mode only.                          |                       |                    |

| bit 1             | UA: Upd                      | late Address bit                                     |                       |                    |

|                   | Used in I                    | I <sup>2</sup> C mode only.                          |                       |                    |

| bit 0             | BF: Buffe                    | er Full Status bit                                   |                       |                    |

|                   |                              | eive complete, SSPBUF is fu                          |                       |                    |

|                   | 0 - Rece                     | eive not complete, SSPBUF                            | ic omntv              |                    |

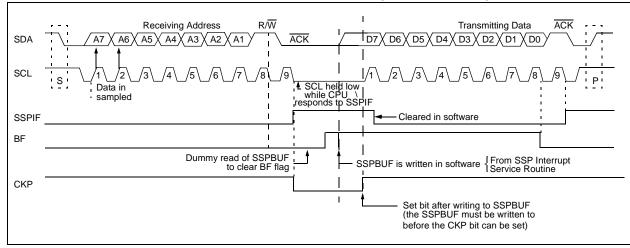

#### 17.2.6 TRANSMISSION

When the R/W bit of the received address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set and the slave will respond to the master by reading out data. After the address match, an ACK pulse is generated by the slave hardware and the SCL pin is held low (clock is automatically stretched) until the slave is ready to respond. See **Section 17.2.7 "Clock Stretching"**. The data the slave will transmit must be loaded into the SSPBUF register, which sets the BF bit. The SCL line is released by setting the CKP bit of the SSPCON register.

An SSP interrupt is generated for each transferred data byte. The SSPIF flag bit of the PIR1 register initiates an SSP interrupt, and must be cleared by software before the next byte is transmitted. The BF bit of the SSPSTAT register is cleared on the falling edge of the eighth received clock pulse. The SSPIF flag bit is set on the falling edge of the ninth clock pulse. Following the eighth falling clock edge, control of the SDA line is released back to the master so that the master can acknowledge or not acknowledge the response. If the master sends a not acknowledge, the slave's transmission is complete and the slave must monitor for the next Start condition. If the master acknowledges, control of the bus is returned to the slave to transmit another byte of data. Just as with the previous byte, the clock is stretched by the slave, data must be loaded into the SSPBUF and CKP must be set to release the clock line (SCL).

#### FIGURE 17-12: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

# PIC16(L)F722/3/4/6/7

| RETFIE           | Return from Interrupt                                                                                                                                                                                                |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                       |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                 |  |  |  |  |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                              |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                 |  |  |  |  |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top-of-Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global<br>Interrupt Enable bit, GIE (INT-<br>CON<7>). This is a 2-cycle<br>instruction. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                    |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                    |  |  |  |  |

| Example:         | RETFIE                                                                                                                                                                                                               |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                               |  |  |  |  |

| RETLW            | Return with literal in W                                                                                                                                                                                                        |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                                                                        |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                                                             |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                                                                    |

| Status Affected: | None                                                                                                                                                                                                                            |

| Description:     | The W register is loaded with the<br>8-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a 2-cycle instruction.                                                   |

| Words:           | 1                                                                                                                                                                                                                               |

| Cycles:          | 2                                                                                                                                                                                                                               |

| Example:         | CALL TABLE;W contains table                                                                                                                                                                                                     |

| TABLE            | <pre>;offset value<br/>;W now has table value<br/>ADDWF PC ;W = offset<br/>RETLW k1 ;Begin table<br/>RETLW k2 ;<br/>RETLW kn ; End of table<br/>Before Instruction<br/>W = 0x07<br/>After Instruction<br/>W = value of k8</pre> |

| RETURN           | Return from Subroutine                                                                                                                                                                                                          |

| Syntax:          | [label] RETURN                                                                                                                                                                                                                  |

| Operands:        | None                                                                                                                                                                                                                            |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                            |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a 2-cycle instruc-<br>tion.                                                                      |

| Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |          |                                                              |               |          |          |       |                              |  |  |

|--------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------|---------------|----------|----------|-------|------------------------------|--|--|

| Param<br>No.                                                                                                             | Sym.     | Characteristic                                               | Min.          | Тур†     | Max.     | Units | Conditions                   |  |  |

| OS11                                                                                                                     | TosH2ckL | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                              | _             |          | 70       | ns    | VDD = 3.3-5.0V               |  |  |

| OS12                                                                                                                     | TosH2ckH | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                              | —             |          | 72       | ns    | VDD = 3.3-5.0V               |  |  |

| OS13                                                                                                                     | TckL2ioV | CLKOUT↓ to Port out valid <sup>(1)</sup>                     | —             | _        | 20       | ns    |                              |  |  |

| OS14                                                                                                                     | TioV2ckH | Port input valid before CLKOUT <sup>(1)</sup>                | Tosc + 200 ns |          | _        | ns    |                              |  |  |

| OS15                                                                                                                     | TosH2ioV | Fosc↑ (Q1 cycle) to Port out valid                           | —             | 50       | 70*      | ns    | VDD = 3.3-5.0V               |  |  |

| OS16                                                                                                                     | TosH2iol | Fosc↑ (Q2 cycle) to Port input invalid<br>(I/O in hold time) | 50            | —        | —        | ns    | VDD = 3.3-5.0V               |  |  |

| OS17                                                                                                                     | TioV2osH | Port input valid to Fosc↑ (Q2 cycle)<br>(I/O in setup time)  | 20            | —        | _        | ns    |                              |  |  |

| OS18                                                                                                                     | TioR     | Port output rise time <sup>(2)</sup>                         |               | 40<br>15 | 72<br>32 | ns    | VDD = 2.0V<br>VDD = 3.3-5.0V |  |  |

| OS19                                                                                                                     | TioF     | Port output fall time <sup>(2)</sup>                         |               | 28<br>15 | 55<br>30 | ns    | VDD = 2.0V<br>VDD = 3.3-5.0V |  |  |

| OS20*                                                                                                                    | Tinp     | INT pin input high or low time                               | 25            | —        | —        | ns    |                              |  |  |

| OS21*                                                                                                                    | Trbp     | PORTB interrupt-on-change new input level time               | Тсү           | —        | —        | ns    |                              |  |  |

#### TABLE 23-3: CLKOUT AND I/O TIMING PARAMETERS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

**Note 1:** Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

2: Includes OSC2 in CLKOUT mode.

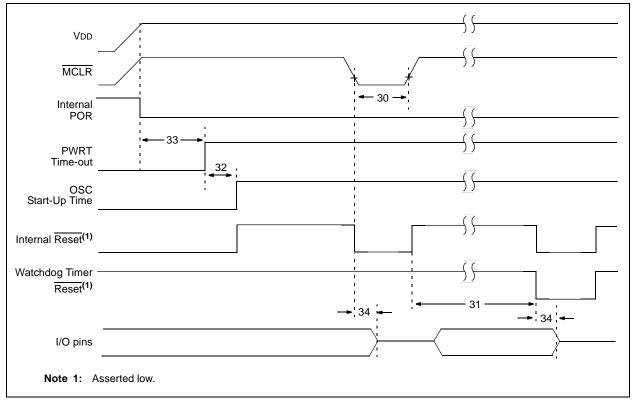

### FIGURE 23-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

| Param<br>No. | Symbol                | Characteristic                                                                 |          | Min.        | Тур† | Max. | Units | Conditions |

|--------------|-----------------------|--------------------------------------------------------------------------------|----------|-------------|------|------|-------|------------|

| SP70*        | TssL2scH,<br>TssL2scL | $\overline{\mathrm{SS}}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input |          | Тсү         |      | —    | ns    |            |

| SP71*        | TscH                  | SCK input high time (Slave mode)                                               |          | TCY + 20    |      | _    | ns    |            |

| SP72*        | TscL                  | SCK input low time (Slave mode)                                                |          | TCY + 20    |      | _    | ns    |            |

| SP73*        | TDIV2scH,<br>TDIV2scL | Setup time of SDI data input to SCK edge                                       |          | 100         |      | —    | ns    |            |

| SP74*        | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                                        |          | 100         |      | —    | ns    |            |

| SP75* TDOR   | TDOR                  | SDO data output rise time                                                      | 3.0-5.5V | —           | 10   | 25   | ns    |            |

|              |                       |                                                                                | 1.8-5.5V | —           | 25   | 50   | ns    |            |

| SP76*        | TDOF                  | SDO data output fall time                                                      |          | —           | 10   | 25   | ns    |            |

| SP77*        | TssH2doZ              | SS↑ to SDO output high-impedance                                               |          | 10          | _    | 50   | ns    |            |

| SP78* TscR   | TscR                  | SCK output rise time                                                           | 3.0-5.5V | —           | 10   | 25   | ns    |            |

|              |                       | (Master mode)                                                                  | 1.8-5.5V | _           | 25   | 50   | ns    |            |

| SP79*        | TscF                  | SCK output fall time (Master mode)                                             |          | _           | 10   | 25   | ns    |            |

| SP80*        | TscH2doV,             | SDO data output valid after SCK                                                | 3.0-5.5V | —           | _    | 50   | ns    |            |

|              | TscL2doV              | edge                                                                           | 1.8-5.5V | —           | _    | 145  | ns    |            |

| SP81*        | TDOV2SCH,<br>TDOV2SCL | SDO data output setup to SCK edge                                              |          | Тсу         | _    | —    | ns    |            |

| SP82*        | TssL2doV              | SDO data output valid after $\overline{SS}\downarrow$ edge                     |          | _           | _    | 50   | ns    |            |

| SP83*        | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                                            |          | 1.5Tcy + 40 | _    | -    | ns    |            |

#### TABLE 23-11: SPI MODE REQUIREMENTS

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

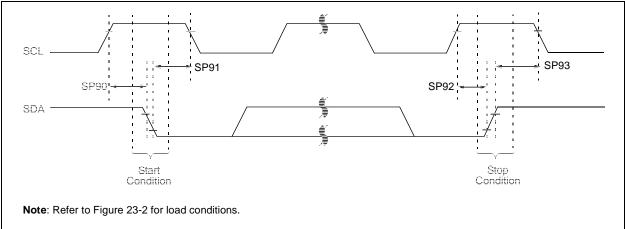

#### FIGURE 23-20: I<sup>2</sup>C BUS START/STOP BITS TIMING

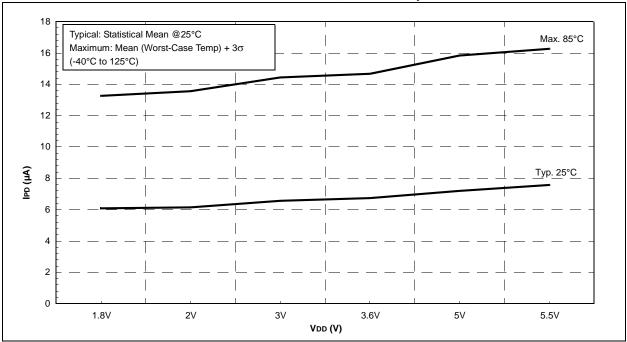

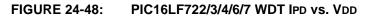

#### FIGURE 24-47: PIC16F722/3/4/6/7 WDT IPD vs. VDD, VCAP = 0.1 µF

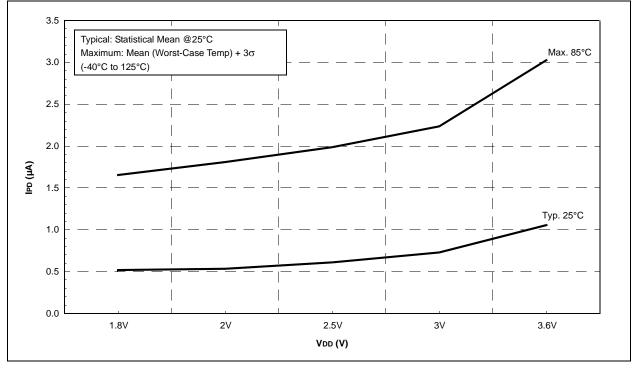

#### 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Κ

0.20

\_

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

Contact-to-Exposed Pad

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103B

\_