Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 14x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 40-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 40-UQFN (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f727t-i-mv |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

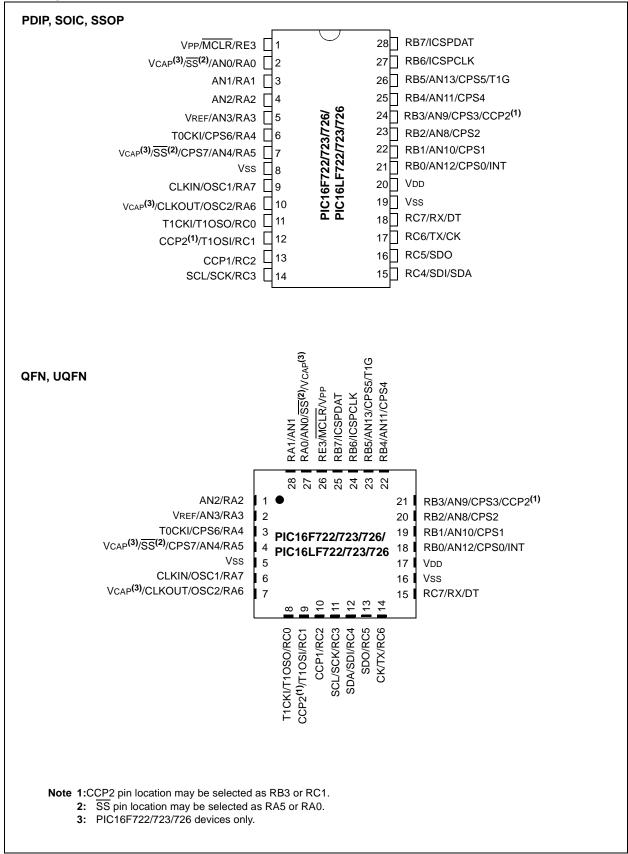

## Pin Diagrams - 28-PIN PDIP/SOIC/SSOP/QFN/UQFN (PIC16F722/723/726/PIC16LF722/723/726)

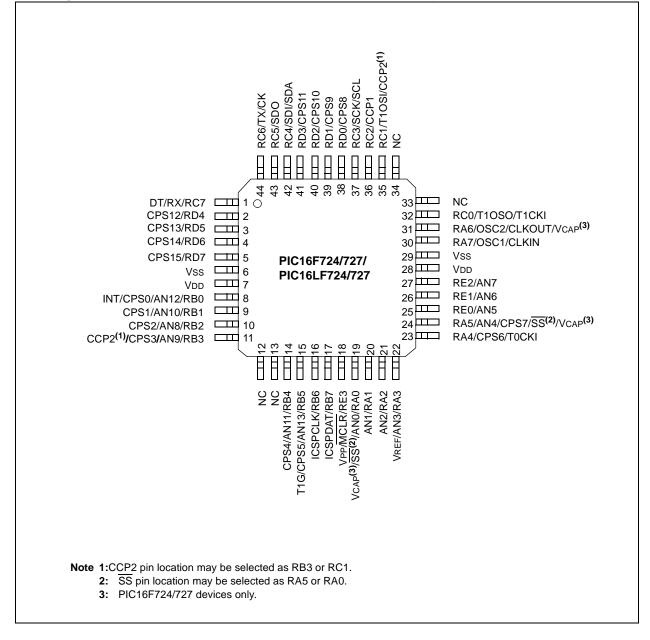

## Pin Diagrams – 44-PIN TQFP (PIC16F724/727/PIC16LF724/727)

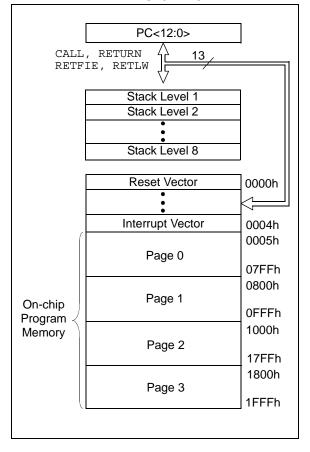

## FIGURE 2-3:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16F726/LF726 AND PIC16F727/LF727

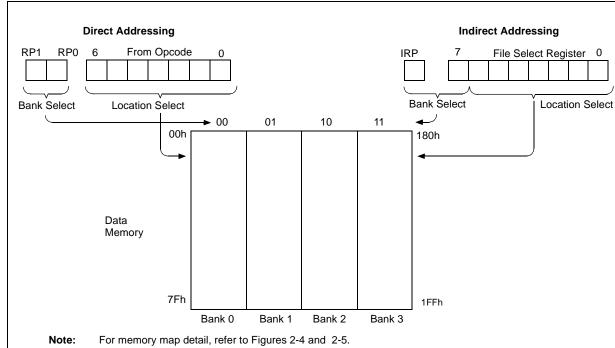

## 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers (GPRs) and the Special Function Registers (SFRs). Bits RP0 and RP1 are bank select bits.

| <u>RP1</u> | <u>RP0</u> |

|------------|------------|

|            |            |

| 0 | 0 | $\rightarrow$ | Bank 0 is selected |

|---|---|---------------|--------------------|

| 0 | 1 | $\rightarrow$ | Bank 1 is selected |

| 1 | 0 | $\rightarrow$ | Bank 2 is selected |

| 1 | 1 | $\rightarrow$ | Bank 3 is selected |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are the General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank are mirrored in another bank for code reduction and quicker access.

### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 128 x 8 bits in the PIC16F722/LF722, 192 x 8 bits in the PIC16F723/LF723 and PIC16F724/LF724, and 368 x 8 bits in the PIC16F726/LF726 and PIC16F727/LF727. Each register is accessed either directly or indirectly through the File Select Register (FSR), (Refer to **Section 2.5** "Indirect Addressing, INDF and FSR Registers").

## 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (refer to Table 2-1). These registers are static RAM.

The Special Function Registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the "core" are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

### 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains:

- the arithmetic status of the ALU

- · the Reset status

- the bank select bits for data memory (SRAM)

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to **Section 21.0** "Instruction Set Summary").

**Note 1:** The <u>C</u> and <u>DC</u> bits operate as Borrow and <u>Digit</u> Borrow out bits, respectively, in subtraction.

REGISTER 2-1: STATUS: STATUS REGISTER

| R/W-0 | R/W-0 | R/W-0 | R-1 | R-1 | R/W-x | R/W-x             | R/W-x            |

|-------|-------|-------|-----|-----|-------|-------------------|------------------|

| IRP   | RP1   | RP0   | TO  | PD  | Z     | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7 |       |       |     |     |       |                   | bit 0            |

| Legend:          |                                                                                             |                                                                                                                        |                                                                    |                                  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------|--|--|--|

| R = Readable bit |                                                                                             | W = Writable bit                                                                                                       | U = Unimplemented bit,                                             | read as '0'                      |  |  |  |

| -n = Value a     | at POR                                                                                      | '1' = Bit is set                                                                                                       | '0' = Bit is cleared                                               | x = Bit is unknown               |  |  |  |

|                  |                                                                                             |                                                                                                                        |                                                                    |                                  |  |  |  |

| bit 7            | •                                                                                           | ster Bank Select bit (used for                                                                                         | or indirect addressing)                                            |                                  |  |  |  |

|                  |                                                                                             | 2, 3 (100h-1FFh)<br>0, 1 (00h-FFh)                                                                                     |                                                                    |                                  |  |  |  |

| bit 6-5          |                                                                                             | Register Bank Select bits (                                                                                            | used for direct addressing)                                        |                                  |  |  |  |

|                  |                                                                                             | < 0 (00h-7Fh)                                                                                                          |                                                                    |                                  |  |  |  |

|                  |                                                                                             | < 1 (80h-FFh)                                                                                                          |                                                                    |                                  |  |  |  |

|                  |                                                                                             | k 2 (100h-17Fh)                                                                                                        |                                                                    |                                  |  |  |  |

|                  |                                                                                             | < 3 (180h-1FFh)                                                                                                        |                                                                    |                                  |  |  |  |

|                  |                                                                                             | -out bit                                                                                                               |                                                                    |                                  |  |  |  |

|                  |                                                                                             | 1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time out occurred                             |                                                                    |                                  |  |  |  |

|                  |                                                                                             | er-down bit                                                                                                            |                                                                    |                                  |  |  |  |

|                  |                                                                                             |                                                                                                                        | instruction                                                        |                                  |  |  |  |

|                  |                                                                                             | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul> |                                                                    |                                  |  |  |  |

| bit 2            | Z: Zero bi                                                                                  |                                                                                                                        |                                                                    |                                  |  |  |  |

|                  | 1 = The re                                                                                  | esult of an arithmetic or logi                                                                                         | c operation is zero                                                |                                  |  |  |  |

|                  |                                                                                             | esult of an arithmetic or logi                                                                                         | •                                                                  |                                  |  |  |  |

| bit 1            | DC: Digit                                                                                   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                              |                                                                    |                                  |  |  |  |

|                  |                                                                                             | ry out from the 4th low-orde                                                                                           |                                                                    |                                  |  |  |  |

|                  |                                                                                             | rry-out from the 4th low-ord                                                                                           |                                                                    | . (4)                            |  |  |  |

| bit 0            | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup> |                                                                                                                        |                                                                    |                                  |  |  |  |

|                  |                                                                                             |                                                                                                                        | ant bit of the result occurred<br>icant bit of the result occurred |                                  |  |  |  |

|                  | 0 = 100  Ca                                                                                 |                                                                                                                        |                                                                    |                                  |  |  |  |

|                  |                                                                                             |                                                                                                                        | traction is executed by adding                                     |                                  |  |  |  |

| ę                | second operan                                                                               | d. For rotate (RRF, RLF) inst                                                                                          | ructions, this bit is loaded with                                  | either the high-order or low-ord |  |  |  |

bit of the source register.

## 2.2.2.3 PCON Register

The Power Control (PCON) register contains flag bits (refer to Table 3-2) to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the software enable of the BOR.

The PCON register bits are shown in Register 2-3.

## REGISTER 2-3: PCON: POWER CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-q | R/W-q |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | _   | _   | _   | _   | _   | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:                 |                  |                        |                    |

|-------------------------|------------------|------------------------|--------------------|

| R = Readable bit        | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR       | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| q = Value depends on co | ondition         |                        |                    |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                        |

|---------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | POR: Power-on Reset Status bit                                                                                                    |

|         | 1 = No Power-on Reset occurred                                                                                                    |

|         | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                                             |

| bit 0   | BOR: Brown-out Reset Status bit                                                                                                   |

|         | 1 = No Brown-out Reset occurred                                                                                                   |

|         | <ul> <li>0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset<br/>occurs)</li> </ul> |

|         |                                                                                                                                   |

**Note 1:** Set BOREN<1:0> = 01 in the Configuration Word register for this bit to control the  $\overline{\text{BOR}}$ .

## 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit of the STATUS register, as shown in Figure 2-8.

A simple program to clear RAM location 020h-02Fh using indirect addressing is shown in Example 2-2.

### EXAMPLE 2-2: INDIRECT ADDRESSING

|      | MOVLW<br>MOVWF<br>BANKISEL | 020h<br>FSR<br>020h | ;initialize pointer<br>;to RAM       |

|------|----------------------------|---------------------|--------------------------------------|

| NEXT | CLRF<br>INCF               | INDF<br>FSR         | ;clear INDF register<br>;inc pointer |

|      | BTFSS                      | FSR,4               | ;all done?                           |

|      | GOTO                       | NEXT                | ;no clear next                       |

| CONT | INUE                       |                     | ;yes continue                        |

|      |                            |                     |                                      |

## FIGURE 2-8: DIRECT/INDIRECT ADDRESSING

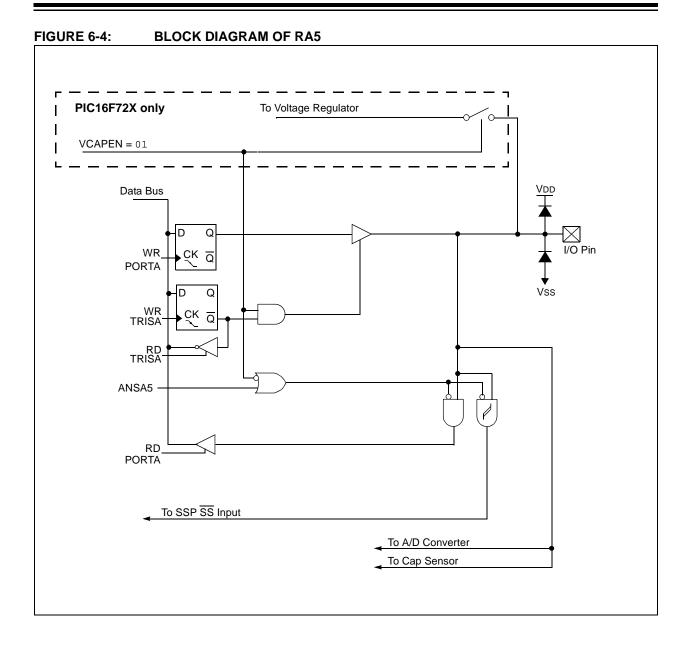

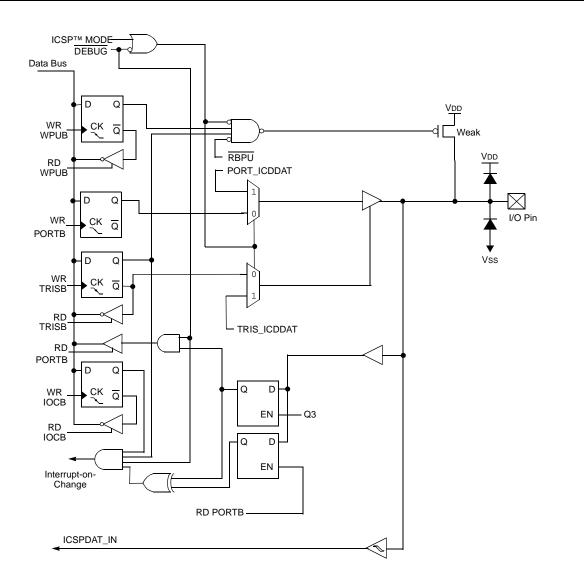

## FIGURE 6-12: BLOCK DIAGRAM OF RB7

## 9.2.7 ADC REGISTER DEFINITIONS

The following registers are used to control the operation of the ADC.

#### REGISTER 9-1: ADCON0: A/D CONTROL REGISTER 0

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 |

|-------|-----|-------|-------|-------|-------|---------|-------|

| —     | —   | CHS3  | CHS2  | CHS1  | CHS0  | GO/DONE | ADON  |

| bit 7 |     |       |       |       |       |         | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-2 CHS<3:0>: Analog Channel Select bits

|       | 0000 = ANO                                                                                                                                                                                               |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 0001 = AN1                                                                                                                                                                                               |

|       | 0010 = AN2                                                                                                                                                                                               |

|       | 0011 = AN3                                                                                                                                                                                               |

|       | 0100 = AN4                                                                                                                                                                                               |

|       | 0101 = AN5                                                                                                                                                                                               |

|       | 0110 = AN6                                                                                                                                                                                               |

|       | 0111 = AN7                                                                                                                                                                                               |

|       | 1000 = AN8                                                                                                                                                                                               |

|       | 1001 = AN9                                                                                                                                                                                               |

|       | 1010 = AN10                                                                                                                                                                                              |

|       | 1011 = AN11                                                                                                                                                                                              |

|       | 1100 = AN12                                                                                                                                                                                              |

|       | 1101 = AN13                                                                                                                                                                                              |

|       | 1110 = Reserved                                                                                                                                                                                          |

|       | 1111 = Fixed Voltage Reference (FVREF)                                                                                                                                                                   |

| bit 1 | GO/DONE: A/D Conversion Status bit                                                                                                                                                                       |

|       | <ul> <li>1 = A/D conversion cycle in progress. Setting this bit starts an A/D conversion cycle.</li> <li>This bit is automatically cleared by hardware when the A/D conversion has completed.</li> </ul> |

|       | 0 = A/D conversion completed/not in progress                                                                                                                                                             |

| bit 0 | ADON: ADC Enable bit                                                                                                                                                                                     |

|       | 1 = ADC is enabled                                                                                                                                                                                       |

0 = ADC is disabled and consumes no operating current

| R/W-0         | R/W-0                                                                                                                                               | R/W-0            | R/W-0          | R/W-0            | R-0              | R-0               | R-x          |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|------------------|------------------|-------------------|--------------|--|--|--|

| SPEN          | RX9                                                                                                                                                 | SREN             | CREN           | ADDEN            | FERR             | OERR              | RX9D         |  |  |  |

| bit 7         |                                                                                                                                                     |                  |                |                  |                  |                   | bit (        |  |  |  |

|               |                                                                                                                                                     |                  |                |                  |                  |                   |              |  |  |  |

| Legend:       |                                                                                                                                                     |                  |                |                  |                  |                   |              |  |  |  |

| R = Readable  |                                                                                                                                                     | W = Writable     |                | -                | mented bit, read | as '0'            |              |  |  |  |

| -n = Value at | POR                                                                                                                                                 | '1' = Bit is set |                | '0' = Bit is cle | ared             | x = Bit is unkn   | own          |  |  |  |

| L :4 7        |                                                                                                                                                     | Deut Frieklach   | .(1)           |                  |                  |                   |              |  |  |  |

| bit 7         | <b>SPEN:</b> Serial Port Enable bit <sup>(1)</sup>                                                                                                  |                  |                |                  |                  |                   |              |  |  |  |

|               | <ul> <li>1 = Serial port enabled (configures RX/DT and TX/CK pins as serial port pins)</li> <li>0 = Serial port disabled (held in Reset)</li> </ul> |                  |                |                  |                  |                   |              |  |  |  |

| bit 6         | <b>RX9:</b> 9-bit Re                                                                                                                                | ceive Enable b   | bit            |                  |                  |                   |              |  |  |  |

|               | 1 = Selects 9-bit reception                                                                                                                         |                  |                |                  |                  |                   |              |  |  |  |

| bit 5         | <ul> <li>0 = Selects 8-bit reception</li> <li>SREN: Single Receive Enable bit</li> </ul>                                                            |                  |                |                  |                  |                   |              |  |  |  |

|               | Asynchronous mode:                                                                                                                                  |                  |                |                  |                  |                   |              |  |  |  |

|               | Don't care                                                                                                                                          |                  |                |                  |                  |                   |              |  |  |  |

|               | Synchronous mode – Master:                                                                                                                          |                  |                |                  |                  |                   |              |  |  |  |

|               | 1 = Enables single receive                                                                                                                          |                  |                |                  |                  |                   |              |  |  |  |

|               | <ul> <li>0 = Disables single receive</li> <li>This bit is cleared after reception is complete.</li> </ul>                                           |                  |                |                  |                  |                   |              |  |  |  |

|               | Synchronous mode – Slave:                                                                                                                           |                  |                |                  |                  |                   |              |  |  |  |

|               | Don't care                                                                                                                                          |                  |                |                  |                  |                   |              |  |  |  |

| bit 4         | CREN: Continuous Receive Enable bit                                                                                                                 |                  |                |                  |                  |                   |              |  |  |  |

|               | Asynchronous mode:                                                                                                                                  |                  |                |                  |                  |                   |              |  |  |  |

|               | 1 = Enables receiver                                                                                                                                |                  |                |                  |                  |                   |              |  |  |  |

|               | 0 = Disables receiver<br>Synchronous mode:                                                                                                          |                  |                |                  |                  |                   |              |  |  |  |

|               | <u>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)</u>                                                        |                  |                |                  |                  |                   |              |  |  |  |

|               |                                                                                                                                                     | continuous rea   |                |                  |                  |                   |              |  |  |  |

| bit 3         | ADDEN: Address Detect Enable bit                                                                                                                    |                  |                |                  |                  |                   |              |  |  |  |

|               | Asynchronous mode 9-bit (RX9 = $1$ ):                                                                                                               |                  |                |                  |                  |                   |              |  |  |  |

|               | 1 = Enables address detection, enable interrupt and load the receive buffer when RSR<8> is set                                                      |                  |                |                  |                  |                   |              |  |  |  |

|               | 0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit<br><u>Asynchronous mode 8-bit (RX9 = 0)</u> :        |                  |                |                  |                  |                   |              |  |  |  |

|               | Don't care                                                                                                                                          |                  |                |                  |                  |                   |              |  |  |  |

|               | Synchronous                                                                                                                                         | mode:            |                |                  |                  |                   |              |  |  |  |

|               | Must be set to                                                                                                                                      | <b>o</b> '0'     |                |                  |                  |                   |              |  |  |  |

| bit 2         | FERR: Frami                                                                                                                                         | -                |                |                  |                  |                   |              |  |  |  |

|               | 1 = Framing<br>0 = No framir                                                                                                                        |                  | pdated by rea  | ading RCREG I    | egister and rec  | eive next valid l | oyte)        |  |  |  |

| bit 1         | OERR: Overr                                                                                                                                         | un Error bit     |                |                  |                  |                   |              |  |  |  |

|               | 1 = Overrun<br>0 = No overru                                                                                                                        | •                | leared by clea | aring bit CREN   | )                |                   |              |  |  |  |

| bit 0         |                                                                                                                                                     | bit of Received  | Data           |                  |                  |                   |              |  |  |  |

|               | This can be address/data bit or a parity bit and must be calculated by user firmware.                                                               |                  |                |                  |                  |                   |              |  |  |  |

|               | he AUSART m<br>RISx = 1.                                                                                                                            | odule automa     | tically change | es the pin fro   | m tri-state to o | drive as neede    | ed. Configur |  |  |  |

## REGISTER 16-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

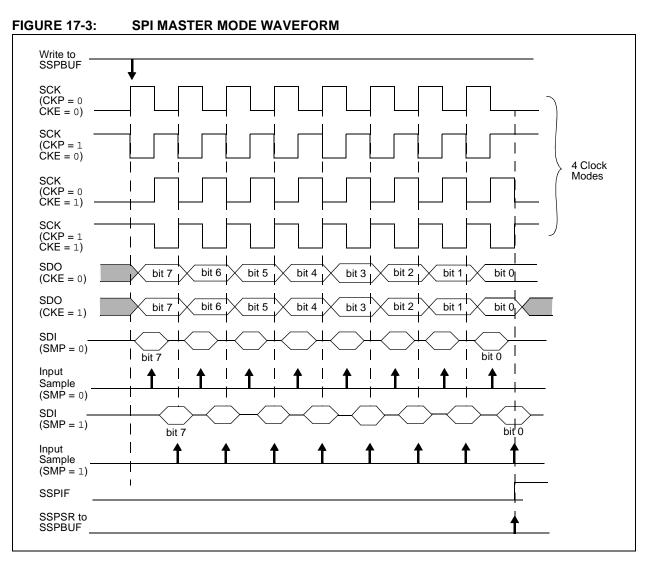

### EXAMPLE 17-1: LOADING THE SSPBUF (SSPSR) REGISTER

|      | BANKSEL | SSPSTAT     | ;                                           |

|------|---------|-------------|---------------------------------------------|

| LOOP | BTFSS   | SSPSTAT, BF | ;Has data been received(transmit complete)? |

|      | GOTO    | LOOP        | ; No                                        |

|      | BANKSEL | SSPBUF      | ;                                           |

|      | MOVF    | SSPBUF, W   | ;WREG reg = contents of SSPBUF              |

|      | MOVWF   | RXDATA      | ;Save in user RAM, if data is meaningful    |

|      | MOVF    | TXDATA, W   | ;W reg = contents of TXDATA                 |

|      | MOVWF   | SSPBUF      | ;New data to xmit                           |

|      |         |             |                                             |

# 22.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 22.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

- File History and Bug Tracking:

- Local file history feature

- Built-in support for Bugzilla issue tracker

| Param.<br>No. | Symbol                | Characteristic               |              | Min.       | Max. | Units                                | Conditions                                  |

|---------------|-----------------------|------------------------------|--------------|------------|------|--------------------------------------|---------------------------------------------|

| SP100*        | Тнідн                 | Clock high time              | 100 kHz mode | 4.0        | —    | μs                                   | Device must operate at a minimum of 1.5 MHz |

|               |                       |                              | 400 kHz mode | 0.6        | _    | μs                                   | Device must operate at a minimum of 10 MHz  |

|               |                       |                              | SSP Module   | 1.5Tcy     | _    |                                      |                                             |

| SP101* TLOW   |                       | Clock low time               | 100 kHz mode | 4.7        | _    | μs                                   | Device must operate at a minimum of 1.5 MHz |

|               |                       |                              | 400 kHz mode | 1.3        | _    | μS                                   | Device must operate at a minimum of 10 MHz  |

|               |                       |                              | SSP Module   | 1.5Tcy     | _    |                                      |                                             |

| SP102* TR     | SDA and SCL rise time | 100 kHz mode                 | —            | 1000       | ns   |                                      |                                             |

|               |                       | 400 kHz mode                 | 20 + 0.1CB   | 300        | ns   | CB is specified to be from 10-400 pF |                                             |

| SP103*        | TF                    | SDA and SCL fall time        | 100 kHz mode | —          | 250  | ns                                   |                                             |

|               |                       |                              | 400 kHz mode | 20 + 0.1CB | 250  | ns                                   | CB is specified to be from 10-400 pF        |

| SP106*        | THD:DAT               | Data input hold time         | 100 kHz mode | 0          |      | ns                                   |                                             |

|               |                       |                              | 400 kHz mode | 0          | 0.9  | μs                                   | -                                           |

| SP107*        | TSU:DAT               | Data input setup time        | 100 kHz mode | 250        |      | ns                                   | (Note 2)                                    |

|               |                       |                              | 400 kHz mode | 100        |      | ns                                   | -                                           |

| SP109*        | ΤΑΑ                   | A Output valid from<br>clock | 100 kHz mode | —          | 3500 | ns                                   | (Note 1)                                    |

|               |                       |                              | 400 kHz mode | _          |      | ns                                   |                                             |

| SP110*        | TBUF                  | Bus free time                | 100 kHz mode | 4.7        | _    | μs                                   | Time the bus must be free                   |

|               |                       |                              | 400 kHz mode | 1.3        | —    | μs                                   | before a new transmission can start         |

| SP111         | Св                    | Bus capacitive loading       | —            | 400        | pF   |                                      |                                             |

# TABLE 23-13: I<sup>2</sup>C BUS DATA REQUIREMENTS

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement TsU:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

#### © 2007-2015 Microchip Technology Inc.

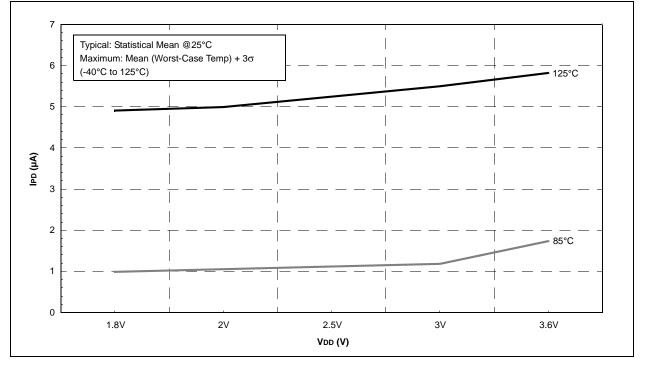

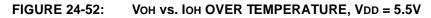

FIGURE 24-51: SCHMITT TRIGGER INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

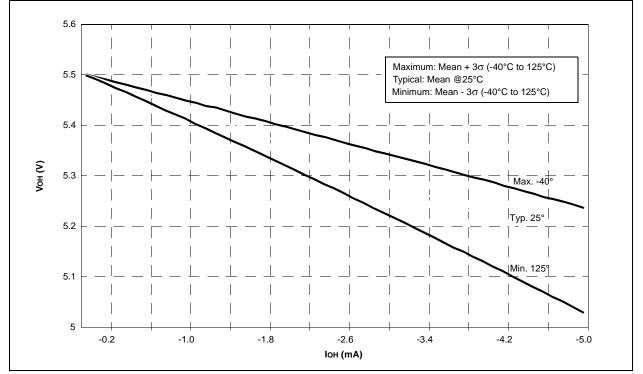

## 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Κ

0.20

\_

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

Contact-to-Exposed Pad

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103B

\_

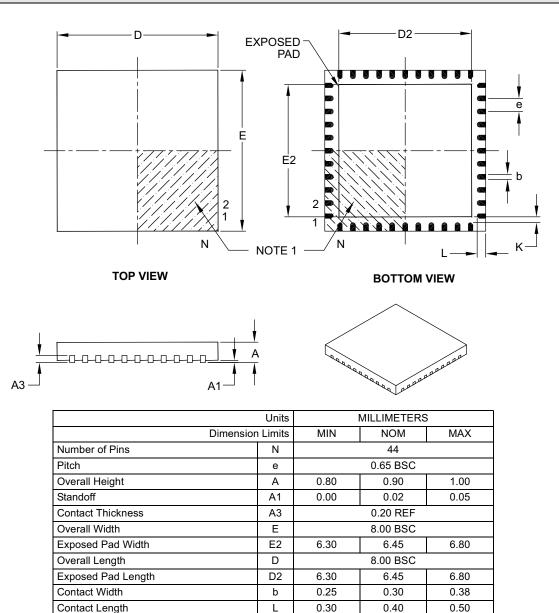

## 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |          |      |      |  |

|----------------------------|-------------|----------|------|------|--|

| Dimensior                  | MIN         | NOM      | MAX  |      |  |

| Contact Pitch E            |             | 0.65 BSC |      |      |  |

| Optional Center Pad Width  | W2          |          |      | 6.80 |  |

| Optional Center Pad Length | T2          |          |      | 6.80 |  |

| Contact Pad Spacing        | C1          |          | 8.00 |      |  |

| Contact Pad Spacing        | C2          |          | 8.00 |      |  |

| Contact Pad Width (X44)    | X1          |          |      | 0.35 |  |

| Contact Pad Length (X44)   | Y1          |          |      | 0.80 |  |

| Distance Between Pads      | G           | 0.25     |      |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103A

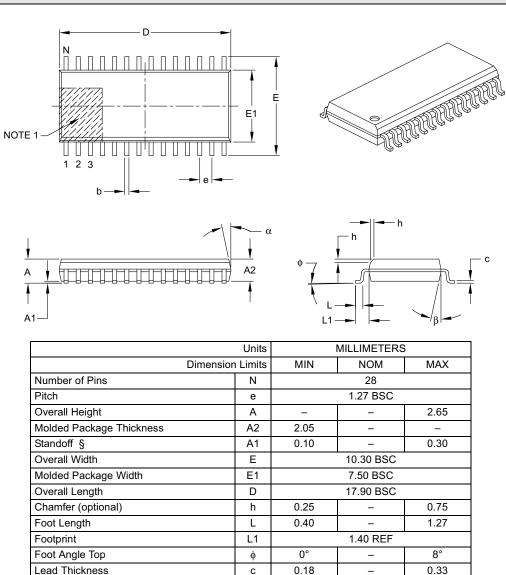

## 28-Lead Plastic Small Outline (SO) – Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

b

α

β

0.31

5°

5°

\_

\_

\_

4. Dimensioning and tolerancing per ASME Y14.5M.

Lead Width

Mold Draft Angle Top

Mold Draft Angle Bottom

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-052B

0.51

15°

15°

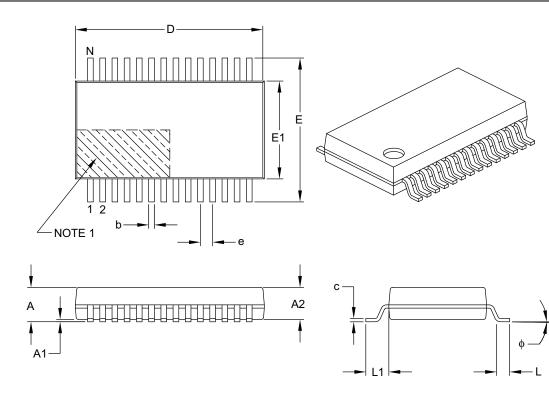

## 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |          | MILLIMETERS | 6     |  |

|--------------------------|----------|----------|-------------|-------|--|

| Dimensio                 | n Limits | MIN      | NOM         | MAX   |  |

| Number of Pins           | Ν        |          | 28          |       |  |

| Pitch                    | е        |          | 0.65 BSC    |       |  |

| Overall Height           | Α        | -        | -           | 2.00  |  |

| Molded Package Thickness | A2       | 1.65     | 1.75        | 1.85  |  |

| Standoff                 | A1       | 0.05     | -           | -     |  |

| Overall Width            | E        | 7.40     | 7.80        | 8.20  |  |

| Molded Package Width     | E1       | 5.00     | 5.30        | 5.60  |  |

| Overall Length           | D        | 9.90     | 10.20       | 10.50 |  |

| Foot Length              | L        | 0.55     | 0.75        | 0.95  |  |

| Footprint L1             |          | 1.25 REF |             |       |  |

| Lead Thickness           | с        | 0.09     | -           | 0.25  |  |

| Foot Angle               | φ        | 0°       | 4°          | 8°    |  |

| Lead Width               | b        | 0.22     | -           | 0.38  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

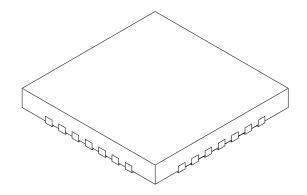

## 28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units | N         | ILLIMETER | S    |  |

|------------------------|-------|-----------|-----------|------|--|

| Dimensio               | MIN   | NOM       | MAX       |      |  |

| Number of Pins         | Ν     | 28        |           |      |  |

| Pitch                  | е     |           | 0.40 BSC  |      |  |

| Overall Height         | Α     | 0.45      | 0.50      | 0.55 |  |

| Standoff               | A1    | 0.00      | 0.02      | 0.05 |  |

| Contact Thickness      | A3    | 0.127 REF |           |      |  |

| Overall Width          | E     | 4.00 BSC  |           |      |  |

| Exposed Pad Width      | E2    | 2.55      | 2.65      | 2.75 |  |

| Overall Length         | D     | 4.00 BSC  |           |      |  |

| Exposed Pad Length     | D2    | 2.55      | 2.65      | 2.75 |  |

| Contact Width          | b     | 0.15      | 0.20      | 0.25 |  |

| Contact Length         | L     | 0.30      | 0.40      | 0.50 |  |

| Contact-to-Exposed Pad | K     | 0.20      | -         | -    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-152A Sheet 2 of 2