Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 11x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf722-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

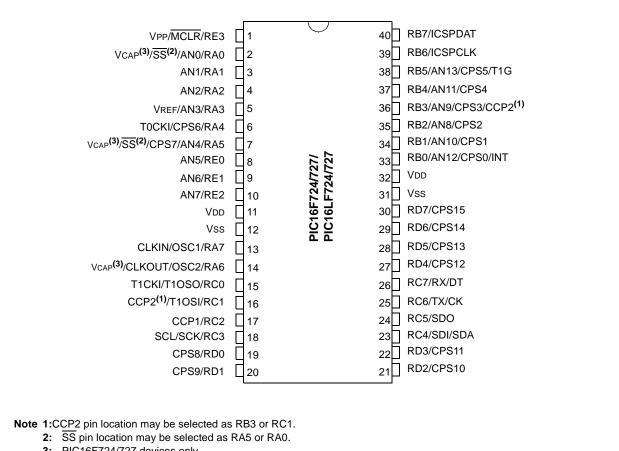

### Pin Diagrams - 40-PIN PDIP (PIC16F724/727/PIC16LF724/727)

3: PIC16F724/727 devices only.

| Name                                                                      | Function | Input<br>Type | Output<br>Type | Description                                                                                              |  |  |

|---------------------------------------------------------------------------|----------|---------------|----------------|----------------------------------------------------------------------------------------------------------|--|--|

| RD3/CPS11                                                                 | RD3      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | CPS11    | AN            | —              | Capacitive sensing input 11.                                                                             |  |  |

| RD4/CPS12                                                                 | RD4      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | CPS12    | AN            | —              | Capacitive sensing input 12.                                                                             |  |  |

| RD5/CPS13                                                                 | RD5      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | CPS13    | AN            | —              | Capacitive sensing input 13.                                                                             |  |  |

| RD6/CPS14                                                                 | RD6      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | CPS14    | AN            | _              | Capacitive sensing input 14.                                                                             |  |  |

| RD7/CPS15                                                                 | RD7      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | CPS15    | AN            | _              | Capacitive sensing input 15.                                                                             |  |  |

| RE0/AN5                                                                   | RE0      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | AN5      | AN            | —              | A/D Channel 5 input.                                                                                     |  |  |

| RE1/AN6                                                                   | RE1      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | AN6      | AN            | —              | A/D Channel 6 input.                                                                                     |  |  |

| RE2/AN7                                                                   | RE2      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | AN7      | AN            | _              | A/D Channel 7 input.                                                                                     |  |  |

| RE3/MCLR/Vpp                                                              | RE3      | TTL           | —              | General purpose input.                                                                                   |  |  |

|                                                                           | MCLR     | ST            | _              | Master Clear with internal pull-up.                                                                      |  |  |

|                                                                           | Vpp      | ΗV            | —              | Programming voltage.                                                                                     |  |  |

| VDD                                                                       | Vdd      | Power         | —              | - Positive supply.                                                                                       |  |  |

| Vss                                                                       | Vss      | Power         | _              | Ground reference.                                                                                        |  |  |

| Legend: AN = Analog input or<br>TTL = TTL compatible<br>HV = High Voltage | input ST |               | nitt Trigger   | ble input or output OD = Open Drain<br>input with CMOS levels $I^2C$ = Schmitt Trigger input with $I^2C$ |  |  |

### TABLE 1-1: PIC16(L)F722/3/4/6/7 PINOUT DESCRIPTION (CONTINUED)

**Note:** The PIC16F722/3/4/6/7 devices have an internal low dropout voltage regulator. An external capacitor must be connected to one of the available VCAP pins to stabilize the regulator. For more information, see **Section 5.0 "Low Dropout (LDO) Voltage Regulator**". The PIC16LF722/3/4/6/7 devices do not have the voltage regulator and therefore no external capacitor is required.

# 2.0 MEMORY ORGANIZATION

## 2.1 Program Memory Organization

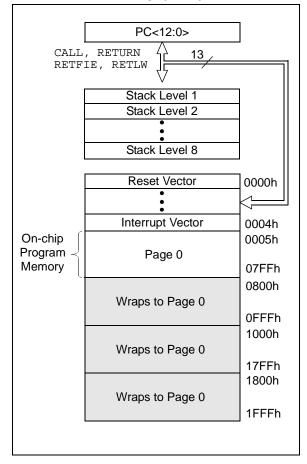

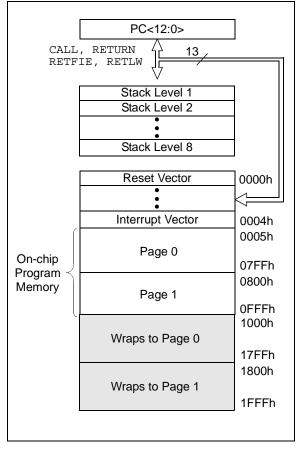

The PIC16(L)F722/3/4/6/7 has a 13-bit program counter capable of addressing a 2K x 14 program memory space for the PIC16F722/LF722 (0000h-07FFh), a 4K x 14 program memory space for PIC16F723/LF723 and PIC16F724/LF724 the (0000h-0FFFh) and an 8K x 14 program memory space for the PIC16F726/LF726 and PIC16F727/LF727 (0000h-1FFFh). Accessing a location above the memory boundaries for the PIC16F722/LF722 will cause a wrap-around within the first 2K x 14 program memory space. Accessing a location above the memory boundaries for the PIC16F723/LF723 and PIC16F724/LF724 will cause a wrap-around within the first 4K x 14 program memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h.

### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16F722/LF722

### FIGURE 2-2:

### PROGRAM MEMORY MAP AND STACK FOR THE PIC16F723/LF723 AND PIC16F724/LF724

### 2.2.2.3 PCON Register

The Power Control (PCON) register contains flag bits (refer to Table 3-2) to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the software enable of the BOR.

The PCON register bits are shown in Register 2-3.

### REGISTER 2-3: PCON: POWER CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-q | R/W-q |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | _   | _   | _   | _   | _   | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:                                                              |                                    |  |                    |  |  |  |  |  |

|----------------------------------------------------------------------|------------------------------------|--|--------------------|--|--|--|--|--|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                    |  |                    |  |  |  |  |  |

| -n = Value at POR                                                    | -n = Value at POR '1' = Bit is set |  | x = Bit is unknown |  |  |  |  |  |

| q = Value depends on condition                                       |                                    |  |                    |  |  |  |  |  |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                        |

|---------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | POR: Power-on Reset Status bit                                                                                                    |

|         | 1 = No Power-on Reset occurred                                                                                                    |

|         | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                                             |

| bit 0   | BOR: Brown-out Reset Status bit                                                                                                   |

|         | 1 = No Brown-out Reset occurred                                                                                                   |

|         | <ul> <li>0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset<br/>occurs)</li> </ul> |

|         |                                                                                                                                   |

**Note 1:** Set BOREN<1:0> = 01 in the Configuration Word register for this bit to control the  $\overline{\text{BOR}}$ .

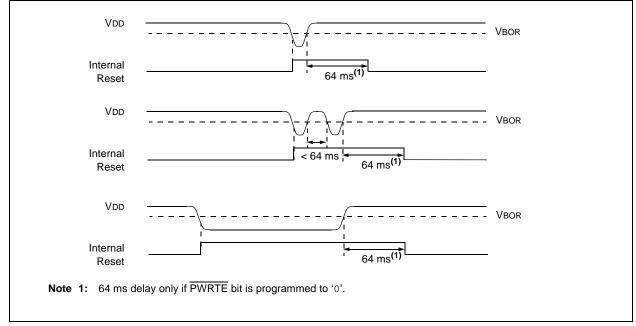

### 3.5 Brown-Out Reset (BOR)

Brown-out Reset is enabled by programming the BOREN<1:0> bits in the Configuration register. The brown-out trip point is selectable from two trip points via the BORV bit in the Configuration register.

Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

Two bits are used to enable the BOR. When BOREN = 11, the BOR is always enabled. When BOREN = 10, the BOR is enabled, but disabled during Sleep. When BOREN = 0X, the BOR is disabled.

If VDD falls below VBOR for greater than parameter (TBOR) (see **Section 23.0** "**Electrical Specifica-tions**"), the brown-out situation will reset the device. This will occur regardless of VDD slew rate. A Reset is not ensured to occur if VDD falls below VBOR for more than TBOR.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

**Note:** When erasing Flash program memory, the BOR is forced to enabled at the minimum BOR setting to ensure that any code protection circuitry is operating properly.

### FIGURE 3-3: BROWN-OUT SITUATIONS

### 4.5.3 PIE2 REGISTER

Γ.

bit 0

The PIE2 register contains the interrupt enable bits, as shown in Register 4-3.

# Note: Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

### REGISTER 4-3: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

| —     | —   | —   | —   | —   | —   |     | CCP2IE |

| bit 7 |     |     |     |     |     |     | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 7-1 Unimplemented: Read as '0'

CCP2IE: CCP2 Interrupt Enable bit

1 = Enables the CCP2 interrupt

0 = Disables the CCP2 interrupt

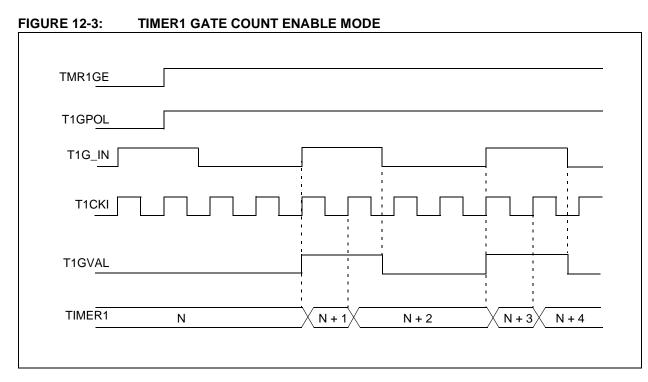

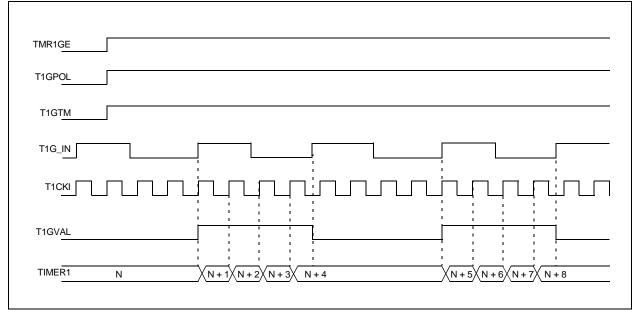

## FIGURE 12-4: TIMER1 GATE TOGGLE MODE

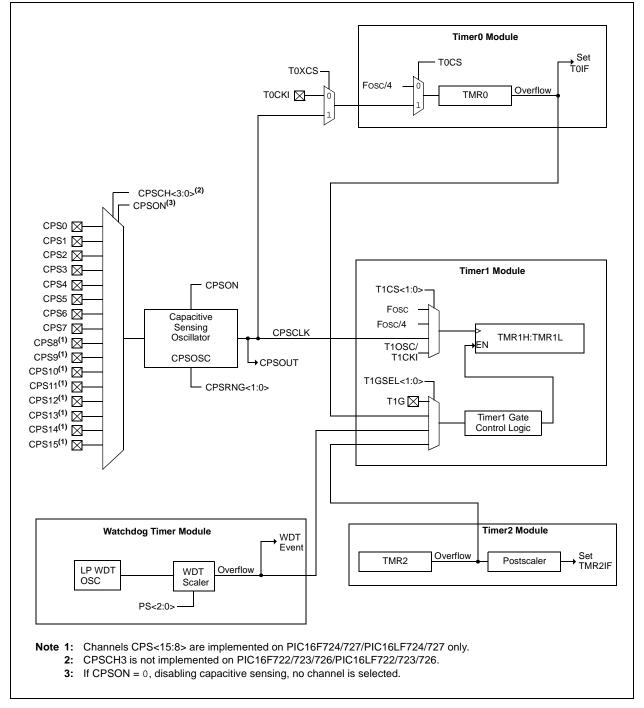

# 14.0 CAPACITIVE SENSING MODULE

The capacitive sensing module allows for an interaction with an end user without a mechanical interface. In a typical application, the capacitive sensing module is attached to a pad on a printed circuit board (PCB), which is electrically isolated from the end user. When the end user places their finger over the PCB pad, a capacitive load is added, causing a frequency shift in the capacitive sensing module. The capacitive sensing module requires software and at least one timer resource to determine the change in frequency. Key features of this module include:

- · Analog MUX for monitoring multiple inputs

- · Capacitive sensing oscillator

- Multiple timer resources

- Software control

- · Operation during Sleep

### FIGURE 14-1: CAPACITIVE SENSING BLOCK DIAGRAM

| Name    | Bit 7                  | Bit 6       | Bit 5         | Bit 4     | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|------------------------|-------------|---------------|-----------|---------|--------|---------|---------|----------------------|---------------------------------|

| ANSELB  | —                      | —           | ANSB5         | ANSB4     | ANSB3   | ANSB2  | ANSB1   | ANSB0   | 11 1111              | 11 1111                         |

| APFCON  | _                      | _           | _             | _         | _       | _      | SSSEL   | CCP2SEL | 00                   | 00                              |

| CCP1CON | _                      | _           | DC1B1         | DC1B0     | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00 0000              | 00 0000                         |

| CCP2CON | _                      | _           | DC2B1         | DC2B0     | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00 0000              | 00 0000                         |

| CCPRxL  | Capture/Con            |             | xxxx xxxx     | uuuu uuuu |         |        |         |         |                      |                                 |

| CCPRxH  | Capture/Con            | npare/PWM R | egister X Hig | h Byte    |         |        |         |         | xxxx xxxx            | uuuu uuuu                       |

| PR2     | Timer2 Perio           | d Register  |               |           |         |        |         |         | 1111 1111            | 1111 1111                       |

| T2CON   | _                      | TOUTPS3     | TOUTPS2       | TOUTPS1   | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

| TMR2    | Timer2 Module Register |             |               |           |         |        |         |         |                      | 0000 0000                       |

| TRISB   | TRISB7                 | TRISB6      | TRISB5        | TRISB4    | TRISB3  | TRISB2 | TRISB1  | TRISB0  | 1111 1111            | 1111 1111                       |

| TRISC   | TRISC7                 | TRISC6      | TRISC5        | TRISC4    | TRISC3  | TRISC2 | TRISC1  | TRISC0  | 1111 1111            | 1111 1111                       |

TABLE 15-7: SUMMARY OF REGISTERS ASSOCIATED WITH PWM

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the PWM.

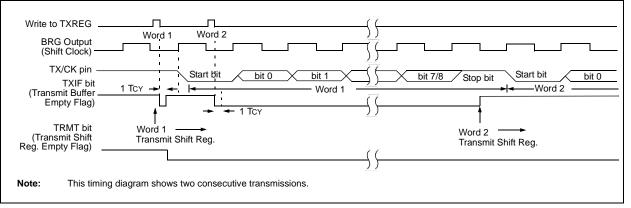

#### TABLE 16-1: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name   | Bit 7                              | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|------------------------------------|--------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE                                | PEIE   | TOIE   | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE                            | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF                            | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN                               | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7                               | BRG6   | BRG5   | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7                             | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXREG  | (REG AUSART Transmit Data Register |        |        |        |        |        |        |        |                      | 0000 0000                       |

| TXSTA  | CSRC                               | TX9    | TXEN   | SYNC   | —      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Asynchronous Transmission.

# 16.4 AUSART Operation During Sleep

The AUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 16.4.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (refer to Section 16.3.2.4 "Synchronous Slave Reception Setup:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE global interrupt enable bit of the INTCON register is also set, then the Interrupt Service Routine at address 0004h will be called.

### 16.4.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Transmission (refer to Section 16.3.2.2 "Synchronous Slave Transmission Setup:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE global interrupt enable bit is also set then the Interrupt Service Routine at address 0004h will be called.

| R/W-0                 | R/W-0                                                                             | R/W-0                                                                                       | R/W-0                        | R/W-0                             | R/W-0                               | R/W-0                                 | R/W-0                         |  |  |

|-----------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------|-----------------------------------|-------------------------------------|---------------------------------------|-------------------------------|--|--|

| WCOL                  | SSPOV                                                                             | SSPEN                                                                                       | CKP                          | SSPM3                             | SSPM2                               | SSPM1                                 | SSPM0                         |  |  |

| bit 7                 | ·                                                                                 |                                                                                             |                              |                                   |                                     |                                       | bit (                         |  |  |

| Levendi               |                                                                                   |                                                                                             |                              |                                   |                                     |                                       |                               |  |  |

| Legend:<br>R = Readat | ala hit                                                                           | W = Writable                                                                                | hit                          |                                   | monted hit rea                      | d oo 'O'                              |                               |  |  |

| -n = Value a          |                                                                                   | '1' = Bit is set                                                                            |                              | 0 = 0 miniple<br>0' = Bit is cle  | mented bit, rea                     | x = Bit is unki                       | 0.011/0                       |  |  |

|                       |                                                                                   |                                                                                             |                              |                                   | aleu                                |                                       | IOWII                         |  |  |

| bit 7                 | WCOL: Writ                                                                        | te Collision Dete                                                                           | ct bit                       |                                   |                                     |                                       |                               |  |  |

|                       |                                                                                   | PBUF register is                                                                            |                              | e it is still transr              | nittina the prev                    | ious word (mus                        | t be cleared i                |  |  |

|                       | softwar                                                                           | •                                                                                           |                              |                                   | 5 1                                 | , , , , , , , , , , , , , , , , , , , |                               |  |  |

|                       | 0 = No colli                                                                      |                                                                                             |                              |                                   |                                     |                                       |                               |  |  |

| bit 6                 | SSPOV: Re                                                                         | ceive Overflow I                                                                            | ndicator bit                 |                                   |                                     |                                       |                               |  |  |

|                       | overflov<br>the SS<br>overflov<br>SSPBU                                           | byte is received<br>w, the data in SS<br>PBUF, even if o<br>w bit is not set s<br>register. | PSR is lost. Conly transmitt | Overflow can or<br>ing data, to a | nly occur in Sla<br>void setting ov | ve mode. The uverflow. In Mas         | user must rea<br>ter mode, th |  |  |

|                       | 0 = No ove                                                                        |                                                                                             |                              | 1.5                               |                                     |                                       |                               |  |  |

| bit 5                 | •                                                                                 | nchronous Seria                                                                             |                              |                                   |                                     | rt. m:m.a.(1)                         |                               |  |  |

|                       |                                                                                   | s serial port and on serial port and on the serial port and                                 |                              |                                   |                                     | t pins <sup>(1)</sup>                 |                               |  |  |

| bit 4                 |                                                                                   | Polarity Select k                                                                           | •                            | ·                                 |                                     |                                       |                               |  |  |

|                       |                                                                                   | e for clock is a h                                                                          | 0                            |                                   |                                     |                                       |                               |  |  |

| <b>h</b> it 0 0       |                                                                                   |                                                                                             |                              | de Celesthite                     |                                     |                                       |                               |  |  |

| bit 3-0               | SSPM<3:0>: Synchronous Serial Port Mode Select bits                               |                                                                                             |                              |                                   |                                     |                                       |                               |  |  |

|                       | 0000 = SPI Master mode, clock = Fosc/4<br>0001 = SPI Master mode, clock = Fosc/16 |                                                                                             |                              |                                   |                                     |                                       |                               |  |  |

|                       |                                                                                   | Master mode, c                                                                              |                              |                                   |                                     |                                       |                               |  |  |

|                       |                                                                                   | Master mode, c                                                                              |                              |                                   |                                     |                                       |                               |  |  |

|                       |                                                                                   | Slave mode, clo                                                                             |                              |                                   |                                     |                                       |                               |  |  |

|                       |                                                                                   | Slave mode, clo                                                                             | -                            | -                                 |                                     | can be used as                        | i/O pin.                      |  |  |

| Note 1: V             | when enabled, th                                                                  | hese pins must b                                                                            | be properly co               | onfigured as inp                  | out or output.                      |                                       |                               |  |  |

## REGISTER 17-1: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (SPI MODE)

### 17.2.7 CLOCK STRETCHING

During any SCL low phase, any device on the  $I^2C$  bus may hold the SCL line low and delay, or pause, the transmission of data. This "stretching" of a transmission allows devices to slow down communication on the bus. The SCL line must be constantly sampled by the master to ensure that all devices on the bus have released SCL for more data.

Stretching usually occurs after an ACK bit of a transmission, delaying the first bit of the next byte. The SSP module hardware automatically stretches for two conditions:

- After a 10-bit address byte is received (update SSPADD register)

- Anytime the CKP bit of the SSPCON register is cleared by hardware

The module will hold SCL low until the CKP bit is set. This allows the user slave software to update SSPBUF with data that may not be readily available. In 10-bit addressing modes, the SSPADD register must be updated after receiving the first and second address bytes. The SSP module will hold the SCL line low until the SSPADD has a byte written to it. The UA bit of the SSPSTAT register will be set, along with SSPIF, indicating an address update is needed.

### 17.2.8 FIRMWARE MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits of the SSPSTAT register are cleared from a Reset or when the SSP module is disabled (SSPEN cleared). The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set or the bus is Idle and both the S and P bits are clear.

In Firmware Master mode, the SCL and SDA lines are manipulated by setting/clearing the corresponding TRIS bit(s). The output level is always low, irrespective of the value(s) in the corresponding PORT register bit(s). When transmitting a '1', the TRIS bit must be set (input) and a '0', the TRIS bit must be clear (output).

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt will occur if enabled):

- Start condition

- Stop condition

- Data transfer byte transmitted/received

Firmware Master Mode of operation can be done with either the Slave mode Idle (SSPM<3:0 > = 1011), or with either of the Slave modes in which interrupts are enabled. When both master and slave functionality is enabled, the software needs to differentiate the source(s) of the interrupt. Refer to Application Note AN554, Software Implementation of  $l^2 C^{TM}$  Bus Master (DS00554) for more information.

### 17.2.9 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allow the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSPSTAT register is set or when the bus is Idle, and both the S and P bits are clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the Stop condition occurs.

In Multi-Master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRIS bits). There are two stages where this arbitration of the bus can be lost. They are the Address Transfer and Data Transfer stages.

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an  $\overrightarrow{ACK}$  pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

Refer to Application Note AN578, Use of the SSP Module in the  $l^2 C^{TM}$  Multi-Master Environment (DS00578) for more information.

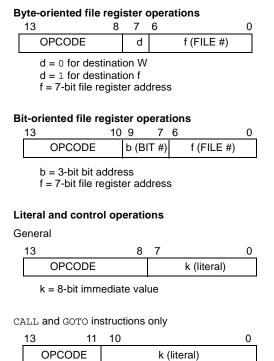

# 21.0 INSTRUCTION SET SUMMARY

The PIC16(L)F722/3/4/6/7 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 21-1, while the various opcode fields are summarized in Table 21-1.

Table 21-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8-bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 21.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF PORTB instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended consequence of clearing the condition that set the RBIF flag.

### TABLE 21-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ . It is<br>the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                  |

| PC    | Program Counter                                                                                                                                                                   |

| TO    | Time-out bit                                                                                                                                                                      |

| С     | Carry bit                                                                                                                                                                         |

| DC    | Digit carry bit                                                                                                                                                                   |

| Z     | Zero bit                                                                                                                                                                          |

| PD    | Power-down bit                                                                                                                                                                    |

# FIGURE 21-1: GENERAL FORMAT FOR INSTRUCTIONS

### 22.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 22.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

#### 23.5 **Thermal Considerations**

| Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |           |                                        |      |                          |                                                          |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------|------|--------------------------|----------------------------------------------------------|--|--|--|--|--|

| Param<br>No.                                                                                                             | Sym.      | Characteristic                         | Тур. | Units                    | Conditions                                               |  |  |  |  |  |

| TH01                                                                                                                     | θJA       | Thermal Resistance Junction to Ambient | 60   | °C/W                     | 28-pin SPDIP package                                     |  |  |  |  |  |

|                                                                                                                          |           |                                        | 80   | °C/W                     | 28-pin SOIC package                                      |  |  |  |  |  |

|                                                                                                                          |           |                                        | 90   | °C/W                     | 28-pin SSOP package                                      |  |  |  |  |  |

|                                                                                                                          |           |                                        | 27.5 | °C/W                     | 28-pin UQFN 4x4mm package                                |  |  |  |  |  |

|                                                                                                                          |           | 27.5                                   | °C/W | 28-pin QFN 6x6mm package |                                                          |  |  |  |  |  |

|                                                                                                                          |           |                                        | 47.2 | °C/W                     | 40-pin PDIP package                                      |  |  |  |  |  |

|                                                                                                                          |           |                                        | 46   | °C/W                     | 44-pin TQFP package                                      |  |  |  |  |  |

|                                                                                                                          |           |                                        | 24.4 | °C/W                     | 44-pin QFN 8x8mm package                                 |  |  |  |  |  |

| TH02                                                                                                                     | θJC       | Thermal Resistance Junction to Case    | 31.4 | °C/W                     | 28-pin SPDIP package                                     |  |  |  |  |  |

|                                                                                                                          |           |                                        | 24   | °C/W                     | 28-pin SOIC package                                      |  |  |  |  |  |

|                                                                                                                          |           |                                        | 24   | °C/W                     | 28-pin SSOP package                                      |  |  |  |  |  |

|                                                                                                                          |           |                                        | 24   | °C/W                     | 28-pin UQFN 4x4mm package                                |  |  |  |  |  |

|                                                                                                                          |           |                                        | 24   | °C/W                     | 28-pin QFN 6x6mm package                                 |  |  |  |  |  |

|                                                                                                                          |           |                                        | 24.7 | °C/W                     | 40-pin PDIP package                                      |  |  |  |  |  |

|                                                                                                                          |           |                                        | 14.5 | °C/W                     | 44-pin TQFP package                                      |  |  |  |  |  |

|                                                                                                                          |           |                                        | 20   | °C/W                     | 44-pin QFN 8x8mm package                                 |  |  |  |  |  |

| TH03                                                                                                                     | TJMAX     | Maximum Junction Temperature           | 150  | °C                       |                                                          |  |  |  |  |  |

| TH04                                                                                                                     | PD        | Power Dissipation                      |      | W                        | PD = PINTERNAL + PI/O                                    |  |  |  |  |  |

| TH05                                                                                                                     | PINTERNAL | Internal Power Dissipation             | _    | W                        | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |  |  |  |  |  |

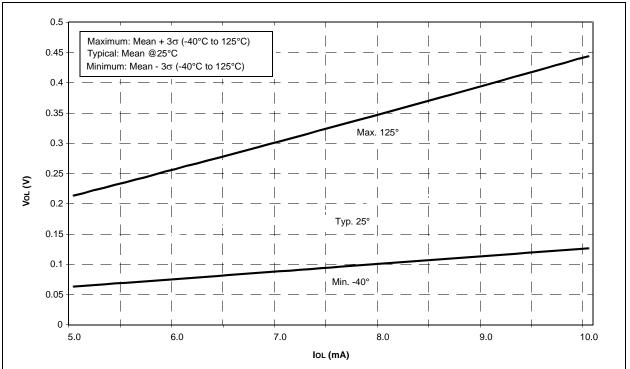

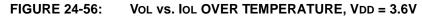

| TH06                                                                                                                     | Pi/o      | I/O Power Dissipation                  |      | W                        | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |  |  |  |  |  |

| TH07                                                                                                                     | Pder      | Derated Power                          | _    | W                        | Pder = PDmax (Tj - Ta)/θja <sup>(2)</sup>                |  |  |  |  |  |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

**2:** TA = Ambient Temperature

**3:** T<sub>J</sub> = Junction Temperature

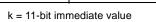

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |       |                                         |      |        |        |       |                    |  |

|----------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------|------|--------|--------|-------|--------------------|--|

| Param<br>No.                                                                                                         | Sym.  | Characteristic                          | Min. | Тур†   | Max.   | Units | Conditions         |  |

| OS01                                                                                                                 | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC   | _      | 37     | kHz   | LP Oscillator mode |  |

|                                                                                                                      |       |                                         | DC   | _      | 4      | MHz   | XT Oscillator mode |  |

|                                                                                                                      |       |                                         | DC   | _      | 20     | MHz   | HS Oscillator mode |  |

|                                                                                                                      |       |                                         | DC   | _      | 20     | MHz   | EC Oscillator mode |  |

|                                                                                                                      |       | Oscillator Frequency <sup>(1)</sup>     | —    | 32.768 | —      | kHz   | LP Oscillator mode |  |

|                                                                                                                      |       |                                         | 0.1  | _      | 4      | MHz   | XT Oscillator mode |  |

|                                                                                                                      |       |                                         | 1    | _      | 20     | MHz   | HS Oscillator mode |  |

|                                                                                                                      |       |                                         | DC   | _      | 4      | MHz   | RC Oscillator mode |  |

| OS02                                                                                                                 | Tosc  | External CLKIN Period <sup>(1)</sup>    | 27   | —      | ×      | μs    | LP Oscillator mode |  |

|                                                                                                                      |       |                                         | 250  | _      | ×      | ns    | XT Oscillator mode |  |

|                                                                                                                      |       |                                         | 50   | _      | ×      | ns    | HS Oscillator mode |  |

|                                                                                                                      |       |                                         | 50   | _      | ×      | ns    | EC Oscillator mode |  |

|                                                                                                                      |       | Oscillator Period <sup>(1)</sup>        | —    | 30.5   | —      | μs    | LP Oscillator mode |  |

|                                                                                                                      |       |                                         | 250  | _      | 10,000 | ns    | XT Oscillator mode |  |

|                                                                                                                      |       |                                         | 50   | _      | 1,000  | ns    | HS Oscillator mode |  |

|                                                                                                                      |       |                                         | 250  | _      | —      | ns    | RC Oscillator mode |  |

| OS03                                                                                                                 | Тсү   | Instruction Cycle Time <sup>(1)</sup>   | 200  | Тсү    | DC     | ns    | TCY = 4/FOSC       |  |

| OS04*                                                                                                                | TosH, | External CLKIN High,                    | 2    | —      | —      | μS    | LP oscillator      |  |

|                                                                                                                      | TosL  | External CLKIN Low                      | 100  | —      | —      | ns    | XT oscillator      |  |

|                                                                                                                      |       |                                         | 20   | —      | —      | ns    | HS oscillator      |  |

| OS05*                                                                                                                | TosR, | External CLKIN Rise,                    | 0    | —      | ×      | ns    | LP oscillator      |  |

|                                                                                                                      | TosF  | External CLKIN Fall                     | 0    | —      | ×      | ns    | XT oscillator      |  |

|                                                                                                                      |       |                                         | 0    | —      | ×      | ns    | HS oscillator      |  |

### TABLE 23-1: CLOCK OSCILLATOR TIMING REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

#### TABLE 23-2: **OSCILLATOR PARAMETERS**

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |          |                                                          |                    |      |      |      |       |                                                                                       |  |

|----------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------|--------------------|------|------|------|-------|---------------------------------------------------------------------------------------|--|

| Param<br>No.                                                                                                         | Sym.     | Characteristic                                           | Freq.<br>Tolerance | Min. | Тур† | Max. | Units | Conditions                                                                            |  |

| OS08                                                                                                                 | HFosc    | Internal Calibrated HFINTOSC<br>Frequency <sup>(2)</sup> | ±2%                |      | 16.0 |      | MHz   | $\begin{array}{l} 0^{\circ}C \leq TA \leq +85^{\circ}C, \\ VDD \geq 2.5V \end{array}$ |  |

|                                                                                                                      |          |                                                          | ±5%                | _    | 16.0 | —    | MHz   | $\text{-40°C} \leq \text{TA} \leq \text{+125°C}$                                      |  |

| OS08A                                                                                                                | MFosc    | Internal Calibrated MFINTOSC<br>Frequency <sup>(2)</sup> | ±2%                | _    | 500  | _    | kHz   | $0^{\circ}C \le TA \le +85^{\circ}C$<br>VDD $\ge 2.5V$                                |  |

|                                                                                                                      |          |                                                          | ±5%                | _    | 500  | 10   | kHz   | $-40^{\circ}C \leq TA \leq +125^{\circ}C$                                             |  |

| OS10*                                                                                                                | TIOSC ST | HFINTOSC Wake-up from Sleep<br>Start-up Time             | —                  | _    | 5    | 8    | μS    |                                                                                       |  |

|                                                                                                                      |          | MFINTOSC Wake-up from Sleep<br>Start-up Time             | —                  |      | 20   | 30   | μS    |                                                                                       |  |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are t not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

2: To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

3: By design.

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                 | <u>[X]</u> (1)                                                                                                       | ¥                                                           | <u>/xx</u>                                   | <u>xxx</u>                                                     | Exam   | ples:                                                                                                                                                       |

|--------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                   | Tape and Reel<br>Option                                                                                              | Temperature<br>Range                                        | Package                                      | Pattern                                                        | b) F   | IC16F722-E/SP 301 = Extended Temp.,<br>kinny PDIP package, QTP pattern #301<br>IC16F722-I/SO = Industrial Temp., SOIC<br>ackage                             |

| Device:                  | PIC16F722, PIC16<br>PIC16F723, PIC16<br>PIC16F724, PIC16<br>PIC16F726, PIC16<br>PIC16F726, PIC16<br>PIC16F727, PIC16 | LF723, PIC16F723<br>LF724, PIC16F724<br>LF726, PIC16F726    | T, PIC16LF72<br>T, PIC16LF72<br>T, PIC16LF72 | 23T <sup>(1)</sup><br>24T <sup>(1)</sup><br>26T <sup>(1)</sup> |        | uonugo                                                                                                                                                      |

| Tape and Reel<br>Option: | $I = -40^{\circ}C \text{ to}$ $E = -40^{\circ}C \text{ to}$ $MV = \text{Micro Le}$                                   |                                                             |                                              |                                                                |        |                                                                                                                                                             |

| Temperature<br>Range:    |                                                                                                                      | o +85°C (Indus<br>o +125°C (Exten                           |                                              |                                                                | Note 1 | <ul> <li>Tape and Reel identifier only appears in the<br/>catalog part number description. This<br/>identifier is used for ordering purposes and</li> </ul> |

| Package:                 | P = Plastic IPT = TQFP (1SO = SOIC                                                                                   | ead Frame (QFN)<br>DIP<br>Thin Quad Flatpack<br>Plastic DIP | )                                            |                                                                |        | is not printed on the device package. Check<br>with your Microchip Sales Office for package<br>availability with the Tape and Reel option.                  |