#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 11x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf722-e-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

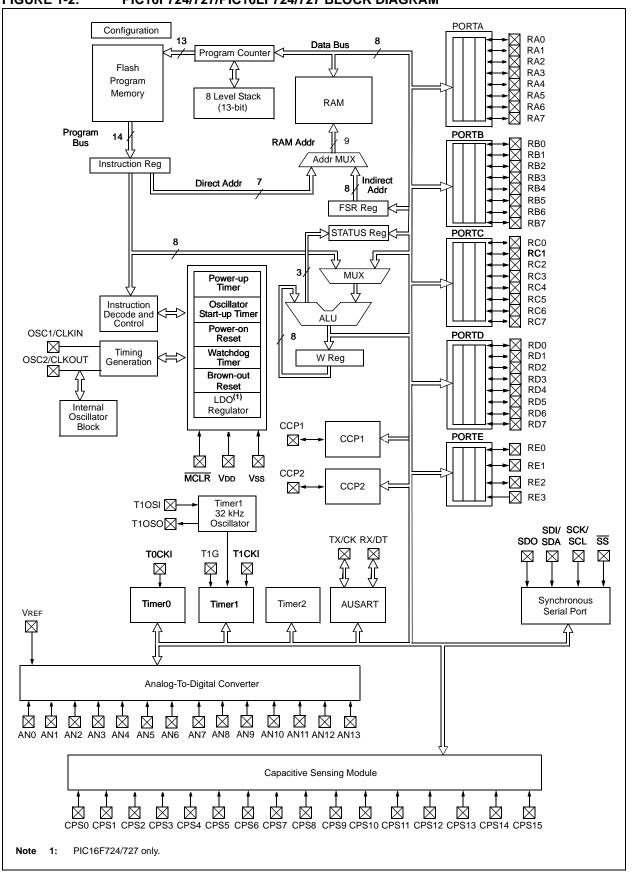

FIGURE 1-2: PIC16F724/727/PIC16LF724/727 BLOCK DIAGRAM

| FIGURE 2-5: | PIC16F723/LF723 AND PIC16F724/LF724 SPECIAL FUNCTION REGISTERS |

|-------------|----------------------------------------------------------------|

|             |                                                                |

| Indirect addr.(*)    | 00h     | Indirect addr. <sup>(*)</sup>   | 80h     | Indirect addr.(*)           | 100h         | Indirect addr.(*)     | 180h     |

|----------------------|---------|---------------------------------|---------|-----------------------------|--------------|-----------------------|----------|

| TMR0                 | 01h     | OPTION                          | 81h     | TMR0                        | 101h         | OPTION                | 181h     |

| PCL                  | 02h     | PCL                             | 82h     | PCL                         | 102h         | PCL                   | 182h     |

| STATUS               | 03h     | STATUS                          | 83h     | STATUS                      | 103h         | STATUS                | 183h     |

| FSR                  | 04h     | FSR                             | 84h     | FSR                         | 104h         | FSR                   | 184h     |

| PORTA                | 05h     | TRISA                           | 85h     |                             | 105h         | ANSELA                | 185h     |

| PORTB                | 06h     | TRISB                           | 86h     |                             | 106h         | ANSELB                | 186h     |

| PORTC                | 07h     | TRISC                           | 87h     |                             | 107h         |                       | 187h     |

| PORTD <sup>(1)</sup> | 08h     | TRISD <sup>(1)</sup>            | 88h     | CPSCON0                     | 108h         | ANSELD <sup>(1)</sup> | 188h     |

| PORTE                | 09h     | TRISE                           | 89h     | CPSCON1                     | 109h         | ANSELE <sup>(1)</sup> | 189h     |

| PCLATH               | 0Ah     | PCLATH                          | 8Ah     | PCLATH                      | 10Ah         | PCLATH                | 18Ah     |

| INTCON               | 0Bh     | INTCON                          | 8Bh     | INTCON                      | 10Bh         | INTCON                | 18Bh     |

| PIR1                 | 0Ch     | PIE1                            | 8Ch     | PMDATL                      | 10Ch         | PMCON1                | 18Ch     |

| PIR2                 | 0Dh     | PIE2                            | 8Dh     | PMADRL                      | 10Dh         | Reserved              | 18Dh     |

| TMR1L                | 0Eh     | PCON                            | 8Eh     | PMDATH                      | 10Eh         | Reserved              | 18Eh     |

| TMR1H                | 0Fh     | T1GCON                          | 8Fh     | PMADRH                      | 10Fh         | Reserved              | 18Fh     |

| T1CON                | 10h     | OSCCON                          | 90h     |                             | 110h         |                       | 190h     |

| TMR2                 | 11h     | OSCTUNE                         | 91h     |                             | 111h         |                       | 191h     |

| T2CON                | 12h     | PR2                             | 92h     |                             | 112h         |                       | 192h     |

| SSPBUF               | 13h     | SSPADD/SSPMSK                   | 93h     |                             | 113h         |                       | 193h     |

| SSPCON               | 14h     | SSPSTAT                         | 94h     |                             | 114h         |                       | 194h     |

| CCPR1L               | 15h     | WPUB                            | 95h     |                             | 115h         |                       | 195h     |

| CCPR1H               | 16h     | IOCB                            | 96h     |                             | 116h         |                       | 196h     |

| CCP1CON              | 17h     |                                 | 97h     |                             | 117h         |                       | 197h     |

| RCSTA                | 18h     | TXSTA                           | 98h     |                             | 118h         |                       | 198h     |

| TXREG                | 19h     | SPBRG                           | 99h     |                             | 119h         |                       | 199h     |

| RCREG                | 1Ah     |                                 | 9Ah     |                             | 11Ah         |                       | 19Ah     |

| CCPR2L               | 1Bh     |                                 | 9Bh     |                             | 11Bh         |                       | 19Bh     |

| CCPR2H               | 1Ch     | APFCON                          | 9Ch     |                             | 11Ch         |                       | 19Ch     |

| CCP2CON              | 1Dh     | FVRCON                          | 9Dh     |                             | 11Dh         |                       | 19Dh     |

| ADRES                | 1Eh     |                                 | 9Eh     |                             | 11Eh         |                       | 19Eh     |

| ADCON0               | 1Fh     | ADCON1                          | 9Fh     |                             | 11Fh         |                       | 19Fh     |

|                      | 20h     | General                         | A0h     | General Purpose<br>Register | 120h         |                       | 1A0h     |

| General<br>Purpose   |         | Purpose<br>Register<br>80 Bytes |         | 16 Bytes                    | 12Fh<br>130h |                       |          |

| Register<br>96 Bytes |         |                                 | EFh     |                             | 16Fh         |                       | 1EFh     |

| JU Dytes             |         | Accesses<br>70h-7Fh             | F0h     | Accesses<br>70h-7Fh         | 170h         | Accesses<br>70h-7Fh   | 1F0h     |

|                      | 7Fh     |                                 | FFh     |                             | 17Fh         |                       | 1FFh     |

| Bank 0               | J       | Bank 1                          | 1       | Bank 2                      | J            | Bank 3                | <b>_</b> |

| nd: = Unimple        | emented | l data memory locatio           | ns. rea | d as '0'.                   |              |                       |          |

#### EXAMPLE 4-1: SAVING W, STATUS AND PCLATH REGISTERS IN RAM

| MOVWF W_TEMP                       | ;Copy W to W_TEMP register                                                                       |

|------------------------------------|--------------------------------------------------------------------------------------------------|

| SWAPF STATUS,W                     | ;Swap status to be saved into W                                                                  |

| BANKSEL STATUS TEMP                | Swaps are used because they do not affect the status bits;<br>Select regardless of current bank; |

| MOVWF STATUS TEMP                  | Copy status to bank zero STATUS TEMP register                                                    |

| MOVF PCLATH,W                      | Copy PCLATH to W register                                                                        |

| MOVWF PCLATH_TEMP                  | Copy W register to PCLATH_TEMP                                                                   |

| :                                  |                                                                                                  |

| :(ISR)                             | ;Insert user code here                                                                           |

|                                    |                                                                                                  |

| BANKSEL STATUS_TEMP                | ;Select regardless of current bank                                                               |

| MOVF PCLATH_TEMP,W<br>MOVWF PCLATH | ,<br>:Restore PCLATH                                                                             |

| SWAPF STATUS TEMP,W                | ;Swap STATUS_TEMP register into W                                                                |

|                                    | ;(sets bank to original state)                                                                   |

| MOVWF STATUS                       | ;Move W into STATUS register                                                                     |

| SWAPF W_TEMP,F                     | ;Swap W_TEMP                                                                                     |

| SWAPF W_TEMP,W                     | ;Swap W_TEMP into W                                                                              |

|                                    |                                                                                                  |

### 4.5.1 INTCON REGISTER

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, PORTB change and external RB0/INT/SEG0 pin interrupts.

| Note: | Interrupt flag bits are set when an interrupt |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|

|       | condition occurs, regardless of the state of  |  |  |  |  |  |

|       | its corresponding enable bit or the global    |  |  |  |  |  |

|       | enable bit, GIE of the INTCON register.       |  |  |  |  |  |

|       | User software should ensure the               |  |  |  |  |  |

|       | appropriate interrupt flag bits are clear     |  |  |  |  |  |

|       | prior to enabling an interrupt.               |  |  |  |  |  |

#### 4.5.2 PIE1 REGISTER

The PIE1 register contains the interrupt enable bits, as shown in Register 4-2.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

| <b>REGISTER 4-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1</b> |

|-------------------------------------------------------------------|

|-------------------------------------------------------------------|

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|---------|-------|-------|-------|-------|--------|--------|--------|

| TMR1GIE | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE |

| bit 7   |       |       |       |       |        |        | bit 0  |

| Legend:      |                       |                                                                    |                        |                    |

|--------------|-----------------------|--------------------------------------------------------------------|------------------------|--------------------|

| R = Readab   | ole bit               | W = Writable bit                                                   | U = Unimplemented bit, | read as '0'        |

| -n = Value a | at POR                | '1' = Bit is set                                                   | '0' = Bit is cleared   | x = Bit is unknown |

|              |                       |                                                                    |                        |                    |

| bit 7        |                       | E: Timer1 Gate Interrupt Ena                                       |                        |                    |

|              |                       | ble the Timer1 Gate Acquisition<br>ole the Timer1 Gate Acquisition |                        |                    |

| bit 6        | ADIE: A/              | D Converter (ADC) Interrupt                                        | Enable bit             |                    |

|              |                       | les the ADC interrupt<br>bles the ADC interrupt                    |                        |                    |

| bit 5        | RCIE: US              | SART Receive Interrupt Enal                                        | ble bit                |                    |

|              | 1 = Enab              | les the USART receive inter                                        | rupt                   |                    |

|              | 0 = Disat             | bles the USART receive inter                                       | rrupt                  |                    |

| bit 4        | TXIE: US              | SART Transmit Interrupt Ena                                        | ble bit                |                    |

|              |                       | oles the USART transmit inte<br>oles the USART transmit inte       | •                      |                    |

| bit 3        |                       | Synchronous Serial Port (SSI                                       | 1                      |                    |

| bit 5        |                       | les the SSP interrupt                                              |                        |                    |

|              |                       | bles the SSP interrupt                                             |                        |                    |

| bit 2        | CCP1IE:               | CCP1 Interrupt Enable bit                                          |                        |                    |

|              |                       | les the CCP1 interrupt                                             |                        |                    |

|              | 0 = Disat             | oles the CCP1 interrupt                                            |                        |                    |

| bit 1        | TMR2IE:               | TMR2 to PR2 Match Interru                                          | pt Enable bit          |                    |

|              |                       | eles the Timer2 to PR2 match                                       |                        |                    |

|              |                       | bles the Timer2 to PR2 matc                                        | •                      |                    |

| bit 0        |                       | Timer1 Overflow Interrupt E                                        |                        |                    |

|              | 1 = Enab<br>0 = Disat | ples the Timer1 overflow inter                                     | rrupt                  |                    |

# PIC16(L)F722/3/4/6/7

## 8.0 DEVICE CONFIGURATION

Device Configuration consists of Configuration Word 1 and Configuration Word 2 registers, Code Protection and Device ID.

### 8.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 register at 2007h and Configuration Word 2 register at 2008h. These registers are only accessible during programming.

#### REGISTER 8-1: CONFIG1: CONFIGURATION WORD REGISTER 1

|        |   | R/P-1 | R/P-1 | U-1 <sup>(4)</sup> | R/P-1 | R/P-1  | R/P-1  |

|--------|---|-------|-------|--------------------|-------|--------|--------|

| —      | _ | DEBUG | PLLEN | _                  | BORV  | BOREN1 | BOREN0 |

| bit 15 |   |       |       |                    |       |        | bit 8  |

| U-1 <sup>(4)</sup> | R/P-1 |

|--------------------|-------|-------|-------|-------|-------|-------|-------|

| —                  | CP    | MCLRE | PWRTE | WDTE  | FOSC2 | FOSC1 | FOSC0 |

| bit 7              |       |       |       |       |       |       | bit 0 |

| Legend:           | P = Programmable bit |                             |                    |

|-------------------|----------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared        | x = Bit is unknown |

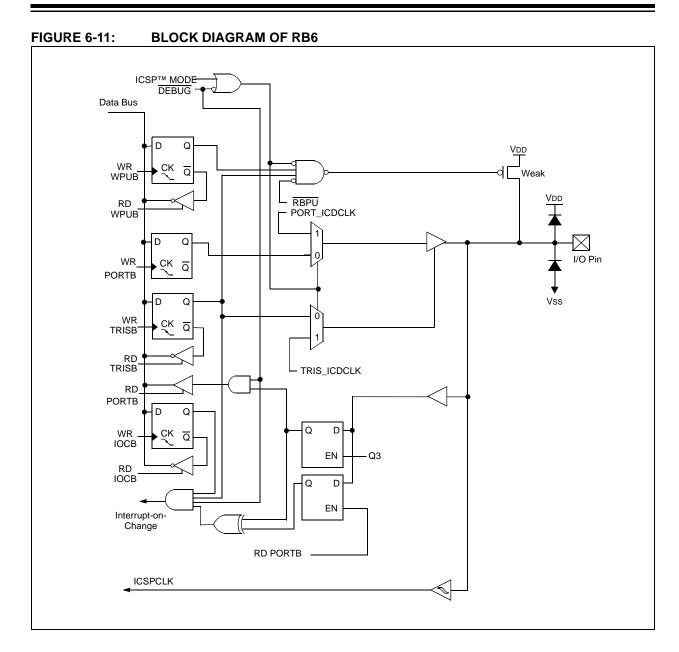

| bit 13  | <b>DEBUG:</b> In-Circuit Debugger Mode bit<br>1 = In-Circuit Debugger disabled, RB6/ICSPCLK and RB7/ICSPDAT are general purpose I/O pins<br>0 = In-Circuit Debugger enabled, RB6/ICSPCLK and RB7/ICSPDAT are dedicated to the debugger |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 12  | <b>PLLEN:</b> INTOSC PLL Enable bit<br>0 = INTOSC Frequency is 500 kHz<br>1 = INTOSC Frequency is 16 MHz (32x)                                                                                                                         |

| bit 11  | Unimplemented: Read as '1'                                                                                                                                                                                                             |

| bit 10  | <b>BORV:</b> Brown-out Reset Voltage selection bit<br>0 = Brown-out Reset Voltage (VBOR) set to 2.5 V nominal<br>1 = Brown-out Reset Voltage (VBOR) set to 1.9 V nominal                                                               |

| bit 9-8 | <b>BOREN&lt;1:0&gt;:</b> Brown-out Reset Selection bits <sup>(1)</sup><br>0x = BOR disabled (Preconditioned State)<br>10 = BOR enabled during operation and disabled in Sleep<br>11 = BOR enabled                                      |

| bit 7   | Unimplemented: Read as '1'                                                                                                                                                                                                             |

| bit 6   | <b>CP</b> : Code Protection bit <sup>(2)</sup><br>1 = Program memory code protection is disabled                                                                                                                                       |

|         | 0 = Program memory code protection is enabled                                                                                                                                                                                          |

| bit 5   | MCLRE: RE3/MCLR pin function select bit <sup>(3)</sup><br>1 = RE3/MCLR pin function is MCLR                                                                                                                                            |

|         | 0 = RE3/MCLR pin function is digital input, MCLR internally tied to VDD                                                                                                                                                                |

| Note 1: | Enabling Brown-out Reset does not automatically enable Power-up Timer.                                                                                                                                                                 |

| 2:      | The entire program memory will be erased when the code protection is turned off.                                                                                                                                                       |

| 3:      | When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.                                                                                                                                                 |

| 4.      | MDLAD <sup>®</sup> VIDE maaka unimplemented Configuration bits to (0)                                                                                                                                                                  |

**4:** MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

#### 11.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the OPTION register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

| Note: | When the prescaler is assigned to WDT, a  |

|-------|-------------------------------------------|

|       | CLRWDTnstruction will clear the prescaler |

|       | along with the WDT.                       |

#### 11.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The T0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The T0IF bit can only be cleared in software. The Timer0 interrupt enable is the T0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|

|       | processor from Sleep since the timer is |  |  |  |  |  |

|       | frozen during Sleep.                    |  |  |  |  |  |

#### 11.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 23.0** "**Electrical Specifications**".

## PIC16(L)F722/3/4/6/7

| FIGURE 12-6:           | TIMER1 GATE SINGLE                                          | -PULSE AND TOGGLE COMBINED MODE                  |

|------------------------|-------------------------------------------------------------|--------------------------------------------------|

| TMR1GE                 |                                                             |                                                  |

| T1GPOL                 |                                                             |                                                  |

| T1GSPM                 |                                                             |                                                  |

| T1GTM                  |                                                             |                                                  |

| T1GG <u>O/</u><br>DONE | ← Set by software<br>Counting enabled<br>rising edge of T10 | Cleared by hardware on<br>falling edge of T1GVAL |

| T1G_IN                 |                                                             |                                                  |

| тіскі                  |                                                             |                                                  |

| T1GVAL                 |                                                             |                                                  |

| TIMER1                 | Ν                                                           | N+1 $N+2$ $N+3$ $N+4$                            |

| TMR1GIF                | - Cleared by software                                       | Set by hardware on<br>falling edge of T1GVAL —   |

PIC16(L)F722/3/4/6/7

## 18.0 PROGRAM MEMORY READ

The Flash program memory is readable during normal operation over the full VDD range of the device. To read data from Program Memory, five Special Function Registers (SFRs) are used:

- PMCON1

- PMDATL

- PMDATH

- PMADRL

- PMADRH

The value written to the PMADRH:PMADRL register pair determines which program memory location is read. The read operation will be initiated by setting the RD bit of the PMCON1 register. The program memory flash controller takes two instructions to complete the read, causing the second instruction after the setting the RD bit will be ignored. To avoid conflict with program execution, it is recommended that the two instructions following the setting of the RD bit are NOP. When the read completes, the result is placed in the PMDATLH:PMDATL register pair. Refer to Example 18-1 for sample code.

**Note:** Code-protect does not effect the CPU from performing a read operation on the program memory. For more information, refer to **Section 8.2 "Code Protection"**.

### EXAMPLE 18-1: PROGRAM MEMORY READ

|                      | BANKSEL<br>MOVF<br>MOVWF<br>MOVF | PMADRL<br>MS_PROG_ADDF<br>PMADRH<br>LS_PROG_ADDR | ;MS Byte of Program Address to read                                                        |

|----------------------|----------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------|

|                      | MOVWF                            | PMADRL                                           | ;LS Byte of Program Address to read                                                        |

| - 0                  | BANKSEL<br>BSF                   | PMCON1                                           | ;<br>Initiata Bood                                                                         |

| ired                 | NOP                              | PMCON1, RD                                       | ;Initiate Read                                                                             |

| Required<br>Sequence | NOP                              |                                                  | ;Any instructions here are ignored as program<br>;memory is read in second cycle after BSF |

|                      | BANKSEL                          | PMDATL                                           | •                                                                                          |

|                      | MOVF                             | PMDATL, W                                        | ;W = LS Byte of Program Memory Read                                                        |

|                      | MOVWF                            | LOWPMBYTE                                        | ;<br>W. MO.D. to a December Manager December 2                                             |

|                      | MOVF<br>MOVWF                    | PMDATH, W<br>HIGHPMBYTE                          | ;W = MS Byte of Program Memory Read                                                        |

|                      |                                  |                                                  | ,                                                                                          |

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                 | <u>[X]</u> (1)                                                                                                       | ¥                                                           | <u>/xx</u>                                   | <u>xxx</u>                                                     | Exam   | ples:                                                                                                                                                       |

|--------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                   | Tape and Reel<br>Option                                                                                              | Temperature<br>Range                                        | Package                                      | Pattern                                                        | b) F   | IC16F722-E/SP 301 = Extended Temp.,<br>kinny PDIP package, QTP pattern #301<br>IC16F722-I/SO = Industrial Temp., SOIC<br>ackage                             |

| Device:                  | PIC16F722, PIC16<br>PIC16F723, PIC16<br>PIC16F724, PIC16<br>PIC16F726, PIC16<br>PIC16F726, PIC16<br>PIC16F727, PIC16 | LF723, PIC16F723<br>LF724, PIC16F724<br>LF726, PIC16F726    | T, PIC16LF72<br>T, PIC16LF72<br>T, PIC16LF72 | 23T <sup>(1)</sup><br>24T <sup>(1)</sup><br>26T <sup>(1)</sup> |        | uonugo                                                                                                                                                      |

| Tape and Reel<br>Option: | $I = -40^{\circ}C \text{ to}$ $E = -40^{\circ}C \text{ to}$ $MV = \text{Micro Le}$                                   |                                                             |                                              |                                                                |        |                                                                                                                                                             |

| Temperature<br>Range:    |                                                                                                                      | o +85°C (Indus<br>o +125°C (Exten                           |                                              |                                                                | Note 1 | <ul> <li>Tape and Reel identifier only appears in the<br/>catalog part number description. This<br/>identifier is used for ordering purposes and</li> </ul> |

| Package:                 | P = Plastic IPT = TQFP (1SO = SOIC                                                                                   | ead Frame (QFN)<br>DIP<br>Thin Quad Flatpack<br>Plastic DIP | )                                            |                                                                |        | is not printed on the device package. Check<br>with your Microchip Sales Office for package<br>availability with the Tape and Reel option.                  |