#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf722t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

# PIC16(L)F722/3/4/6/7

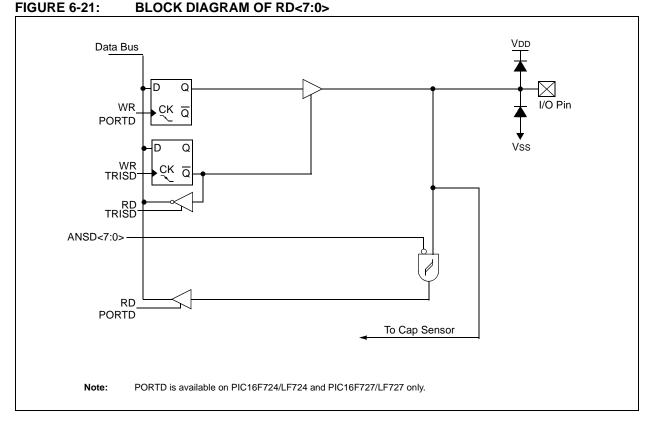

#### 6.5.6 RD4/CPS12

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### 6.5.7 RD5/CPS13

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- a capacitive sensing input

#### 6.5.8 RD6/CPS14

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### 6.5.9 RD7/CPS15

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

| TABLE 6-4: SUMM | IARY OF REGISTERS ASSOCIATED WITH PORTD <sup>(1)</sup> |

|-----------------|--------------------------------------------------------|

|-----------------|--------------------------------------------------------|

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|--------|--------|--------|---------|---------|--------|--------|----------------------|---------------------------------|

| ANSELD  | ANSD7  | ANSD6  | ANSD5  | ANSD4  | ANSD3   | ANSD2   | ANSD1  | ANSD0  | 1111 1111            | 1111 1111                       |

| CPSCON0 | CPSON  | —      | —      | —      | CPSRNG1 | CPSRNG0 | CPSOUT | TOXCS  | 0 0000               | 0 0000                          |

| CPSCON1 |        | —      | —      | _      | CPSCH3  | CPSCH2  | CPSCH1 | CPSCH0 | 0000                 | 0000                            |

| PORTD   | RD7    | RD6    | RD5    | RD4    | RD3     | RD2     | RD1    | RD0    | XXXX XXXX            | xxxx xxxx                       |

| TRISD   | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3  | TRISD2  | TRISD1 | TRISD0 | 1111 1111            | 1111 1111                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTD.**Note 1:**These registers are not implemented on the PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'.

#### © 2007-2015 Microchip Technology Inc.

#### DS40001341F-page 79

#### REGISTER 6-17: ANSELE: PORTE ANALOG SELECT REGISTER

| U-0                                | U-0 U-0 U-0 |  |     | U-0                                      | R/W-1                | R/W-1                | R/W-1                |  |  |

|------------------------------------|-------------|--|-----|------------------------------------------|----------------------|----------------------|----------------------|--|--|

| —                                  | _           |  | _   | _                                        | ANSE2 <sup>(2)</sup> | ANSE1 <sup>(2)</sup> | ANSE0 <sup>(2)</sup> |  |  |

| bit 7                              |             |  |     |                                          |                      | bit 0                |                      |  |  |

|                                    |             |  |     |                                          |                      |                      |                      |  |  |

| Legend:                            |             |  |     |                                          |                      |                      |                      |  |  |

| R = Readable bit W = Writable bit  |             |  | bit | U = Unimplemented bit, read as '0'       |                      |                      |                      |  |  |

| -n = Value at POR '1' = Bit is set |             |  |     | 0' = Bit is cleared $x = Bit is unknown$ |                      |                      |                      |  |  |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 **ANSE<2:0>:** Analog Select between Analog or Digital Function on Pins RE<2:0>, respectively 0 = Digital I/O. Pin is assigned to port or Digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital Input buffer disabled.

2: ANSELE register is not implemented on the PIC16F722/723/726/PIC16LF722/723/726. Read as '0'

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3                 | Bit 2                 | Bit 1                 | Bit 0                 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-------|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|----------------------|---------------------------------|

| ADCON0 |       |       | CHS3  | CHS2  | CHS1                  | CHS0                  | GO/DONE               | ADON                  | 00 0000              | 00 0000                         |

| ANSELE | _     |       | _     | _     | _                     | ANSE2                 | ANSE1                 | ANSE0                 | 111                  | 111                             |

| PORTE  | _     | _     | _     | _     | RE3                   | RE2                   | RE1                   | RE0                   | xxxx                 | xxxx                            |

| TRISE  | _     |       | _     | _     | TRISE3 <sup>(2)</sup> | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> | 1111                 | 1111                            |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE

Note 1: These registers are not implemented on the PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'.

**2:** This bit is always '1' as RE3 is input only.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### 7.5 Oscillator Tuning

The INTOSC is factory calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 7-2). The default value of the OSCTUNE register is '0'. The value is a 6-bit two's complement number.

When the OSCTUNE register is modified, the INTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

#### REGISTER 7-2: OSCTUNE: OSCILLATOR TUNING REGISTER

| —         —         TUN5         TUN4         TUN3         TUN2         TUN1         T           bit 7 | W-0   |

|--------------------------------------------------------------------------------------------------------|-------|

| hit 7                                                                                                  | JN0   |

|                                                                                                        | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0

#### 9.2.7 ADC REGISTER DEFINITIONS

The following registers are used to control the operation of the ADC.

#### REGISTER 9-1: ADCON0: A/D CONTROL REGISTER 0

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 |

|-------|-----|-------|-------|-------|-------|---------|-------|

| —     | —   | CHS3  | CHS2  | CHS1  | CHS0  | GO/DONE | ADON  |

| bit 7 |     |       |       |       |       |         | bit 0 |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-2 CHS<3:0>: Analog Channel Select bits

|       | 0000 = ANO                                                                                                                                                                                               |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 0001 = AN1                                                                                                                                                                                               |

|       | 0010 = AN2                                                                                                                                                                                               |

|       | 0011 = AN3                                                                                                                                                                                               |

|       | 0100 = AN4                                                                                                                                                                                               |

|       | 0101 = AN5                                                                                                                                                                                               |

|       | 0110 = AN6                                                                                                                                                                                               |

|       | 0111 = AN7                                                                                                                                                                                               |

|       | 1000 = AN8                                                                                                                                                                                               |

|       | 1001 = AN9                                                                                                                                                                                               |

|       | 1010 = AN10                                                                                                                                                                                              |

|       | 1011 = AN11                                                                                                                                                                                              |

|       | 1100 = AN12                                                                                                                                                                                              |

|       | 1101 = AN13                                                                                                                                                                                              |

|       | 1110 = Reserved                                                                                                                                                                                          |

|       | 1111 = Fixed Voltage Reference (FVREF)                                                                                                                                                                   |

| bit 1 | GO/DONE: A/D Conversion Status bit                                                                                                                                                                       |

|       | <ul> <li>1 = A/D conversion cycle in progress. Setting this bit starts an A/D conversion cycle.</li> <li>This bit is automatically cleared by hardware when the A/D conversion has completed.</li> </ul> |

|       | 0 = A/D conversion completed/not in progress                                                                                                                                                             |

| bit 0 | ADON: ADC Enable bit                                                                                                                                                                                     |

|       | 1 = ADC is enabled                                                                                                                                                                                       |

0 = ADC is disabled and consumes no operating current

|         |         |        |        |            |               |        | -       | -      | -                    | -                               |

|---------|---------|--------|--------|------------|---------------|--------|---------|--------|----------------------|---------------------------------|

| Name    | Bit 7   | Bit 6  | Bit 5  | Bit 4      | Bit 3         | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| ADCON0  | _       |        | CHS3   | CHS2       | CHS1          | CHS0   | GO/DONE | ADON   | 00 0000              | 00 0000                         |

| ADCON1  | _       | ADCS2  | ADCS1  | ADCS0      | _             | _      | ADREF1  | ADREF0 | -00000               | -00000                          |

| ANSELA  | _       | _      | ANSA5  | ANSA4      | ANSA3         | ANSA2  | ANSA1   | ANSA0  | 11 1111              | 11 1111                         |

| ANSELB  | _       | _      | ANSB5  | ANSB4      | ANSB3         | ANSB2  | ANSB1   | ANSB0  | 11 1111              | 11 1111                         |

| ANSELE  | _       | _      | _      | _          | _             | ANSE2  | ANSE1   | ANSE0  | 111                  | 111                             |

| ADRES   |         |        |        | A/D Result | Register Byte | Э      |         |        | xxxx xxxx            | uuuu uuuu                       |

| CCP2CON | _       | _      | DC2B1  | DC2B0      | CCP2M3        | CCP2M2 | CCP2M1  | CCP2M0 | 00 0000              | 00 0000                         |

| FVRCON  | FVRRDY  | FVREN  | _      | _          | _             | _      | ADFVR1  | ADFVR0 | q000                 | q000                            |

| INTCON  | GIE     | PEIE   | T0IE   | INTE       | RBIE          | T0IF   | INTF    | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1    | TMR1GIE | ADIE   | RCIE   | TXIE       | SSPIE         | CCP1IE | TMR2IE  | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1    | TMR1GIF | ADIF   | RCIF   | TXIF       | SSPIF         | CCP1IF | TMR2IF  | TMR1IF | 0000 0000            | 0000 0000                       |

| TRISA   | TRISA7  | TRISA6 | TRISA5 | TRISA4     | TRISA3        | TRISA2 | TRISA1  | TRISA0 | 1111 1111            | 1111 1111                       |

| TRISB   | TRISB7  | TRISB6 | TRISB5 | TRISB4     | TRISB3        | TRISB2 | TRISB1  | TRISB0 | 1111 1111            | 1111 1111                       |

| TRISE   | _       | _      | _      | _          | TRISE3        | TRISE2 | TRISE1  | TRISE0 | 1111                 | 1111                            |

|         |         |        |        |            |               |        |         |        |                      |                                 |

TABLE 9-2: SUMMARY OF ASSOCIATED ADC REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for ADC module.

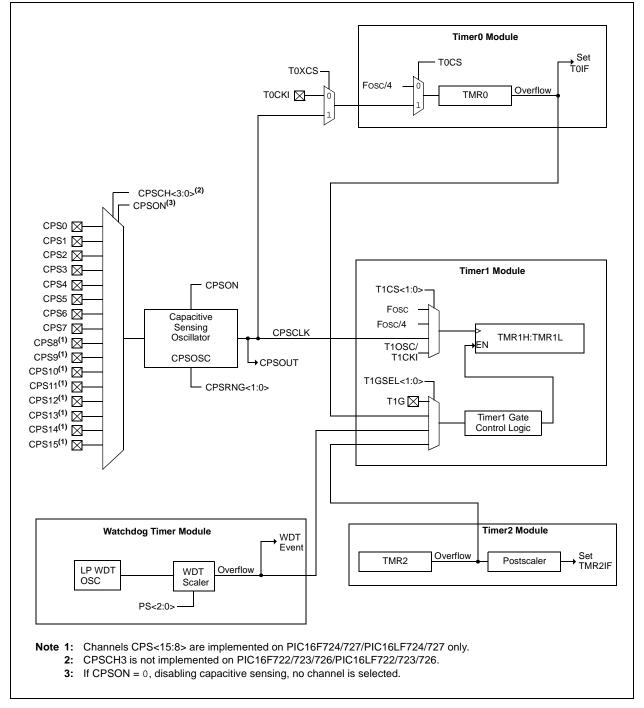

### 14.0 CAPACITIVE SENSING MODULE

The capacitive sensing module allows for an interaction with an end user without a mechanical interface. In a typical application, the capacitive sensing module is attached to a pad on a printed circuit board (PCB), which is electrically isolated from the end user. When the end user places their finger over the PCB pad, a capacitive load is added, causing a frequency shift in the capacitive sensing module. The capacitive sensing module requires software and at least one timer resource to determine the change in frequency. Key features of this module include:

- · Analog MUX for monitoring multiple inputs

- · Capacitive sensing oscillator

- Multiple timer resources

- Software control

- · Operation during Sleep

#### FIGURE 14-1: CAPACITIVE SENSING BLOCK DIAGRAM

#### REGISTER 14-2: CPSCON1: CAPACITIVE SENSING CONTROL REGISTER 1

| U-0          | U-0 | U-0            | U-0 | R/W-0 <sup>(2)</sup> | R/W-0            | R/W-0    | R/W-0  |

|--------------|-----|----------------|-----|----------------------|------------------|----------|--------|

| —            | —   | —              | _   | CPSCH3               | CPSCH2           | CPSCH1   | CPSCH0 |

| bit 7        |     |                |     |                      |                  |          | bit 0  |

| Legend:      |     |                |     |                      |                  |          |        |

|              |     |                |     |                      |                  |          |        |

| R = Readable | bit | W = Writable I | oit | U = Unimplen         | nented bit, read | l as '0' |        |

| bit 7-4 | Unimplemented: Read as '0'                         |

|---------|----------------------------------------------------|

| bit 3-0 | CPSCH<3:0>: Capacitive Sensing Channel Select bits |

|         | If CPSON = 0:                                      |

|         | These bits are ignored. No channel is selected.    |

|         | <u>If CPSON = 1</u> :                              |

|         | 0000 = channel 0, (CPS0)                           |

|         | 0001 = channel 1, (CPS1)                           |

|         | 0010 = channel 2, (CPS2)                           |

|         | 0011 = channel 3, (CPS3)                           |

|         | 0100 = channel 4, (CPS4)                           |

|         | 0101 = channel 5, (CPS5)                           |

|         | 0110 = channel 6, (CPS6)                           |

|         | 0111 =  channel 7, (CPS7)                          |

|         | 1000 = channel 8, (CPS8 <sup>(1)</sup> )           |

|         | 1001 = channel 9, (CPS9 <sup>(1)</sup> )           |

|         | 1010 = channel 10, (CPS10 <sup>(1)</sup> )         |

|         | 1011 = channel 11, (CPS11 <sup>(1)</sup> )         |

|         | 1100 =  channel 12, (CPS12(1))                     |

|         | $1101 = \text{ channel } 13, (CPS13^{(1)})$        |

|         | 1110 = channel 14, (CPS14(1))                      |

|         | 1111 = channel 15, (CPS15 <sup>(1)</sup> )         |

**Note 1:** These channels are not implemented on the PIC16F722/723/726/PIC16LF722/723/726.

2: This bit is not implemented on PIC16F722/723/726/PIC16LF722/723/726, Read as '0'

| TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH CAPACITIVE SENSIN | G |

|--------------------------------------------------------------------|---|

|--------------------------------------------------------------------|---|

| Name       | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|---------|---------|---------|---------|---------|--------|---------|---------|----------------------|---------------------------------|

| ANSELA     | _       | _       | ANSA5   | ANSA4   | ANSA3   | ANSA2  | ANSA1   | ANSA0   | 11 1111              | 11 1111                         |

| ANSELB     | _       | _       | ANSB5   | ANSB4   | ANSB3   | ANSB2  | ANSB1   | ANSB0   | 11 1111              | 11 1111                         |

| ANSELD     | ANSD7   | ANSD6   | ANSD5   | ANSD4   | ANSD3   | ANSD2  | ANSD1   | ANSD0   | 1111 1111            | 1111 1111                       |

| OPTION_REG | RBPU    | INTEDG  | TOCS    | T0SE    | PSA     | PS2    | PS1     | PS0     | 1111 1111            | 1111 1111                       |

| PIE1       | TMR1GIE | ADIE    | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIR1       | TMR1GIF | ADIF    | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| T1CON      | TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | _       | TMR10N  | 0000 00-0            | 0000 00-0                       |

| T2CON      |         | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

| TRISA      | TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2 | TRISA1  | TRISA0  | 1111 1111            | 1111 1111                       |

| TRISB      | TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2 | TRISB1  | TRISB0  | 1111 1111            | 1111 1111                       |

| TRISD      | TRISD7  | TRISD6  | TRISD5  | TRISD4  | TRISD3  | TRISD2 | TRISD1  | TRISD0  | 1111 1111            | 1111 1111                       |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the capacitive sensing module.

#### 16.1.2 AUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 16-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the AUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 16.1.2.1 Enabling the Receiver

The AUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other AUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the AUSART. Clearing the SYNC bit of the TXSTA register configures the AUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the AUSART and automatically configures the RX/DT I/O pin as an input.

| Note: | When the SPEN bit is set the TX/CK I/O         |

|-------|------------------------------------------------|

|       | pin is automatically configured as an          |

|       | output, regardless of the state of the         |

|       | corresponding TRIS bit and whether or          |

|       | not the AUSART transmitter is enabled.         |

|       | The PORT latch is disconnected from the        |

|       | output driver so it is not possible to use the |

|       | TX/CK pin as a general purpose output.         |

#### 16.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. Refer to Section 16.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the AUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

Note: If the receive FIFO is overrun, no additional characters will be received until the overrun condition is cleared. Refer to Section 16.1.2.5 "Receive Overrun Error" for more information on overrun errors.

#### 16.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the AUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- RCIE interrupt enable bit of the PIE1 register

- PEIE peripheral interrupt enable bit of the INTCON register

- GIE global interrupt enable bit of the INTCON register

The RCIF interrupt flag bit of the PIR1 register will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

|        |                |            |                             |                |                   | SYNC = 0,                   | BRGH =         | 0                  |                             |                |                    |                             |  |

|--------|----------------|------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|--------------------|-----------------------------|----------------|--------------------|-----------------------------|--|

| BAUD   | Foso           | ; = 20.00  | 0 MHz                       | Fosc           | Fosc = 18.432 MHz |                             |                | Fosc = 16.0000 MHz |                             |                | Fosc = 11.0592 MHz |                             |  |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |

| 300    |                | _          | _                           |                | _                 | _                           |                | —                  | —                           |                | _                  | _                           |  |

| 1200   | 1221           | 1.73       | 255                         | 1200           | 0.00              | 239                         | 1201           | 0.08               | 207                         | 1200           | 0.00               | 143                         |  |

| 2400   | 2404           | 0.16       | 129                         | 2400           | 0.00              | 119                         | 2403           | 0.16               | 103                         | 2400           | 0.00               | 71                          |  |

| 9600   | 9470           | -1.36      | 32                          | 9600           | 0.00              | 29                          | 9615           | 0.16               | 25                          | 9600           | 0.00               | 17                          |  |

| 10417  | 10417          | 0.00       | 29                          | 10286          | -1.26             | 27                          | 10416          | -0.01              | 23                          | 10165          | -2.42              | 16                          |  |

| 19.2k  | 19.53k         | 1.73       | 15                          | 19.20k         | 0.00              | 14                          | 19.23k         | 0.16               | 12                          | 19.20k         | 0.00               | 8                           |  |

| 57.6k  | _              | —          | _                           | 57.60k         | 0.00              | 7                           | —              | —                  | _                           | 57.60k         | 0.00               | 2                           |  |

| 115.2k | —              | _          | —                           | _              | _                 | —                           | _              | —                  | —                           | _              | —                  | —                           |  |

#### TABLE 16-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        |                  | SYNC = 0, BRGH = 0 |                             |                  |            |                             |                   |            |                             |                |                  |                             |  |  |  |

|--------|------------------|--------------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|----------------|------------------|-----------------------------|--|--|--|

| BAUD   | Fosc = 8.000 MHz |                    |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fos            | Fosc = 1.000 MHz |                             |  |  |  |

| RATE   | Actual<br>Rate   | %<br>Error         | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |  |  |

| 300    | _                | _                  | _                           | 300              | 0.16       | 207                         | 300               | 0.00       | 191                         | 300            | 0.16             | 51                          |  |  |  |

| 1200   | 1202             | 0.16               | 103                         | 1202             | 0.16       | 51                          | 1200              | 0.00       | 47                          | 1202           | 0.16             | 12                          |  |  |  |

| 2400   | 2404             | 0.16               | 51                          | 2404             | 0.16       | 25                          | 2400              | 0.00       | 23                          | —              | _                | _                           |  |  |  |

| 9600   | 9615             | 0.16               | 12                          | _                | _          | _                           | 9600              | 0.00       | 5                           | —              | _                | _                           |  |  |  |

| 10417  | 10417            | 0.00               | 11                          | 10417            | 0.00       | 5                           | —                 | _          | _                           | —              | _                | _                           |  |  |  |

| 19.2k  | _                | _                  | _                           | —                | _          | _                           | 19.20k            | 0.00       | 2                           | —              | _                | _                           |  |  |  |

| 57.6k  | —                | _                  | —                           | —                | _          | —                           | 57.60k            | 0.00       | 0                           | —              | _                | —                           |  |  |  |

| 115.2k |                  | —                  | —                           |                  | —          | —                           |                   | _          | —                           |                | —                | —                           |  |  |  |

|        |                   |            |                             |                |                   | SYNC = 0,                   | BRGH = 2       | L                  |                             |                |                    |                             |  |

|--------|-------------------|------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|--------------------|-----------------------------|----------------|--------------------|-----------------------------|--|

| BAUD   | Fosc = 20.000 MHz |            |                             | Fosc           | Fosc = 18.432 MHz |                             |                | Fosc = 16.0000 MHz |                             |                | Fosc = 11.0592 MHz |                             |  |

| RATE   | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |

| 300    | —                 |            | _                           |                | _                 | _                           | _              | —                  | _                           | —              | —                  | —                           |  |

| 1200   | —                 | —          | —                           | —              | —                 | —                           | —              | —                  | —                           | —              | —                  | —                           |  |

| 2400   | —                 | _          | _                           | _              | _                 | _                           | _              | _                  | _                           | —              | —                  | _                           |  |

| 9600   | 9615              | 0.16       | 129                         | 9600           | 0.00              | 119                         | 9615           | 0.16               | 103                         | 9600           | 0.00               | 71                          |  |

| 10417  | 10417             | 0.00       | 119                         | 10378          | -0.37             | 110                         | 10417          | 0.00               | 95                          | 10473          | 0.53               | 65                          |  |

| 19.2k  | 19.23k            | 0.16       | 64                          | 19.20k         | 0.00              | 59                          | 19.23k         | 0.16               | 51                          | 19.20k         | 0.00               | 35                          |  |

| 57.6k  | 56.82k            | -1.36      | 21                          | 57.60k         | 0.00              | 19                          | 58.8k          | 2.12               | 16                          | 57.60k         | 0.00               | 11                          |  |

| 115.2k | 113.64k           | -1.36      | 10                          | 115.2k         | 0.00              | 9                           | _              | _                  | _                           | 115.2k         | 0.00               | 5                           |  |

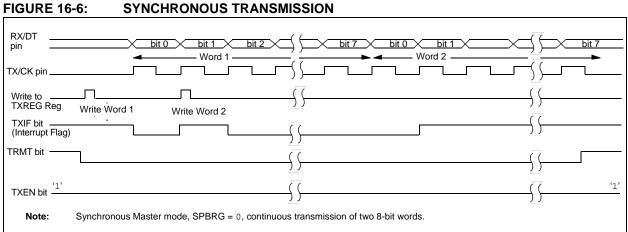

#### 16.3 AUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The AUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 16.3.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the AUSART for Synchronous Master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the AUSART.

#### 16.3.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/ CK line. The TX/CK pin output driver is automatically enabled when the AUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

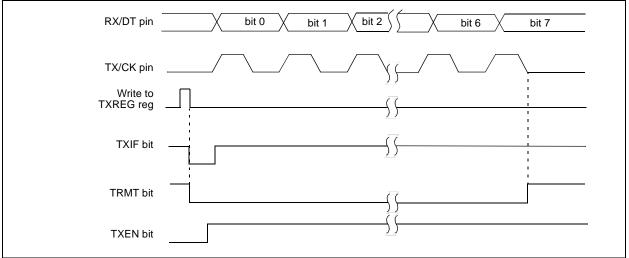

#### 16.3.1.2 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the AUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

Note: The TSR register is not mapped in data memory, so it is not available to the user.

16.3.1.3 Synchronous Master Transmission Setup:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (refer to Section 16.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

### FIGURE 16-7: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

#### TABLE 16-6: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name   | Bit 7    | Bit 6       | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|-------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE        | TOIE       | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE  | ADIE        | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF  | ADIF        | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN     | RX9         | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7     | BRG6        | BRG5       | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7   | TRISC6      | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXREG  | AUSART T | ransmit Dat | a Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA  | CSRC     | TX9         | TXEN       | SYNC   |        | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Transmission.

# PIC16(L)F722/3/4/6/7

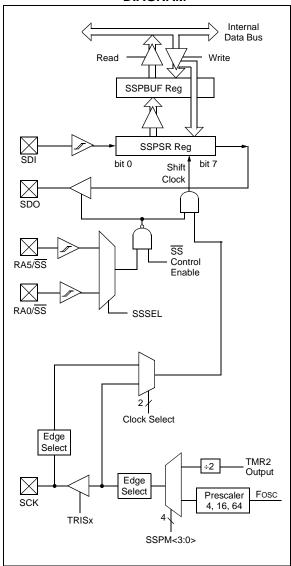

FIGURE 17-2: SPI MODE BLOCK DIAGRAM

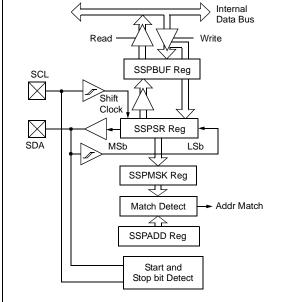

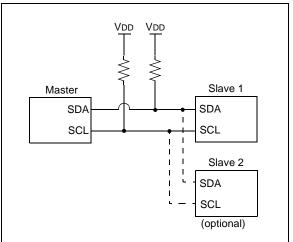

### 17.2 I<sup>2</sup>C Mode

The SSP module, in  $I^2C$  mode, implements all slave functions, except general call support. It provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the  $I^2C$  Standard mode specifications:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- Start and Stop bit interrupts enabled to support firmware Master mode

- Address masking

Two pins are used for data transfer; the SCL pin (clock line) and the SDA pin (data line). The user must configure the two pin's data direction bits as inputs in the appropriate TRIS register. Upon enabling  $I^2C$  mode, the  $I^2C$  slew rate limiters in the I/O pads are controlled by the SMP bit of SSPSTAT register. The SSP module functions are enabled by setting the SSPEN bit of SSPCON register.

Data is sampled on the rising edge and shifted out on the falling edge of the clock. This ensures that the SDA signal is valid during the SCL high time. The SCL clock input must have minimum high and low times for proper operation. Refer to **Section 23.0** "**Electrical Specifications**".

# FIGURE 17-7: I<sup>2</sup>C MODE BLOCK DIAGRAM

# FIGURE 17-8: TYPICAL I<sup>2</sup>C

#### CONNECTIONS

The SSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. They are:

- SSP Control (SSPCON) register

- SSP Status (SSPSTAT) register

- Serial Receive/Transmit Buffer (SSPBUF) register

- SSP Shift Register (SSPSR), not directly accessible

- SSP Address (SSPADD) register

- SSP Address Mask (SSPMSK) register

#### 17.2.1 HARDWARE SETUP

Selection of  $I^2C$  mode, with the SSPEN bit of the SSPCON register set, forces the SCL and SDA pins to be open drain, provided these pins are programmed as inputs by setting the appropriate TRISC bits. The SSP module will override the input state with the output data, when required, such as for Acknowledge and slave-transmitter sequences.

**Note:** Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module

#### REGISTER 17-5: SSPMSK: SSP MASK REGISTER

| R/W-1           | R/W-1 | R/W-1            | R/W-1 | R/W-1              | R/W-1                    | R/W-1 | R/W-1 |  |  |

|-----------------|-------|------------------|-------|--------------------|--------------------------|-------|-------|--|--|

| MSK7            | MSK6  | MSK5             | MSK4  | MSK3               | MSK2                     | MSK1  | MSK0  |  |  |

| bit 7           |       |                  |       |                    | -                        |       | bit   |  |  |

| Legend:         |       |                  |       |                    |                          |       |       |  |  |

| R = Readable    | bit   | W = Writable bit | t     | U = Unimpleme      | ented bit, read a        | s 'O' |       |  |  |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is clear | eared x = Bit is unknown |       |       |  |  |

|       | 0 = 110 received address bit instructused to detect i C address match                              |

|-------|----------------------------------------------------------------------------------------------------|

| bit 0 | MSK<0>: Mask bit for I <sup>2</sup> C Slave Mode, 10-bit Address                                   |

|       | I <sup>2</sup> C Slave Mode, 10-bit Address (SSPM<3:0> = 0111):                                    |

|       | 1 = The received address bit '0' is compared to SSPADD<0> to detect I <sup>2</sup> C address match |

|       | $0 =$ The received address bit '0' is not used to detect $1^2$ C address match                     |

|       | All other SSP modes: this bit has no effect.                                                       |

|       |                                                                                                    |

# REGISTER 17-6: SSPADD: SSP I<sup>2</sup>C ADDRESS REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ADD7  | ADD6  | ADD5  | ADD4  | ADD3  | ADD2  | ADD1  | ADD0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

|       |       |       |       |       |       |       |       |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | ʻ0'                |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-0 ADD<7:0>: Address bits Received address

### TABLE 17-7: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

| Name                  | Bit 7                                                                 | Bit 6              | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|-----------------------------------------------------------------------|--------------------|--------|--------|--------|--------|--------|-----------|----------------------|---------------------------------|

| INTCON                | GIE                                                                   | PEIE               | TOIE   | INTE   | RBIE   | TOIF   | INTF   | RBIF      | x000 0000x           | 0000 000u                       |

| PIR1                  | TMR1GIF                                                               | ADIF               | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF    | 0000 0000            | 0000 0000                       |

| PIE1                  | TMR1GIE                                                               | ADIE               | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE    | 0000 0000            | 0000 0000                       |

| SSPBUF                | Synchronous Serial Port Receive Buffer/Transmit Register              |                    |        |        |        |        |        | xxxx xxxx | uuuu uuuu            |                                 |

| SSPADD                | Synchronous Serial Port (I <sup>2</sup> C mode) Address Register      |                    |        |        |        |        |        |           | 0000 0000            | 0000 0000                       |

| SSPCON                | WCOL                                                                  | SSPOV              | SSPEN  | CKP    | SSPM3  | SSPM2  | SSPM1  | SSPM0     | 0000 0000            | 0000 0000                       |

| SSPMSK <sup>(2)</sup> | Synchronous Serial Port (I <sup>2</sup> C mode) Address Mask Register |                    |        |        |        |        |        | 1111 1111 | 1111 1111            |                                 |

| SSPSTAT               | SMP <sup>(1)</sup>                                                    | CKE <sup>(1)</sup> | D/A    | Р      | S      | R/W    | UA     | BF        | 0000 0000            | 0000 0000                       |

| TRISC                 | TRISC7                                                                | TRISC6             | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0    | 1111 1111            | 1111 1111                       |

| $\mathbf{L}$          |                                                                       |                    |        |        |        |        |        |           |                      |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in I<sup>2</sup>C mode.

**Note 1:** Maintain these bits clear in  $I^2C$  mode.

**2:** Accessible only when SSPM<3:0> = 1001.

### 23.4 DC Characteristics: PIC16(L)F722/3/4/6/7-I/E (Continued)

|                         |        | HARACTERISTICS                                   | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |      |       |                                                                         |  |  |

|-------------------------|--------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------------------------------------------------------------------------|--|--|

| Param<br>No.            | Sym.   | Characteristic                                   | Min.                                                                                                                                                                                           | Тур† | Max. | Units | Conditions                                                              |  |  |

| D130                    | Eр     | Cell Endurance                                   | 100                                                                                                                                                                                            | 1k   | —    | E/W   | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

| D131                    |        | VDD for Read                                     | Vmin                                                                                                                                                                                           | —    | _    | V     |                                                                         |  |  |

|                         |        | Voltage on MCLR/VPP during<br>Erase/Program      | 8.0                                                                                                                                                                                            | _    | 9.0  | V     | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

|                         |        | VDD for Bulk Erase                               | 2.7                                                                                                                                                                                            | 3    | —    | V     | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

| D132 VPEW               | VPEW   | VDD for Write or Row Erase                       | 2.7                                                                                                                                                                                            | _    | —    | V     | VMIN = Minimum operating voltage<br>VMAX = Maximum operating<br>voltage |  |  |

|                         | IPPPGM | Current on MCLR/VPP during<br>Erase/Write        | —                                                                                                                                                                                              | -    | 5.0  | mA    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

|                         | IDDPGM | Current on VDD during Erase/<br>Write            | —                                                                                                                                                                                              |      | 5.0  | mA    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

| D133                    | TPEW   | Erase/Write cycle time                           | -                                                                                                                                                                                              |      | 2.8  | ms    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

| D134                    | TRETD  | Characteristic Retention                         | 40                                                                                                                                                                                             | —    | —    | Year  | Provided no other specifications are violated                           |  |  |

| VCAP Capacitor Charging |        |                                                  |                                                                                                                                                                                                |      |      |       | •                                                                       |  |  |

| D135                    |        | Charging current                                 | —                                                                                                                                                                                              | 200  | _    | μΑ    |                                                                         |  |  |

| D135A                   |        | Source/sink capability when<br>charging complete | —                                                                                                                                                                                              | 0.0  | —    | mA    |                                                                         |  |  |

Legend: TBD = To Be Determined

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

**3:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: Including OSC2 in CLKOUT mode.

# PIC16(L)F722/3/4/6/7

# THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Micro-chip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://www.microchip.com/support

# PIC16(L)F722/3/4/6/7

NOTES: