Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                |                                                                            |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf722t-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

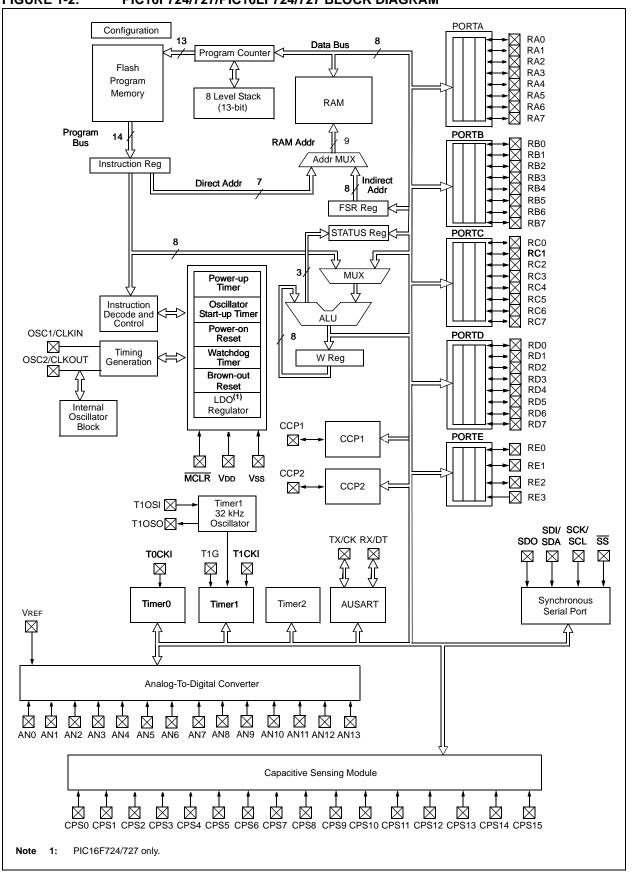

FIGURE 1-2: PIC16F724/727/PIC16LF724/727 BLOCK DIAGRAM

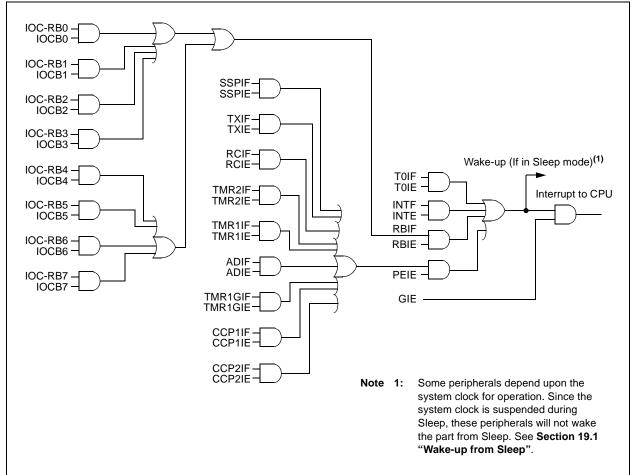

## 4.0 INTERRUPTS

The PIC16(L)F722/3/4/6/7 device family features an interruptible core, allowing certain events to preempt normal program flow. An Interrupt Service Routine (ISR) is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

The PIC16(L)F722/3/4/6/7 device family has 12 interrupt sources, differentiated by corresponding interrupt enable and flag bits:

- Timer0 Overflow Interrupt

- External Edge Detect on INT Pin Interrupt

- PORTB Change Interrupt

- Timer1 Gate Interrupt

- A/D Conversion Complete Interrupt

- AUSART Receive Interrupt

- AUSART Transmit Interrupt

- SSP Event Interrupt

- CCP1 Event Interrupt

- · Timer2 Match with PR2 Interrupt

- Timer1 Overflow Interrupt

- CCP2 Event Interrupt

A block diagram of the interrupt logic is shown in Figure 4-1.

## FIGURE 4-1: INTERRUPT LOGIC

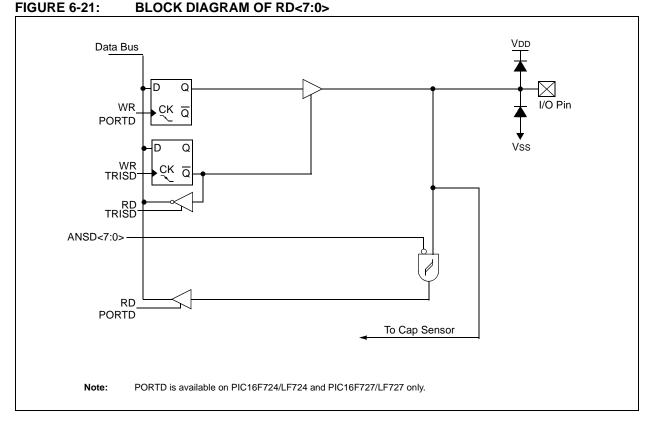

## 6.5.6 RD4/CPS12

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### 6.5.7 RD5/CPS13

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- a capacitive sensing input

## 6.5.8 RD6/CPS14

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### 6.5.9 RD7/CPS15

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

| TABLE 6-4: SUMM | IARY OF REGISTERS ASSOCIATED WITH PORTD <sup>(1)</sup> |

|-----------------|--------------------------------------------------------|

|-----------------|--------------------------------------------------------|

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|--------|--------|--------|---------|---------|--------|--------|----------------------|---------------------------------|

| ANSELD  | ANSD7  | ANSD6  | ANSD5  | ANSD4  | ANSD3   | ANSD2   | ANSD1  | ANSD0  | 1111 1111            | 1111 1111                       |

| CPSCON0 | CPSON  | —      | —      | —      | CPSRNG1 | CPSRNG0 | CPSOUT | TOXCS  | 0 0000               | 0 0000                          |

| CPSCON1 |        | —      | —      | _      | CPSCH3  | CPSCH2  | CPSCH1 | CPSCH0 | 0000                 | 0000                            |

| PORTD   | RD7    | RD6    | RD5    | RD4    | RD3     | RD2     | RD1    | RD0    | XXXX XXXX            | xxxx xxxx                       |

| TRISD   | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3  | TRISD2  | TRISD1 | TRISD0 | 1111 1111            | 1111 1111                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTD.**Note 1:**These registers are not implemented on the PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'.

#### © 2007-2015 Microchip Technology Inc.

#### DS40001341F-page 79

## 6.6.1 RE0/AN5<sup>(1)</sup>

Figure 6-22 shows the diagram for this pin. This pin is configurable to function as one of the following:

• a general purpose I/O

• an analog input for the ADC

| Note 1: | RE0/AN5 is available on |

|---------|-------------------------|

|         | PIC16F724/LF724 and     |

|         | PIC16F727/LF727 only.   |

## 6.6.2 RE1/AN6<sup>(1)</sup>

Figure 6-22 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

| Note 1: | RE0/AN5 is available on |

|---------|-------------------------|

|         | PIC16F724/LF724 and     |

|         | PIC16F727/LF727 only.   |

#### 6.6.3 RE2/AN7<sup>(1)</sup>

Figure 6-22 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

Note 1: RE0/AN5 is available on PIC16F724/LF724 and PIC16F727/LF727 only.

#### 6.6.4 RE3/MCLR/VPP

Figure 6-23 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose input

- as Master Clear Reset with weak pull-up

- · a programming voltage reference input

## 8.0 DEVICE CONFIGURATION

Device Configuration consists of Configuration Word 1 and Configuration Word 2 registers, Code Protection and Device ID.

## 8.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 register at 2007h and Configuration Word 2 register at 2008h. These registers are only accessible during programming.

#### REGISTER 8-1: CONFIG1: CONFIGURATION WORD REGISTER 1

|        |   | R/P-1 | R/P-1 | U-1 <sup>(4)</sup> | R/P-1 | R/P-1  | R/P-1  |

|--------|---|-------|-------|--------------------|-------|--------|--------|

| —      | _ | DEBUG | PLLEN | _                  | BORV  | BOREN1 | BOREN0 |

| bit 15 |   |       |       |                    |       |        | bit 8  |

| U-1 <sup>(4)</sup> | R/P-1 |

|--------------------|-------|-------|-------|-------|-------|-------|-------|

| —                  | CP    | MCLRE | PWRTE | WDTE  | FOSC2 | FOSC1 | FOSC0 |

| bit 7              |       |       |       |       |       |       | bit 0 |

| Legend:           | P = Programmable bit |                             |                    |

|-------------------|----------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared        | x = Bit is unknown |

| bit 13              | <b>DEBUG:</b> In-Circuit Debugger Mode bit<br>1 = In-Circuit Debugger disabled, RB6/ICSPCLK and RB7/ICSPDAT are general purpose I/O pins<br>0 = In-Circuit Debugger enabled, RB6/ICSPCLK and RB7/ICSPDAT are dedicated to the debugger                            |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bit 12              | PLLEN: INTOSC PLL Enable bit<br>0 = INTOSC Frequency is 500 kHz<br>1 = INTOSC Frequency is 16 MHz (32x)                                                                                                                                                           |  |

| bit 11              | Unimplemented: Read as '1'                                                                                                                                                                                                                                        |  |

| bit 10              | <b>BORV:</b> Brown-out Reset Voltage selection bit<br>0 = Brown-out Reset Voltage (VBOR) set to 2.5 V nominal<br>1 = Brown-out Reset Voltage (VBOR) set to 1.9 V nominal                                                                                          |  |

| bit 9-8             | <b>BOREN&lt;1:0&gt;:</b> Brown-out Reset Selection bits <sup>(1)</sup><br>0x = BOR disabled (Preconditioned State)<br>10 = BOR enabled during operation and disabled in Sleep<br>11 = BOR enabled                                                                 |  |

| bit 7               | Unimplemented: Read as '1'                                                                                                                                                                                                                                        |  |

| bit 6               | <b>CP</b> : Code Protection bit <sup>(2)</sup><br>1 = Program memory code protection is disabled<br>0 = Program memory code protection is enabled                                                                                                                 |  |

| bit 5               | MCLRE: <u>RE3/MCLR</u> pin function select bit <sup>(3)</sup><br>1 = RE3/ <u>MCLR</u> pin function is MCLR<br>0 = RE3/MCLR pin function is digital input, MCLR internally tied to VDD                                                                             |  |

| Note 1:<br>2:<br>3: | Enabling Brown-out Reset does not automatically enable Power-up Timer.<br>The entire program memory will be erased when the code protection is turned off.<br>When $\overline{MCLR}$ is asserted in INTOSC or RC mode, the internal clock oscillator is disabled. |  |

**4:** MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

#### 9.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

- **Note 1:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

- **2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the GIE and PEIE bits of the INTCON register must be disabled. If the GIE and PEIE bits of the INT-CON register are enabled, execution will switch to the Interrupt Service Routine.

Please refer to **Section 9.1.5** "Interrupts" for more information.

## 9.2 ADC Operation

## 9.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

Note: The GO/DONE bit should not be set in the same instruction that turns on the ADC. Refer to Section 9.2.6 "A/D Conversion Procedure".

## 9.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRES register with new conversion result

## 9.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRES register will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

| Note: | A device Reset forces all registers to their |

|-------|----------------------------------------------|

|       | Reset state. Thus, the ADC module is         |

|       | turned off and any pending conversion is     |

|       | terminated.                                  |

## 9.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

## 9.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCP module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 15.0 "Capture/Compare/PWM (CCP) Module" for more information.

## 12.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 Gate circuitry. This is also referred to as Timer1 Gate Count Enable.

Timer1 Gate can also be driven by multiple selectable sources.

#### 12.6.1 TIMER1 GATE COUNT ENABLE

The Timer1 Gate is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate is configured using the T1GPOL bit of the T1GCON register.

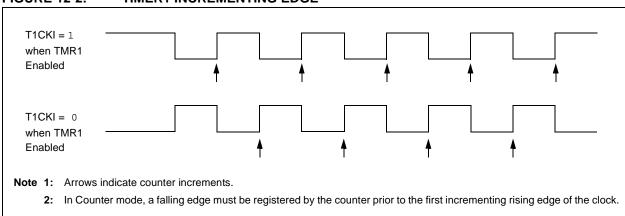

When Timer1 Gate (T1G) input is active, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate input is inactive, no incrementing will occur and Timer1 will hold the current count. See Figure 12-3 for timing details.

#### TABLE 12-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

#### 12.6.2 TIMER1 GATE SOURCE SELECTION

The Timer1 Gate source can be selected from one of four different sources. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

#### TABLE 12-4: TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                    |  |  |  |  |

|-------|-----------------------------------------------------------------------|--|--|--|--|

| 00    | Timer1 Gate Pin                                                       |  |  |  |  |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)               |  |  |  |  |

| 10    | Timer2 match PR2<br>(TMR2 increments to match PR2)                    |  |  |  |  |

| 11    | Count Enabled by WDT Overflow<br>(Watchdog Time-out interval expired) |  |  |  |  |

#### 12.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 Gate Control. It can be used to supply an external source to the Timer1 Gate circuitry.

#### 12.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 Gate circuitry.

#### 12.6.2.3 Timer2 Match Gate Operation

The TMR2 register will increment until it matches the value in the PR2 register. On the very next increment cycle, TMR2 will be reset to 00h. When this Reset occurs, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 Gate circuitry.

#### 12.6.2.4 Watchdog Overflow Gate Operation

The Watchdog Timer oscillator, prescaler and counter will be automatically turned on when TMR1GE = 1 and T1GSS selects the WDT as a gate source for Timer1 (T1GSS = 11). TMR1ON does not factor into the oscillator, prescaler and counter enable. See Table 12-5.

The PSA and PS bits of the OPTION register still control what time-out interval is selected. Changing the prescaler during operation may result in a spurious capture.

Enabling the Watchdog Timer oscillator does not automatically enable a Watchdog Reset or Wake-up from Sleep upon counter overflow.

| Note: | When using the WDT as a gate source for<br>Timer1, operations that clear the Watchdog |

|-------|---------------------------------------------------------------------------------------|

|       |                                                                                       |

|       | Timer (CLRWDT, SLEEP instructions) will                                               |

|       | affect the time interval being measured for                                           |

|       | capacitive sensing. This includes waking                                              |

|       | from Sleep. All other interrupts that might                                           |

|       | wake the device from Sleep should be                                                  |

|       | disabled to prevent them from disturbing                                              |

|       | the measurement period.                                                               |

As the gate signal coming from the WDT counter will generate different pulse widths depending on if the WDT is enabled, when the CLRWDT instruction is executed, and so on, Toggle mode must be used. A specific sequence is required to put the device into the correct state to capture the next WDT counter interval.

## 12.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR1ON bit of the T1CON register

- TMR1IE bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

## 12.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- PEIE bit of the INTCON register must be set

- TISYNC bit of the T1CON register must be set

- TMR1CS bits of the T1CON register must be configured

- T1OSCEN bit of the T1CON register must be configured

- TMR1GIE bit of the T1GCON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine (0004h).

## 12.9 CCP Capture/Compare Time Base

The CCP module uses the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Special Event Trigger.

For more information, see Section 15.0 "Capture/Compare/PWM (CCP) Module".

## 12.10 CCP Special Event Trigger

When the CCP is configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair becomes the period register for Timer1.

Timer1 should be synchronized to the Fosc/4 to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the CCP, the write will take precedence.

For more information, see Section 9.2.5 "Special Event Trigger".

## FIGURE 12-2: TIMER1 INCREMENTING EDGE

| R/W-0                                                                                                                                                                                                                   | U-0                                                                                                                                                                                                                                                                                                                                                                                                                       | U-0              | U-0 | R/W-0            | R/W-0            | R-0             | R/W-0 |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|------------------|------------------|-----------------|-------|--|

| CPSON                                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                                                                                         | —                | —   | CPSRNG1          | CPSRNG0          | CPSOUT          | TOXCS |  |

| bit 7                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |     |                  |                  |                 | bit 0 |  |

|                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |     |                  |                  |                 |       |  |

| Legend:                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |     |                  |                  |                 |       |  |

| R = Readable I                                                                                                                                                                                                          | bit                                                                                                                                                                                                                                                                                                                                                                                                                       | W = Writable I   | bit | U = Unimpler     | mented bit, read | l as '0'        |       |  |

| -n = Value at P                                                                                                                                                                                                         | OR                                                                                                                                                                                                                                                                                                                                                                                                                        | '1' = Bit is set |     | '0' = Bit is cle | ared             | x = Bit is unkn | own   |  |

| <ul> <li>bit 7</li> <li>CPSON: Capacitive Sensing Module Enable bit</li> <li>1 = Capacitive sensing module is operating</li> <li>0 = Capacitive sensing module is shut off and consumes no operating current</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |     |                  |                  |                 |       |  |

| bit 6-4                                                                                                                                                                                                                 | Unimplement                                                                                                                                                                                                                                                                                                                                                                                                               | ted: Read as 'd  | )'  |                  |                  |                 |       |  |

| bit 3-2                                                                                                                                                                                                                 | <b>CPSRNG&lt;1:0&gt;:</b> Capacitive Sensing Oscillator Range bits<br>00 = Oscillator is Off.<br>01 = Oscillator is in low range. Charge/discharge current is nominally 0.1 μA.<br>10 = Oscillator is in medium range. Charge/discharge current is nominally 1.2 μA.<br>11 = Oscillator is in high range. Charge/discharge current is nominally 18 μA.                                                                    |                  |     |                  |                  |                 |       |  |

| bit 1                                                                                                                                                                                                                   | <b>CPSOUT:</b> Capacitive Sensing Oscillator Status bit<br>1 = Oscillator is sourcing current (Current flowing out the pin)<br>0 = Oscillator is sinking current (Current flowing into the pin)                                                                                                                                                                                                                           |                  |     |                  |                  |                 |       |  |

| bit 0                                                                                                                                                                                                                   | <b>TOXCS:</b> Timer0 External Clock Source Select bit<br>$\frac{\text{If TOCS} = 1}{\text{The T0XCS bit controls which clock external to the core/Timer0 module supplies Timer0:}$ $1 = \text{Timer0 Clock Source is the capacitive sensing oscillator}$ $0 = \text{Timer0 Clock Source is the T0CKI pin}$ $\frac{\text{If T0CS} = 0}{\text{Timer0 clock source is controlled by the core/Timer0 module and is Fosc/4.}}$ |                  |     |                  |                  |                 |       |  |

## REGISTER 14-1: CPSCON0: CAPACITIVE SENSING CONTROL REGISTER 0

| Name    | Bit 7                                                                            | Bit 6       | Bit 5         | Bit 4   | Bit 3                   | Bit 2  | Bit 1  | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|----------------------------------------------------------------------------------|-------------|---------------|---------|-------------------------|--------|--------|---------|----------------------|---------------------------------|

| ANSELB  | —                                                                                | —           | ANSB5         | ANSB4   | ANSB3                   | ANSB2  | ANSB1  | ANSB0   | 11 1111              | 11 1111                         |

| APFCON  | _                                                                                | _           | _             | _       | _                       | _      | SSSEL  | CCP2SEL | 00                   | 00                              |

| CCP1CON | _                                                                                | _           | DC1B1         | DC1B0   | CCP1M3                  | CCP1M2 | CCP1M1 | CCP1M0  | 00 0000              | 00 0000                         |

| CCP2CON | _                                                                                | _           | DC2B1         | DC2B0   | CCP2M3                  | CCP2M2 | CCP2M1 | CCP2M0  | 00 0000              | 00 0000                         |

| CCPRxL  | Capture/Con                                                                      | npare/PWM R | egister X Lov | v Byte  |                         |        |        |         | XXXX XXXX            | uuuu uuuu                       |

| CCPRxH  | Capture/Con                                                                      | npare/PWM R | egister X Hig | h Byte  |                         |        |        |         | XXXX XXXX            | uuuu uuuu                       |

| INTCON  | GIE                                                                              | PEIE        | TOIE          | INTE    | RBIE                    | T0IF   | INTF   | RBIF    | 0000 000x            | 0000 000x                       |

| PIE1    | TMR1GIE                                                                          | ADIE        | RCIE          | TXIE    | SSPIE                   | CCP1IE | TMR2IE | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIE2    | —                                                                                | _           |               |         | —                       |        |        | CCP2IE  | 0                    | 0                               |

| PIR1    | TMR1GIF                                                                          | ADIF        | RCIF          | TXIF    | SSPIF                   | CCP1IF | TMR2IF | TMR1IF  | 0000 0000            | 0000 0000                       |

| PIR2    | —                                                                                | —           | -             | -       | —                       | -      | —      | CCP2IF  | 0                    | 0                               |

| T1CON   | TMR1CS1                                                                          | TMR1CS0     | T1CKPS1       | T1CKPS0 | T1OSCEN                 | T1SYNC | —      | TMR10N  | 0000 00-0            | uuuu uu-u                       |

| T1GCON  | TMR1GE                                                                           | T1GPOL      | T1GTM         | T1GSPM  | T <u>1GGO</u> /<br>DONE | T1GVAL | T1GSS1 | T1GSS0  | 00x0 0x00            | 0000 0x00                       |

| TMR1L   | IR1L Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |             |               |         |                         |        |        |         |                      | uuuu uuuu                       |

| TMR1H   | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register       |             |               |         |                         |        |        |         | xxxx xxxx            | uuuu uuuu                       |

| TRISB   | TRISB7                                                                           | TRISB6      | TRISB5        | TRISB4  | TRISB3                  | TRISB2 | TRISB1 | TRISB0  | 1111 1111            | 1111 1111                       |

| TRISC   | TRISC7                                                                           | TRISC6      | TRISC5        | TRISC4  | TRISC3                  | TRISC2 | TRISC1 | TRISC0  | 1111 1111            | 1111 1111                       |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Capture.

| Name    | Bit 7       | Bit 6          | Bit 5       | Bit 4        | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on all<br>other Resets |

|---------|-------------|----------------|-------------|--------------|----------|--------|---------|---------|----------------------|------------------------------|

| ANSELA  | —           | —              | ANSA5       | ANSA4        | ANSA3    | ANSA2  | ANSA1   | ANSA0   | 11 1111              | 11 1111                      |

| APFCON  | —           | —              | _           | —            | _        | _      | SSSEL   | CCP2SEL | 00                   | 00                           |

| INTCON  | GIE         | PEIE           | T0IE        | INTE         | RBIE     | T0IF   | INTF    | RBIF    | 0000 000x            | 0000 000x                    |

| PIE1    | TMR1GIE     | ADIE           | RCIE        | TXIE         | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                    |

| PIR1    | TMR1GIF     | ADIF           | RCIF        | TXIF         | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                    |

| PR2     | Timer2 Peri | iod Register   | •           | •            |          |        |         | •       | 1111 1111            | 1111 1111                    |

| SSPBUF  | Synchronou  | us Serial Port | Receive But | fer/Transmit | Register |        |         |         | XXXX XXXX            | uuuu uuuu                    |

| SSPCON  | WCOL        | SSPOV          | SSPEN       | CKP          | SSPM3    | SSPM2  | SSPM1   | SSPM0   | 0000 0000            | 0000 0000                    |

| SSPSTAT | SMP         | CKE            | D/A         | Р            | S        | R/W    | UA      | BF      | 0000 0000            | 0000 0000                    |

| TRISA   | TRISA7      | TRISA6         | TRISA5      | TRISA4       | TRISA3   | TRISA2 | TRISA1  | TRISA0  | 1111 1111            | 1111 1111                    |

| TRISC   | TRISC7      | TRISC6         | TRISC5      | TRISC4       | TRISC3   | TRISC2 | TRISC1  | TRISC0  | 1111 1111            | 1111 1111                    |

| T2CON   |             | TOUTPS3        | TOUTPS2     | TOUTPS1      | TOUTPS0  | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                    |

## TABLE 17-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode.

## 17.2.7 CLOCK STRETCHING

During any SCL low phase, any device on the  $I^2C$  bus may hold the SCL line low and delay, or pause, the transmission of data. This "stretching" of a transmission allows devices to slow down communication on the bus. The SCL line must be constantly sampled by the master to ensure that all devices on the bus have released SCL for more data.

Stretching usually occurs after an ACK bit of a transmission, delaying the first bit of the next byte. The SSP module hardware automatically stretches for two conditions:

- After a 10-bit address byte is received (update SSPADD register)

- Anytime the CKP bit of the SSPCON register is cleared by hardware

The module will hold SCL low until the CKP bit is set. This allows the user slave software to update SSPBUF with data that may not be readily available. In 10-bit addressing modes, the SSPADD register must be updated after receiving the first and second address bytes. The SSP module will hold the SCL line low until the SSPADD has a byte written to it. The UA bit of the SSPSTAT register will be set, along with SSPIF, indicating an address update is needed.

#### 17.2.8 FIRMWARE MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits of the SSPSTAT register are cleared from a Reset or when the SSP module is disabled (SSPEN cleared). The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set or the bus is Idle and both the S and P bits are clear.

In Firmware Master mode, the SCL and SDA lines are manipulated by setting/clearing the corresponding TRIS bit(s). The output level is always low, irrespective of the value(s) in the corresponding PORT register bit(s). When transmitting a '1', the TRIS bit must be set (input) and a '0', the TRIS bit must be clear (output).

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt will occur if enabled):

- Start condition

- Stop condition

- Data transfer byte transmitted/received

Firmware Master Mode of operation can be done with either the Slave mode Idle (SSPM<3:0 > = 1011), or with either of the Slave modes in which interrupts are enabled. When both master and slave functionality is enabled, the software needs to differentiate the source(s) of the interrupt. Refer to Application Note AN554, Software Implementation of  $l^2 C^{TM}$  Bus Master (DS00554) for more information.

#### 17.2.9 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allow the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSPSTAT register is set or when the bus is Idle, and both the S and P bits are clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the Stop condition occurs.

In Multi-Master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRIS bits). There are two stages where this arbitration of the bus can be lost. They are the Address Transfer and Data Transfer stages.

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an  $\overrightarrow{ACK}$  pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

Refer to Application Note AN578, Use of the SSP Module in the  $l^2 C^{TM}$  Multi-Master Environment (DS00578) for more information.

## 19.2 Wake-up Using Interrupts

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will not be cleared, the TO bit will not be set and the PD bit will not be cleared.

- If the interrupt occurs **during or after** the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

#### FIGURE 19-1: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| : 1 02 03 04;01 02 03 04;01  : : : : : : : : : : : : : : : : : : :                                                                                                                                                                                                      | Q4       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                                                                                                                                                                                                                         | <u> </u> |

| INT pin                                                                                                                                                                                                                                                                 |          |

| INTF flag<br>(INTCON reg.)                                                                                                                                                                                                                                              |          |

| GIE bit<br>(INTCON reg.), Sleep                                                                                                                                                                                                                                         |          |

|                                                                                                                                                                                                                                                                         |          |

| PC         V         PC + 1         V         PC + 2         V         PC + 2         V         PC + 2         V         O005h           Instruction Fetched         Inst(PC) = Sleep         Inst(PC + 1)         Inst(PC + 2)         Inst(0004h)         Inst(0005h) | h)       |

| Instruction Inst(PC - 1) Sleep Inst(PC + 1) Dummy Cycle Dummy Cycle Inst(000                                                                                                                                                                                            | h)       |

Note 1: XT, HS or LP Oscillator mode assumed.

2: TOST = 1024 Tosc (drawing not to scale). This delay does not apply to EC and RC Oscillator modes.

4: CLKOUT is not available in XT, HS, LP or EC Oscillator modes, but shown here for timing reference.

| Name   | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on all other Resets |

|--------|---------|-------|-------|-------|-------|--------|--------|--------|----------------------|---------------------------|

| IOCB   | IOCB7   | IOCB6 | IOCB5 | IOCB4 | IOCB3 | IOCB2  | IOCB1  | IOCB0  | 0000 0000            | 0000 0000                 |

| INTCON | GIE     | PEIE  | TOIE  | INTE  | RBIE  | T0IF   | INTF   | RBIF   | 0000 0000            | 0000 0000                 |

| PIE1   | TMR1GIE | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                 |

| PIE2   | _       | _     | _     | _     | —     | _      | _      | CCP2IE | 0                    | 0                         |

| PIR1   | TMR1GIF | ADIF  | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                 |

| PIR2   | —       |       | _     | -     | —     | —      | _      | CCP2IF | 0                    | 0                         |

#### TABLE 19-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used in Power-Down mode.

<sup>3:</sup> GIE = 1 assumed. In this case after wake-up, the processor jumps to 0004h. If GIE = 0, execution will continue in-line.

| Mnemonic,<br>Operands |                                        | Description                                      | Cycles       |       | 14-Bit | Opcode | Status | Natas    |         |  |

|-----------------------|----------------------------------------|--------------------------------------------------|--------------|-------|--------|--------|--------|----------|---------|--|

|                       |                                        | Description                                      |              | MSb   |        |        | LSb    | Affected | Notes   |  |

|                       | BYTE-ORIENTED FILE REGISTER OPERATIONS |                                                  |              |       |        |        |        |          |         |  |

| ADDWF                 | f, d                                   | Add W and f                                      | 1            | 00    | 0111   | dfff   | ffff   | C, DC, Z | 1, 2    |  |

| ANDWF                 | f, d                                   | AND W with f                                     | 1            | 00    | 0101   | dfff   | ffff   | Z        | 1, 2    |  |

| CLRF                  | f                                      | Clear f                                          | 1            | 00    | 0001   | lfff   | ffff   | Z        | 2       |  |

| CLRW                  | -                                      | Clear W                                          | 1            | 00    | 0001   | 0xxx   | xxxx   | Z        |         |  |

| COMF                  | f, d                                   | Complement f                                     | 1            | 00    | 1001   | dfff   | ffff   | Z        | 1, 2    |  |

| DECF                  | f, d                                   | Decrement f                                      | 1            | 00    | 0011   | dfff   | ffff   | Z        | 1, 2    |  |

| DECFSZ                | f, d                                   | Decrement f, Skip if 0                           | 1 <b>(2)</b> | 00    | 1011   | dfff   | ffff   |          | 1, 2, 3 |  |

| INCF                  | f, d                                   | Increment f                                      | 1            | 00    | 1010   | dfff   | ffff   | Z        | 1, 2    |  |

| INCFSZ                | f, d                                   | Increment f, Skip if 0                           | 1 <b>(2)</b> | 00    | 1111   | dfff   | ffff   |          | 1, 2, 3 |  |

| IORWF                 | f, d                                   | Inclusive OR W with f                            | 1            | 00    | 0100   | dfff   | ffff   | Z        | 1, 2    |  |

| MOVF                  | f, d                                   | Move f                                           | 1            | 00    | 1000   | dfff   | ffff   | Z        | 1, 2    |  |

| MOVWF                 | f                                      | Move W to f                                      | 1            | 00    | 0000   | lfff   | ffff   |          | -       |  |

| NOP                   | -                                      | No Operation                                     | 1            | 00    | 0000   | 0xx0   | 0000   |          |         |  |

| RLF                   | f, d                                   | Rotate Left f through Carry                      | 1            | 00    | 1101   | dfff   | ffff   | С        | 1, 2    |  |

| RRF                   | f, d                                   | Rotate Right f through Carry                     | 1            | 00    | 1100   | dfff   | ffff   | С        | 1, 2    |  |

| SUBWF                 | f, d                                   | Subtract W from f                                | 1            | 00    | 0010   | dfff   | ffff   | C, DC, Z | 1, 2    |  |

| SWAPF                 | f, d                                   | Swap nibbles in f                                | 1            | 00    | 1110   | dfff   | ffff   |          | 1, 2    |  |

| XORWF                 | f, d                                   | Exclusive OR W with f                            | 1            | 00    | 0110   | dfff   | ffff   | Z        | 1, 2    |  |

|                       |                                        | BIT-ORIENTED FILE R                              | EGISTER OPER | RATIO | NS     |        |        |          |         |  |

| BCF                   | f, b                                   | Bit Clear f                                      | 1            | 01    | 00bb   | bfff   | ffff   |          | 1, 2    |  |

| BSF                   | f, b                                   | Bit Set f                                        | 1            | 01    |        | bfff   | ffff   |          | 1, 2    |  |

| BTFSC                 | f, b                                   | Bit Test f, Skip if Clear                        | 1 <b>(2)</b> | 01    | 10bb   | bfff   | ffff   |          | 3       |  |

| BTFSS                 | f, b                                   | Bit Test f, Skip if Set                          | 1 (2)        | 01    | 11bb   | bfff   | ffff   |          | 3       |  |

|                       |                                        | LITERAL AND CON                                  | ITROL OPERAT | IONS  |        |        |        |          |         |  |

| ADDLW                 | k                                      | Add literal and W                                | 1            | 11    | 111x   | kkkk   | kkkk   | C, DC, Z |         |  |

| ANDLW                 | k                                      | AND literal with W                               | 1            | 11    | 1001   | kkkk   | kkkk   | Z        |         |  |

| CALL                  | k                                      | Call Subroutine                                  | 2            | 10    | 0kkk   | kkkk   | kkkk   |          |         |  |

| CLRWDT                | -                                      | Clear Watchdog Timer                             | 1            | 00    | 0000   | 0110   | 0100   | TO, PD   |         |  |

| GOTO                  | k                                      | Go to address                                    | 2            | 10    | 1kkk   | kkkk   | kkkk   |          |         |  |

| IORLW                 | k                                      | Inclusive OR literal with W                      | 1            | 11    | 1000   | kkkk   | kkkk   | Z        |         |  |

| MOVLW                 | k                                      | Move literal to W                                | 1            | 11    | 00xx   | kkkk   | kkkk   |          |         |  |

| RETFIE                | -                                      | Return from interrupt                            | 2            | 00    | 0000   | 0000   | 1001   |          |         |  |

| RETLW                 | k                                      | Return with literal in W                         | 2            | 11    | 01xx   | kkkk   | kkkk   |          |         |  |

| RETURN                | -                                      | Return from Subroutine                           | 2            | 00    | 0000   | 0000   | 1000   |          |         |  |

| SLEEP                 | _                                      | Go into Standby mode                             | 1            | 00    | 0000   | 0110   | 0011   | TO, PD   |         |  |

| SUBLW                 | k                                      | Subtract W from literal                          | 1            | 11    |        | kkkk   |        | C, DC, Z |         |  |

| XORLW                 | k                                      | Exclusive OR literal with W                      | 1            | 11    |        | kkkk   |        | Z        |         |  |

| Noto 1                |                                        | 1/O register is modified as a function of itself |              | I     |        |        |        | I        | l       |  |

#### TABLE 21-2: PIC16(L)F722/3/4/6/7 INSTRUCTION SET

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF PORTA, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

**3:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| PIC16LF       | 722/3/4/6  | 71                                                     | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array}$ |                                                      |                          |                  |                                                                                                                                                                                                                                                              |  |  |

|---------------|------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIC16F7       | 22/3/4/6/7 | 7                                                      |                                                                                                                                                                                                                                                           | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                          |                  |                                                                                                                                                                                                                                                              |  |  |

| Param.<br>No. | Sym.       | Characteristic                                         | Min.                                                                                                                                                                                                                                                      | Тур†                                                 | Max.                     | Units            | Conditions                                                                                                                                                                                                                                                   |  |  |

| D001          | Vdd        | Supply Voltage                                         |                                                                                                                                                                                                                                                           |                                                      |                          |                  |                                                                                                                                                                                                                                                              |  |  |

|               |            | PIC16LF722/3/4/6/7                                     | 1.8<br>1.8<br>2.3<br>2.5                                                                                                                                                                                                                                  |                                                      | 3.6<br>3.6<br>3.6<br>3.6 | V<br>V<br>V<br>V | Fosc $\leq$ 16 MHz: HFINTOSC, EC<br>Fosc $\leq$ 4 MHz<br>Fosc $\leq$ 20 MHz, EC<br>Fosc $\leq$ 20 MHz, HS                                                                                                                                                    |  |  |

| D001          |            | PIC16F722/3/4/6/7                                      | 1.8<br>1.8<br>2.3<br>2.5                                                                                                                                                                                                                                  |                                                      | 5.5<br>5.5<br>5.5<br>5.5 | V<br>V<br>V<br>V | Fosc $\leq$ 16 MHz: HFINTOSC, EC<br>Fosc $\leq$ 4 MHz<br>Fosc $\leq$ 20 MHz, EC<br>Fosc $\leq$ 20 MHz, HS                                                                                                                                                    |  |  |

| D002*         | Vdr        | RAM Data Retention Voltage <sup>(1)</sup>              |                                                                                                                                                                                                                                                           |                                                      |                          |                  |                                                                                                                                                                                                                                                              |  |  |

|               |            | PIC16LF722/3/4/6/7                                     | 1.5                                                                                                                                                                                                                                                       |                                                      | _                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |  |

| D002*         |            | PIC16F722/3/4/6/7                                      | 1.7                                                                                                                                                                                                                                                       | _                                                    | _                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |  |

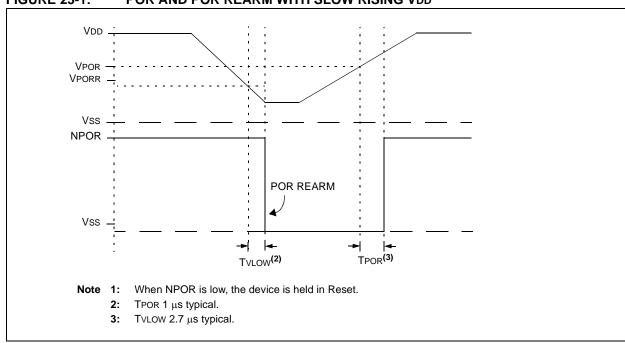

|               | VPOR*      | Power-on Reset Release Voltage                         | _                                                                                                                                                                                                                                                         | 1.6                                                  | _                        | V                |                                                                                                                                                                                                                                                              |  |  |

|               | VPORR*     | Power-on Reset Rearm Voltage                           |                                                                                                                                                                                                                                                           |                                                      |                          |                  |                                                                                                                                                                                                                                                              |  |  |

|               |            | PIC16LF722/3/4/6/7                                     | _                                                                                                                                                                                                                                                         | 0.8                                                  | _                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |  |

|               |            | PIC16F722/3/4/6/7                                      |                                                                                                                                                                                                                                                           | 1.7                                                  | —                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |  |

| D003          | Vfvr       | Fixed Voltage Reference Voltage,<br>Initial Accuracy   | -8<br>-8<br>-8                                                                                                                                                                                                                                            | <br>                                                 | 6<br>6<br>6              | %<br>%<br>%      | $ \begin{array}{l} {\sf VFVR} = 1.024{\sf V},  {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 2.048{\sf V},  {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 4.096{\sf V},  {\sf VDD} \geq 4.75{\sf V}; \\ {\sf -40} \leq {\sf TA} \leq 85^{\circ}{\sf C} \end{array} $ |  |  |

|               |            |                                                        | -8<br>-8<br>-8                                                                                                                                                                                                                                            |                                                      | 6<br>6<br>6              | %<br>%<br>%      | $ \begin{array}{l} V{\sf FVR} = 1.024V, \ V{\sf DD} \geq 2.5V \\ V{\sf FVR} = 2.048V, \ V{\sf DD} \geq 2.5V \\ V{\sf FVR} = 4.096V, \ V{\sf DD} \geq 4.75V; \\ -40 \leq {\sf TA} \leq 125^{\circ}{\sf C} \end{array} $                                       |  |  |

| D004*         | SVDD       | VDD Rise Rate to ensure internal Power-on Reset signal | 0.05                                                                                                                                                                                                                                                      | —                                                    | —                        | V/ms             | See Section 3.2 "Power-on Reset (POR)" for details.                                                                                                                                                                                                          |  |  |

## 23.1 DC Characteristics: PIC16(L)F722/3/4/6/7-I/E (Industrial, Extended)

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

# PIC16(L)F722/3/4/6/7

#### FIGURE 23-1: POR AND POR REARM WITH SLOW RISING VDD

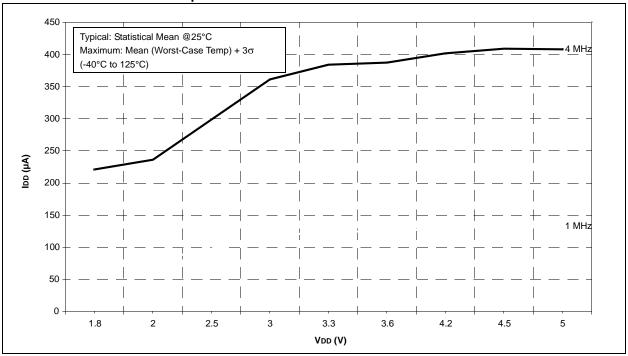

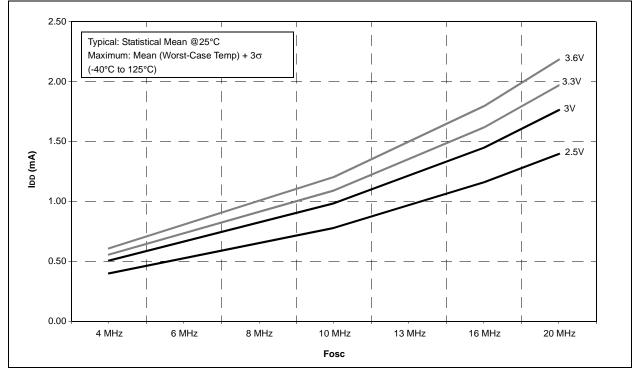

## FIGURE 24-7: PIC16F722/3/4/6/7 TYPICAL IDD vs. VDD OVER Fosc, EXTRC MODE, VCAP = $0.1 \mu$ F

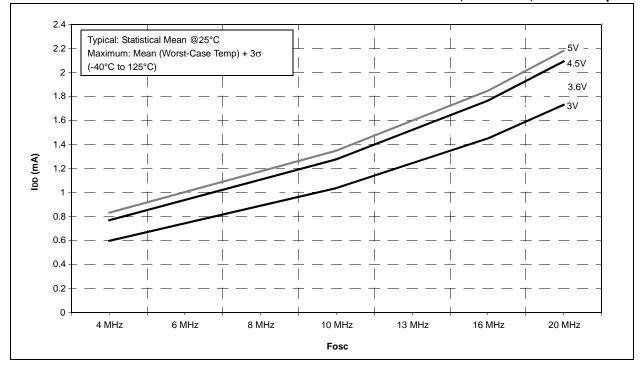

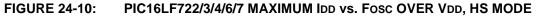

#### FIGURE 24-9: PIC16F722/3/4/6/7 MAXIMUM IDD vs. Fosc OVER VDD, HS MODE, VCAP = 0.1 µF

## APPENDIX A: DATA SHEET REVISION HISTORY

## Revision A (12/2007)

Original release.

## Revision B (08/2008)

Electrical Specification updates; Package Drawings; miscellaneous updates.

## Revision C (04/2009)

Revised data sheet title; Revised Low-Power Features section; Revised Section 6.2.2.4 RA3/AN3/VREF; Revised Figure 16-8 Synchronous Reception.

## Revision D (07/2009)

Removed the Preliminary Label; Updated the "Electrical Characteristics" section; Added charts in the "Char. Data" section; Deleted "Based 8-Bit CMOS" from title; Updated the "Special Microcontroller Features" section and the "Peripheral Features" section; Changed the title of the "Low Power Features" section into "Extreme Low-Power Management PIC16LF72X with nanoWatt XLP" and updated this section; Inserted new section – "Analog Features" (page 1); Changed the title of the "Peripheral Features" section into "Peripheral Highlights" and updated the section.

## **Revision E (10/2009)**

Added paragraph to section 5.0 (LDO Voltage Regulator); Updated the Electrical Specifications section (Added another absolute Maximum Rating; Updated section 23.1 and Table 23-4); Updated the Pin Diagrams with the UQFN package; Updated Table 1, adding UQFN; Updated section 23.5 (Thermal Considerations); Updated the Packaging Information section adding the UQFN Package; Updated the Product Identification System section.

## **Revision F (12/2015)**

Updated Table 2; Updated 23.1, 23.3 and 9.2.4 Sections; Updated Figure 23-9; Other minor corrections.

## APPENDIX B: MIGRATING FROM OTHER PIC® DEVICES

This discusses some of the issues in migrating from other  $\text{PIC}^{\textcircled{B}}$  devices to the PIC16F72X family of devices.

## B.1 PIC16F77 to PIC16F72X

#### TABLE B-1: FEATURE COMPARISON

| Feature                               | PIC16F77 | PIC16F727           |

|---------------------------------------|----------|---------------------|

| Max. Operating Speed                  | 20 MHz   | 20 MHz              |

| Max. Program<br>Memory (Words)        | 8K       | 8K                  |

| Max. SRAM (Bytes)                     | 368      | 368                 |

| A/D Resolution                        | 8-bit    | 8-bit               |

| Timers (8/16-bit)                     | 2/1      | 2/1                 |

| Oscillator Modes                      | 4        | 8                   |

| Brown-out Reset                       | Y        | Y                   |

| Internal Pull-ups                     | RB<7:0>  | RB<7:0>             |

| Interrupt-on-change                   | RB<7:4>  | RB<7:0>             |

| Comparator                            | 0        | 0                   |

| USART                                 | Y        | Y                   |

| Extended WDT                          | Ν        | N                   |

| Software Control<br>Option of WDT/BOR | N        | N                   |

| INTOSC Frequencies                    | None     | 500 kHz -<br>16 MHz |

| Clock Switching                       | Ν        | Ν                   |