#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf722t-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

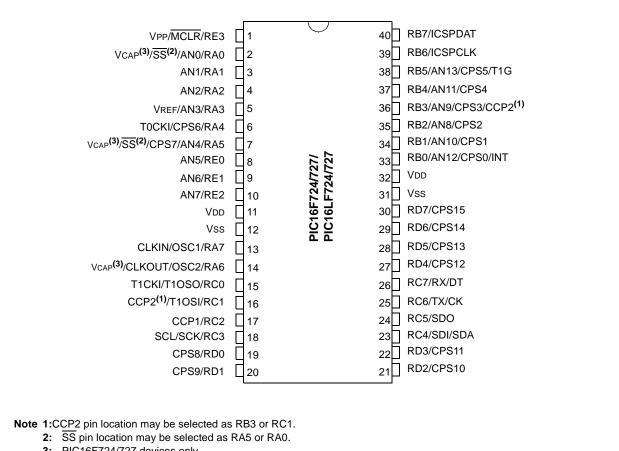

# Pin Diagrams - 40-PIN PDIP (PIC16F724/727/PIC16LF724/727)

3: PIC16F724/727 devices only.

| Name                                                                      | Function | Input<br>Type | Output<br>Type | Description                                                                                              |  |  |

|---------------------------------------------------------------------------|----------|---------------|----------------|----------------------------------------------------------------------------------------------------------|--|--|

| RD3/CPS11                                                                 | RD3      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | CPS11    | AN            | —              | Capacitive sensing input 11.                                                                             |  |  |

| RD4/CPS12                                                                 | RD4      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | CPS12    | AN            | —              | Capacitive sensing input 12.                                                                             |  |  |

| RD5/CPS13                                                                 | RD5      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | CPS13    | AN            | —              | Capacitive sensing input 13.                                                                             |  |  |

| RD6/CPS14                                                                 | RD6      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | CPS14    | AN            | _              | Capacitive sensing input 14.                                                                             |  |  |

| RD7/CPS15                                                                 | RD7      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | CPS15    | AN            | _              | Capacitive sensing input 15.                                                                             |  |  |

| RE0/AN5                                                                   | RE0      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | AN5      | AN            | —              | A/D Channel 5 input.                                                                                     |  |  |

| RE1/AN6                                                                   | RE1      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | AN6      | AN            | —              | A/D Channel 6 input.                                                                                     |  |  |

| RE2/AN7                                                                   | RE2      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |

|                                                                           | AN7      | AN            | _              | A/D Channel 7 input.                                                                                     |  |  |

| RE3/MCLR/Vpp                                                              | RE3      | TTL           | —              | General purpose input.                                                                                   |  |  |

|                                                                           | MCLR     | ST            | _              | Master Clear with internal pull-up.                                                                      |  |  |

|                                                                           | Vpp      | ΗV            | —              | Programming voltage.                                                                                     |  |  |

| VDD                                                                       | Vdd      | Power         | —              | Positive supply.                                                                                         |  |  |

| Vss                                                                       | Vss      | Power         | _              | Ground reference.                                                                                        |  |  |

| Legend: AN = Analog input or<br>TTL = TTL compatible<br>HV = High Voltage | input ST |               | nitt Trigger   | ble input or output OD = Open Drain<br>input with CMOS levels $I^2C$ = Schmitt Trigger input with $I^2C$ |  |  |

# TABLE 1-1: PIC16(L)F722/3/4/6/7 PINOUT DESCRIPTION (CONTINUED)

**Note:** The PIC16F722/3/4/6/7 devices have an internal low dropout voltage regulator. An external capacitor must be connected to one of the available VCAP pins to stabilize the regulator. For more information, see **Section 5.0 "Low Dropout (LDO) Voltage Regulator**". The PIC16LF722/3/4/6/7 devices do not have the voltage regulator and therefore no external capacitor is required.

# 2.2.2.2 OPTION register

The OPTION register, shown in Register 2-2, is a readable and writable register, which contains various control bits to configure:

- Timer0/WDT prescaler

- External RB0/INT interrupt

- Timer0

- Weak pull-ups on PORTB

| Note: | To achieve a 1:1 prescaler assignment for |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | Timer0, assign the prescaler to the WDT   |  |  |  |  |  |  |  |

|       | by setting the PSA bit of the             |  |  |  |  |  |  |  |

|       | OPTION_REG register to '1'. Refer to      |  |  |  |  |  |  |  |

|       | Section 11.1.3 "Software                  |  |  |  |  |  |  |  |

|       | Programmable Prescaler".                  |  |  |  |  |  |  |  |

# REGISTER 2-2: OPTION\_REG: OPTION REGISTER

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7   | <b>RBPU:</b> PORTB Pull-up Enable bit<br>1 = PORTB pull-ups are disabled<br>0 = PORTB pull-ups are enabled by individual bits in the WPUB register                                                                             |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | INTEDG: Interrupt Edge Select bit<br>1 = Interrupt on rising edge of RB0/INT pin<br>0 = Interrupt on falling edge of RB0/INT pin                                                                                               |

| bit 5   | <b>T0CS:</b> Timer0 Clock Source Select bit<br>1 = Transition on RA4/T0CKI pin<br>0 = Internal instruction cycle clock (Fosc/4)                                                                                                |

| bit 4   | <b>T0SE:</b> Timer0 Source Edge Select bit<br>1 = Increment on high-to-low transition on RA4/T0CKI pin<br>0 = Increment on low-to-high transition on RA4/T0CKI pin                                                             |

| bit 3   | <b>PSA:</b> Prescaler Assignment bit<br>1 = Prescaler is assigned to the WDT<br>0 = Prescaler is assigned to the Timer0 module                                                                                                 |

| bit 2-0 | PS<2:0>: Prescaler Rate Select bits                                                                                                                                                                                            |

|         | Bit Value Timer0 Rate WDT Rate                                                                                                                                                                                                 |

|         | 000         1:2         1:1           001         1:4         1:2           010         1:8         1:4           011         1:16         1:8           100         1:32         1:16           101         1:64         1:32 |

1:128

1:256

1:64

1 : 128

110

111

## 6.3.4 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTB pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the SSP,  $l^2C$  or interrupts, refer to the appropriate section in this data sheet.

# 6.3.4.1 RB0/AN12/CPS0/INT

Figure 6-7 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- · a capacitive sensing input

- an external edge triggered interrupt

# 6.3.4.2 RB1/AN10/CPS1

Figure 6-8 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- · a capacitive sensing input

## 6.3.4.3 RB2/AN8/CPS2

Figure 6-8 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- · a capacitive sensing input

## 6.3.4.4 RB3/AN9/CPS3/CCP2

Figure 6-9 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- a capacitive sensing input

- a Capture 2 input, Compare 2 output, and PWM2 output

| Note: | CCP2 pin location may be selected as |

|-------|--------------------------------------|

|       | RB3 or RC1.                          |

## 6.3.4.5 RB4/AN11/CPS4

Figure 6-8 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- · a capacitive sensing input

# 6.3.4.6 RB5/AN13/CPS5/T1G

Figure 6-10 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- a capacitive sensing input

- a Timer1 gate input

# 6.3.4.7 RB6/ICSPCLK

Figure 6-11 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- In-Circuit Serial Programming clock

# 6.3.4.8 RB7/ICSPDAT

Figure 6-12 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- In-Circuit Serial Programming data

| REGISTER      | <b>19-2.</b> ADCO                                         |                                | ITROL REG        |                    |                    |                  |        |  |  |  |  |  |

|---------------|-----------------------------------------------------------|--------------------------------|------------------|--------------------|--------------------|------------------|--------|--|--|--|--|--|

| U-0           | R/W-0                                                     | R/W-0                          | R/W-0            | U-0                | U-0                | R/W-0            | R/W-0  |  |  |  |  |  |

| _             | ADCS2                                                     | ADCS1                          | ADCS0            | _                  | _                  | ADREF1           | ADREF0 |  |  |  |  |  |

| bit 7         |                                                           |                                |                  |                    |                    |                  | bit 0  |  |  |  |  |  |

| Legend:       |                                                           |                                |                  |                    |                    |                  |        |  |  |  |  |  |

| R = Readabl   | le bit                                                    | W = Writable bi                | t                | U = Unimpleme      | ented bit, read as | s 'O'            |        |  |  |  |  |  |

| -n = Value at | t POR                                                     | '1' = Bit is set               |                  | '0' = Bit is clear | red                | x = Bit is unkno | wn     |  |  |  |  |  |

|               |                                                           |                                |                  |                    |                    |                  |        |  |  |  |  |  |

| bit 7         | Unimplemente                                              | ed: Read as '0'                |                  |                    |                    |                  |        |  |  |  |  |  |

| bit 6-4       | ADCS<2:0>: A                                              | /D Conversion C                | lock Select bits |                    |                    |                  |        |  |  |  |  |  |

|               | 000 = Fosc/2                                              | 000 = Fosc/2                   |                  |                    |                    |                  |        |  |  |  |  |  |

|               | 001 = Fosc/8                                              | 001 = FOSC/8                   |                  |                    |                    |                  |        |  |  |  |  |  |

|               |                                                           | 010 = Fosc/32                  |                  |                    |                    |                  |        |  |  |  |  |  |

|               | 011 = FRC (clock supplied from a dedicated RC oscillator) |                                |                  |                    |                    |                  |        |  |  |  |  |  |

|               |                                                           | 100 = Fosc/4<br>101 = Fosc/16  |                  |                    |                    |                  |        |  |  |  |  |  |

|               |                                                           | 101 = FOSC/16<br>110 = FOSC/64 |                  |                    |                    |                  |        |  |  |  |  |  |

|               |                                                           | ,<br>ock supplied from         | a dedicated RC   | coscillator)       |                    |                  |        |  |  |  |  |  |

| bit 3-2       | Unimplemente                                              | ••                             |                  | ,                  |                    |                  |        |  |  |  |  |  |

| bit 1-0       | ADREF<1:0>:                                               | Voltage Referend               | e Configuration  | bits               |                    |                  |        |  |  |  |  |  |

|               |                                                           | 0x = VREF is connected to VDD  |                  |                    |                    |                  |        |  |  |  |  |  |

|               | 10 = VREF is c                                            | connected to exte              | rnal VREF (RA3   | /AN3)              |                    |                  |        |  |  |  |  |  |

|               |                                                           |                                | nal Fixed Voltag |                    |                    |                  |        |  |  |  |  |  |

# REGISTER 9-2: ADCON1: A/D CONTROL REGISTER 1

## REGISTER 9-3: ADRES: ADC RESULT REGISTER

| R/W-x  | x R/W-x R/W-x |        | N-x R/W-x R/W |        | R/W-x  | R/W-x  | R/W-x  |

|--------|---------------|--------|---------------|--------|--------|--------|--------|

| ADRES7 | ADRES6        | ADRES5 | ADRES4        | ADRES3 | ADRES2 | ADRES1 | ADRES0 |

| bit 7  |               |        |               |        |        |        | bit 0  |

| Legend:           |                  |                                                 |                    |  |  |  |

|-------------------|------------------|-------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | Writable bit U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                            | x = Bit is unknown |  |  |  |

bit 7-0 **ADRES<7:0>**: ADC Result Register bits 8-bit conversion result.

|         |         |        |        |            |               |        | -       | -      | -                    | -                               |

|---------|---------|--------|--------|------------|---------------|--------|---------|--------|----------------------|---------------------------------|

| Name    | Bit 7   | Bit 6  | Bit 5  | Bit 4      | Bit 3         | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| ADCON0  | _       |        | CHS3   | CHS2       | CHS1          | CHS0   | GO/DONE | ADON   | 00 0000              | 00 0000                         |

| ADCON1  | _       | ADCS2  | ADCS1  | ADCS0      | _             | _      | ADREF1  | ADREF0 | -00000               | -00000                          |

| ANSELA  | _       | _      | ANSA5  | ANSA4      | ANSA3         | ANSA2  | ANSA1   | ANSA0  | 11 1111              | 11 1111                         |

| ANSELB  | _       | _      | ANSB5  | ANSB4      | ANSB3         | ANSB2  | ANSB1   | ANSB0  | 11 1111              | 11 1111                         |

| ANSELE  | _       | _      | _      | _          | _             | ANSE2  | ANSE1   | ANSE0  | 111                  | 111                             |

| ADRES   |         |        |        | A/D Result | Register Byte | Э      |         |        | xxxx xxxx            | uuuu uuuu                       |

| CCP2CON | _       | _      | DC2B1  | DC2B0      | CCP2M3        | CCP2M2 | CCP2M1  | CCP2M0 | 00 0000              | 00 0000                         |

| FVRCON  | FVRRDY  | FVREN  | _      | _          | _             | _      | ADFVR1  | ADFVR0 | q000                 | q000                            |

| INTCON  | GIE     | PEIE   | T0IE   | INTE       | RBIE          | T0IF   | INTF    | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1    | TMR1GIE | ADIE   | RCIE   | TXIE       | SSPIE         | CCP1IE | TMR2IE  | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1    | TMR1GIF | ADIF   | RCIF   | TXIF       | SSPIF         | CCP1IF | TMR2IF  | TMR1IF | 0000 0000            | 0000 0000                       |

| TRISA   | TRISA7  | TRISA6 | TRISA5 | TRISA4     | TRISA3        | TRISA2 | TRISA1  | TRISA0 | 1111 1111            | 1111 1111                       |

| TRISB   | TRISB7  | TRISB6 | TRISB5 | TRISB4     | TRISB3        | TRISB2 | TRISB1  | TRISB0 | 1111 1111            | 1111 1111                       |

| TRISE   | _       | _      | _      | _          | TRISE3        | TRISE2 | TRISE1  | TRISE0 | 1111                 | 1111                            |

|         |         |        |        |            |               |        |         |        |                      |                                 |

TABLE 9-2: SUMMARY OF ASSOCIATED ADC REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for ADC module.

# REGISTER 14-2: CPSCON1: CAPACITIVE SENSING CONTROL REGISTER 1

| U-0          | U-0 | U-0            | U-0 | R/W-0 <sup>(2)</sup>               | R/W-0            | R/W-0    | R/W-0  |  |  |

|--------------|-----|----------------|-----|------------------------------------|------------------|----------|--------|--|--|

| —            | —   | —              | _   | CPSCH3                             | CPSCH2           | CPSCH1   | CPSCH0 |  |  |

| bit 7        |     |                |     |                                    |                  |          | bit 0  |  |  |

| Legend:      |     |                |     |                                    |                  |          |        |  |  |

|              |     |                |     | U = Unimplemented bit, read as '0' |                  |          |        |  |  |

| R = Readable | bit | W = Writable I | oit | U = Unimplen                       | nented bit, read | l as '0' |        |  |  |

| bit 7-4 | Unimplemented: Read as '0'                         |

|---------|----------------------------------------------------|

| bit 3-0 | CPSCH<3:0>: Capacitive Sensing Channel Select bits |

|         | If CPSON = 0:                                      |

|         | These bits are ignored. No channel is selected.    |

|         | <u>If CPSON = 1</u> :                              |

|         | 0000 = channel 0, (CPS0)                           |

|         | 0001 = channel 1, (CPS1)                           |

|         | 0010 = channel 2, (CPS2)                           |

|         | 0011 = channel 3, (CPS3)                           |

|         | 0100 = channel 4, (CPS4)                           |

|         | 0101 = channel 5, (CPS5)                           |

|         | 0110 = channel 6, (CPS6)                           |

|         | 0111 = channel 7, (CPS7)                           |

|         | 1000 = channel 8, (CPS8 <sup>(1)</sup> )           |

|         | 1001 = channel 9, (CPS9 <sup>(1)</sup> )           |

|         | 1010 = channel 10, (CPS10 <sup>(1)</sup> )         |

|         | 1011 = channel 11, (CPS11 <sup>(1)</sup> )         |

|         | 1100 =  channel 12, (CPS12(1))                     |

|         | $1101 = \text{ channel } 13, (CPS13^{(1)})$        |

|         | 1110 = channel 14, (CPS14(1))                      |

|         | 1111 = channel 15, (CPS15 <sup>(1)</sup> )         |

**Note 1:** These channels are not implemented on the PIC16F722/723/726/PIC16LF722/723/726.

2: This bit is not implemented on PIC16F722/723/726/PIC16LF722/723/726, Read as '0'

| TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH CAPACITIVE SENSIN | G |

|--------------------------------------------------------------------|---|

|--------------------------------------------------------------------|---|

| Name       | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|---------|---------|---------|---------|---------|--------|---------|---------|----------------------|---------------------------------|

| ANSELA     | _       | _       | ANSA5   | ANSA4   | ANSA3   | ANSA2  | ANSA1   | ANSA0   | 11 1111              | 11 1111                         |

| ANSELB     | _       | _       | ANSB5   | ANSB4   | ANSB3   | ANSB2  | ANSB1   | ANSB0   | 11 1111              | 11 1111                         |

| ANSELD     | ANSD7   | ANSD6   | ANSD5   | ANSD4   | ANSD3   | ANSD2  | ANSD1   | ANSD0   | 1111 1111            | 1111 1111                       |

| OPTION_REG | RBPU    | INTEDG  | TOCS    | T0SE    | PSA     | PS2    | PS1     | PS0     | 1111 1111            | 1111 1111                       |

| PIE1       | TMR1GIE | ADIE    | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIR1       | TMR1GIF | ADIF    | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| T1CON      | TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | _       | TMR10N  | 0000 00-0            | 0000 00-0                       |

| T2CON      |         | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

| TRISA      | TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2 | TRISA1  | TRISA0  | 1111 1111            | 1111 1111                       |

| TRISB      | TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2 | TRISB1  | TRISB0  | 1111 1111            | 1111 1111                       |

| TRISD      | TRISD7  | TRISD6  | TRISD5  | TRISD4  | TRISD3  | TRISD2 | TRISD1  | TRISD0  | 1111 1111            | 1111 1111                       |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the capacitive sensing module.

# 17.2.6 TRANSMISSION

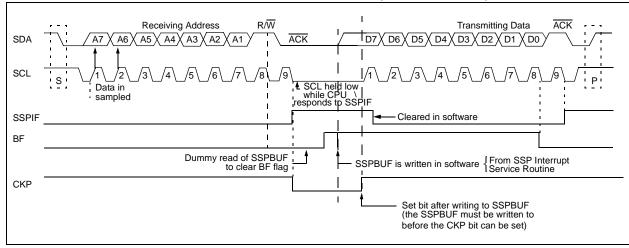

When the R/W bit of the received address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set and the slave will respond to the master by reading out data. After the address match, an ACK pulse is generated by the slave hardware and the SCL pin is held low (clock is automatically stretched) until the slave is ready to respond. See **Section 17.2.7 "Clock Stretching"**. The data the slave will transmit must be loaded into the SSPBUF register, which sets the BF bit. The SCL line is released by setting the CKP bit of the SSPCON register.

An SSP interrupt is generated for each transferred data byte. The SSPIF flag bit of the PIR1 register initiates an SSP interrupt, and must be cleared by software before the next byte is transmitted. The BF bit of the SSPSTAT register is cleared on the falling edge of the eighth received clock pulse. The SSPIF flag bit is set on the falling edge of the ninth clock pulse. Following the eighth falling clock edge, control of the SDA line is released back to the master so that the master can acknowledge or not acknowledge the response. If the master sends a not acknowledge, the slave's transmission is complete and the slave must monitor for the next Start condition. If the master acknowledges, control of the bus is returned to the slave to transmit another byte of data. Just as with the previous byte, the clock is stretched by the slave, data must be loaded into the SSPBUF and CKP must be set to release the clock line (SCL).

## FIGURE 17-12: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

# 19.0 POWER-DOWN MODE (SLEEP)

The Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If the Watchdog Timer is enabled:

- WDT will be cleared but keeps running.

- PD bit of the STATUS register is cleared.

- TO bit of the STATUS register is set.

- Oscillator driver is turned off.

- Timer1 oscillator is unaffected

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSs, with no external circuitry drawing current from the I/O pin. I/O pins that are high-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level when external  $\overline{\text{MCLR}}$  is enabled.

**Note:** A Reset generated by a WDT time out does not drive MCLR pin low.

# 19.1 Wake-up from Sleep

The device can wake up from Sleep through one of the following events:

- 1. External Reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer wake-up (if WDT was enabled).

- 3. Interrupt from RB0/INT pin, PORTB change or a peripheral interrupt.

The first event will cause a device Reset. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. TO bit is cleared if WDT wake-up occurred.

The following peripheral interrupts can wake the device from Sleep:

- 1. TMR1 Interrupt. Timer1 must be operating as an asynchronous counter.

- USART Receive Interrupt (Synchronous Slave mode only)

- 3. A/D conversion (when A/D clock source is RC)

- 4. Interrupt-on-change

- 5. External Interrupt from INT pin

- 6. Capture event on CCP1 or CCP2

- 7. SSP Interrupt in SPI or I<sup>2</sup>C Slave mode

Other peripherals cannot generate interrupts since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction, then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

**Note:** If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from Sleep. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

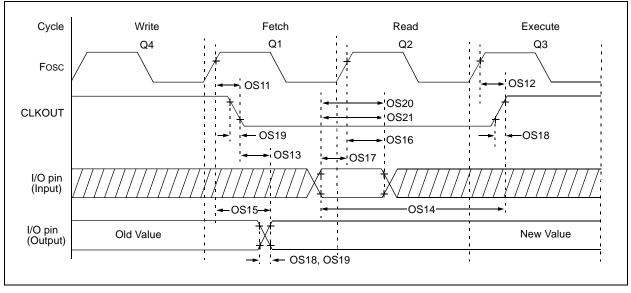

# 23.6 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| 2. Tpp3 |                                       |     |                |

|---------|---------------------------------------|-----|----------------|

| т       |                                       |     |                |

| F       | Frequency                             | Т   | Time           |

| Lowerc  | case letters (pp) and their meanings: |     |                |

| рр      |                                       |     |                |

| сс      | CCP1                                  | OSC | OSC1           |

| ck      | CLKOUT                                | rd  | RD             |

| CS      | CS                                    | rw  | RD or WR       |

| di      | SDI                                   | SC  | SCK            |

| do      | SDO                                   | SS  | SS             |

| dt      | Data in                               | tO  | TOCKI          |

| io      | I/O PORT                              | t1  | T1CKI          |

| mc      | MCLR                                  | wr  | WR             |

| Upperc  | case letters and their meanings:      |     |                |

| S       |                                       |     |                |

| F       | Fall                                  | Р   | Period         |

| н       | High                                  | R   | Rise           |

| I       | Invalid (High-impedance)              | V   | Valid          |

| L       | Low                                   | Z   | High-impedance |

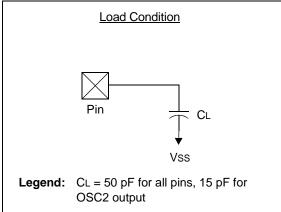

## FIGURE 23-2: LOAD CONDITIONS

#### TABLE 23-2: **OSCILLATOR PARAMETERS**

|              | Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature -40°C ≤ TA ≤ +125°C |                                                          |                    |      |      |      |       |                                                                                       |  |  |

|--------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------|------|------|------|-------|---------------------------------------------------------------------------------------|--|--|

| Param<br>No. | Sym.                                                                                                 | Characteristic                                           | Freq.<br>Tolerance | Min. | Тур† | Max. | Units | Conditions                                                                            |  |  |

| OS08         | HFosc                                                                                                | Internal Calibrated HFINTOSC<br>Frequency <sup>(2)</sup> | ±2%                |      | 16.0 |      | MHz   | $\begin{array}{l} 0^{\circ}C \leq TA \leq +85^{\circ}C, \\ VDD \geq 2.5V \end{array}$ |  |  |

|              |                                                                                                      |                                                          | ±5%                | _    | 16.0 | —    | MHz   | $\text{-40°C} \leq \text{TA} \leq \text{+125°C}$                                      |  |  |

| OS08A        | MFosc                                                                                                | Internal Calibrated MFINTOSC<br>Frequency <sup>(2)</sup> | ±2%                | _    | 500  | _    | kHz   | $0^{\circ}C \le TA \le +85^{\circ}C$<br>VDD $\ge 2.5V$                                |  |  |

|              |                                                                                                      |                                                          | ±5%                | _    | 500  | 10   | kHz   | $-40^{\circ}C \leq TA \leq +125^{\circ}C$                                             |  |  |

| OS10*        | TIOSC ST                                                                                             | HFINTOSC Wake-up from Sleep<br>Start-up Time             | —                  | _    | 5    | 8    | μS    |                                                                                       |  |  |

|              |                                                                                                      | MFINTOSC Wake-up from Sleep<br>Start-up Time             | —                  |      | 20   | 30   | μS    |                                                                                       |  |  |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are t not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

2: To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

3: By design.

# TABLE 23-5: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

Standard Operating Conditions (unless otherwise stated)

| Param<br>No. | Sym.      | Characteristic            |                                                           | Min.           | Тур†                                      | Max.   | Units | Conditions          |                                    |

|--------------|-----------|---------------------------|-----------------------------------------------------------|----------------|-------------------------------------------|--------|-------|---------------------|------------------------------------|

| 40*          | T⊤0H      | T0CKI High F              | Pulse Width No Prescaler                                  |                | 0.5 Tcy + 20                              | —      | _     | ns                  |                                    |

|              |           |                           |                                                           | With Prescaler | 10                                        | _      | _     | ns                  |                                    |

| 41*          | TT0L      | T0CKI Low F               | ulse Width                                                | No Prescaler   | 0.5 Tcy + 20                              | —      | _     | ns                  |                                    |

|              |           |                           |                                                           | With Prescaler | 10                                        | —      | _     | ns                  |                                    |

| 42*          | Тт0Р      | T0CKI Period              | d                                                         |                | Greater of:<br>20 or <u>Tcy + 40</u><br>N | —      | _     | ns                  | N = prescale value<br>(2, 4,, 256) |

| 45*          | T⊤1H      | T1CKI High<br>Time        | Synchronous, No Prescaler                                 |                | 0.5 TCY + 20                              | _      | _     | ns                  |                                    |

|              |           |                           | Synchronous, with Prescaler                               |                | 15                                        | _      | _     | ns                  |                                    |

|              |           |                           | Asynchronous                                              |                | 30                                        | —      | _     | ns                  |                                    |

| 46*          | TT1L      | T1CKI Low<br>Time         | Synchronous, No Prescaler                                 |                | 0.5 TCY + 20                              | —      | _     | ns                  |                                    |

|              |           |                           | Synchronous, with Prescaler                               |                | 15                                        | —      | _     | ns                  |                                    |

|              |           |                           | Asynchronous                                              |                | 30                                        | —      | _     | ns                  |                                    |

| 47*          | TT1P      | T1CKI Input<br>Period     | Synchronous                                               |                | Greater of:<br>30 or <u>TCY + 40</u><br>N | —      |       | ns                  | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                           | Asynchronous                                              | 3              | 60                                        | _      | _     | ns                  |                                    |

| 48           | F⊤1       |                           | lator Input Frequency Range abled by setting bit T1OSCEN) |                | 32.4                                      | 32.768 | 33.1  | kHz                 |                                    |

| 49*          | TCKEZTMR1 | Delay from E<br>Increment | xternal Clock E                                           | 2 Tosc         | —                                         | 7 Tosc | —     | Timers in Sync mode |                                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

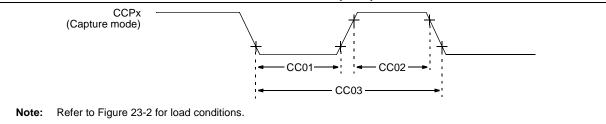

## FIGURE 23-11: CAPTURE/COMPARE/PWM TIMINGS (CCP)

## TABLE 23-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP)

|              | Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                      |                |                       |      |      |       |                                 |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|----------------------|----------------|-----------------------|------|------|-------|---------------------------------|--|--|--|

| Param<br>No. | Sym.                                                                                                                 | Characteris          | stic           | Min.                  | Тур† | Max. | Units | Conditions                      |  |  |  |

| CC01*        | TccL                                                                                                                 | CCPx Input Low Time  | No Prescaler   | 0.5Tcy + 20           | _    | —    | ns    |                                 |  |  |  |

|              |                                                                                                                      |                      | With Prescaler | 20                    | _    | _    | ns    |                                 |  |  |  |

| CC02*        | TccH                                                                                                                 | CCPx Input High Time | No Prescaler   | 0.5TCY + 20           | _    | _    | ns    |                                 |  |  |  |

|              |                                                                                                                      |                      | With Prescaler | 20                    | _    | _    | ns    |                                 |  |  |  |

| CC03*        | TccP                                                                                                                 | CCPx Input Period    |                | <u>3Tcy + 40</u><br>N |      | _    | ns    | N = prescale value (1, 4 or 16) |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Param<br>No.   | Symbol                | Characteristic                                            | Min.        | Тур†     | Max. | Units | Conditions |  |

|----------------|-----------------------|-----------------------------------------------------------|-------------|----------|------|-------|------------|--|

| SP70*          | TssL2scH,<br>TssL2scL | $\overline{\text{SS}}$ ↓ to SCK↓ or SCK↑ input            | Тсү         |          | —    | ns    |            |  |

| SP71*          | TscH                  | SCK input high time (Slave mode)                          |             | TCY + 20 |      | _     | ns         |  |

| SP72*          | TscL                  | SCK input low time (Slave mode)                           |             | TCY + 20 |      | _     | ns         |  |

| SP73*          | TDIV2scH,<br>TDIV2scL | Setup time of SDI data input to SCK                       | edge        | 100      |      | —     | ns         |  |

| SP74*          | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK e                      | 100         |          | —    | ns    |            |  |

| SP75* TDOR SDO |                       | SDO data output rise time                                 | 3.0-5.5V    | —        | 10   | 25    | ns         |  |

|                |                       |                                                           | 1.8-5.5V    | —        | 25   | 50    | ns         |  |

| SP76*          | TDOF                  | SDO data output fall time                                 |             | —        | 10   | 25    | ns         |  |

| SP77*          | TssH2doZ              | $\overline{SS}$ to SDO output high-impedance              | 10          | _        | 50   | ns    |            |  |

| SP78*          | TscR                  | SCK output rise time                                      | 3.0-5.5V    | —        | 10   | 25    | ns         |  |

|                |                       | (Master mode)                                             | 1.8-5.5V    | _        | 25   | 50    | ns         |  |

| SP79*          | TscF                  | SCK output fall time (Master mode)                        |             | _        | 10   | 25    | ns         |  |

| SP80*          | TscH2doV,             | SDO data output valid after SCK                           | 3.0-5.5V    | —        | _    | 50    | ns         |  |

|                | TscL2doV              | edge                                                      | 1.8-5.5V    | —        | _    | 145   | ns         |  |

| SP81*          | TDOV2SCH,<br>TDOV2SCL | SDO data output setup to SCK edge                         | Тсу         | _        | —    | ns    |            |  |

| SP82*          | TssL2doV              | SDO data output valid after $\overline{SS}\downarrow$ edg | _           | _        | 50   | ns    |            |  |

| SP83*          | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                       | 1.5Tcy + 40 | _        | -    | ns    |            |  |

# TABLE 23-11: SPI MODE REQUIREMENTS

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

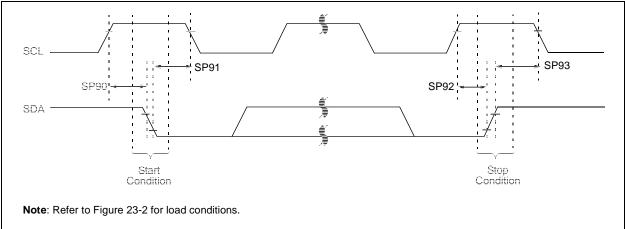

#### FIGURE 23-20: I<sup>2</sup>C BUS START/STOP BITS TIMING

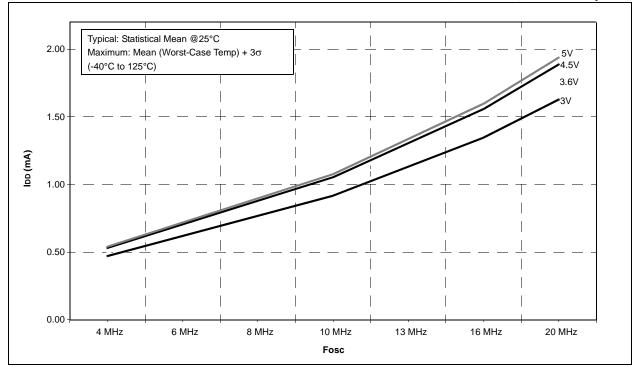

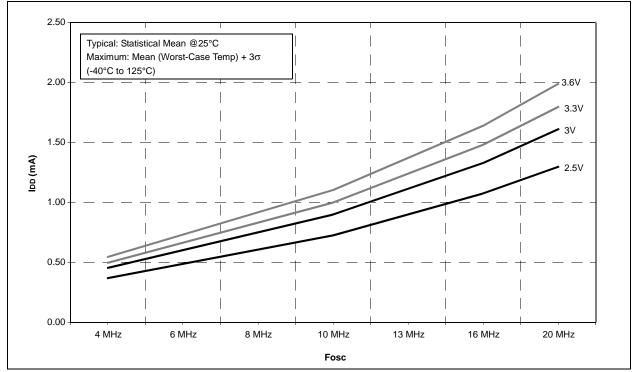

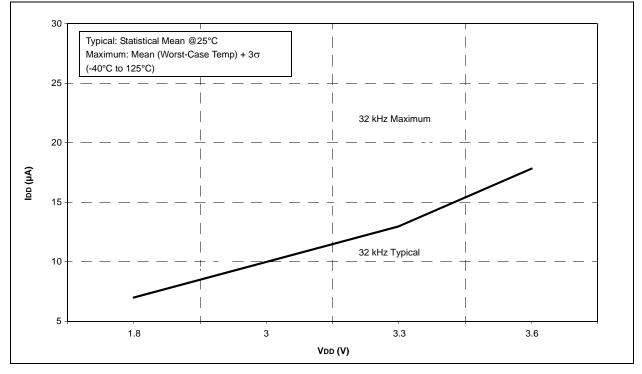

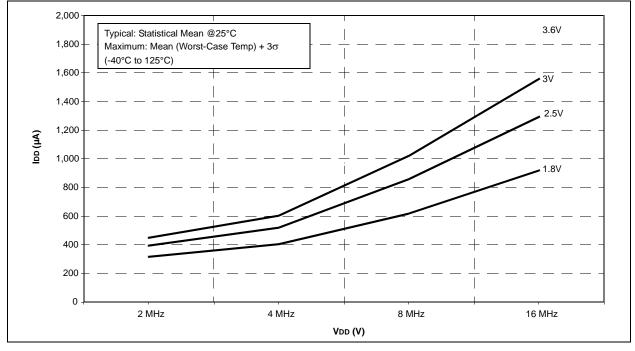

FIGURE 24-25: PIC16F722/3/4/6/7 TYPICAL IDD vs. Fosc OVER VDD, INTOSC MODE, VCAP =  $0.1 \mu F$

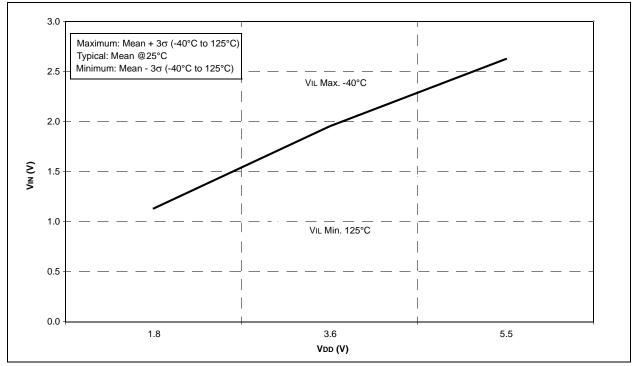

FIGURE 24-51: SCHMITT TRIGGER INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

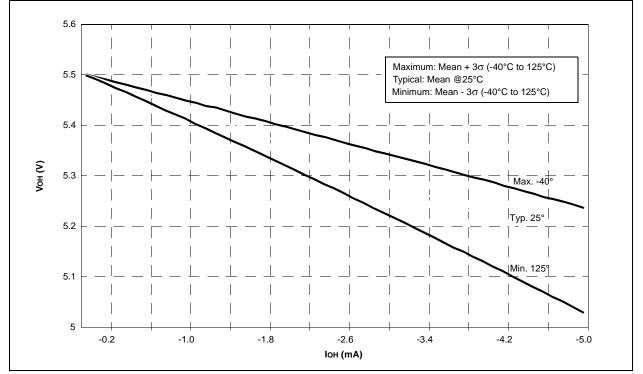

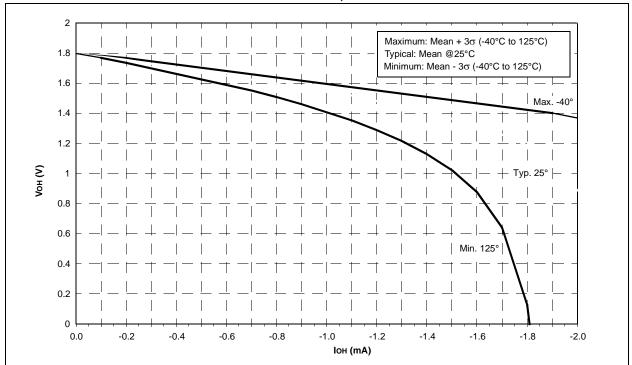

FIGURE 24-54: VOH vs. IOH OVER TEMPERATURE, VDD = 1.8V