#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

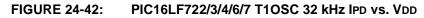

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 11x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf723-e-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

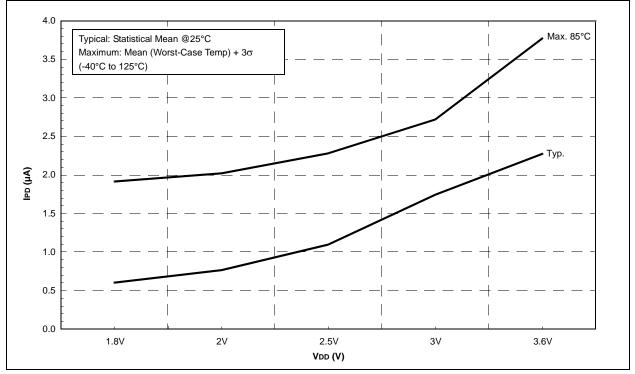

## Pin Diagrams - 28-PIN PDIP/SOIC/SSOP/QFN/UQFN (PIC16F722/723/726/PIC16LF722/723/726)

| Name                                                                      | Function | Input<br>Type | Output<br>Type | Description                                                                                              |  |  |  |

|---------------------------------------------------------------------------|----------|---------------|----------------|----------------------------------------------------------------------------------------------------------|--|--|--|

| RD3/CPS11                                                                 | RD3      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |  |

|                                                                           | CPS11    | AN            | —              | Capacitive sensing input 11.                                                                             |  |  |  |

| RD4/CPS12                                                                 | RD4      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |  |

|                                                                           | CPS12    | AN            | —              | Capacitive sensing input 12.                                                                             |  |  |  |

| RD5/CPS13                                                                 | RD5      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |  |

|                                                                           | CPS13    | AN            | —              | Capacitive sensing input 13.                                                                             |  |  |  |

| RD6/CPS14                                                                 | RD6      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |  |

|                                                                           | CPS14    | AN            | _              | Capacitive sensing input 14.                                                                             |  |  |  |

| RD7/CPS15                                                                 | RD7      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |  |

|                                                                           | CPS15    | AN            | _              | Capacitive sensing input 15.                                                                             |  |  |  |

| RE0/AN5                                                                   | RE0      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |  |

|                                                                           | AN5      | AN            | —              | A/D Channel 5 input.                                                                                     |  |  |  |

| RE1/AN6                                                                   | RE1      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |  |

|                                                                           | AN6      | AN            | —              | A/D Channel 6 input.                                                                                     |  |  |  |

| RE2/AN7                                                                   | RE2      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |  |

|                                                                           | AN7      | AN            | _              | A/D Channel 7 input.                                                                                     |  |  |  |

| RE3/MCLR/Vpp                                                              | RE3      | TTL           | —              | General purpose input.                                                                                   |  |  |  |

|                                                                           | MCLR     | ST            | _              | Master Clear with internal pull-up.                                                                      |  |  |  |

|                                                                           | Vpp      | ΗV            | —              | Programming voltage.                                                                                     |  |  |  |

| VDD                                                                       | Vdd      | Power         | —              | Positive supply.                                                                                         |  |  |  |

| Vss                                                                       | Vss      | Power         | _              | Ground reference.                                                                                        |  |  |  |

| Legend: AN = Analog input or<br>TTL = TTL compatible<br>HV = High Voltage | input ST |               | nitt Trigger   | ble input or output OD = Open Drain<br>input with CMOS levels $I^2C$ = Schmitt Trigger input with $I^2C$ |  |  |  |

## TABLE 1-1: PIC16(L)F722/3/4/6/7 PINOUT DESCRIPTION (CONTINUED)

**Note:** The PIC16F722/3/4/6/7 devices have an internal low dropout voltage regulator. An external capacitor must be connected to one of the available VCAP pins to stabilize the regulator. For more information, see **Section 5.0 "Low Dropout (LDO) Voltage Regulator**". The PIC16LF722/3/4/6/7 devices do not have the voltage regulator and therefore no external capacitor is required.

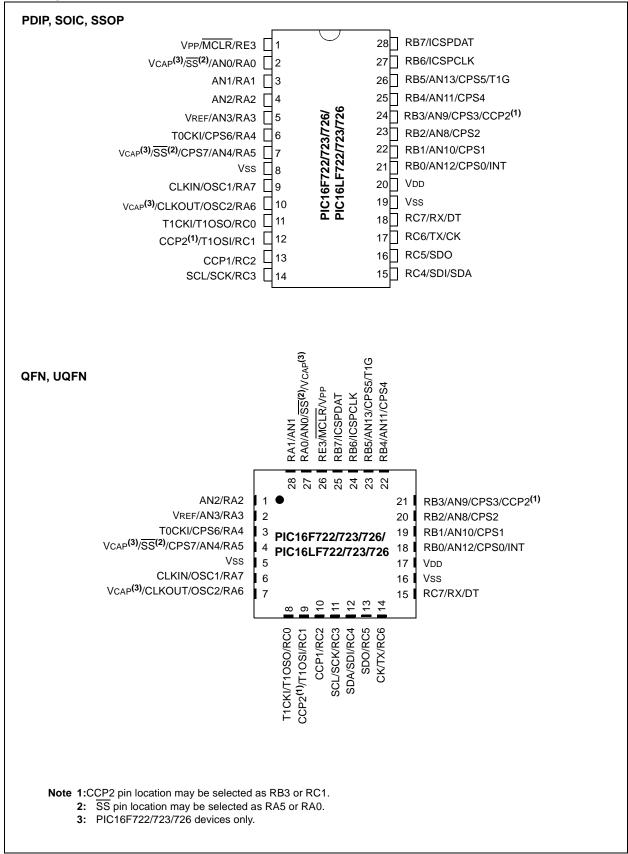

## REGISTER 6-5: PORTB: PORTB REGISTER

| R/W-x                                                                | R/W-x | R/W-x | R/W-x | R/W-x           | R/W-x | R/W-x | R/W-x |  |

|----------------------------------------------------------------------|-------|-------|-------|-----------------|-------|-------|-------|--|

| RB7                                                                  | RB6   | RB5   | RB4   | RB3             | RB2   | RB1   | RB0   |  |

| bit 7                                                                |       |       |       |                 |       |       | bit 0 |  |

|                                                                      |       |       |       |                 |       |       |       |  |

| Legend:                                                              |       |       |       |                 |       |       |       |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |       |                 |       |       |       |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x            |       |       |       | x = Bit is unkr |       |       |       |  |

bit 7-0 **RB<7:0>**: PORTB I/O Pin bit 1 = Port pin is > VIH 0 = Port pin is < VIL

## REGISTER 6-6: TRISB: PORTB TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 TRISB<7:0>: PORTB Tri-State Control bit

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

| REGISTER      | <b>19-2.</b> ADCO              |                        | ITROL REG        |                    |                    |                  |        |

|---------------|--------------------------------|------------------------|------------------|--------------------|--------------------|------------------|--------|

| U-0           | R/W-0                          | R/W-0                  | R/W-0            | U-0                | U-0                | R/W-0            | R/W-0  |

| _             | ADCS2                          | ADCS1                  | ADCS0            | _                  | _                  | ADREF1           | ADREF0 |

| bit 7         |                                |                        |                  |                    |                    |                  | bit 0  |

| Legend:       |                                |                        |                  |                    |                    |                  |        |

| R = Readabl   | le bit                         | W = Writable bi        | t                | U = Unimpleme      | ented bit, read as | s 'O'            |        |

| -n = Value at | t POR                          | '1' = Bit is set       |                  | '0' = Bit is clear | red                | x = Bit is unkno | wn     |

|               |                                |                        |                  |                    |                    |                  |        |

| bit 7         | Unimplemente                   | ed: Read as '0'        |                  |                    |                    |                  |        |

| bit 6-4       | ADCS<2:0>: A                   | /D Conversion C        | lock Select bits |                    |                    |                  |        |

|               | 000 = Fosc/2                   |                        |                  |                    |                    |                  |        |

|               | 001 = Fosc/8                   |                        |                  |                    |                    |                  |        |

|               | 010 = Fosc/32                  | -                      |                  |                    |                    |                  |        |

|               | · · ·                          | ock supplied from      | a dedicated RC   | Coscillator)       |                    |                  |        |

|               | 100 = Fosc/4<br>101 = Fosc/16  |                        |                  |                    |                    |                  |        |

|               | 101 = FOSC/10<br>110 = FOSC/64 | -                      |                  |                    |                    |                  |        |

|               |                                | ,<br>ock supplied from | a dedicated RC   | coscillator)       |                    |                  |        |

| bit 3-2       | Unimplemente                   | ••                     |                  | ,                  |                    |                  |        |

| bit 1-0       | ADREF<1:0>:                    | Voltage Referend       | e Configuration  | bits               |                    |                  |        |

|               |                                | connected to VDD       | 0                |                    |                    |                  |        |

|               | 10 = VREF is c                 | connected to exte      | rnal VREF (RA3   | /AN3)              |                    |                  |        |

|               |                                |                        | nal Fixed Voltag |                    |                    |                  |        |

## REGISTER 9-2: ADCON1: A/D CONTROL REGISTER 1

#### REGISTER 9-3: ADRES: ADC RESULT REGISTER

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 | ADRES1 | ADRES0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 **ADRES<7:0>**: ADC Result Register bits 8-bit conversion result.

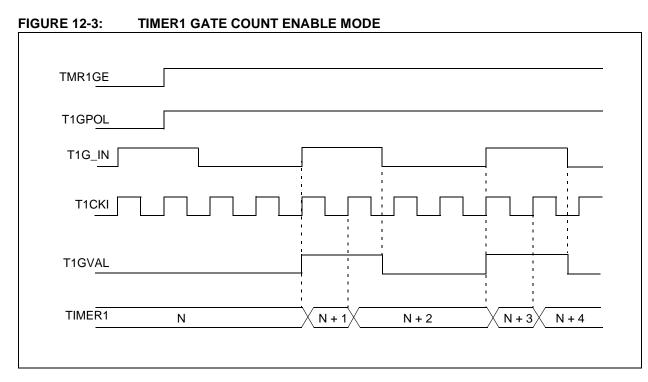

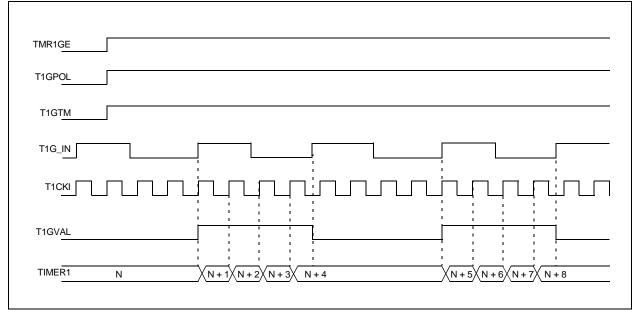

## FIGURE 12-4: TIMER1 GATE TOGGLE MODE

| FIGURE 12-6:           | TIMER1 GATE SINGLE                                          | -PULSE AND TOGGLE COMBINED MODE                  |

|------------------------|-------------------------------------------------------------|--------------------------------------------------|

| TMR1GE                 |                                                             |                                                  |

| T1GPOL                 |                                                             |                                                  |

| T1GSPM                 |                                                             |                                                  |

| T1GTM                  |                                                             |                                                  |

| T1GG <u>O/</u><br>DONE | ← Set by software<br>Counting enabled<br>rising edge of T10 | Cleared by hardware on<br>falling edge of T1GVAL |

| T1G_IN                 |                                                             |                                                  |

| тіскі                  |                                                             |                                                  |

| T1GVAL                 |                                                             |                                                  |

| TIMER1                 | Ν                                                           | N+1 $N+2$ $N+3$ $N+4$                            |

| TMR1GIF                | - Cleared by software                                       | Set by hardware on<br>falling edge of T1GVAL —   |

| Name    | Bit 7       | Bit 6          | Bit 5         | Bit 4          | Bit 3                   | Bit 2       | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------|----------------|---------------|----------------|-------------------------|-------------|--------|--------|----------------------|---------------------------------|

| ANSELB  | —           | —              | ANSB5         | ANSB4          | ANSB3                   | ANSB2       | ANSB1  | ANSB0  | 11 1111              | 11 1111                         |

| CCP1CON | _           | _              | DC1B1         | DC1B0          | CCP1M3                  | CCP1M2      | CCP1M1 | CCP1M0 | 00 0000              | 00 0000                         |

| CCP2CON | _           | _              | DC2B1         | DC2B0          | CCP2M3                  | CCP2M2      | CCP2M1 | CCP2M0 | 00 0000              | 00 0000                         |

| INTCON  | GIE         | PEIE           | T0IE          | INTE           | RBIE                    | T0IF        | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1    | TMR1GIE     | ADIE           | RCIE          | TXIE           | SSPIE                   | CCP1IE      | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1    | TMR1GIF     | ADIF           | RCIF          | TXIF           | SSPIF                   | CCP1IF      | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PORTB   | RB7         | RB6            | RB5           | RB4            | RB3                     | RB2         | RB1    | RB0    | XXXX XXXX            | xxxx xxxx                       |

| TMR1H   | Holding Reg | gister for the | Most Signific | ant Byte of th | he 16-bit TMI           | R1 Register |        |        | XXXX XXXX            | uuuu uuuu                       |

| TMR1L   | Holding Reg | gister for the | Least Signifi | cant Byte of   | the 16-bit TM           | R1 Register |        |        | XXXX XXXX            | uuuu uuuu                       |

| TRISB   | TRISB7      | TRISB6         | TRISB5        | TRISB4         | TRISB3                  | TRISB2      | TRISB1 | TRISB0 | 1111 1111            | 1111 1111                       |

| TRISC   | TRISC7      | TRISC6         | TRISC5        | TRISC4         | TRISC3                  | TRISC2      | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| T1CON   | TMR1CS1     | TMR1CS0        | T1CKPS1       | T1CKPS0        | T1OSCEN                 | T1SYNC      | —      | TMR1ON | 0000 00-0            | uuuu uu-u                       |

| T1GCON  | TMR1GE      | T1GPOL         | T1GTM         | T1GSPM         | T <u>1GGO</u> /<br>DONE | T1GVAL      | T1GSS1 | T1GSS0 | 00x0 0x00            | uuuu uxuu                       |

#### TABLE 12-6: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

## 17.1.2 SLAVE MODE

For any SPI device acting as a slave, the data is transmitted and received as external clock pulses appear on SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

#### 17.1.2.1 Slave Mode Operation

The SSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready.

The slave has no control as to when data will be clocked in or out of the device. All data that is to be transmitted, to a master or another slave, must be loaded into the SSPBUF register before the first clock pulse is received.

Once eight bits of data have been received:

- · Received byte is moved to the SSPBUF register

- BF bit of the SSPSTAT register is set

- SSPIF bit of the PIR1 register is set

Any write to the SSPBUF register during transmission/reception of data will be ignored and the Write Collision Detect bit, WCOL of the SSPCON register, will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

The user's firmware must read SSPBUF, clearing the BF flag, or the SSPOV bit of the SSPCON register will be set with the reception of the next byte and communication will be disabled.

A SPI module transmits and receives at the same time, occasionally causing dummy data to be transmitted/received. It is up to the user to determine which data is to be used and what can be discarded.

## 17.1.2.2 Enabling Slave I/O

To enable the serial port, the SSPEN bit of the SSPCON register must be set. If a Slave mode of operation is selected in the SSPM bits of the SSPCON register, the SDI, SDO, SCK pins will be assigned as serial port pins.

For these pins to function as serial port pins, they must have their corresponding data direction bits set or cleared in the associated TRIS register as follows:

- SDI configured as input

- SDO configured as output

- SCK configured as input

Optionally, a fourth pin, Slave Select  $(\overline{SS})$  may be used in Slave mode. Slave Select may be configured to operate on one of the following pins via the SSSEL bit in the APFCON register.

- RA5/AN4/SS

- RA0/AN0/SS

Upon selection of a Slave Select pin, the appropriate bits must be set in the ANSELA and TRISA registers. Slave Select must be set as an input by setting the corresponding bit in TRISA, and digital I/O must be enabled on the SS pin by clearing the corresponding bit of the ANSELA register.

#### 17.1.2.3 Slave Mode Setup

When initializing the SSP module to SPI Slave mode, compatibility must be ensured with the master device. This is done by programming the appropriate control bits of the SSPCON and SSPSTAT registers. These control bits allow the following to be specified:

- · SCK as clock input

- Idle state of SCK (CKP bit)

- Data input sample phase (SMP bit)

- Output data on rising/falling edge of SCK (CKE bit)

Figure 17-4 and Figure 17-5 show example waveforms of Slave mode operation.

| Name    | Bit 7       | Bit 6          | Bit 5       | Bit 4        | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on all<br>other Resets |

|---------|-------------|----------------|-------------|--------------|----------|--------|---------|---------|----------------------|------------------------------|

| ANSELA  | —           | —              | ANSA5       | ANSA4        | ANSA3    | ANSA2  | ANSA1   | ANSA0   | 11 1111              | 11 1111                      |

| APFCON  | —           | —              | _           | —            | _        | _      | SSSEL   | CCP2SEL | 00                   | 00                           |

| INTCON  | GIE         | PEIE           | T0IE        | INTE         | RBIE     | T0IF   | INTF    | RBIF    | 0000 000x            | 0000 000x                    |

| PIE1    | TMR1GIE     | ADIE           | RCIE        | TXIE         | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                    |

| PIR1    | TMR1GIF     | ADIF           | RCIF        | TXIF         | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                    |

| PR2     | Timer2 Peri | iod Register   | •           | •            |          |        |         | •       | 1111 1111            | 1111 1111                    |

| SSPBUF  | Synchronou  | us Serial Port | Receive But | fer/Transmit | Register |        |         |         | XXXX XXXX            | uuuu uuuu                    |

| SSPCON  | WCOL        | SSPOV          | SSPEN       | CKP          | SSPM3    | SSPM2  | SSPM1   | SSPM0   | 0000 0000            | 0000 0000                    |

| SSPSTAT | SMP         | CKE            | D/A         | Р            | S        | R/W    | UA      | BF      | 0000 0000            | 0000 0000                    |

| TRISA   | TRISA7      | TRISA6         | TRISA5      | TRISA4       | TRISA3   | TRISA2 | TRISA1  | TRISA0  | 1111 1111            | 1111 1111                    |

| TRISC   | TRISC7      | TRISC6         | TRISC5      | TRISC4       | TRISC3   | TRISC2 | TRISC1  | TRISC0  | 1111 1111            | 1111 1111                    |

| T2CON   | _           | TOUTPS3        | TOUTPS2     | TOUTPS1      | TOUTPS0  | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                    |

## TABLE 17-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode.

## REGISTER 17-4: SSPSTAT: SYNCHRONOUS SERIAL PORT STATUS REGISTER (I<sup>2</sup>C MODE)

| R/W-0           | R/W-0                                                 | R-0                                                                                | R-0                        | R-0                                                              | R-0                             | R-0                     | R-0           |

|-----------------|-------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------|---------------------------------|-------------------------|---------------|

| SMP             | CKE                                                   | D/A                                                                                | Р                          | S                                                                | R/W                             | UA                      | BF            |

| bit 7           |                                                       |                                                                                    |                            |                                                                  |                                 |                         | bit 0         |

|                 |                                                       |                                                                                    |                            |                                                                  |                                 |                         |               |

| Legend:         |                                                       |                                                                                    |                            |                                                                  |                                 | (0)                     |               |

| R = Readable    |                                                       | W = Writable bi                                                                    | t                          |                                                                  | ented bit, read                 |                         |               |

| -n = Value at F | POR                                                   | '1' = Bit is set                                                                   |                            | '0' = Bit is clea                                                | ired                            | x = Bit is unkno        | own           |

| bit 7           | 1 = Slew Rate                                         | Input Sample Pl<br>Control (limiting)<br>Control (limiting)                        | disabled. Oper             | ating in I <sup>2</sup> C Star<br>ating in I <sup>2</sup> C Fast | dard Mode (100<br>Mode (400 kHz | ) kHz and 1 MHz).<br>). |               |

| bit 6           |                                                       | < Edge Select bit<br>e maintained clea                                             |                            | mode only.                                                       |                                 |                         |               |

| bit 5           | 1 = Indicates th                                      | DRESS bit (I <sup>2</sup> C n<br>lat the last byte r<br>lat the last byte r        | eceived or tran            |                                                                  |                                 |                         |               |

| bit 4           | 1 = Indicates th                                      | ed when the SSI<br>hat a Stop bit has<br>s not detected la                         | been detected              | -                                                                |                                 | etected last.           |               |

| bit 3           | 1 = Indicates th                                      | ed when the SSI<br>at a Start bit has<br>s not detected la                         | been detected              | -                                                                | •                               | tected last.            |               |

| bit 2           | This bit holds th                                     | RITE bit Informat<br>le R/W bit informat<br>t bit, Stop bit or 7                   | ation following t          | he last address i                                                | natch. This bit is              | s only valid from the   | address match |

| bit 1           | 1 = Indicates th                                      | dress bit (10-bit<br>at the user need<br>es not need to b                          | s to update the            |                                                                  | SSPADD registe                  | er                      |               |

| bit 0           | 0 = Receive no<br><u>Transmit:</u><br>1 = Transmit in | Status bit<br>mplete, SSPBUF<br>t complete, SSP<br>progress, SSPB<br>mplete, SSPBU | BUF is empty<br>UF is full |                                                                  |                                 |                         |               |

| Mnemonic,<br>Operands |      | Description                                      | Cycles       |       | 14-Bit | Opcode | Status | Neter    |         |

|-----------------------|------|--------------------------------------------------|--------------|-------|--------|--------|--------|----------|---------|

|                       |      | Description                                      | Cycles       | MSb   |        |        | LSb    | Affected | Notes   |

|                       |      | BYTE-ORIENTED FILE                               | REGISTER OPE | RATIC | ONS    |        |        |          |         |

| ADDWF                 | f, d | Add W and f                                      | 1            | 00    | 0111   | dfff   | ffff   | C, DC, Z | 1, 2    |

| ANDWF                 | f, d | AND W with f                                     | 1            | 00    | 0101   | dfff   | ffff   | Z        | 1, 2    |

| CLRF                  | f    | Clear f                                          | 1            | 00    | 0001   | lfff   | ffff   | Z        | 2       |

| CLRW                  | -    | Clear W                                          | 1            | 00    | 0001   | 0xxx   | xxxx   | Z        |         |

| COMF                  | f, d | Complement f                                     | 1            | 00    | 1001   | dfff   | ffff   | Z        | 1, 2    |

| DECF                  | f, d | Decrement f                                      | 1            | 00    | 0011   | dfff   | ffff   | Z        | 1, 2    |

| DECFSZ                | f, d | Decrement f, Skip if 0                           | 1 <b>(2)</b> | 00    | 1011   | dfff   | ffff   |          | 1, 2, 3 |

| INCF                  | f, d | Increment f                                      | 1            | 00    | 1010   | dfff   | ffff   | Z        | 1, 2    |

| INCFSZ                | f, d | Increment f, Skip if 0                           | 1 <b>(2)</b> | 00    | 1111   | dfff   | ffff   |          | 1, 2, 3 |

| IORWF                 | f, d | Inclusive OR W with f                            | 1            | 00    | 0100   | dfff   | ffff   | Z        | 1, 2    |

| MOVF                  | f, d | Move f                                           | 1            | 00    | 1000   | dfff   | ffff   | Z        | 1, 2    |

| MOVWF                 | f    | Move W to f                                      | 1            | 00    | 0000   | lfff   | ffff   |          | -       |

| NOP                   | -    | No Operation                                     | 1            | 00    | 0000   | 0xx0   | 0000   |          |         |

| RLF                   | f, d | Rotate Left f through Carry                      | 1            | 00    | 1101   | dfff   | ffff   | С        | 1, 2    |

| RRF                   | f, d | Rotate Right f through Carry                     | 1            | 00    | 1100   | dfff   | ffff   | С        | 1, 2    |

| SUBWF                 | f, d | Subtract W from f                                | 1            | 00    | 0010   | dfff   | ffff   | C, DC, Z | 1, 2    |

| SWAPF                 | f, d | Swap nibbles in f                                | 1            | 00    | 1110   | dfff   | ffff   |          | 1, 2    |

| XORWF                 | f, d | Exclusive OR W with f                            | 1            | 00    | 0110   | dfff   | ffff   | Z        | 1, 2    |

|                       |      | BIT-ORIENTED FILE R                              | EGISTER OPER | RATIO | NS     |        |        |          |         |

| BCF                   | f, b | Bit Clear f                                      | 1            | 01    | 00bb   | bfff   | ffff   |          | 1, 2    |

| BSF                   | f, b | Bit Set f                                        | 1            | 01    |        | bfff   | ffff   |          | 1, 2    |

| BTFSC                 | f, b | Bit Test f, Skip if Clear                        | 1 <b>(2)</b> | 01    | 10bb   | bfff   | ffff   |          | 3       |

| BTFSS                 | f, b | Bit Test f, Skip if Set                          | 1 (2)        | 01    | 11bb   | bfff   | ffff   |          | 3       |

|                       |      | LITERAL AND CON                                  | ITROL OPERAT | IONS  |        |        |        |          |         |

| ADDLW                 | k    | Add literal and W                                | 1            | 11    | 111x   | kkkk   | kkkk   | C, DC, Z |         |

| ANDLW                 | k    | AND literal with W                               | 1            | 11    | 1001   | kkkk   | kkkk   | Z        |         |

| CALL                  | k    | Call Subroutine                                  | 2            | 10    | 0kkk   | kkkk   | kkkk   |          |         |

| CLRWDT                | -    | Clear Watchdog Timer                             | 1            | 00    | 0000   | 0110   | 0100   | TO, PD   |         |

| GOTO                  | k    | Go to address                                    | 2            | 10    | 1kkk   | kkkk   | kkkk   |          |         |

| IORLW                 | k    | Inclusive OR literal with W                      | 1            | 11    | 1000   | kkkk   | kkkk   | Z        |         |

| MOVLW                 | k    | Move literal to W                                | 1            | 11    | 00xx   | kkkk   | kkkk   |          |         |

| RETFIE                | -    | Return from interrupt                            | 2            | 00    | 0000   | 0000   | 1001   |          |         |

| RETLW                 | k    | Return with literal in W                         | 2            | 11    | 01xx   | kkkk   | kkkk   |          |         |

| RETURN                | _    | Return from Subroutine                           | 2            | 00    | 0000   | 0000   | 1000   |          |         |

| SLEEP                 | _    | Go into Standby mode                             | 1            | 00    | 0000   | 0110   | 0011   | TO, PD   |         |

| SUBLW                 | k    | Subtract W from literal                          | 1            | 11    |        | kkkk   |        | C, DC, Z |         |

| XORLW                 | k    | Exclusive OR literal with W                      | 1            | 11    |        | kkkk   |        | Z        |         |

| Noto 1                |      | 1/O register is modified as a function of itself |              | I     |        |        |        | I        | l       |

## TABLE 21-2: PIC16(L)F722/3/4/6/7 INSTRUCTION SET

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF PORTA, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

**3:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

## 22.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

## 22.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 22.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 22.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

## 23.4 DC Characteristics: PIC16(L)F722/3/4/6/7-I/E (Continued)

|              |        |                                                  | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |      |       |                                                                         |  |  |

|--------------|--------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------------------------------------------------------------------------|--|--|

| Param<br>No. | Sym.   | Characteristic                                   | Min.                                                                                                                                                                                           | Тур† | Max. | Units | Conditions                                                              |  |  |

| D130         | Eр     | Cell Endurance                                   | 100                                                                                                                                                                                            | 1k   | —    | E/W   | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

| D131         |        | VDD for Read                                     | Vmin                                                                                                                                                                                           | —    | _    | V     |                                                                         |  |  |

|              |        | Voltage on MCLR/VPP during<br>Erase/Program      | 8.0                                                                                                                                                                                            | _    | 9.0  | V     | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

|              |        | VDD for Bulk Erase                               | 2.7                                                                                                                                                                                            | 3    | —    | V     | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

| D132         | VPEW   | VDD for Write or Row Erase                       | 2.7                                                                                                                                                                                            | _    | —    | V     | VMIN = Minimum operating voltage<br>VMAX = Maximum operating<br>voltage |  |  |

|              | IPPPGM | Current on MCLR/VPP during<br>Erase/Write        | —                                                                                                                                                                                              | -    | 5.0  | mA    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

|              | IDDPGM | Current on VDD during Erase/<br>Write            | —                                                                                                                                                                                              |      | 5.0  | mA    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

| D133         | TPEW   | Erase/Write cycle time                           | -                                                                                                                                                                                              |      | 2.8  | ms    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

| D134         | TRETD  | Characteristic Retention                         | 40                                                                                                                                                                                             | —    | —    | Year  | Provided no other specifications are violated                           |  |  |

|              |        | VCAP Capacitor Charging                          |                                                                                                                                                                                                |      |      |       |                                                                         |  |  |

| D135         |        | Charging current                                 | —                                                                                                                                                                                              | 200  | _    | μΑ    |                                                                         |  |  |

| D135A        |        | Source/sink capability when<br>charging complete | —                                                                                                                                                                                              | 0.0  | —    | mA    |                                                                         |  |  |

Legend: TBD = To Be Determined

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

**3:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: Including OSC2 in CLKOUT mode.

FIGURE 23-6: HFINTOSC FREQUENCY ACCURACY OVER DEVICE VDD AND TEMPERATURE

| Param<br>No. | Symbol  | Characteristic  |              | Min. | Тур | Max. | Units | Conditions                   |  |

|--------------|---------|-----------------|--------------|------|-----|------|-------|------------------------------|--|

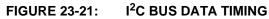

| SP90*        | TSU:STA | Start condition | 100 kHz mode | 4700 |     | _    | ns    | Only relevant for Repeated   |  |

|              |         | Setup time      | 400 kHz mode | 600  | _   | —    |       | Start condition              |  |

| SP91*        | THD:STA | Start condition | 100 kHz mode | 4000 | _   | —    | ns    | After this period, the first |  |

|              |         | Hold time       | 400 kHz mode | 600  | _   | _    |       | clock pulse is generated     |  |

| SP92*        | Tsu:sto | Stop condition  | 100 kHz mode | 4700 | —   | _    | ns    |                              |  |

|              |         | Setup time      | 400 kHz mode | 600  | _   | _    |       |                              |  |

| SP93         | THD:STO | Stop condition  | 100 kHz mode | 4000 | —   | —    | ns    |                              |  |

|              |         | Hold time       | 400 kHz mode | 600  | _   |      |       |                              |  |

## TABLE 23-12: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

\* These parameters are characterized but not tested.