Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 11x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf723-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F722/3/4/6/7

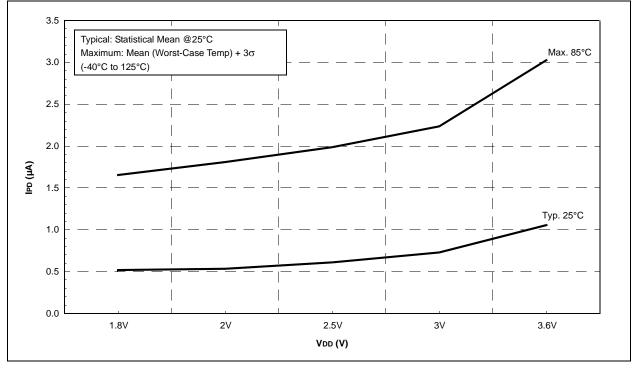

#### Pin Diagrams – 44-PIN TQFP (PIC16F724/727/PIC16LF724/727)

# PIC16(L)F722/3/4/6/7

| TABLE 2: 40/44-PIN PDIP/TQFP/QFN SUMMARY (PIC16F724/727/PIC16LF724/727) |                |                |               |          |               |                 | (27)                |        |                   |           |         |                     |

|-------------------------------------------------------------------------|----------------|----------------|---------------|----------|---------------|-----------------|---------------------|--------|-------------------|-----------|---------|---------------------|

| I/O                                                                     | 40-Pin<br>PDIP | 44-Pin<br>TQFP | 44-Pin<br>QFN | A/D      | Cap<br>Sensor | Timers          | ССР                 | AUSART | SSP               | Interrupt | Pull-Up | Basic               |

| RA0                                                                     | 2              | 19             | 19            | AN0      | -             | _               | —                   |        | SS <sup>(3)</sup> | _         | _       | VCAP <sup>(4)</sup> |

| RA1                                                                     | 3              | 20             | 20            | AN1      |               | _               | _                   |        | _                 | _         | _       | _                   |

| RA2                                                                     | 4              | 21             | 21            | AN2      |               | _               | _                   |        | _                 | _         | _       | —                   |

| RA3                                                                     | 5              | 22             | 22            | AN3/VREF |               | _               | _                   |        | _                 | _         | _       | _                   |

| RA4                                                                     | 6              | 23             | 23            | —        | CPS6          | TOCKI           | —                   |        | —                 | —         | _       | _                   |

| RA5                                                                     | 7              | 24             | 24            | AN4      | CPS7          | _               | _                   |        | SS <sup>(3)</sup> | _         | —       | VCAP <sup>(4)</sup> |

| RA6                                                                     | 14             | 31             | 33            | _        |               | —               | —                   |        | —                 | —         | —       | OSC2/CLKOUT/VCAP(4) |

| RA7                                                                     | 13             | 30             | 32            | _        |               | _               | _                   |        | _                 | _         | —       | OSC1/CLKIN          |

| RB0                                                                     | 33             | 8              | 9             | AN12     | CPS0          | —               | —                   |        | —                 | IOC/INT   | Y       | _                   |

| RB1                                                                     | 34             | 9              | 10            | AN10     | CPS1          | _               | _                   |        | _                 | IOC       | Y       | _                   |

| RB2                                                                     | 35             | 10             | 11            | AN8      | CPS2          | —               | —                   |        | —                 | IOC       | Y       | _                   |

| RB3                                                                     | 36             | 11             | 12            | AN9      | CPS3          | _               | CCP2 <sup>(2)</sup> |        | _                 | IOC       | Y       | _                   |

| RB4                                                                     | 37             | 14             | 14            | AN11     | CPS4          | —               | —                   |        | —                 | IOC       | Y       | _                   |

| RB5                                                                     | 38             | 15             | 15            | AN13     | CPS5          | T1G             | _                   | _      | _                 | IOC       | Y       | —                   |

| RB6                                                                     | 39             | 16             | 16            | —        | _             | —               | —                   | _      | —                 | IOC       | Y       | ICSPCLK/ICDCLK      |

| RB7                                                                     | 40             | 17             | 17            | _        | _             | _               | _                   | _      | _                 | IOC       | Y       | ICSPDAT/ICDDAT      |

| RC0                                                                     | 15             | 32             | 34            | _        |               | T1OSO/<br>T1CKI | —                   |        | —                 | —         | —       | —                   |

| RC1                                                                     | 16             | 35             | 35            | _        | -             | T1OSI           | CCP2 <sup>(2)</sup> | _      | _                 | _         | _       | —                   |

| RC2                                                                     | 17             | 36             | 36            | —        | _             | _               | CCP1                | _      | _                 | _         | _       | _                   |

| RC3                                                                     | 18             | 37             | 37            | _        | _             | _               | —                   | _      | SCK/SCL           | _         | _       | —                   |

| RC4                                                                     | 23             | 42             | 42            | _        | _             |                 | —                   | _      | SDI/SDA           | _         | _       | -                   |

| RC5                                                                     | 24             | 43             | 43            | _        | _             |                 | _                   | _      | SDO               | _         | _       | _                   |

| RC6                                                                     | 25             | 44             | 44            | _        | _             | —               | —                   | TX/CK  | _                 | _         | _       | -                   |

| RC7                                                                     | 26             | 1              | 1             | _        | _             | _               | —                   | RX/DT  | _                 | _         | _       | —                   |

| RD0                                                                     | 19             | 38             | 38            | _        | CPS8          | —               | —                   | _      | _                 | _         | _       | -                   |

| RD1                                                                     | 20             | 39             | 39            | —        | CPS9          | —               | —                   |        | —                 | —         | —       | —                   |

| RD2                                                                     | 21             | 40             | 40            | _        | CPS10         | —               | —                   |        | _                 | _         | —       | —                   |

| RD3                                                                     | 22             | 41             | 41            | —        | CPS11         | —               | —                   |        | —                 | —         | —       | —                   |

| RD4                                                                     | 27             | 2              | 2             | _        | CPS12         | —               | —                   |        | _                 | _         | —       | —                   |

| RD5                                                                     | 28             | 3              | 3             | _        | CPS13         | _               | —                   | _      | _                 | _         | _       | —                   |

| RD6                                                                     | 29             | 4              | 4             | —        | CPS14         | —               | —                   |        | —                 | —         | _       | —                   |

| RD7                                                                     | 30             | 5              | 5             | _        | CPS15         | _               | _                   |        | _                 | _         | _       | —                   |

| RE0                                                                     | 8              | 25             | 25            | AN5      | _             | _               | _                   | _      |                   | _         | _       | —                   |

| RE1                                                                     | 9              | 26             | 26            | AN6      |               | —               | _                   | _      | —                 | —         | _       | —                   |

| RE2                                                                     | 10             | 27             | 27            | AN7      |               | _               | _                   |        |                   | _         | —       | —                   |

| RE3                                                                     | 1              | 18             | 18            | _        |               | _               | _                   | _      | _                 | _         | Y(1)    | MCLR/Vpp            |

| —                                                                       | 11,32          | 7,28           | 7,8,28        | —        | —             | —               | —                   | —      | —                 | —         | —       | Vdd                 |

| _                                                                       | 12,13          | 6,29           | 6,30,31       | _        | _             | _               | _                   | _      | _                 | _         | _       | Vss                 |

#### TABLE 2:40/44-PIN PDIP/TQFP/QFN SUMMARY (PIC16F724/727/PIC16LF724/727)

**Note 1:** Pull-up enabled only with external MCLR configuration.

2: RC1 is the default pin location for CCP2. RB3 may be selected by changing the CCP2SEL bit in the APFCON register.

3: RA5 is the default pin location for SS. RA0 may be selected by changing the SSSEL bit in the APFCON register.

4: PIC16F722/3/4/6/7 devices only.

**Note:** The PIC16F722/3/4/6/7 devices have an internal low dropout voltage regulator. An external capacitor must be connected to one of the available VCAP pins to stabilize the regulator. For more information, see **Section 5.0 "Low Dropout (LDO) Voltage Regulator**". The PIC16LF722/3/4/6/7 devices do not have the voltage regulator and therefore no external capacitor is required.

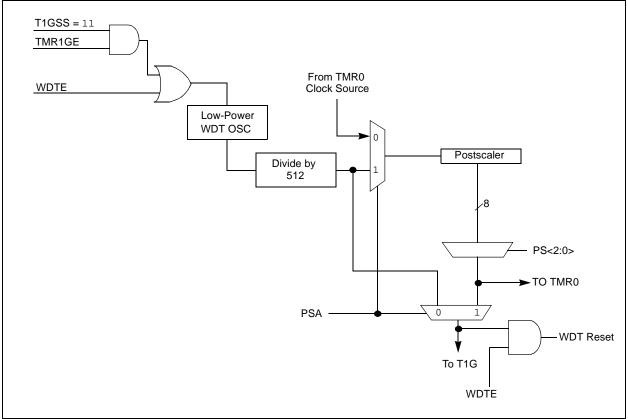

#### 3.4.2 WDT CONTROL

The WDTE bit is located in the Configuration Word Register 1. When set, the WDT runs continuously.

The PSA and PS<2:0> bits of the OPTION register control the WDT period. See **Section 11.0 "Timer0 Module"** for more information.

#### TABLE 3-1: WDT STATUS

| Conditions                                               | WDT                          |

|----------------------------------------------------------|------------------------------|

| WDTE = 0                                                 | Cleared                      |

| CLRWDT Command                                           |                              |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |

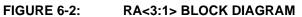

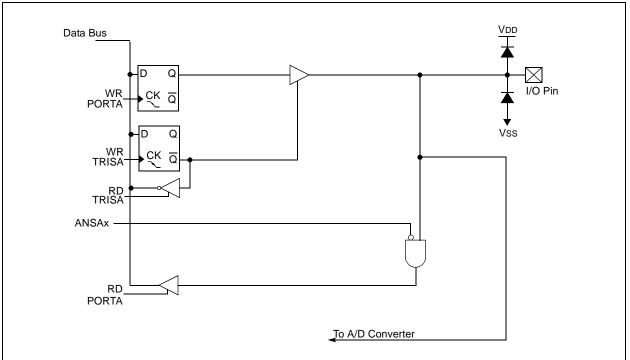

#### 6.2 PORTA and the TRISA Registers

PORTA is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 6-3). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 6-1 shows how to initialize PORTA.

Reading the PORTA register (Register 6-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISA register (Register 6-3) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the

#### REGISTER 6-2: PORTA: PORTA REGISTER

TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

| Note: | The ANSELA register must be initialized     |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | to configure an analog channel as a digital |  |  |  |  |  |

|       | input. Pins configured as analog inputs     |  |  |  |  |  |

|       | will read '0'.                              |  |  |  |  |  |

| EXAMPLE 6-1:                                                                                              | INITIALIZING PORTA                                                                                          |

|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| BANKSEL PORTA<br>CLRF PORTA<br>BANKSEL ANSELA<br>CLRF ANSELA<br>BANKSEL TRISA<br>MOVLW 0Ch<br>MOVWF TRISA | ;<br>;Init PORTA<br>;<br>;digital I/O<br>;<br>;Set RA<3:2> as inputs<br>;and set RA<7:4,1:0><br>;as outputs |

| R/W-x    | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|----------|-------|-------|-------|-------|-------|-------|-------|

| RA7      | RA6   | RA5   | RA4   | RA3   | RA2   | RA1   | RA0   |

| bit 7    |       |       |       |       |       |       | bit 0 |

|          |       |       |       |       |       |       |       |

| l egend: |       |       |       |       |       |       |       |

| Legena.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

**RA<7:0>**: PORTA I/O Pin bit 1 = Port pin is > VIH 0 = Port pin is < VIL

#### REGISTER 6-3: TRISA: PORTA TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                                                                  |                      |                    |  |

|-------------------|------------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                                 | '0' = Bit is cleared | x = Bit is unknown |  |

bit 7-0

bit 7-0

TRISA<7:0>: PORTA Tri-State Control bit

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

# PIC16(L)F722/3/4/6/7

#### REGISTER 6-5: PORTB: PORTB REGISTER

| R/W-x        | R/W-x                             | R/W-x | R/W-x                                   | R/W-x                              | R/W-x | R/W-x | R/W-x |  |

|--------------|-----------------------------------|-------|-----------------------------------------|------------------------------------|-------|-------|-------|--|

| RB7          | RB6                               | RB5   | RB4                                     | RB3                                | RB2   | RB1   | RB0   |  |

| bit 7        |                                   |       |                                         |                                    |       |       | bit 0 |  |

|              |                                   |       |                                         |                                    |       |       |       |  |

| Legend:      |                                   |       |                                         |                                    |       |       |       |  |

| R = Readable | R = Readable bit W = Writable bit |       |                                         | U = Unimplemented bit, read as '0' |       |       |       |  |

|              | n = Value at POR '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                                    |       |       |       |  |

bit 7-0 **RB<7:0>**: PORTB I/O Pin bit 1 = Port pin is > VIH 0 = Port pin is < VIL

#### REGISTER 6-6: TRISB: PORTB TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                                     |                    |  |

|-------------------|------------------|-----------------------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | V = Writable bit U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                                | x = Bit is unknown |  |

bit 7-0 TRISB<7:0>: PORTB Tri-State Control bit

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

#### 6.5 **PORTD and TRISD Registers**

PORTD is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISD (Register 6-13). Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 6-4 shows how to initialize PORTD.

Reading the PORTD register (Register 6-12) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

Note: PORTD is available on PIC16F724/LF724 and PIC16F727/LF727 only.

The TRISD register (Register 6-13) controls the PORTD pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISD register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### EXAMPLE 6-4: INITIALIZING PORTD

| BANKSEL | PORTD       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTD       | ;Init PORTD            |

| BANKSEL | ANSELD      |                        |

| CLRF    | ANSELD      | ;Make PORTD digital    |

| BANKSEL | TRISD       | ;                      |

| MOVLW   | B`00001100′ | ;Set RD<3:2> as inputs |

| MOVWF   | TRISD       | ;and set RD<7:4,1:0>   |

|         |             | ;as outputs            |

|         |             |                        |

#### 6.5.1 ANSELD REGISTER

The ANSELD register (Register 6-9) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELD bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELD bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELD register must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

#### **REGISTER 6-12: PORTD: PORTD REGISTER<sup>(1)</sup>**

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RD7   | RD6   | RD5   | RD4   | RD3   | RD2   | RD1   | RD0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 RD<7:0>: PORTD General Purpose I/O Pin bits

1 = Port pin is > VIH

0 = Port pin is < VIL

Note 1: PORTD is not implemented on PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'.

#### 6.6 PORTE and TRISE Registers

PORTE is a 4-bit wide, bidirectional port. The corresponding data direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). The exception is RE3, which is input only and its TRIS bit will always read as '1'. Example 6-5 shows how to initialize PORTE.

Reading the PORTE register (Register 6-15) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch. RE3 reads '0' when MCLRE = 1.

| Note: | RE<2:0>   | and    | TRISE<2:0>     | are    | not  |

|-------|-----------|--------|----------------|--------|------|

|       | implement | ted on | the PIC16F722  | 2/723/ | 726/ |

|       | PIC16LF7  | 22/723 | 3/726. Read as | '0'.   |      |

The TRISE register (Register 6-16) controls the PORTE pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISE register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

Note: The ANSELE register must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

#### EXAMPLE 6-5: INITIALIZING PORTE

| BANKSEL | PORTE       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTE       | ;Init PORTE            |

| BANKSEL | ANSELE      | ;                      |

| CLRF    | ANSELE      | ;digital I/O           |

| BANKSEL | TRISE       | ;                      |

| MOVLW   | B`00001100′ | ;Set RE<2> as an input |

| MOVWF   | TRISE       | ;and set RE<1:0>       |

|         |             | ;as outputs            |

|         |             |                        |

## 7.0 OSCILLATOR MODULE

#### 7.1 Overview

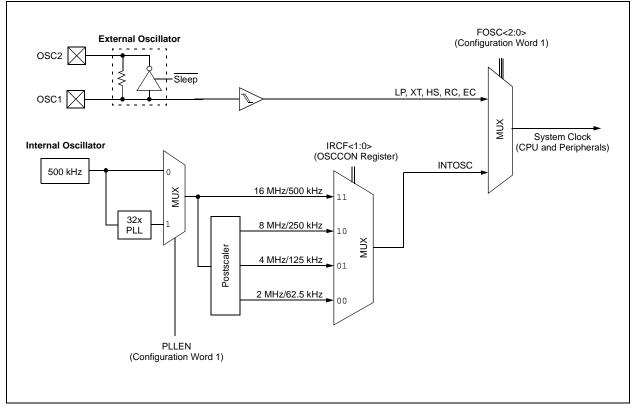

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 7-1 illustrates a block diagram of the oscillator module.

Clock sources can be configured from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system can be configured to use an internal calibrated high-frequency oscillator as clock source, with a choice of selectable speeds via software.

Clock source modes are configured by the FOSC bits in Configuration Word 1 (CONFIG1). The oscillator module can be configured for one of eight modes of operation.

- 1. RC External Resistor-Capacitor (RC) with Fosc/4 output on OSC2/CLKOUT.

- 2. RCIO External Resistor-Capacitor (RC) with I/O on OSC2/CLKOUT.

- 3. INTOSC Internal oscillator with Fosc/4 output on OSC2 and I/O on OSC1/CLKIN.

- 4. INTOSCIO Internal oscillator with I/O on OSC1/CLKIN and OSC2/CLKOUT.

- 5. EC External clock with I/O on OSC2/CLKOUT.

- 6. HS High Gain Crystal or Ceramic Resonator mode.

- 7. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode.

- 8. LP Low-Power Crystal mode.

FIGURE 7-1: SIMPLIFIED PIC<sup>®</sup> MCU CLOCK SOURCE BLOCK DIAGRAM

### 8.0 DEVICE CONFIGURATION

Device Configuration consists of Configuration Word 1 and Configuration Word 2 registers, Code Protection and Device ID.

#### 8.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 register at 2007h and Configuration Word 2 register at 2008h. These registers are only accessible during programming.

#### REGISTER 8-1: CONFIG1: CONFIGURATION WORD REGISTER 1

|        |   | R/P-1 | R/P-1 | U-1 <sup>(4)</sup> | R/P-1 | R/P-1  | R/P-1  |

|--------|---|-------|-------|--------------------|-------|--------|--------|

| —      | _ | DEBUG | PLLEN | _                  | BORV  | BOREN1 | BOREN0 |

| bit 15 |   |       |       |                    |       |        | bit 8  |

| U-1 <sup>(4)</sup> | R/P-1 |

|--------------------|-------|-------|-------|-------|-------|-------|-------|

| _                  | CP    | MCLRE | PWRTE | WDTE  | FOSC2 | FOSC1 | FOSC0 |

| bit 7              |       |       |       |       |       |       | bit 0 |

| Legend:           | P = Programmable bit |                             |                    |

|-------------------|----------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared        | x = Bit is unknown |

| bit 13              | <b>DEBUG:</b> In-Circuit Debugger Mode bit<br>1 = In-Circuit Debugger disabled, RB6/ICSPCLK and RB7/ICSPDAT are general purpose I/O pins<br>0 = In-Circuit Debugger enabled, RB6/ICSPCLK and RB7/ICSPDAT are dedicated to the debugger                            |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bit 12              | PLLEN: INTOSC PLL Enable bit<br>0 = INTOSC Frequency is 500 kHz<br>1 = INTOSC Frequency is 16 MHz (32x)                                                                                                                                                           |  |

| bit 11              | Unimplemented: Read as '1'                                                                                                                                                                                                                                        |  |

| bit 10              | <b>BORV:</b> Brown-out Reset Voltage selection bit<br>0 = Brown-out Reset Voltage (VBOR) set to 2.5 V nominal<br>1 = Brown-out Reset Voltage (VBOR) set to 1.9 V nominal                                                                                          |  |

| bit 9-8             | <b>BOREN&lt;1:0&gt;:</b> Brown-out Reset Selection bits <sup>(1)</sup><br>0x = BOR disabled (Preconditioned State)<br>10 = BOR enabled during operation and disabled in Sleep<br>11 = BOR enabled                                                                 |  |

| bit 7               | Unimplemented: Read as '1'                                                                                                                                                                                                                                        |  |

| bit 6               | <b>CP</b> : Code Protection bit <sup>(2)</sup><br>1 = Program memory code protection is disabled<br>0 = Program memory code protection is enabled                                                                                                                 |  |

| bit 5               | MCLRE: <u>RE3/MCLR</u> pin function select bit <sup>(3)</sup><br>1 = RE3/ <u>MCLR</u> pin function is MCLR<br>0 = RE3/MCLR pin function is digital input, MCLR internally tied to VDD                                                                             |  |

| Note 1:<br>2:<br>3: | Enabling Brown-out Reset does not automatically enable Power-up Timer.<br>The entire program memory will be erased when the code protection is turned off.<br>When $\overline{MCLR}$ is asserted in INTOSC or RC mode, the internal clock oscillator is disabled. |  |

**4:** MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

#### 9.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

- **Note 1:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

- **2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the GIE and PEIE bits of the INTCON register must be disabled. If the GIE and PEIE bits of the INT-CON register are enabled, execution will switch to the Interrupt Service Routine.

Please refer to **Section 9.1.5** "Interrupts" for more information.

### 9.2 ADC Operation

#### 9.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

Note: The GO/DONE bit should not be set in the same instruction that turns on the ADC. Refer to Section 9.2.6 "A/D Conversion Procedure".

#### 9.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRES register with new conversion result

#### 9.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRES register will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

| Note: | A device Reset forces all registers to their |

|-------|----------------------------------------------|

|       | Reset state. Thus, the ADC module is         |

|       | turned off and any pending conversion is     |

|       | terminated.                                  |

#### 9.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 9.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCP module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 15.0 "Capture/Compare/PWM (CCP) Module" for more information.

#### 11.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the OPTION register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

| Note: | When the prescaler is assigned to WDT, a    |

|-------|---------------------------------------------|

|       | CLRWDT instruction will clear the prescaler |

|       | along with the WDT.                         |

#### 11.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The T0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The T0IF bit can only be cleared in software. The Timer0 interrupt enable is the T0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |

|-------|-----------------------------------------|

|       | processor from Sleep since the timer is |

|       | frozen during Sleep.                    |

#### 11.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 23.0** "**Electrical Specifications**".

#### TABLE 12-5: WDT/TIMER1 GATE INTERACTION

| WDTE | TMR1GE = 1<br>and<br>T1GSS = 11 | WDT Oscillator<br>Enable | WDT Reset | Wake-up | WDT Available for<br>T1G Source |

|------|---------------------------------|--------------------------|-----------|---------|---------------------------------|

| 1    | N                               | Y                        | Y         | Y       | N                               |

| 1    | Y                               | Y                        | Y         | Y       | Y                               |

| 0    | Y                               | Y                        | N         | N       | Y                               |

| 0    | Ν                               | N                        | N         | N       | N                               |

#### 12.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 Gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 12-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

**Note:** Enabling Toggle mode at the same time as changing the gate polarity may result in indeterminate operation.

# 12.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software.

Clearing the T1GSPM bit of the T1GCON register will also clear the T1GGO/DONE bit. See Figure 12-5 for timing details.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 Gate source to be measured. See Figure 12-6 for timing details.

#### 12.6.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 Gate is not enabled (TMR1GE bit is cleared).

#### 12.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 Gate is not enabled (TMR1GE bit is cleared).

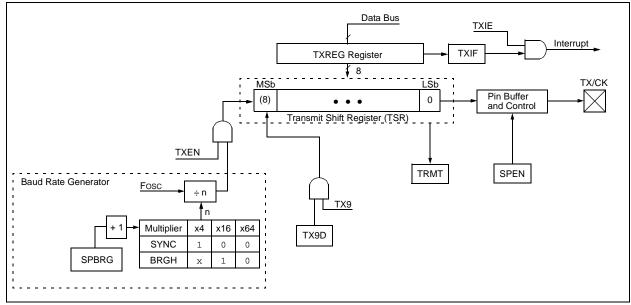

### 16.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (AUSART)

The Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The AUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The AUSART module includes the following capabilities:

- Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- Address detection in 9-bit mode

- Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- Half-duplex synchronous slave

- Sleep operation

Block diagrams of the AUSART transmitter and receiver are shown in Figure 16-1 and Figure 16-2.

#### FIGURE 16-1: AUSART TRANSMIT BLOCK DIAGRAM

#### 16.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the AUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | FIFO have framing errors, repeated reads  |  |  |  |  |  |  |  |

|       | of the RCREG will not clear the FERR bit. |  |  |  |  |  |  |  |

#### 16.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by setting the AUSART by clearing the SPEN bit of the RCSTA register.

#### 16.1.2.6 Receiving 9-bit Characters

The AUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the AUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

#### 16.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit of the PIR1 register. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

# PIC16(L)F722/3/4/6/7

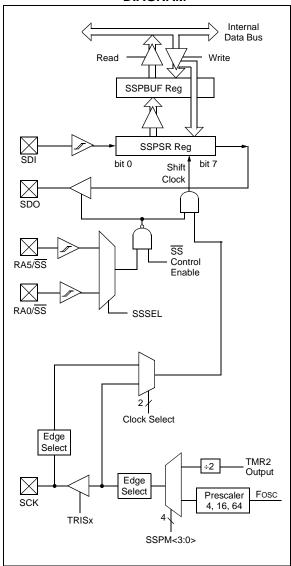

FIGURE 17-2: SPI MODE BLOCK DIAGRAM

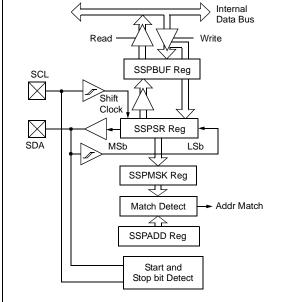

### 17.2 I<sup>2</sup>C Mode

The SSP module, in  $I^2C$  mode, implements all slave functions, except general call support. It provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the  $I^2C$  Standard mode specifications:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- Start and Stop bit interrupts enabled to support firmware Master mode

- · Address masking

Two pins are used for data transfer; the SCL pin (clock line) and the SDA pin (data line). The user must configure the two pin's data direction bits as inputs in the appropriate TRIS register. Upon enabling  $I^2C$  mode, the  $I^2C$  slew rate limiters in the I/O pads are controlled by the SMP bit of SSPSTAT register. The SSP module functions are enabled by setting the SSPEN bit of SSPCON register.

Data is sampled on the rising edge and shifted out on the falling edge of the clock. This ensures that the SDA signal is valid during the SCL high time. The SCL clock input must have minimum high and low times for proper operation. Refer to **Section 23.0** "**Electrical Specifications**".

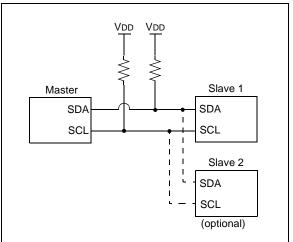

# FIGURE 17-7: I<sup>2</sup>C MODE BLOCK DIAGRAM

## FIGURE 17-8: TYPICAL I<sup>2</sup>C

#### CONNECTIONS

The SSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. They are:

- SSP Control (SSPCON) register

- SSP Status (SSPSTAT) register

- Serial Receive/Transmit Buffer (SSPBUF) register

- SSP Shift Register (SSPSR), not directly accessible

- SSP Address (SSPADD) register

- SSP Address Mask (SSPMSK) register

#### 17.2.1 HARDWARE SETUP

Selection of  $I^2C$  mode, with the SSPEN bit of the SSPCON register set, forces the SCL and SDA pins to be open drain, provided these pins are programmed as inputs by setting the appropriate TRISC bits. The SSP module will override the input state with the output data, when required, such as for Acknowledge and slave-transmitter sequences.

**Note:** Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module

#### 23.3 DC Characteristics: PIC16(L)F722/3/4/6/7-I/E (Power-Down)

| PIC16LF722/3/4/6/7<br>PIC16F722/3/4/6/7 |                             |          |                                                      |               |                |       |                     |                                         |  |

|-----------------------------------------|-----------------------------|----------|------------------------------------------------------|---------------|----------------|-------|---------------------|-----------------------------------------|--|

|                                         |                             |          | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |               |                |       | °C for industrial   |                                         |  |

| Param<br>No.                            | Device Characteristics Min. |          | Тур†                                                 | Max.<br>+85°C | Max.<br>+125°C | Units | Conditions VDD Note |                                         |  |

| -                                       | Power-down Base Current     | (100)(2) |                                                      |               |                |       | VDD                 | Note                                    |  |

| D020                                    | rower-down base current     | (IFD). / | 0.02                                                 | 0.7           | 3.9            | μA    | 1.8                 | WDT, BOR, FVR, and T1OSC                |  |

| D020                                    |                             |          | 0.02                                                 | 1.0           | 4.3            | μΑ    | 3.0                 | disabled, all Peripherals Inactive      |  |

| D020                                    |                             |          | 4.3                                                  | 10.2          | 17             | μΑ    | 1.8                 | WDT, BOR, FVR, and T1OSC                |  |

| 0020                                    |                             | _        | 5                                                    | 10.5          | 18             | μΑ    | 3.0                 | disabled, all Peripherals Inactiv       |  |

|                                         |                             |          | 5.5                                                  | 11.8          | 21             | μA    | 5.0                 |                                         |  |

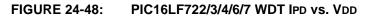

| D021                                    |                             |          | 0.5                                                  | 1.7           | 4.1            | μΑ    | 1.8                 | LPWDT Current (Note 1)                  |  |

|                                         |                             | _        | 0.8                                                  | 2.5           | 4.8            | μA    | 3.0                 |                                         |  |

| D021                                    |                             | _        | 6                                                    | 13.5          | 18             | μA    | 1.8                 | LPWDT Current (Note 1)                  |  |

|                                         |                             | _        | 6.5                                                  | 14.5          | 19             | μΑ    | 3.0                 |                                         |  |

|                                         |                             | _        | 7.5                                                  | 16            | 22             | μΑ    | 5.0                 | 1                                       |  |

| D021A                                   |                             | _        | 8.5                                                  | 14            | 19             | μΑ    | 1.8                 | FVR current (Note 1. Note 3)            |  |

|                                         |                             | _        | 8.5                                                  | 14            | 20             | μA    | 3.0                 |                                         |  |

| D021A                                   |                             | —        | 23                                                   | 44            | 48             | μΑ    | 1.8                 | FVR current (Note 1, Note 3,<br>Note 5) |  |

|                                         |                             |          | 25                                                   | 45            | 55             | μA    | 3.0                 |                                         |  |

|                                         |                             |          | 26                                                   | 60            | 70             | μA    | 5.0                 |                                         |  |

| D022                                    |                             | _        | —                                                    |               |                | μΑ    | 1.8                 | BOR Current (Note 1, Note 3)            |  |

|                                         |                             | —        | 7.5                                                  | 12            | 22             | μA    | 3.0                 |                                         |  |

| D022                                    |                             | —        | —                                                    | —             | —              | μA    | 1.8                 | BOR Current (Note 1, Note 3,            |  |

|                                         |                             |          | 23                                                   | 42            | 49             | μΑ    | 3.0                 | Note 5)                                 |  |

|                                         |                             | —        | 25                                                   | 46            | 50             | μΑ    | 5.0                 |                                         |  |

| D026                                    |                             | _        | 0.6                                                  | 2             |                | μΑ    | 1.8                 | T1OSC Current (Note 1)                  |  |

|                                         |                             | —        | 1.8                                                  | 3.0           | _              | μΑ    | 3.0                 |                                         |  |

| D026                                    |                             |          | 4.5                                                  | 11.1          | —              | μΑ    | 1.8                 | T1OSC Current (Note 1)                  |  |

|                                         |                             |          | 6                                                    | 12.5          | —              | μΑ    | 3.0                 | -                                       |  |

|                                         |                             | —        | 7                                                    | 13.5          | —              | μΑ    | 5.0                 |                                         |  |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

3: Fixed Voltage Reference is automatically enabled whenever the BOR is enabled

4: A/D oscillator source is FRC

5: 0.1 µF capacitor on VCAP (RA0).

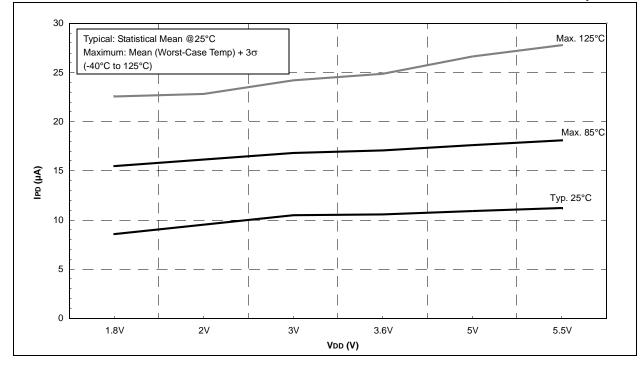

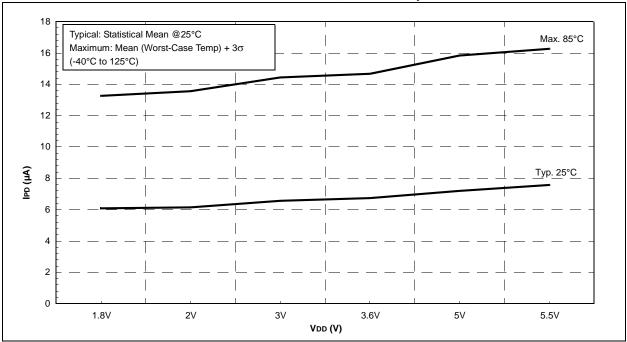

#### FIGURE 24-37: PIC16F722/3/4/6/7 CAP SENSE MEDIUM POWER IPD vs. VDD, VCAP = 0.1 µF

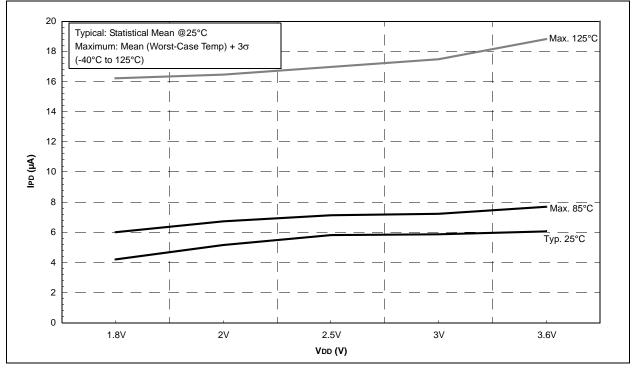

#### FIGURE 24-47: PIC16F722/3/4/6/7 WDT IPD vs. VDD, VCAP = 0.1 µF