Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 14x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 40-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 40-UQFN (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf724-i-mv |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

# TABLE 1-1: PIC16(L)F722/3/4/6/7 PINOUT DESCRIPTION

| Name                 | Function | Input<br>Type | Output<br>Type | Description                                                                                          |  |  |  |

|----------------------|----------|---------------|----------------|------------------------------------------------------------------------------------------------------|--|--|--|

| RA0/AN0/SS/VCAP      | RA0      | TTL           | CMOS           | General purpose I/O.                                                                                 |  |  |  |

|                      | AN0      | AN            |                | A/D Channel 0 input.                                                                                 |  |  |  |

|                      | SS       | ST            | _              | Slave Select input.                                                                                  |  |  |  |

|                      | VCAP     | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F72X only).                                             |  |  |  |

| RA1/AN1              | RA1      | TTL           | CMOS           | General purpose I/O.                                                                                 |  |  |  |

|                      | AN1      | AN            | _              | A/D Channel 1 input.<br>General purpose I/O.<br>A/D Channel 2 input.                                 |  |  |  |

| RA2/AN2              | RA2      | TTL           | CMOS           | General purpose I/O.                                                                                 |  |  |  |

|                      | AN2      | AN            | —              | S General purpose I/O.<br>A/D Channel 3 input.<br>A/D Voltage Reference input.                       |  |  |  |

| RA3/AN3/Vref         | RA3      | TTL           | CMOS           | General purpose I/O.                                                                                 |  |  |  |

|                      | AN3      | AN            | _              | A/D Channel 3 input.                                                                                 |  |  |  |

|                      | Vref     | AN            | —              | A/D Voltage Reference input.                                                                         |  |  |  |

| RA4/CPS6/T0CKI       | RA4      | TTL           | CMOS           | General purpose I/O.                                                                                 |  |  |  |

|                      | CPS6     | AN            | _              | Capacitive sensing input 6.                                                                          |  |  |  |

|                      | T0CKI    | ST            | _              | Timer0 clock input.                                                                                  |  |  |  |

| RA5/AN4/CPS7/SS/VCAP | RA5      | TTL           | CMOS           | General purpose I/O.                                                                                 |  |  |  |

|                      | AN4      | AN            |                | A/D Channel 4 input.                                                                                 |  |  |  |

|                      | CPS7     | AN            | —              | Capacitive sensing input 7.                                                                          |  |  |  |

|                      | SS       | ST            | _              | Slave Select input.                                                                                  |  |  |  |

|                      | VCAP     | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F72X only).                                             |  |  |  |

| RA6/OSC2/CLKOUT/VCAP | RA6      | TTL           | CMOS           | General purpose I/O.                                                                                 |  |  |  |

|                      | OSC2     | —             | XTAL           | Crystal/Resonator (LP, XT, HS modes).                                                                |  |  |  |

|                      | CLKOUT   | _             | CMOS           | Fosc/4 output.                                                                                       |  |  |  |

|                      | VCAP     | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F72X only).                                             |  |  |  |

| RA7/OSC1/CLKIN       | RA7      | TTL           | CMOS           | General purpose I/O.                                                                                 |  |  |  |

|                      | OSC1     | XTAL          | _              | Crystal/Resonator (LP, XT, HS modes).                                                                |  |  |  |

|                      | CLKIN    | CMOS          | _              | External clock input (EC mode).                                                                      |  |  |  |

|                      | CLKIN    | ST            | _              | RC oscillator connection (RC mode).                                                                  |  |  |  |

| RB0/AN12/CPS0/INT    | RB0      | TTL           | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |  |  |  |

|                      | AN12     | AN            | _              | A/D Channel 12 input.                                                                                |  |  |  |

|                      | CPS0     | AN            | _              | Capacitive sensing input 0.                                                                          |  |  |  |

|                      | INT      | ST            | _              | External interrupt.                                                                                  |  |  |  |

| RB1/AN10/CPS1        | RB1      | TTL           | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |  |  |  |

|                      | AN10     | AN            | —              | A/D Channel 10 input.                                                                                |  |  |  |

|                      | CPS1     | AN            | —              | Capacitive sensing input 1.                                                                          |  |  |  |

| RB2/AN8/CPS2         | RB2      | TTL           | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |  |  |  |

|                      | AN8      | AN            | —              | A/D Channel 8 input.                                                                                 |  |  |  |

|                      | CPS2     | AN            |                | Capacitive sensing input 2.                                                                          |  |  |  |

| RB3/AN9/CPS3/CCP2    | RB3      | TTL           | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |  |  |  |

|                      | AN9      | AN            |                | A/D Channel 9 input.                                                                                 |  |  |  |

|                      | CPS3     | AN            | _              | Capacitive sensing input 3.                                                                          |  |  |  |

|                      |          |               | CMOS           | Capture/Compare/PWM2.                                                                                |  |  |  |

# 2.3 PCL and PCLATH

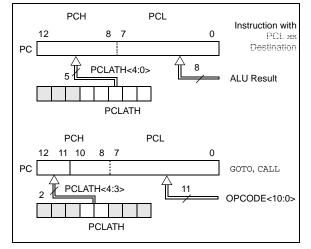

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-7 shows the two situations for the loading of the PC. The upper example in Figure 2-7 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-7 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 2-7: LOADING OF PC IN DIFFERENT SITUATIONS

## 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the Application Note *AN556, Implementing a Table Read* (DS00556).

## 2.3.2 STACK

All devices have an 8-level x 13-bit wide hardware stack (refer to Figures 2-1 and 2-3). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth PUSH overwrites the value that was stored from the first PUSH. The tenth PUSH overwrites the second PUSH (and so on).

- Note 1: There are no Status bits to indicate Stack Overflow or Stack Underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

# 2.4 **Program Memory Paging**

All devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper two bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is POPed off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the RETURN instructions (which POPs the address from the stack).

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 500 | h       |                     |  |  |  |  |

|---------|---------|---------|---------------------|--|--|--|--|

|         | PAGESEL | SUB_P1  | ;Select page 1      |  |  |  |  |

|         |         |         | ;(800h-FFFh)        |  |  |  |  |

|         | CALL    | SUB1_P1 | ;Call subroutine in |  |  |  |  |

|         | :       |         | ;page 1 (800h-FFFh) |  |  |  |  |

|         | :       |         |                     |  |  |  |  |

|         | ORG     | 900h    | ;page 1 (800h-FFFh) |  |  |  |  |

| SUB1_P1 |         |         |                     |  |  |  |  |

|         | :       |         | ;called subroutine  |  |  |  |  |

|         |         |         | ;page 1 (800h-FFFh) |  |  |  |  |

|         | :       |         |                     |  |  |  |  |

|         | RETURN  |         | ;return to          |  |  |  |  |

|         |         |         | ;Call subroutine    |  |  |  |  |

|         |         |         | ;in page 0          |  |  |  |  |

|         |         |         | ;(000h-7FFh)        |  |  |  |  |

Note: The contents of the PCLATH register are unchanged after a RETURN or RETFIE instruction is executed. The user must rewrite the contents of the PCLATH register for any subsequent subroutine calls or GOTO instructions.

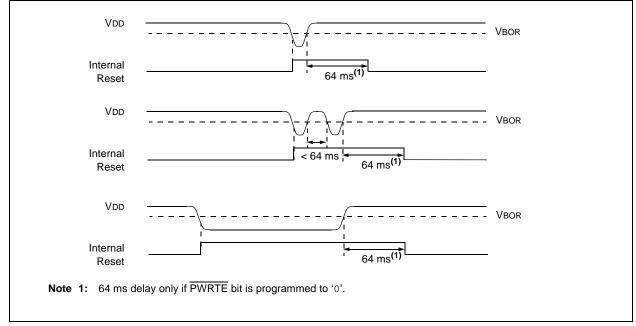

## 3.5 Brown-Out Reset (BOR)

Brown-out Reset is enabled by programming the BOREN<1:0> bits in the Configuration register. The brown-out trip point is selectable from two trip points via the BORV bit in the Configuration register.

Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

Two bits are used to enable the BOR. When BOREN = 11, the BOR is always enabled. When BOREN = 10, the BOR is enabled, but disabled during Sleep. When BOREN = 0X, the BOR is disabled.

If VDD falls below VBOR for greater than parameter (TBOR) (see **Section 23.0** "**Electrical Specifica-tions**"), the brown-out situation will reset the device. This will occur regardless of VDD slew rate. A Reset is not ensured to occur if VDD falls below VBOR for more than TBOR.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

**Note:** When erasing Flash program memory, the BOR is forced to enabled at the minimum BOR setting to ensure that any code protection circuitry is operating properly.

## FIGURE 3-3: BROWN-OUT SITUATIONS

# 6.0 I/O PORTS

There are as many as 35 general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

## 6.1 Alternate Pin Function

The Alternate Pin Function Control (APFCON) register is used to steer specific peripheral input and output functions between different pins. The APFCON register is shown in Register 6-1. For this device family, the following functions can be moved between different pins.

- SS (Slave Select)

- CCP2

## REGISTER 6-1: APFCON: ALTERNATE PIN FUNCTION CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0   |

|-------|-----|-----|-----|-----|-----|-------|---------|

| —     | —   | —   | _   | —   | —   | SSSEL | CCP2SEL |

| bit 7 |     |     |     |     |     |       | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-2 | Unimplemented: Read as '0'.                                                                                                       |

|---------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | SSSEL: SS Input Pin Selection bit                                                                                                 |

|         | $0 = \overline{SS}$ function is on RA5/AN4/CPS7/SS/VCAP<br>1 = SS function is on RA0/AN0/SS/VCAP                                  |

| bit 0   | <b>CCP2SEL:</b> CCP2 Input/Output Pin Selection bit<br>0 = CCP2 function is on RC1/T1OSI/CCP2<br>1 = CCP2 function is on RB3/CCP2 |

## 6.4.1 RC0/T1OSO/T1CKI

Figure 6-13 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 oscillator output

- a Timer1 clock input

## 6.4.2 RC1/T1OSI/CCP2

Figure 6-14 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 oscillator input

- a Capture 2 input, Compare 2 output, and PWM2 output

Note: CCP2 pin location may be selected as RB3 or RC1.

## 6.4.3 RC2/CCP1

Figure 6-15 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a Capture 1 input, Compare 1 output, and PWM1 output

## 6.4.4 RC3/SCK/SCL

Figure 6-16 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a SPI clock

- an I<sup>2</sup>C clock

#### 6.4.5 RC4/SDI/SDA

Figure 6-17 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a SPI data input

- an I<sup>2</sup>C data I/O

## 6.4.6 RC5/SDO

Figure 6-18 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a SPI data output

#### 6.4.7 RC6/TX/CK

Figure 6-19 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an asynchronous serial output

- a synchronous clock I/O

# 6.4.8 RC7/RX/DT

Figure 6-20 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- · an asynchronous serial input

- a synchronous serial data I/O

| REGISTER 6-13: | TRISD: PORTD TRI-STATE REGISTER <sup>(1)</sup> |

|----------------|------------------------------------------------|

|                |                                                |

| TRISD7 TRISD6 TRISD5 TRISD4 TRISD3 TRISD2 TRISD1 TRISD0   bit 7 bit 0 | R/W-1  |

|-----------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| bit 7 bit 0                                                           | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 |

|                                                                       | bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 7-0

**TRISD<7:0>:** PORTD Tri-State Control bits 1 = PORTD pin configured as an input (tri-stated) 0 = PORTD pin configured as an output

Note 1: TRISD is not implemented on PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'.

## REGISTER 6-14: ANSELD: PORTD ANALOG SELECT REGISTER<sup>(2)</sup>

| R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ANSD7 | ANSD6 | ANSD5 | ANSD4 | ANSD3 | ANSD2 | ANSD1 | ANSD0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 7-0 **ANSD<7:0>**: Analog Select between Analog or Digital Function on Pins RD<7:0>, respectively 0 = Digital I/O. Pin is assigned to port or Digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital Input buffer disabled.

- **Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

- 2: ANSELD register is not implemented on the PIC16F722/723/726/PIC16LF722/723/726. Read as '0'.

Note: PORTD is available on PIC16F724/LF724 and PIC16F727/LF727 only.

## 6.5.2 RD0/CPS8

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### 6.5.3 RD1/CPS9

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### 6.5.4 RD2/CPS10

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### 6.5.5 RD3/CPS11

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### **REGISTER 6-15: PORTE: PORTE REGISTER**

| U-0   | U-0 | U-0 | U-0 | R-x | R/W-x              | R/W-x              | R/W-x              |

|-------|-----|-----|-----|-----|--------------------|--------------------|--------------------|

| —     | —   | _   | _   | RE3 | RE2 <sup>(1)</sup> | RE1 <sup>(1)</sup> | RE0 <sup>(1)</sup> |

| bit 7 |     |     |     |     |                    |                    | bit 0              |

|       |     |     |     |     |                    |                    |                    |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| Unimplemented: Read as '0'                 |

|--------------------------------------------|

| RE<3:0>: PORTE I/O Pin bits <sup>(1)</sup> |

| 1 = Port pin is > VIH                      |

| 0 = Port pin is < VIL                      |

|                                            |

Note 1: RE<2:0> are not implemented on the PIC16F722/723/726/PIC16LF722/723/726. Read as '0'.

#### REGISTER 6-16: TRISE: PORTE TRI-STATE REGISTER

| U-0   | U-0 | U-0 | U-0 | R-1    | R/W-1                 | R/W-1                 | R/W-1                 |

|-------|-----|-----|-----|--------|-----------------------|-----------------------|-----------------------|

| _     | _   | _   | —   | TRISE3 | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> |

| bit 7 |     |     |     |        |                       |                       | bit 0                 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-4Unimplemented: Read as '0'bit 3TRISE3: RE3 Port Tri-state Control bit

This bit is always '1' as RE3 is an input onlybit 2-0TRISE<2:0>: RE<2:0> Tri-State Control bits(1)1 = PORTE pin configured as an input (tri-stated)0 = PORTE pin configured as an output

Note 1: TRISE<2:0> are not implemented on the PIC16F722/723/726/PIC16LF722/723/726. Read as '0'.

# 7.2 Clock Source Modes

Clock source modes can be classified as external or internal.

- Internal clock source (INTOSC) is contained within the oscillator module and derived from a 500 kHz high precision oscillator. The oscillator module has eight selectable output frequencies, with a maximum internal frequency of 16 MHz.

- External clock modes rely on external circuitry for the clock source. Examples are: oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

The system clock can be selected between external or internal clock sources via the FOSC bits of the Configuration Word 1.

# 7.3 Internal Clock Modes

The oscillator module has eight output frequencies derived from a 500 kHz high precision oscillator. The IRCF bits of the OSCCON register select the postscaler applied to the clock source dividing the frequency by 1, 2, 4 or 8. Setting the PLLEN bit of the Configuration Word 1 locks the internal clock source to 16 MHz before the postscaler is selected by the IRCF bits. The PLLEN bit must be set or cleared at the time of programming; therefore, only the upper or low four clock source frequencies are selectable in software.

## 7.3.1 INTOSC AND INTOSCIO MODES

The INTOSC and INTOSCIO modes configure the internal oscillators as the system clock source when the device is programmed using the oscillator selection or the FOSC<2:0> bits in the CONFIG1 register. See **Section 8.0** "**Device Configuration**" for more information.

In INTOSC mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT outputs the selected internal oscillator frequency divided by 4. The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

In INTOSCIO mode, OSC1/CLKIN and OSC2/CLKOUT are available for general purpose I/O.

# 7.3.2 FREQUENCY SELECT BITS (IRCF)

The output of the 500 kHz INTOSC and 16 MHz INTOSC, with Phase-Locked Loop enabled, connect to a postscaler and multiplexer (see Figure 7-1). The Internal Oscillator Frequency Select bits (IRCF) of the OSCCON register select the frequency output of the internal oscillator. Depending upon the PLLEN bit, one of four frequencies of two frequency sets can be selected via software:

If PLLEN = 1, frequency selection is as follows:

- 16 MHz

- 8 MHz (default after Reset)

- 4 MHz

- 2 MHz

- If PLLEN = 0, frequency selection is as follows:

- 500 kHz

- 250 kHz (default after Reset)

- 125 kHz

- 62.5 kHz

Note: Following any Reset, the IRCF<1:0> bits of the OSCCON register are set to '10' and the frequency selection is set to 8 MHz or 250 kHz. The user can modify the IRCF bits to select a different frequency.

There is no start-up delay before a new frequency selected in the IRCF bits takes effect. This is because the old and new frequencies are derived from INTOSC via the postscaler and multiplexer.

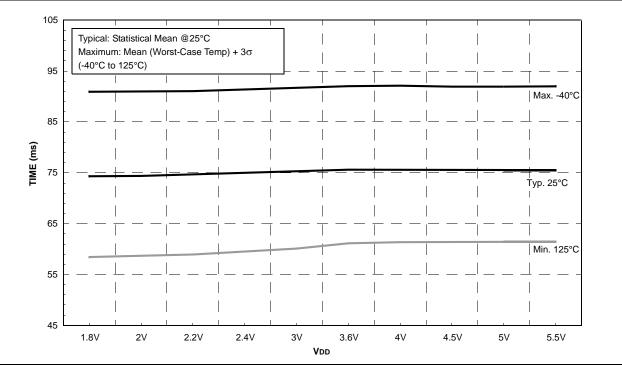

Start-up delay specifications are located in the Table 23-2 in Section 23.0 "Electrical Specifications".

## 9.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- 2. Configure the ADC module:

- Select ADC conversion clock

- Configure voltage reference

- Select ADC input channel

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- Enable ADC interrupt

- Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

**Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

2: Refer to Section 9.3 "A/D Acquisition Requirements".

## EXAMPLE 9-1: A/D CONVERSION

;This code block configures the ADC ;for polling, Vdd reference, Frc clock ;and ANO input. ;

;Conversion start & polling for completion ; are included.

| ;       |             |                      |

|---------|-------------|----------------------|

| BANKSEL | ADCON1      | ;                    |

| MOVLW   | B'01110000' | ;ADC Frc clock,      |

|         |             | ;VDD reference       |

| MOVWF   | ADCON1      | ;                    |

| BANKSEL | TRISA       | ;                    |

| BSF     | TRISA,0     | ;Set RAO to input    |

| BANKSEL | ANSELA      | ;                    |

| BSF     | ANSELA,0    | ;Set RA0 to analog   |

| BANKSEL | ADCON0      | ;                    |

| MOVLW   | B'0000001'  | ;AN0, On             |

| MOVWF   | ADCON0      | ;                    |

| CALL    | SampleTime  | ;Acquisiton delay    |

| BSF     | ADCON0,GO   | ;Start conversion    |

| BTFSC   | ADCON0,GO   | ;Is conversion done? |

| GOTO    | \$-1        | ;No, test again      |

| BANKSEL | ADRES       | i                    |

| MOVF    | ADRES,W     | ;Read result         |

| MOVWF   | RESULT      | ;store in GPR space  |

|         |             |                      |

## 15.3.4 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 15-4.

## EQUATION 15-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2+1)]}{\log(2)}$$

bits

Note: If the pulse-width value is greater than the period, the assigned PWM pin(s) will remain unchanged.

## TABLE 15-5: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

## TABLE 15-6: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

## 15.3.5 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 15.3.6 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency (Fosc). Any changes in the system clock frequency will result in changes to the PWM frequency. Refer to **Section 7.0** "**Oscillator Module**" for additional details.

#### 15.3.7 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 15.3.8 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Disable the PWM pin (CCPx) output driver(s) by setting the associated TRIS bit(s).

- 2. Load the PR2 register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- Load the CCPRxL register and the DCxBx bits of the CCPxCON register, with the PWM duty cycle value.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register. See Note below.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until Timer2 overflows, TMR2IF bit of the PIR1 register is set. See Note below.

- Enable the PWM pin (CCPx) output driver(s) by clearing the associated TRIS bit(s).

- **Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

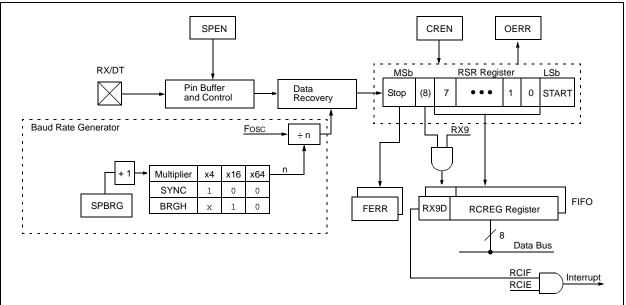

The operation of the AUSART module is controlled through two registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

These registers are detailed in Register 16-1 and Register 16-2, respectively.

# 16.4 AUSART Operation During Sleep

The AUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 16.4.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (refer to Section 16.3.2.4 "Synchronous Slave Reception Setup:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE global interrupt enable bit of the INTCON register is also set, then the Interrupt Service Routine at address 0004h will be called.

## 16.4.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Transmission (refer to Section 16.3.2.2 "Synchronous Slave Transmission Setup:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE global interrupt enable bit is also set then the Interrupt Service Routine at address 0004h will be called.

| SUBWF            | Subtract W                                                      | from f                                                                                                                      |

|------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SU                                                      | JBWF f,d                                                                                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$ |                                                                                                                             |

| Operation:       | (f) - (W) $\rightarrow$ (                                       | destination)                                                                                                                |

| Status Affected: | C, DC, Z                                                        |                                                                                                                             |

| Description:     | W register f<br>'0', the resu<br>register. If 'o                | s complement method)<br>rom register 'f'. If 'd' is<br>It is stored in the W<br>d' is '1', the result is<br>in register 'f. |

|                  | <b>C</b> = 0                                                    | W > f                                                                                                                       |

|                  | <b>C</b> = 1                                                    | W≤f                                                                                                                         |

$\overline{DC} = 0$

**DC** = 1

W<3:0> > f<3:0> W<3:0>  $\leq$  f<3:0>

| XORLW            | Exclusive OR literal with W                                                                                            |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] XORLW k                                                                                                        |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                      |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                          |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the 8-bit<br>literal 'k'. The result is placed in<br>the W register. |  |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                      |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                |

| Status Affected: | None                                                                                                                                                                   |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] XORWF f,d                                                                                                                                                               |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                 |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |

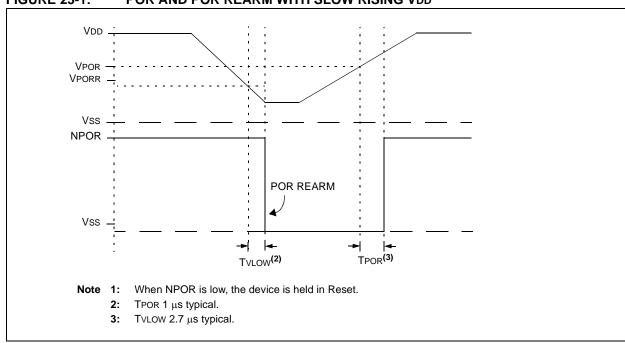

### FIGURE 23-1: POR AND POR REARM WITH SLOW RISING VDD

|               | DC CI | HARACTERISTICS                       |                   |      | $\text{-40°C} \leq \text{TA}$ | ≤ +85°C | otherwise stated)<br>for industrial<br>C for extended                                                              |

|---------------|-------|--------------------------------------|-------------------|------|-------------------------------|---------|--------------------------------------------------------------------------------------------------------------------|

| Param<br>No.  | Sym.  | Characteristic                       | Min.              | Тур† | Max.                          | Units   | Conditions                                                                                                         |

|               | VIL   | Input Low Voltage                    |                   |      |                               |         |                                                                                                                    |

|               |       | I/O PORT:                            |                   |      |                               |         |                                                                                                                    |

| D030          |       | with TTL buffer                      | —                 | _    | 0.8                           | V       | $4.5V \leq V\text{DD} \leq 5.5V$                                                                                   |

| D030A         |       |                                      |                   | _    | 0.15 VDD                      | V       | $1.8V \le V\text{DD} \le 4.5V$                                                                                     |

| D031          |       | with Schmitt Trigger buffer          |                   | _    | 0.2 Vdd                       | V       | $2.0V \le V\text{DD} \le 5.5V$                                                                                     |

|               |       | with I <sup>2</sup> C levels         |                   | _    | 0.3 Vdd                       | V       |                                                                                                                    |

| D032          |       | MCLR, OSC1 (RC mode) <sup>(1)</sup>  | _                 | _    | 0.2 Vdd                       | V       |                                                                                                                    |

| D033A         |       | OSC1 (HS mode)                       |                   |      | 0.3 Vdd                       | V       |                                                                                                                    |

|               | VIH   | Input High Voltage                   | J                 |      |                               |         | L                                                                                                                  |

|               |       | I/O ports:                           |                   | _    | _                             |         |                                                                                                                    |

| D040          |       | with TTL buffer                      | 2.0               | _    | 1 _                           | V       | $4.5V \le VDD \le 5.5V$                                                                                            |

| D040A         |       |                                      | 0.25 VDD +<br>0.8 | _    | -                             | V       | $1.8V \leq V \text{DD} \leq 4.5V$                                                                                  |

| D041          |       | with Schmitt Trigger buffer          | 0.8 Vdd           | _    | —                             | V       | $2.0V \le V \text{DD} \le 5.5 V$                                                                                   |

|               |       | with I <sup>2</sup> C levels         | 0.7 VDD           | _    | _                             | V       |                                                                                                                    |

| D042          |       | MCLR                                 | 0.8 VDD           | _    | _                             | V       |                                                                                                                    |

| D043A         |       | OSC1 (HS mode)                       | 0.7 VDD           |      | _                             | V       |                                                                                                                    |

| D043B         |       | OSC1 (RC mode)                       | 0.9 Vdd           | _    | _                             | V       | (Note 1)                                                                                                           |

|               | lı∟   | Input Leakage Current <sup>(2)</sup> | 11                |      |                               |         |                                                                                                                    |

| D060          |       | I/O ports                            | —                 | ± 5  | ± 125                         | nA      | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \ \text{Pin at high-impedance}, \ 85^\circ C \end{array}$ |

|               |       |                                      |                   | ± 5  | ± 1000                        | nA      | 125°C                                                                                                              |

| D061          |       | MCLR <sup>(3)</sup>                  | —                 | ± 50 | ± 200                         | nA      | $Vss \le Vpin \le Vdd, 85^{\circ}C$                                                                                |

|               | IPUR  | PORTB Weak Pull-up Current           |                   |      |                               | _       |                                                                                                                    |

| D070*         |       |                                      | 25                | 100  | 200                           |         | VDD = 3.3V, VPIN = VSS                                                                                             |

|               |       |                                      | 25                | 140  | 300                           | μA      | VDD = 5.0V, VPIN = VSS                                                                                             |

| _             | Vol   | Output Low Voltage <sup>(4)</sup>    | · · · · ·         |      | 1                             | 1       |                                                                                                                    |

| D080          |       | I/O ports                            | —                 | _    | 0.6                           | V       | IOL = 8mA, VDD = 5V<br>IOL = 6mA, VDD = 3.3V<br>IOL = 1.8mA, VDD = 1.8V                                            |

|               | Voh   | Output High Voltage <sup>(4)</sup>   | 1                 |      |                               |         |                                                                                                                    |

|               | VOH   |                                      |                   |      | 1                             |         | ЮН = 3.5mA, VDD = 5V                                                                                               |

| D090          | VON   | I/O ports                            | Vdd - 0.7         | _    | _                             | V       | IOH = 3mA, VDD = 3.3V                                                                                              |

| D090          |       |                                      |                   | _    | _                             | V       |                                                                                                                    |

| D090<br>D101* | COSC2 | Capacitive Loading Specs on          |                   | _    | 15                            | V<br>pF | IOH = 3mA, VDD = 3.3V<br>IOH = 1mA, VDD = 1.8V                                                                     |

|               |       | Capacitive Loading Specs on          |                   | _    |                               |         | IOH = 3mA, VDD = 3.3V<br>IOH = 1mA, VDD = 1.8V<br>In XT, HS and LP modes when<br>external clock is used to drive   |

## 23.4 DC Characteristics: PIC16(L)F722/3/4/6/7-I/E

Legend: TBD = To Be Determined

<sup>t</sup> These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

**3:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: Including OSC2 in CLKOUT mode.

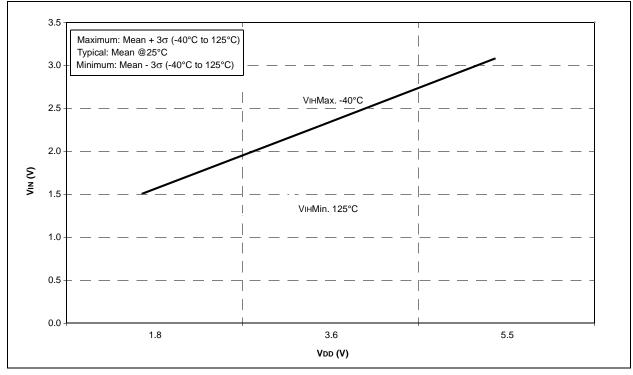

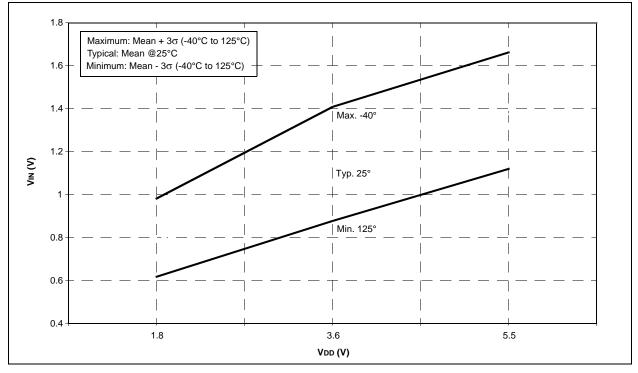

#### FIGURE 24-49: TTL INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE