Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 14x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf724t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### FIGURE 2-6:

### PIC16F726/LF726 AND PIC16F727/LF727 SPECIAL FUNCTION REGISTERS

| Indirect addr.(*)    | 00h     | Indirect addr.(*)      | 80h     | Indirect addr.(*)   | 100h | Indirect addr.(*)     | 180h |

|----------------------|---------|------------------------|---------|---------------------|------|-----------------------|------|

| TMR0                 | 01h     | OPTION                 | 81h     | TMR0                | 101h | OPTION                | 181h |

| PCL                  | 02h     | PCL                    | 82h     | PCL                 | 102h | PCL                   | 182h |

| STATUS               | 03h     | STATUS                 | 83h     | STATUS              | 103h | STATUS                | 183h |

| FSR                  | 04h     | FSR                    | 84h     | FSR                 | 104h | FSR                   | 184h |

| PORTA                | 05h     | TRISA                  | 85h     |                     | 105h | ANSELA                | 185h |

| PORTB                | 06h     | TRISB                  | 86h     |                     | 106h | ANSELB                | 186h |

| PORTC                | 07h     | TRISC                  | 87h     |                     | 107h |                       | 187h |

| PORTD <sup>(1)</sup> | 08h     | TRISD <sup>(1)</sup>   | 88h     | CPSCON0             | 108h | ANSELD <sup>(1)</sup> | 188h |

| PORTE                | 09h     | TRISE                  | 89h     | CPSCON1             | 109h | ANSELE <sup>(1)</sup> | 189h |

| PCLATH               | 0Ah     | PCLATH                 | 8Ah     | PCLATH              | 10Ah | PCLATH                | 18Ah |

| INTCON               | 0Bh     | INTCON                 | 8Bh     | INTCON              | 10Bh | INTCON                | 18Bh |

| PIR1                 | 0Ch     | PIE1                   | 8Ch     | PMDATL              | 10Ch | PMCON1                | 18Ch |

| PIR2                 | 0Dh     | PIE2                   | 8Dh     | PMADRL              | 10Dh | Reserved              | 18Dh |

| TMR1L                | 0Eh     | PCON                   | 8Eh     | PMDATH              | 10Eh | Reserved              | 18Eh |

| TMR1H                | 0Fh     | T1GCON                 | 8Fh     | PMADRH              | 10Fh | Reserved              | 18Fh |

| T1CON                | 10h     | OSCCON                 | 90h     |                     | 110h |                       | 190h |

| TMR2                 | 11h     | OSCTUNE                | 91h     |                     | 111h |                       | 191h |

| T2CON                | 12h     | PR2                    | 92h     |                     | 112h |                       | 192h |

| SSPBUF               | 13h     | SSPADD/SSPMSK          | 93h     |                     | 113h |                       | 193h |

| SSPCON               | 14h     | SSPSTAT                | 94h     |                     | 114h |                       | 194h |

| CCPR1L               | 15h     | WPUB                   | 95h     |                     | 115h |                       | 195h |

| CCPR1H               | 16h     | IOCB                   | 96h     | General             | 116h | General               | 196h |

| CCP1CON              | 17h     |                        | 97h     | Purpose             | 117h | Purpose               | 197h |

| RCSTA                | 18h     | TXSTA                  | 98h     | Register            | 118h | Register              | 198h |

| TXREG                | 19h     | SPBRG                  | 99h     | 16 Bytes            | 119h | 16 Bytes              | 199h |

| RCREG                | 1Ah     |                        | 9Ah     |                     | 11Ah |                       | 19Ah |

| CCPR2L               | 1Bh     |                        | 9Bh     |                     | 11Bh |                       | 19Bh |

| CCPR2H               | 1Ch     | APFCON                 | 9Ch     |                     | 11Ch |                       | 19Ch |

| CCP2CON              | 1Dh     | FVRCON                 | 9Dh     |                     | 11Dh |                       | 19Dh |

| ADRES                | 1Eh     |                        | 9Eh     |                     | 11Eh |                       | 19Eh |

| ADCON0               | 1Fh     | ADCON1                 | 9Fh     |                     | 11Fh |                       | 19Fh |

|                      | 20h     |                        | A0h     |                     | 120h |                       | 1A0h |

|                      |         | General                |         | General             |      | General               |      |

| Conoral              |         | Purpose                |         | Purpose             |      | Purpose               |      |

| General<br>Purpose   |         | Register               |         | Register            |      | Register              |      |

| Register             |         | 80 Bytes               |         | 80 Bytes            |      | 80 Bytes              |      |

| 96 Bytes             |         |                        | EFh     |                     | 16Fh |                       | 1EFh |

|                      |         | Accesses<br>70h-7Fh    | F0h     | Accesses<br>70h-7Fh | 170h | Accesses<br>70h-7Fh   | 1F0h |

|                      | 7Fh     |                        | FFh     |                     | 17Fh |                       | 1FFh |

| Bank 0               | <b></b> | Bank 1                 | I       | Bank 2              |      | Bank 3                | -    |

|                      |         | data memory locations, | read as | ʻ0',                |      |                       |      |

| * = Not a pł         |         | •                      |         |                     |      | 726/LF726, read as    |      |

¤ 2007-2015 Microchip Technology Inc.

## REGISTER 6-5: PORTB: PORTB REGISTER

| R/W-x                   | R/W-x | R/W-x        | R/W-x | R/W-x        | R/W-x            | R/W-x    | R/W-x |

|-------------------------|-------|--------------|-------|--------------|------------------|----------|-------|

| RB7                     | RB6   | RB5          | RB4   | RB3          | RB2              | RB1      | RB0   |

| bit 7 bit 0             |       |              |       |              |                  |          |       |

|                         |       |              |       |              |                  |          |       |

|                         |       |              |       |              |                  |          |       |

| Legend:                 |       |              |       |              |                  |          |       |

| Legend:<br>R = Readable | bit   | W = Writable | bit   | U = Unimplen | nented bit, read | l as '0' |       |

bit 7-0 RB<7:0>: PORTB I/O Pin bit 1 = Port pin is > VIH 0 = Port pin is < VIL

REGISTER 6-6: TRISB: PORTB TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 7-0

TRISB<7:0>: PORTB Tri-State Control bit

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

| R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WPUB7 | WPUB6 | WPUB5 | WPUB4 | WPUB3 | WPUB2 | WPUB1 | WPUB0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0

- WPUB<7:0>: Weak Pull-up Register bits

- 1 = Pull-up enabled

- 0 = Pull-up disabled

Note 1: Global RBPU bit of the OPTION register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

#### REGISTER 6-8: IOCB: INTERRUP T-ON-CHANGE PORTB REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IOCB7 | IOCB6 | IOCB5 | IOCB4 | IOCB3 | IOCB2 | IOCB1 | IOCB0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 IOCB<7:0>: Interrupt-on-Change PORTB Control bits

- 1 = Interrupt-on-change enabled

- 0 = Interrupt-on-change disabled

#### REGISTER 6-9: ANSELB: PORTB ANALOG SELECT REGISTER

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | ANSB5 | ANSB4 | ANSB3 | ANSB2 | ANSB1 | ANSB0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 ANSB<5:0>: Analog Select between Analog or Digital Function on Pins RB<5:0>, respectively

- 0 = Digital I/O. Pin is assigned to port or Digital special function.

- 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital Input buffer disabled.

Note 1: When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

## 6.4.1 RC0/T1OSO/T1CKI

Figure 6-13 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 oscillator output

- a Timer1 clock input

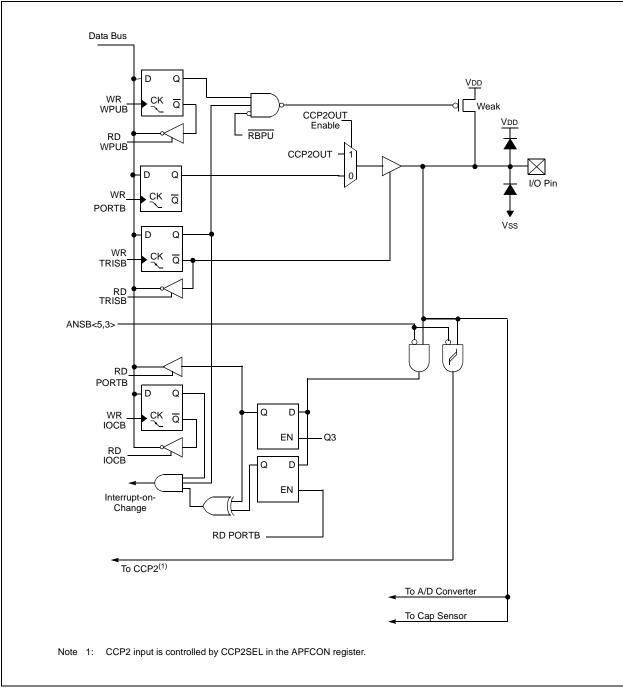

### 6.4.2 RC1/T1OSI/CCP2

Figure 6-14 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 oscillator input

- a Capture 2 input, Compare 2 output, and PWM2 output

Note: CCP2 pin location may be selected as RB3 or RC1.

### 6.4.3 RC2/CCP1

Figure 6-15 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a Capture 1 input, Compare 1 output, and PWM1 output

### 6.4.4 RC3/SCK/SCL

Figure 6-16 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a SPI clock

- an I<sup>2</sup>C clock

#### 6.4.5 RC4/SDI/SDA

Figure 6-17 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a SPI data input

- an I<sup>2</sup>C data I/O

## 6.4.6 RC5/SDO

Figure 6-18 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a SPI data output

#### 6.4.7 RC6/TX/CK

Figure 6-19 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an asynchronous serial output

- a synchronous clock I/O

## 6.4.8 RC7/RX/DT

Figure 6-20 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- · an asynchronous serial input

- a synchronous serial data I/O

## 6.5 PORTD and TRISD Registers

PORTD is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISD (Register 6-13). Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 6-4 shows how to initialize PORTD.

Reading the PORTD register (Register 6-12) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

Note: PORTD is available on PIC16F724/LF724 and PIC16F727/LF727 only.

The TRISD register (Register 6-13) controls the PORTD pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISD register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### EXAMPLE 6-4: INITIALIZING PORTD

| BANKSEL | PORTD       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTD       | ;Init PORTD            |

| BANKSEL | ANSELD      |                        |

| CLRF    | ANSELD      | ;Make PORTD digital    |

| BANKSEL | _ TRISD     | ,                      |

| MOVLW   | B'00001100' | ;Set RD<3:2> as inputs |

| MOVWF   | TRISD       | ;and set RD<7:4,1:0>   |

|         |             | ;as outputs            |

|         |             |                        |

### 6.5.1 ANSELD REGISTER

The ANSELD register (Register 6-9) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELD bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELD bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELD register must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

## REGISTER 6-12: PORTD: PORTD REGISTER<sup>(1)</sup>

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RD7   | RD6   | RD5   | RD4   | RD3   | RD2   | RD1   | RD0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 RD<7:0>: PORTD General Purpose I/O Pin bits

1 = Port pin is > VIH 0 = Port pin is < VIL

Note 1: PORTD is not implemented on PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'.

| U-0                           | U-0                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                         | R/W-0                                                    | R/W-0                                                                      | R/W-0                                                                         | R/W-0               |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------|

| _                             | —                                                                                                                                                                                                                                                                       | DCxB1                                                                                                                                                                                                                                                                                                                          | DCxB0                                                                                                                                                                                                         | CCPxM3                                                   | CCPxM2                                                                     | CCPxM1                                                                        | CCPxM0              |

| bit 7                         | ·                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                               |                                                          |                                                                            |                                                                               | bit 0               |

| Legend:                       |                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                               |                                                          |                                                                            |                                                                               |                     |

| R = Readable                  | bit                                                                                                                                                                                                                                                                     | W = Writable                                                                                                                                                                                                                                                                                                                   | bit                                                                                                                                                                                                           | U = Unimpler                                             | nented bit, read                                                           | d as '0'                                                                      |                     |

| -n = Value at P               | OR                                                                                                                                                                                                                                                                      | '1' = Bit is set                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                               | '0' = Bit is cle                                         | ared                                                                       | x = Bit is unkr                                                               | nown                |

| bit 7-6<br>bit 5-4<br>bit 3-0 | DCxB<1:0>: F<br>Capture mode<br>Unused<br>Compare mod<br>Unused<br>PWM mode:<br>These bits are<br>CCPxM<3:0>:<br>0000 = Captu<br>0001 = Unus<br>0010 = Comp<br>0111 = Unus<br>0100 = Captu<br>0101 = Captu<br>0101 = Captu<br>0101 = Comp<br>1001 = Comp<br>1001 = Comp | e the two LSbs<br>CCP Mode S<br>re/Compare/F<br>ed (reserved)<br>pare mode, tog<br>ed (reserved)<br>ure mode, even<br>ure mode, even<br>ure mode, even<br>pare mode, set<br>pare mode, trig<br>vD conversion | of the PWM of<br>select bits<br>PWM off (reset<br>gle output on<br>y falling edge<br>y 4th rising edge<br>y 4th rising edge<br>y 16th rising edge<br>output on ma<br>ar output on m<br>herate softwar<br>ted) | duty cycle. The<br>s CCP module)<br>match (CCPxIF<br>dge | t of the PIRx re<br>bit of the PIRx re<br>bit of the PIRx<br>hatch (CCPxIF | x register is set<br>egister is set)<br>register is set)<br>bit is set of the | )<br>PIRx register, |

## REGISTER 15-1: CCPxCON: CCPx CONTROL REGISTER

Note 1: A/D conversion start feature is available only on CCP2.

| FIGURE 16-8:                  | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                                 |

|-------------------------------|-------------------------------------------------------------------------------------------|

| RX/DT<br>pin                  | bit 0         bit 2         bit 3         bit 4         bit 5         bit 6         bit 7 |

| TX/CK pin                     |                                                                                           |

| Write to<br>bit SREN          |                                                                                           |

| SREN bit                      |                                                                                           |

| CREN bit <u>'0'</u>           | ʻ0'                                                                                       |

| RCIF bit<br>(Interrupt) ————— |                                                                                           |

| Read<br>RCREG                 | f1                                                                                        |

| Note: Timing dia              | gram demonstrates Synchronous Master mode with bit SREN = 1 and bit BRGH = 0.             |

| Name   | Bit 7    | Bit 6       | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|-------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE        | TOIE       | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE  | ADIE        | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF  | ADIF        | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCREG  | AUSART R | eceive Data | a Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN     | RX9         | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000X            | 0000 000X                       |

| TRISC  | TRISC7   | TRISC6      | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC     | TX9         | TXEN       | SYNC   | —      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

#### TABLE 16-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Reception.

## TABLE 17-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

| Name    | Bit 7                  | Bit 6          | Bit 5       | Bit 4        | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Value on POR, BOR   | Value on all other Resets |

|---------|------------------------|----------------|-------------|--------------|----------|--------|---------|---------|---------------------|---------------------------|

| ANSELA  | —                      | —              | ANSA5       | ANSA4        | ANSA3    | ANSA2  | ANSA1   | ANSA0   | 11 1111             | 11 1111                   |

| APFCON  | _                      | _              | _           | _            | _        | _      | SSSEL   | CCP2SEL | 00                  | 00                        |

| INTCON  | GIE                    | PEIE           | TOIE        | INTE         | RBIE     | T0IF   | INTF    | RBIF    | 0000 000x           | 0000 000x                 |

| PIE1    | TMR1GIE                | ADIE           | RCIE        | TXIE         | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000 0000 0000 |                           |

| PIR1    | TMR1GIF                | ADIF           | RCIF        | TXIF         | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000           | 0000 0000                 |

| PR2     | Timer2 Period Register |                |             |              |          |        |         |         | 1111 1111           | 1111 1111                 |

| SSPBUF  | Synchronou             | is Serial Port | Receive Buf | fer/Transmit | Register |        |         |         | XXXX XXXX           | սսսս սսսս                 |

| SSPCON  | WCOL                   | SSPOV          | SSPEN       | CKP          | SSPM3    | SSPM2  | SSPM1   | SSPM0   | 0000 0000           | 0000 0000                 |

| SSPSTAT | SMP                    | CKE            | D/A         | Р            | S        | R/W    | UA      | BF      | 0000 0000           | 0000 0000                 |

| TRISA   | TRISA7                 | TRISA6         | TRISA5      | TRISA4       | TRISA3   | TRISA2 | TRISA1  | TRISA0  | 1111 1111 1111 1111 |                           |

| TRISC   | TRISC7                 | TRISC6         | TRISC5      | TRISC4       | TRISC3   | TRISC2 | TRISC1  | TRISC0  | 1111 1111           | 1111 1111                 |

| T2CON   |                        | TOUTPS3        | TOUTPS2     | TOUTPS1      | TOUTPS0  | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000           | -000 0000                 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode.

## TABLE 23-11: SPI MODE REQUIREMENTS

| Param<br>No. | Symbol                | Characteristic                         | Min.     | Тур† | Max. | Units | Conditions |  |

|--------------|-----------------------|----------------------------------------|----------|------|------|-------|------------|--|

| SP70*        | TssL2scH,<br>TssL2scL | SS pto SCK por SCK ninput              | Тсү      | —    | _    | ns    |            |  |

| SP71*        | TscH                  | SCK input high time (Slave mode)       | TCY + 20 | _    | _    | ns    |            |  |

| SP72*        | TscL                  | SCK input low time (Slave mode)        | TCY + 20 | _    | _    | ns    |            |  |

| SP73*        | TDIV2SCH,<br>TDIV2SCL | Setup time of SDI data input to SCK ed | 100      | _    | _    | ns    |            |  |

| SP74*        | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edg | е        | 100  | _    | _     | ns         |  |

| SP75*        | TDOR                  | SDO data output rise time              | 3.0-5.5V | —    | 10   | 25    | ns         |  |

|              |                       |                                        | 1.8-5.5V | —    | 25   | 50    | ns         |  |

## FIGURE 23-20: I<sup>2</sup>C BUS START/STOP BITS TIMING