Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 11x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf726-e-so |

# **Table of Contents**

| Device Overview                                                              | 11  |

|------------------------------------------------------------------------------|-----|

| Memory Organization                                                          | 17  |

| Resets                                                                       | 30  |

| Interrupts                                                                   | 40  |

| Low Dropout (LDO) Voltage Regulator                                          | 49  |

| I/O Ports                                                                    | 50  |

| Oscillator Module                                                            | 85  |

| Device Configuration                                                         |     |

| Analog-to-Digital Converter (ADC) Module                                     | 94  |

| Fixed Voltage Reference                                                      | 104 |

| Timer0 Module                                                                | 105 |

| Timer1 Module with Gate Control                                              | 108 |

| Timer2 Module                                                                | 120 |

| Capacitive Sensing Module                                                    | 122 |

| Capture/Compare/PWM (CCP) Module                                             | 128 |

| Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) | 138 |

| SSP Module Overview                                                          |     |

| Program Memory Read                                                          | 181 |

| Power-Down Mode (Sleep)                                                      | 184 |

| In-Circuit Serial Programming™ (ICSP™)                                       |     |

| Instruction Set Summary                                                      | 187 |

| Development Support                                                          |     |

| Electrical Specifications                                                    | 200 |

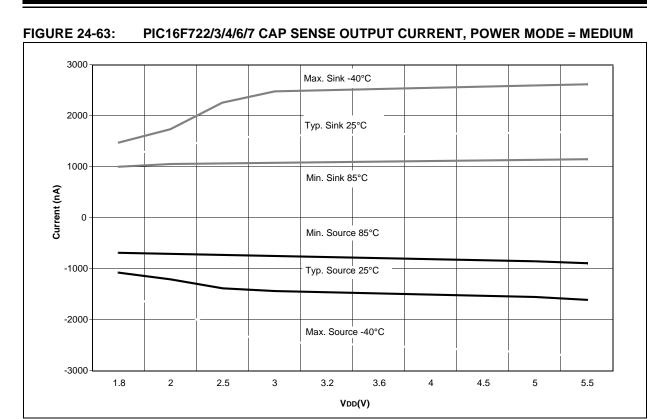

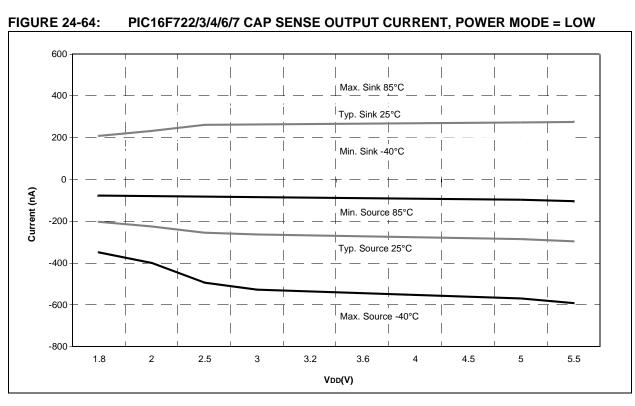

| DC and AC Characteristics Graphs and Charts                                  | 228 |

| Packaging Information                                                        |     |

| Appendix A: Data Sheet Revision History                                      | 277 |

| Appendix B: Migrating From Other PIC® Devices                                | 277 |

| The Microchip Website                                                        | 278 |

| Customer Change Notification Service                                         | 278 |

| Customer Support                                                             | 278 |

| Product Identification System                                                | 279 |

# 1.0 DEVICE OVERVIEW

The PIC16(L)F722/3/4/6/7 devices are covered by this data sheet. They are available in 28/40/44-pin packages. Figure 1-1 shows a block diagram of the PIC16F722/723/726/PIC16LF722/723/726 devices and Figure 1-2 shows a block diagram of the PIC16F724/727/PIC16LF724/727 devices. Table 1-1 shows the pinout descriptions.

#### 2.2.2.2 OPTION register

The OPTION register, shown in Register 2-2, is a readable and writable register, which contains various control bits to configure:

- Timer0/WDT prescaler

- External RB0/INT interrupt

- Timer0

- · Weak pull-ups on PORTB

Note: To achieve a 1:1 prescaler assignment for Timer0, assign the prescaler to the WDT by setting the PSA bit of the OPTION\_REG register to '1'. Refer to Section 11.1.3 "Software Programmable Prescaler".

### REGISTER 2-2: OPTION\_REG: OPTION REGISTER

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7 RBPU: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual bits in the WPUB register

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin 0 = Interrupt on falling edge of RB0/INT pin

bit 5 TOCS: Timer0 Clock Source Select bit

1 = Transition on RA4/T0CKI pin

0 = Internal instruction cycle clock (Fosc/4)

bit 4 T0SE: Timer0 Source Edge Select bit

1 = Increment on high-to-low transition on RA4/T0CKI pin 0 = Increment on low-to-high transition on RA4/T0CKI pin

bit 3 **PSA:** Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 **PS<2:0>:** Prescaler Rate Select bits

| Bit Value | Timer0 Rate | WDT Rate |

|-----------|-------------|----------|

| 000       | 1:2         | 1:1      |

| 001       | 1:4         | 1:2      |

| 010       | 1:8         | 1:4      |

| 011       | 1:16        | 1:8      |

| 100       | 1:32        | 1:16     |

| 101       | 1:64        | 1:32     |

| 110       | 1 : 128     | 1:64     |

| 111       | 1 : 256     | 1 : 128  |

TABLE 3-1: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | TO | PD | Condition                                               |  |  |  |  |

|-----|-----|----|----|---------------------------------------------------------|--|--|--|--|

| 0   | Х   | 1  | 1  | Power-on Reset or LDO Reset                             |  |  |  |  |

| 0   | х   | 0  | х  | legal, TO is set on POR                                 |  |  |  |  |

| 0   | x   | x  | 0  | llegal, PD is set on POR                                |  |  |  |  |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |  |  |  |  |

| 1   | 1   | 0  | 1  | WDT Reset                                               |  |  |  |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |  |  |  |  |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |  |  |  |  |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or interrupt wake-up from Sleep |  |  |  |  |

TABLE 3-2: RESET CONDITION FOR SPECIAL REGISTERS(2)

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 0000h                 | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 0000h                 | 0001 0uuu          | uu               |

| WDT Reset                          | 0000h                 | 0000 1uuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 0000h                 | 0001 1uuu          | u0               |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

2: If a Status bit is not implemented, that bit will be read as '0'.

#### 4.5.5 PIR2 REGISTER

The PIR2 register contains the interrupt flag bits, as shown in Register 4-5.

Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 4-5: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

| _     | _   | _   | _   | _   | _   | _   | CCP2IF |

| bit 7 |     |     |     |     |     |     | bit 0  |

Note:

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-1 **Unimplemented:** Read as '0' bit 0 **CCP2IF:** CCP2 Interrupt Flag bit

Capture Mode:

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 register capture occurred

Compare Mode:

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

PWM mode:

Unused in this mode

#### TABLE 4-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name       | Bit 7   | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|---------|--------|-------|-------|-------|--------|--------|--------|----------------------|---------------------------------|

| INTCON     | GIE     | PEIE   | TOIE  | INTE  | RBIE  | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| OPTION_REG | RBPU    | INTEDG | T0CS  | T0SE  | PSA   | PS2    | PS1    | PS0    | 1111 1111            | 1111 1111                       |

| PIE1       | TMR1GIE | ADIE   | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIE2       | -       | I      | -     |       | -     | _      | -      | CCP2IE | 0                    | 0                               |

| PIR1       | TMR1GIF | ADIF   | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIR2       | _       |        | _     | _     | _     | _      | _      | CCP2IF | 0                    | 0                               |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Capture, Compare and PWM.

# 6.2.2 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTA pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the A/D Converter (ADC), refer to the appropriate section in this data sheet.

## 6.2.2.1 RA0/AN0/SS/VCAP

Figure 6-1 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- a slave select input for the SSP<sup>(1)</sup>

- a Voltage Regulator Capacitor pin (PIC16F72X only)

Note: SS pin location may be selected as RA5 or RA0.

#### 6.2.2.2 RA1/AN1

Figure 6-2 shows the diagram for this pin. This pin is configurable to function as one of the following:

- · a general purpose I/O

- · an analog input for the ADC

#### 6.2.2.3 RA2/AN2

Figure 6-2 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- · an analog input for the ADC

#### 6.2.2.4 RA3/AN3/VREF

Figure 6-2 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- · an analog input for the ADC

- · a voltage reference input for the ADC

#### 6.2.2.5 RA4/CPS6/T0CKI

Figure 6-3 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

- · a clock input for Timer0

The Timer0 clock input function works independently of any TRIS register setting. Effectively, if TRISA4 = 0, the PORTA4 register bit will output to the pad and Clock Timer0 at the same time.

### 6.2.2.6 RA5/AN4/CPS7/SS/VCAP

Figure 6-4 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- · an analog input for the ADC

- · a capacitive sensing input

- a slave select input for the SSP<sup>(1)</sup>

- a Voltage Regulator Capacitor pin (PIC16F72X only)

Note: SS pin location may be selected as RA5 or RA0.

#### 6.2.2.7 RA6/OSC2/CLKOUT/VCAP

Figure 6-5 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- · a crystal/resonator connection

- · a clock output

- a Voltage Regulator Capacitor pin (PIC16F72X only)

#### 6.2.2.8 RA7/OSC1/CLKIN

Figure 6-6 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- · a crystal/resonator connection

- · a clock input

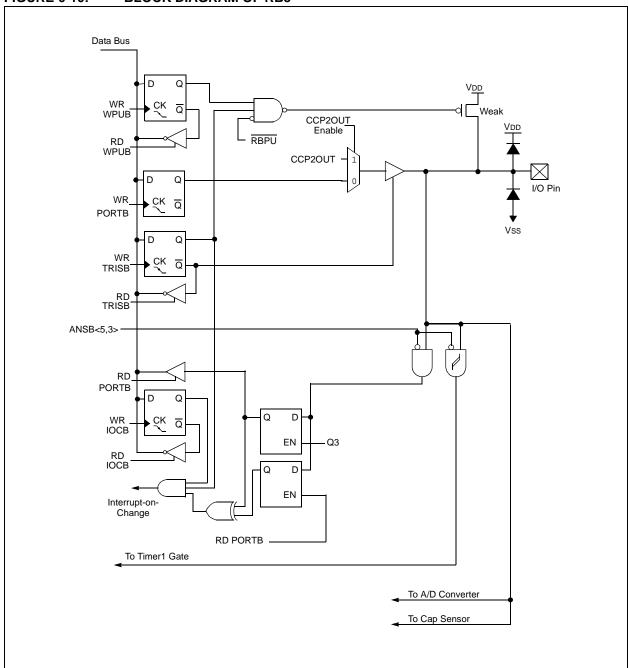

FIGURE 6-9: **BLOCK DIAGRAM OF RB3** Data Bus WR WPUB Q Weak CCP2OU<u>T</u> Enable VDDRD WPUB RBPU CCP2OUT Q 0 I/O Pin WR Q PORTB Vss WR Q TRISB RD TRISB ANSB<5,3> RD PORTB Q Q D WR IOCB Q ΕN Q3 RD IOCB D ΕN Interrupt-on-Change RD PORTB To CCP2<sup>(1)</sup> To A/D Converter To Cap Sensor

Note 1: CCP2 input is controlled by CCP2SEL in the APFCON register.

FIGURE 6-10: BLOCK DIAGRAM OF RB5

#### 6.4.1 RC0/T1OSO/T1CKI

Figure 6-13 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- · a Timer1 oscillator output

- · a Timer1 clock input

#### 6.4.2 RC1/T1OSI/CCP2

Figure 6-14 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- · a Timer1 oscillator input

- a Capture 2 input, Compare 2 output, and PWM2 output

**Note:** CCP2 pin location may be selected as RB3 or RC1.

#### 6.4.3 RC2/CCP1

Figure 6-15 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a Capture 1 input, Compare 1 output, and PWM1 output

#### 6.4.4 RC3/SCK/SCL

Figure 6-16 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a SPI clock

- an I<sup>2</sup>C clock

#### 6.4.5 RC4/SDI/SDA

Figure 6-17 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a SPI data input

- an I<sup>2</sup>C data I/O

# 6.4.6 RC5/SDO

Figure 6-18 shows the diagram for this pin. This pin is configurable to function as one of the following:

- · a general purpose I/O

- · a SPI data output

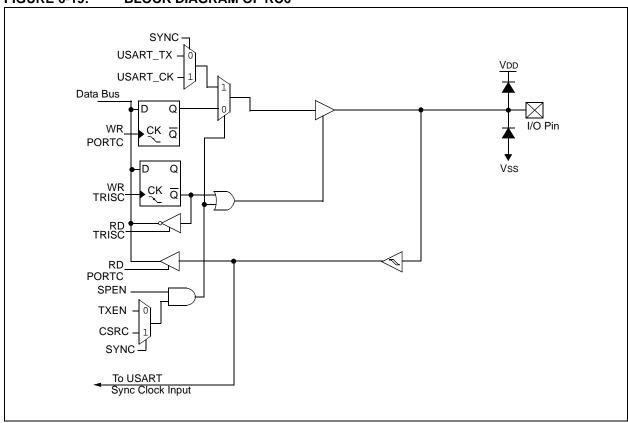

### 6.4.7 RC6/TX/CK

Figure 6-19 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an asynchronous serial output

- · a synchronous clock I/O

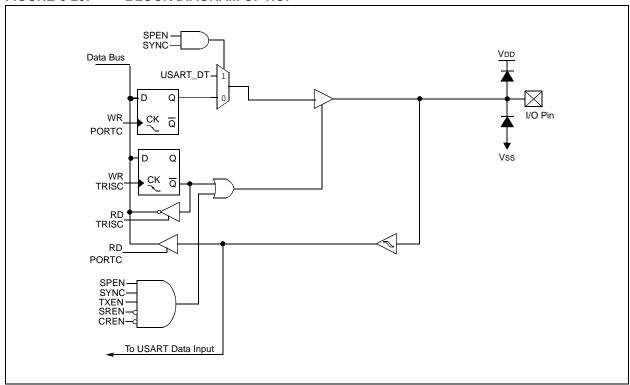

#### 6.4.8 RC7/RX/DT

Figure 6-20 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- · an asynchronous serial input

- · a synchronous serial data I/O

FIGURE 6-19: BLOCK DIAGRAM OF RC6

FIGURE 6-20: BLOCK DIAGRAM OF RC7

# 16.3.2.3 AUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 16.3.1.4 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never Idle

- · SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE interrupt enable bit of the PIE1 register is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

# 16.3.2.4 Synchronous Slave Reception Setup:

- Set the SYNC and SPEN bits and clear the CSRC bit.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 3. If 9-bit reception is desired, set the RX9 bit.

- Verify address detection is disabled by clearing the ADDEN bit of the RCSTA register.

- 5. Set the CREN bit to enable reception.

- The RCIF bit of the PIR1 register will be set when reception is complete. An interrupt will be generated if the RCIE bit of the PIE1 register was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- Retrieve the eight Least Significant bits from the receive FIFO by reading the RCREG register.

- If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register.

TABLE 16-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Name   | Bit 7                              | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|------------------------------------|--------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE                                | PEIE   | TOIE   | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE                            | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF                            | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCREG  | RCREG AUSART Receive Data Register |        |        |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN                               | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| TRISC  | TRISC7                             | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC                               | TX9    | TXEN   | SYNC   | _      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

**Legend:** x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Reception.

#### 17.1.2 SLAVE MODE

For any SPI device acting as a slave, the data is transmitted and received as external clock pulses appear on SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

## 17.1.2.1 Slave Mode Operation

The SSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready.

The slave has no control as to when data will be clocked in or out of the device. All data that is to be transmitted, to a master or another slave, must be loaded into the SSPBUF register before the first clock pulse is received.

Once eight bits of data have been received:

- · Received byte is moved to the SSPBUF register

- BF bit of the SSPSTAT register is set

- · SSPIF bit of the PIR1 register is set

Any write to the SSPBUF register during transmission/reception of data will be ignored and the Write Collision Detect bit, WCOL of the SSPCON register, will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

The user's firmware must read SSPBUF, clearing the BF flag, or the SSPOV bit of the SSPCON register will be set with the reception of the next byte and communication will be disabled.

A SPI module transmits and receives at the same time, occasionally causing dummy data to be transmitted/received. It is up to the user to determine which data is to be used and what can be discarded.

#### 17.1.2.2 Enabling Slave I/O

To enable the serial port, the SSPEN bit of the SSPCON register must be set. If a Slave mode of operation is selected in the SSPM bits of the SSPCON register, the SDI, SDO, SCK pins will be assigned as serial port pins.

For these pins to function as serial port pins, they must have their corresponding data direction bits set or cleared in the associated TRIS register as follows:

- · SDI configured as input

- · SDO configured as output

- · SCK configured as input

Optionally, a fourth pin, Slave Select (\$\overline{SS}\$) may be used in Slave mode. Slave Select may be configured to operate on one of the following pins via the SSSEL bit in the APFCON register.

- RA5/AN4/SS

- RA0/AN0/SS

Upon selection of a Slave Select pin, the appropriate bits must be set in the ANSELA and TRISA registers. Slave Select must be set as an input by setting the corresponding bit in TRISA, and digital I/O must be enabled on the  $\overline{SS}$  pin by clearing the corresponding bit of the ANSELA register.

#### 17.1.2.3 Slave Mode Setup

When initializing the SSP module to SPI Slave mode, compatibility must be ensured with the master device. This is done by programming the appropriate control bits of the SSPCON and SSPSTAT registers. These control bits allow the following to be specified:

- · SCK as clock input

- Idle state of SCK (CKP bit)

- Data input sample phase (SMP bit)

- Output data on rising/falling edge of SCK (CKE bit)

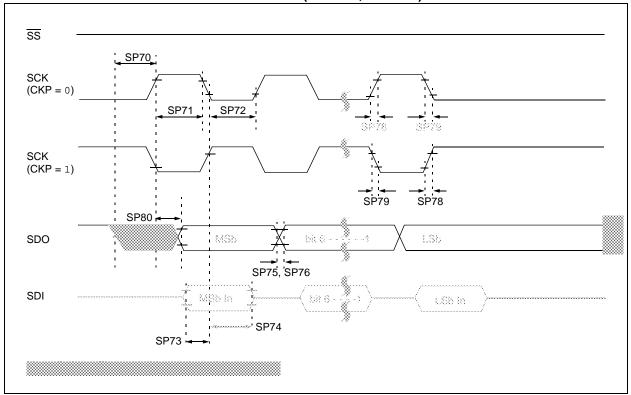

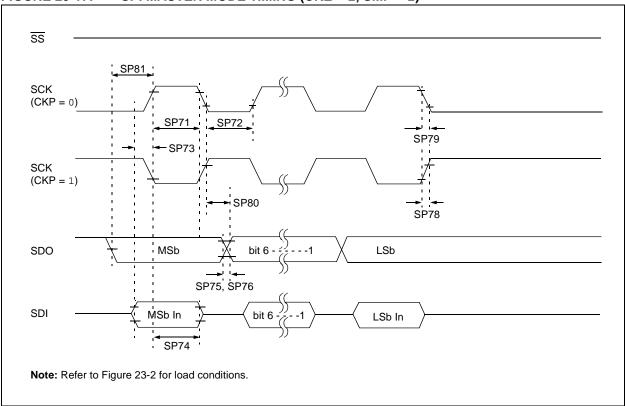

Figure 17-4 and Figure 17-5 show example waveforms of Slave mode operation.

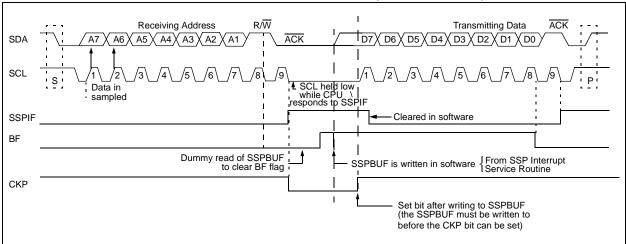

#### 17.2.6 TRANSMISSION

When the  $R/\overline{W}$  bit of the received address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set and the slave will respond to the master by reading out data. After the address match, an  $\overline{ACK}$  pulse is generated by the slave hardware and the SCL pin is held low (clock is automatically stretched) until the slave is ready to respond. See **Section 17.2.7** "Clock Stretching". The data the slave will transmit must be loaded into the SSPBUF register, which sets the BF bit. The SCL line is released by setting the CKP bit of the SSPCON register.

An SSP interrupt is generated for each transferred data byte. The SSPIF flag bit of the PIR1 register initiates an SSP interrupt, and must be cleared by software before the next byte is transmitted. The BF bit of the SSPSTAT register is cleared on the falling edge of the eighth received clock pulse. The SSPIF flag bit is set on the falling edge of the ninth clock pulse.

Following the eighth falling clock edge, control of the SDA line is released back to the master so that the master can acknowledge or not acknowledge the response. If the master sends a not acknowledge, the slave's transmission is complete and the slave must monitor for the next Start condition. If the master acknowledges, control of the bus is returned to the slave to transmit another byte of data. Just as with the previous byte, the clock is stretched by the slave, data must be loaded into the SSPBUF and CKP must be set to release the clock line (SCL).

# FIGURE 17-12: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

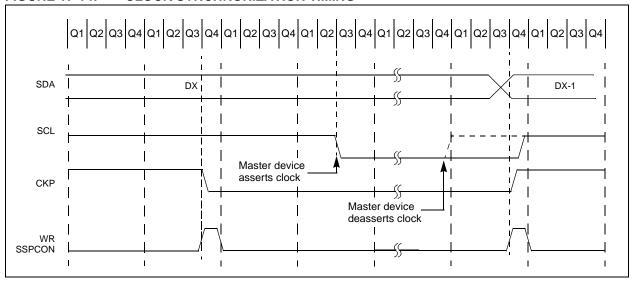

#### 17.2.10 CLOCK SYNCHRONIZATION

When the CKP bit is cleared, the SCL output is held low once it is sampled low. therefore, the CKP bit will not stretch the SCL line until an external I<sup>2</sup>C master device has already asserted the SCL line low. The SCL output will remain low until the CKP bit is set and all other devices on the I<sup>2</sup>C bus have released SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (Figure 17-14).

#### 17.2.11 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C module can receive addresses of data, and when an address match or complete byte transfer occurs, wake the processor from Sleep (if SSP interrupt is enabled).

FIGURE 17-14: CLOCK SYNCHRONIZATION TIMING

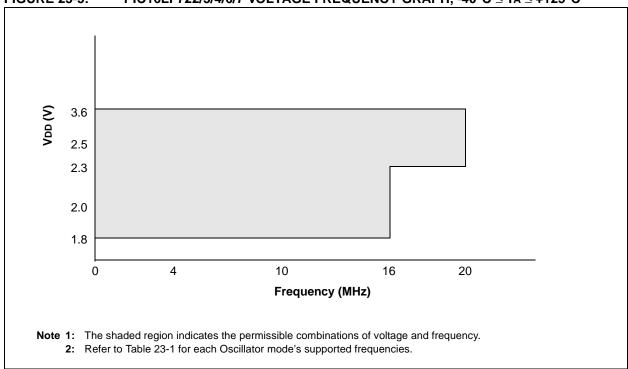

FIGURE 23-5: PIC16LF722/3/4/6/7 VOLTAGE FREQUENCY GRAPH, -40°C ≤TA ≤+125°C

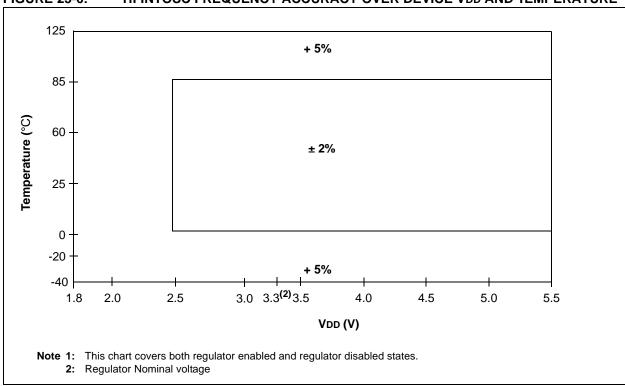

### FIGURE 23-6: HFINTOSC FREQUENCY ACCURACY OVER DEVICE VDD AND TEMPERATURE

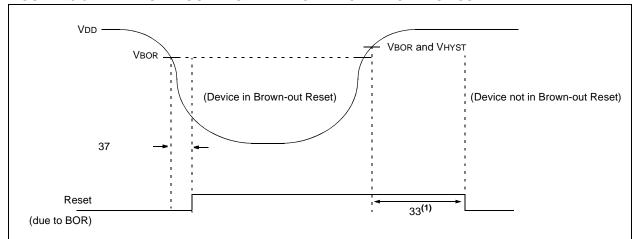

# FIGURE 23-9: BROWN-OUT RESET TIMING AND CHARACTERISTICS

**Note 1:** 64 ms delay only if PWRTE bit in the Configuration Word register is programmed to '0'.

FIGURE 23-16: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

FIGURE 23-17: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

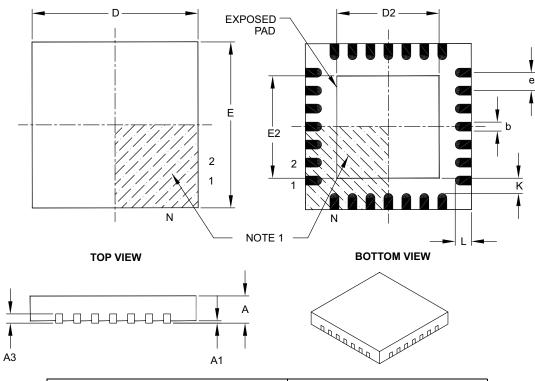

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units    |          |          |      |

|------------------------|----------|----------|----------|------|

| Dimension              | n Limits | MIN      | NOM      | MAX  |

| Number of Pins         | N        |          | 28       |      |

| Pitch                  | е        |          | 0.65 BSC |      |

| Overall Height         | Α        | 0.80     | 0.90     | 1.00 |

| Standoff               | A1       | 0.00     | 0.02     | 0.05 |

| Contact Thickness      | A3       | 0.20 REF |          |      |

| Overall Width          | Е        |          | 6.00 BSC |      |

| Exposed Pad Width      | E2       | 3.65     | 3.70     | 4.20 |

| Overall Length         | D        |          | 6.00 BSC |      |

| Exposed Pad Length     | D2       | 3.65     | 3.70     | 4.20 |

| Contact Width          | b        | 0.23     | 0.30     | 0.35 |

| Contact Length         | L        | 0.50     | 0.55     | 0.70 |

| Contact-to-Exposed Pad | K        | 0.20     | _        | _    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

# Worldwide Sales and Service

#### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277

Technical Support: http://www.microchip.com/

support Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong

Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588

Fax: 86-23-8980-9500 **China - Dongguan**

Tel: 86-769-8702-9880 **China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR Tel: 852-2943-5100

Fax: 852-2401-3431 **China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 **China - Qingdao** Tel: 86-532-8502-7355

Fax: 86-532-8502-7205 **China - Shanghai** Tel: 86-21-5407-5533

Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan**Tel: 86-27-5980-5300

Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444

Fax: 91-80-3090-4123 India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

**India - Pune** Tel: 91-20-3019-1500

Japan - Osaka

Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

**Korea - Seoul** Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

**Malaysia - Kuala Lumpur** Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065

Fax: 63-2-634-9069

**Singapore**

Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung

Tel: 886-7-213-7828

Taiwan - Taipei

Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399

Fax: 31-416-690340

**Poland - Warsaw** Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90

Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

07/14/15