Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 11x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf726-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

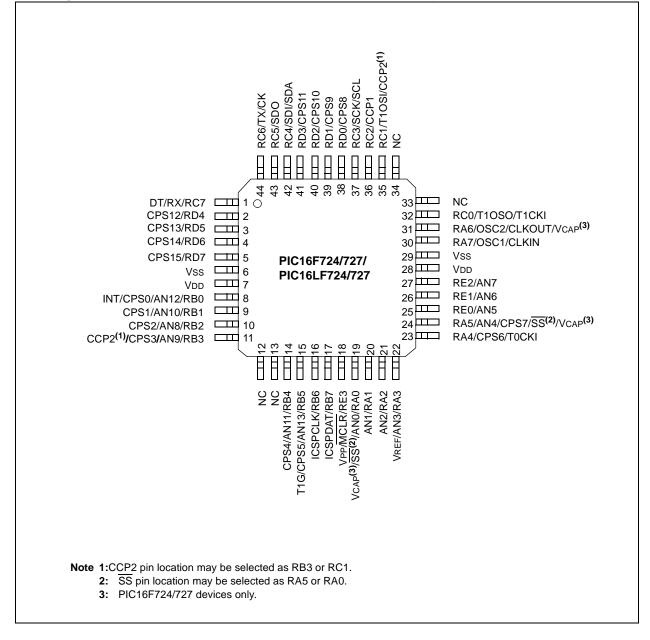

## Pin Diagrams – 44-PIN TQFP (PIC16F724/727/PIC16LF724/727)

| Address               | Name                  | Bit 7         | Bit 6         | Bit 5                   | Bit 4          | Bit 3                   | Bit 2                 | Bit 1                 | Bit 0                 | Value on:<br>POR, BOR | Page   |

|-----------------------|-----------------------|---------------|---------------|-------------------------|----------------|-------------------------|-----------------------|-----------------------|-----------------------|-----------------------|--------|

| Bank 1                |                       |               |               |                         |                |                         |                       |                       |                       |                       |        |

| 80h <sup>(2)</sup>    | INDF                  | Addressing    | this location | uses conten             | ts of FSR to a | ddress data             | memory (not           | a physical re         | gister)               | xxxx xxxx             | 29,37  |

| 81h                   | OPTION_REG            | RBPU          | INTEDG        | TOCS                    | TOSE           | PSA                     | PS2                   | PS1                   | PS0                   | 1111 1111             | 26,37  |

| 82h <sup>(2)</sup>    | PCL                   | Program Co    | ounter (PC) L | east Signific           | ant Byte       | •                       | •                     |                       | •                     | 0000 0000             | 28,37  |

| 83h <sup>(2)</sup>    | STATUS                | IRP           | RP1           | RP0                     | TO             | PD                      | Z                     | DC                    | С                     | 0001 1xxx             | 25,37  |

| 84h <sup>(2)</sup>    | FSR                   | Indirect Data | a Memory Ad   | dress Point             | er             | •                       | •                     |                       | •                     | xxxx xxxx             | 29,37  |

| 85h                   | TRISA                 | TRISA7        | TRISA6        | TRISA5                  | TRISA4         | TRISA3                  | TRISA2                | TRISA1                | TRISA0                | 1111 1111             | 51,37  |

| 86h                   | TRISB                 | TRISB7        | TRISB6        | TRISB5                  | TRISB4         | TRISB3                  | TRISB2                | TRISB1                | TRISB0                | 1111 1111             | 60,37  |

| 87h                   | TRISC                 | TRISC7        | TRISC6        | TRISC5                  | TRISC4         | TRISC3                  | TRISC2                | TRISC1                | TRISC0                | 1111 1111             | 70,37  |

| 88h <sup>(3)</sup>    | TRISD                 | TRISD7        | TRISD6        | TRISD5                  | TRISD4         | TRISD3                  | TRISD2                | TRISD1                | TRISD0                | 1111 1111             | 78,37  |

| 89h                   | TRISE                 | _             | _             | _                       | _              | TRISE3 <sup>(6)</sup>   | TRISE2 <sup>(3)</sup> | TRISE1 <sup>(3)</sup> | TRISE0 <sup>(3)</sup> | 1111                  | 81,37  |

| 8Ah <sup>(1, 2)</sup> | PCLATH                | _             | _             | _                       | Write Buffer   | for the upper           | 5 bits of the F       | Program Cou           | nter                  | 0 0000                | 28,37  |

| 8Bh <sup>(2)</sup>    | INTCON                | GIE           | PEIE          | TOIE                    | INTE           | RBIE                    | T0IF                  | INTF                  | RBIF                  | 0000 000x             | 44,37  |

| 8Ch                   | PIE1                  | TMR1GIE       | ADIE          | RCIE                    | TXIE           | SSPIE                   | CCP1IE                | TMR2IE                | TMR1IE                | 0000 0000             | 45,37  |

| 8Dh                   | PIE2                  | _             | —             | —                       | _              | —                       | _                     | _                     | CCP2IE                | 0                     | 46,37  |

| 8Eh                   | PCON                  | _             | _             | _                       | _              | _                       | _                     | POR                   | BOR                   | qq                    | 27,38  |

| 8Fh                   | T1GCON                | TMR1GE        | T1GPOL        | T1GTM                   | T1GSPM         | T <u>1GGO</u> /<br>DONE | T1GVAL                | T1GSS1                | T1GSS0                | 0000 0x00             | 118,38 |

| 90h                   | OSCCON                | _             | _             | IRCF1                   | IRCF0          | ICSL                    | ICSS                  | _                     | _                     | 10 qq                 | 87,38  |

| 91h                   | OSCTUNE               | _             | _             | TUN5                    | TUN4           | TUN3                    | TUN2                  | TUN1                  | TUN0                  | 00 0000               | 88,38  |

| 92h                   | PR2                   | Timer2 Perio  | od Register   |                         |                |                         |                       |                       |                       | 1111 1111             | 120,38 |

| 93h                   | SSPADD <sup>(5)</sup> | Synchronou    | s Serial Port | (I <sup>2</sup> C mode) | Address Regi   | ster                    |                       |                       |                       | 0000 0000             | 169,38 |

| 93h                   | SSPMSK <sup>(4)</sup> | Synchronou    | s Serial Port | (I <sup>2</sup> C mode) | Address Mas    | k Register              |                       |                       |                       | 1111 1111             | 180,38 |

| 94h                   | SSPSTAT               | SMP           | CKE           | D/A                     | Р              | S                       | R/W                   | UA                    | BF                    | 0000 0000             | 179,38 |

| 95h                   | WPUB                  | WPUB7         | WPUB6         | WPUB5                   | WPUB4          | WPUB3                   | WPUB2                 | WPUB1                 | WPUB0                 | 1111 1111             | 61,38  |

| 96h                   | IOCB                  | IOCB7         | IOCB6         | IOCB5                   | IOCB4          | IOCB3                   | IOCB2                 | IOCB1                 | IOCB0                 | 0000 0000             | 61,38  |

| 97h                   | —                     | Unimplemer    | nted          |                         |                |                         |                       |                       |                       | _                     | —      |

| 98h                   | TXSTA                 | CSRC          | TX9           | TXEN                    | SYNC           | _                       | BRGH                  | TRMT                  | TX9D                  | 0000 -010             | 147,38 |

| 99h                   | SPBRG                 | BRG7          | BRG6          | BRG5                    | BRG4           | BRG3                    | BRG2                  | BRG1                  | BRG0                  | 0000 0000             | 149,38 |

| 9Ah                   | _                     | Unimplemer    | nted          |                         |                |                         |                       |                       |                       | —                     | —      |

| 9Bh                   | _                     | Unimplemer    | nted          |                         |                |                         |                       |                       |                       | —                     | —      |

| 9Ch                   | APFCON                | _             | —             | —                       | _              | —                       | —                     | SSSEL                 | CCP2SEL               | 00                    | 50,38  |

| 9Dh                   | FVRCON                | FVRRDY        | FVREN         | —                       | —              | —                       | —                     | ADFVR1                | ADFVR0                | q000                  | 104,38 |

| 9Eh                   | _                     | Unimplemer    | nted          |                         |                |                         |                       |                       |                       | —                     | —      |

| 9Fh                   | ADCON1                | _             | ADCS2         | ADCS1                   | ADCS0          | _                       | _                     | ADREF1                | ADREF0                | 000000                | 100,38 |

#### **TABLE 2-1:** PIC16(L)F722/3/4/6/7 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are 1: transferred to the upper byte of the program counter.

2:

These registers/bits are not implemented on PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'. 3:

Accessible only when SSPM<3:0>  $\pm$  1001. Accessible only when SSPM<3:0>  $\pm$  1001. This bit is always '1' as RE3 is input-only. 4:

5: 6:

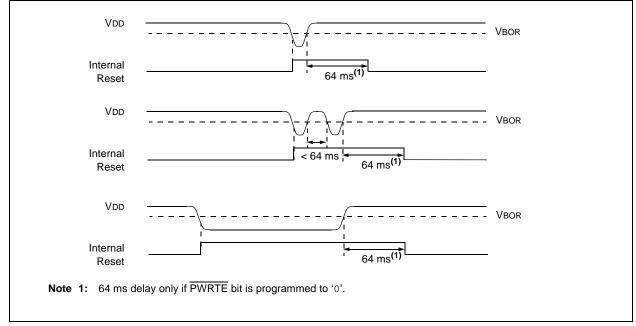

## 3.5 Brown-Out Reset (BOR)

Brown-out Reset is enabled by programming the BOREN<1:0> bits in the Configuration register. The brown-out trip point is selectable from two trip points via the BORV bit in the Configuration register.

Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

Two bits are used to enable the BOR. When BOREN = 11, the BOR is always enabled. When BOREN = 10, the BOR is enabled, but disabled during Sleep. When BOREN = 0X, the BOR is disabled.

If VDD falls below VBOR for greater than parameter (TBOR) (see **Section 23.0** "**Electrical Specifica-tions**"), the brown-out situation will reset the device. This will occur regardless of VDD slew rate. A Reset is not ensured to occur if VDD falls below VBOR for more than TBOR.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

**Note:** When erasing Flash program memory, the BOR is forced to enabled at the minimum BOR setting to ensure that any code protection circuitry is operating properly.

### FIGURE 3-3: BROWN-OUT SITUATIONS

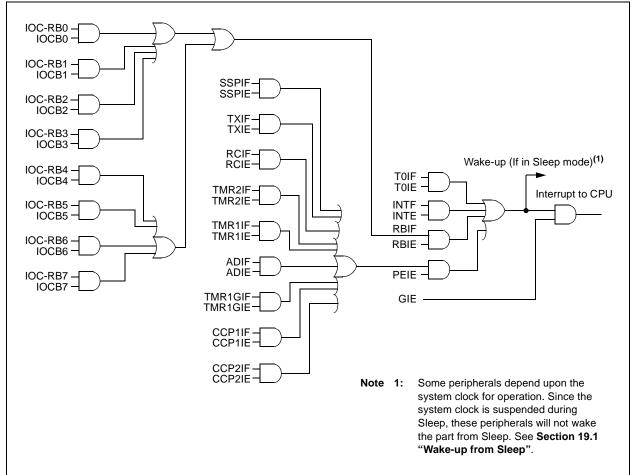

## 4.0 INTERRUPTS

The PIC16(L)F722/3/4/6/7 device family features an interruptible core, allowing certain events to preempt normal program flow. An Interrupt Service Routine (ISR) is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

The PIC16(L)F722/3/4/6/7 device family has 12 interrupt sources, differentiated by corresponding interrupt enable and flag bits:

- Timer0 Overflow Interrupt

- External Edge Detect on INT Pin Interrupt

- PORTB Change Interrupt

- Timer1 Gate Interrupt

- A/D Conversion Complete Interrupt

- AUSART Receive Interrupt

- AUSART Transmit Interrupt

- SSP Event Interrupt

- CCP1 Event Interrupt

- · Timer2 Match with PR2 Interrupt

- Timer1 Overflow Interrupt

- CCP2 Event Interrupt

A block diagram of the interrupt logic is shown in Figure 4-1.

## FIGURE 4-1: INTERRUPT LOGIC

#### 4.5.3 PIE2 REGISTER

Γ.

bit 0

The PIE2 register contains the interrupt enable bits, as shown in Register 4-3.

## Note: Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

#### REGISTER 4-3: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

| —     | —   | —   | —   | —   | —   |     | CCP2IE |

| bit 7 |     |     |     |     |     |     | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 7-1 Unimplemented: Read as '0'

CCP2IE: CCP2 Interrupt Enable bit

1 = Enables the CCP2 interrupt

0 = Disables the CCP2 interrupt

### TABLE 6-1: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name                   | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|--------|---------|---------|---------|---------|---------|---------|----------------------|---------------------------------|

| ADCON0                 | _      | _      | CHS3    | CHS2    | CHS1    | CHS0    | GO/DONE | ADON    | 0000 0000            | 0000 0000                       |

| ADCON1                 | _      | ADCS2  | ADCS1   | ADCS0   | _       | _       | ADREF1  | ADREF0  | -00000               | -00000                          |

| ANSELA                 | _      | _      | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   | 11 1111              | 11 1111                         |

| APFCON                 | _      | _      | _       | _       | _       | _       | SSSEL   | CCP2SEL | 00                   | 00                              |

| CPSCON0                | CPSON  | _      | _       | _       | CPSRNG1 | CPSRNG0 | CPSOUT  | TOXCS   | 0 0000               | 0 0000                          |

| CPSCON1                | _      | _      | _       | _       | CPSCH3  | CPSCH2  | CPSCH1  | CPSCH0  | 0000                 | 0000                            |

| CONFIG2 <sup>(1)</sup> | _      | _      | VCAPEN1 | VCAPEN0 | _       | _       | —       | _       | —                    | —                               |

| OPTION_REG             | RBPU   | INTEDG | TOCS    | T0SE    | PSA     | PS2     | PS1     | PS0     | 1111 1111            | 1111 1111                       |

| PORTA                  | RA7    | RA6    | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | xxxx xxxx            | xxxx xxxx                       |

| SSPCON                 | WCOL   | SSPOV  | SSPEN   | CKP     | SSPM3   | SSPM2   | SSPM1   | SSPM0   | 0000 0000            | 0000 0000                       |

| TRISA                  | TRISA7 | TRISA6 | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 1111 1111            | 1111 1111                       |

$\label{eq:Legend: x = unknown, u = unchanged, - = unimplemented locations read as `0'. Shaded cells are not used by PORTA.$

Note 1: PIC16F72X only.

## 10.0 FIXED VOLTAGE REFERENCE

This device contains an internal voltage regulator. To provide a reference for the regulator, a band gap reference is provided. This band gap is also user accessible via an A/D converter channel.

User level band gap functions are controlled by the FVRCON register, which is shown in Register 10-1.

## REGISTER 10-1: FVRCON: FIXED VOLTAGE REFERENCE REGISTER

| R-q             | R/W-0             | U-0              | U-0 | U-0              | U-0              | R/W-0           | R/W-0  |

|-----------------|-------------------|------------------|-----|------------------|------------------|-----------------|--------|

| FVRRDY          | FVREN             | —                | —   | —                | —                | ADFVR1          | ADFVR0 |

| bit 7           |                   |                  |     |                  |                  |                 | bit 0  |

|                 |                   |                  |     |                  |                  |                 |        |

| Legend:         |                   |                  |     |                  |                  |                 |        |

| R = Readable I  | bit               | W = Writable I   | bit | U = Unimpler     | mented bit, read | as '0'          |        |

| -n = Value at P | OR                | '1' = Bit is set |     | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| q = Value depe  | ends on condition | on               |     |                  |                  |                 |        |

| q = Value depe  | ends on condition | on               |     |                  |                  |                 |        |

| bit 7   | FVRRDY <sup>(1)</sup> : Fixed Voltage Reference Ready Flag bit                        |

|---------|---------------------------------------------------------------------------------------|

|         | 0 = Fixed Voltage Reference output is not active or stable                            |

|         | 1 = Fixed Voltage Reference output is ready for use                                   |

| bit 6   | FVREN <sup>(2)</sup> : Fixed Voltage Reference Enable bit                             |

|         | 0 = Fixed Voltage Reference is disabled                                               |

|         | 1 = Fixed Voltage Reference is enabled                                                |

| bit 5-2 | Unimplemented: Read as '0'                                                            |

| bit 1-0 | ADFVR<1:0>: A/D Converter Fixed Voltage Reference Selection bits                      |

|         | 00 = A/D Converter Fixed Voltage Reference Peripheral output is off.                  |

|         | 01 = A/D Converter Fixed Voltage Reference Peripheral output is 1x (1.024V)           |

|         | $10 = A/D$ Converter Fixed Voltage Reference Peripheral output is $2x (2.048V)^{(2)}$ |

|         | 11 = A/D Converter Fixed Voltage Reference Peripheral output is $4x (4.096V)^{(2)}$   |

| Note 1: | FVRRDY is always '1' for the PIC16F72X devices.                                       |

2: Fixed Voltage Reference output cannot exceed VDD.

#### 11.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the OPTION register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

| Note: | When the prescaler is assigned to WDT, a    |

|-------|---------------------------------------------|

|       | CLRWDT instruction will clear the prescaler |

|       | along with the WDT.                         |

#### 11.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The T0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The T0IF bit can only be cleared in software. The Timer0 interrupt enable is the T0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |

|-------|-----------------------------------------|

|       | processor from Sleep since the timer is |

|       | frozen during Sleep.                    |

#### 11.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 23.0** "**Electrical Specifications**".

## 12.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 Gate circuitry. This is also referred to as Timer1 Gate Count Enable.

Timer1 Gate can also be driven by multiple selectable sources.

#### 12.6.1 TIMER1 GATE COUNT ENABLE

The Timer1 Gate is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate (T1G) input is active, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate input is inactive, no incrementing will occur and Timer1 will hold the current count. See Figure 12-3 for timing details.

#### TABLE 12-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

#### 12.6.2 TIMER1 GATE SOURCE SELECTION

The Timer1 Gate source can be selected from one of four different sources. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

#### TABLE 12-4: TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                    |

|-------|-----------------------------------------------------------------------|

| 00    | Timer1 Gate Pin                                                       |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)               |

| 10    | Timer2 match PR2<br>(TMR2 increments to match PR2)                    |

| 11    | Count Enabled by WDT Overflow<br>(Watchdog Time-out interval expired) |

#### 12.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 Gate Control. It can be used to supply an external source to the Timer1 Gate circuitry.

#### 12.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 Gate circuitry.

#### 12.6.2.3 Timer2 Match Gate Operation

The TMR2 register will increment until it matches the value in the PR2 register. On the very next increment cycle, TMR2 will be reset to 00h. When this Reset occurs, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 Gate circuitry.

#### 12.6.2.4 Watchdog Overflow Gate Operation

The Watchdog Timer oscillator, prescaler and counter will be automatically turned on when TMR1GE = 1 and T1GSS selects the WDT as a gate source for Timer1 (T1GSS = 11). TMR1ON does not factor into the oscillator, prescaler and counter enable. See Table 12-5.

The PSA and PS bits of the OPTION register still control what time-out interval is selected. Changing the prescaler during operation may result in a spurious capture.

Enabling the Watchdog Timer oscillator does not automatically enable a Watchdog Reset or Wake-up from Sleep upon counter overflow.

| Note: | When using the WDT as a gate source for<br>Timer1, operations that clear the Watchdog |

|-------|---------------------------------------------------------------------------------------|

|       |                                                                                       |

|       | Timer (CLRWDT, SLEEP instructions) will                                               |

|       | affect the time interval being measured for                                           |

|       | capacitive sensing. This includes waking                                              |

|       | from Sleep. All other interrupts that might                                           |

|       | wake the device from Sleep should be                                                  |

|       | disabled to prevent them from disturbing                                              |

|       | the measurement period.                                                               |

As the gate signal coming from the WDT counter will generate different pulse widths depending on if the WDT is enabled, when the CLRWDT instruction is executed, and so on, Toggle mode must be used. A specific sequence is required to put the device into the correct state to capture the next WDT counter interval.

## 13.0 TIMER2 MODULE

The Timer2 module is an 8-bit timer with the following features:

- 8-bit timer register (TMR2)

- 8-bit period register (PR2)

- Interrupt on TMR2 match with PR2

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

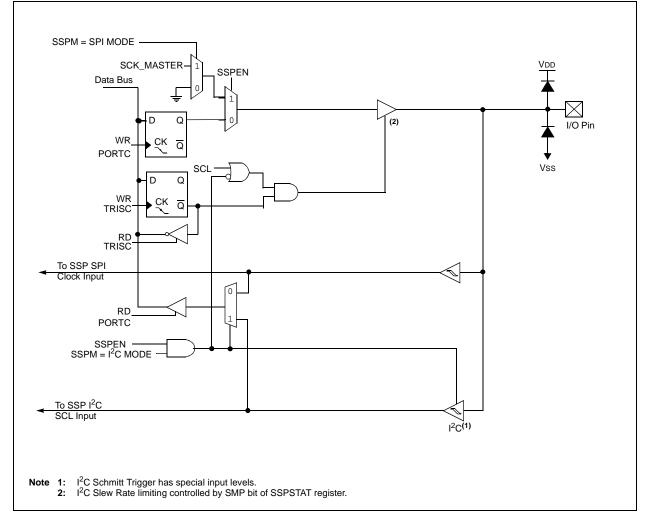

See Figure 13-1 for a block diagram of Timer2.

## 13.1 Timer2 Operation

The clock input to the Timer2 module is the system instruction clock (Fosc/4). The clock is fed into the Timer2 prescaler, which has prescale options of 1:1, 1:4 or 1:16. The output of the prescaler is then used to increment the TMR2 register.

The values of TMR2 and PR2 are constantly compared to determine when they match. TMR2 will increment from 00h until it matches the value in PR2. When a match occurs, two things happen:

- TMR2 is reset to 00h on the next increment cycle.

- The Timer2 postscaler is incremented.

The match output of the Timer2/PR2 comparator is then fed into the Timer2 postscaler. The postscaler has postscale options of 1:1 to 1:16 inclusive. The output of the Timer2 postscaler is used to set the TMR2IF interrupt flag bit in the PIR1 register.

### FIGURE 13-1: TIMER2 BLOCK DIAGRAM

The TMR2 and PR2 registers are both fully readable and writable. On any Reset, the TMR2 register is set to 00h and the PR2 register is set to FFh.

Timer2 is turned on by setting the TMR2ON bit in the T2CON register to a '1'. Timer2 is turned off by clearing the TMR2ON bit to a '0'.

The Timer2 prescaler is controlled by the T2CKPS bits in the T2CON register. The Timer2 postscaler is controlled by the TOUTPS bits in the T2CON register. The prescaler and postscaler counters are cleared when:

- A write to TMR2 occurs.

- A write to T2CON occurs.

- Any device Reset occurs (Power-on Reset, MCLR Reset, Watchdog Timer Reset, or Brown-out Reset).

Note: TMR2 is not cleared when T2CON is written.

## 17.0 SSP MODULE OVERVIEW

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripherals or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

### 17.1 SPI Mode

The SPI mode allows eight bits of data to be synchronously transmitted and received, simultaneously. The SSP module can be operated in one of two SPI modes:

- Master mode

- Slave mode

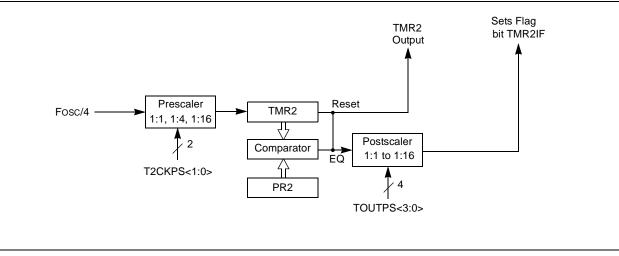

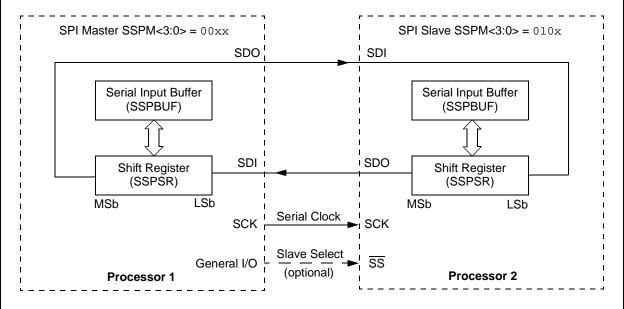

SPI is a full-duplex protocol, with all communication being bidirectional and initiated by a master device. All clocking is provided by the master device and all bits are transmitted, MSb first. Care must be taken to ensure that all devices on the SPI bus are setup to allow all controllers to send and receive data at the same time. A typical SPI connection between microcontroller devices is shown in Figure 17-1. Addressing of more than one slave device is accomplished via multiple hardware slave select lines. External hardware and additional I/O pins must be used to support multiple slave select addressing. This prevents extra overhead in software for communication.

For SPI communication, typically three pins are used:

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS)

## 21.0 INSTRUCTION SET SUMMARY

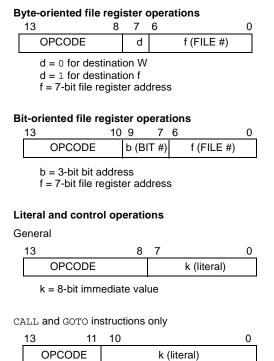

The PIC16(L)F722/3/4/6/7 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 21-1, while the various opcode fields are summarized in Table 21-1.

Table 21-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8-bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 21.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF PORTB instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended consequence of clearing the condition that set the RBIF flag.

#### TABLE 21-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                     |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |  |  |

| W     | Working register (accumulator)                                                                                                                                                  |  |  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |  |  |

| k     | Literal field, constant data or label                                                                                                                                           |  |  |

| x     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ . It is<br>the recommended form of use for<br>compatibility with all Microchip software tools. |  |  |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                             |  |  |

| PC    | Program Counter                                                                                                                                                                 |  |  |

| TO    | Time-out bit                                                                                                                                                                    |  |  |

| С     | Carry bit                                                                                                                                                                       |  |  |

| DC    | Digit carry bit                                                                                                                                                                 |  |  |

| Z     | Zero bit                                                                                                                                                                        |  |  |

| PD    | Power-down bit                                                                                                                                                                  |  |  |

## FIGURE 21-1: GENERAL FORMAT FOR INSTRUCTIONS

## 22.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 22.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 22.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 22.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 22.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

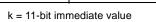

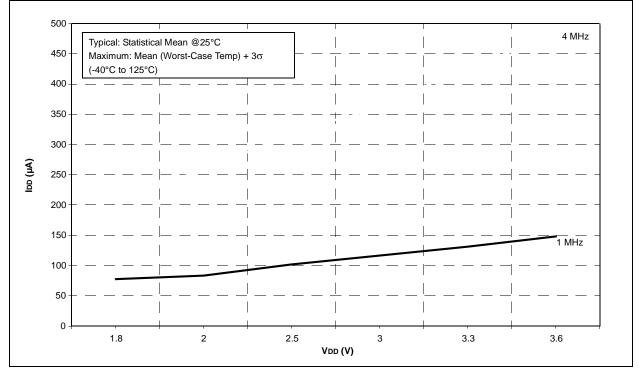

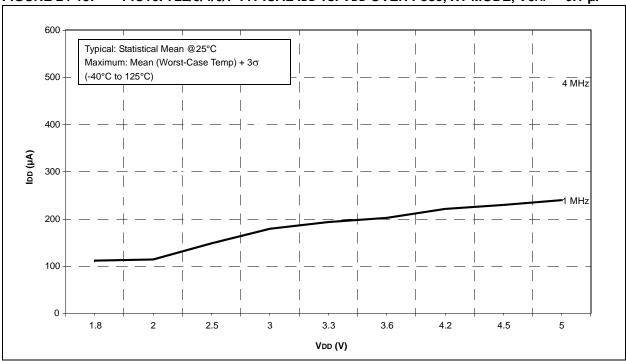

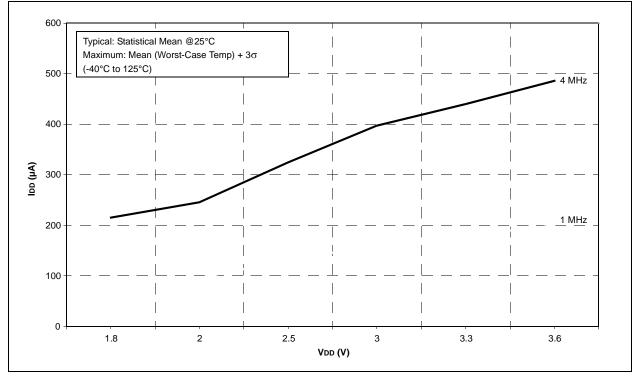

## FIGURE 24-5: PIC16F722/3/4/6/7 MAXIMUM IDD vs. VDD OVER Fosc, EXTRC MODE, VCAP = $0.1 \mu$ F

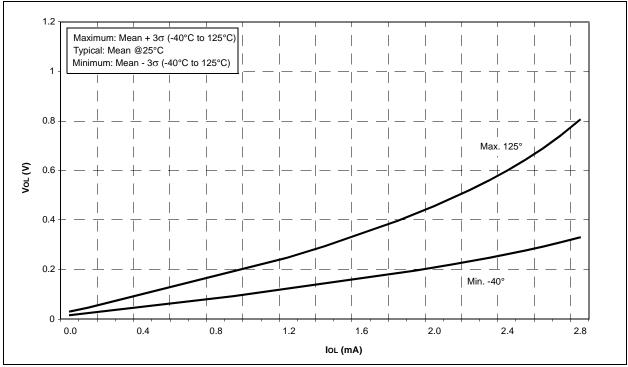

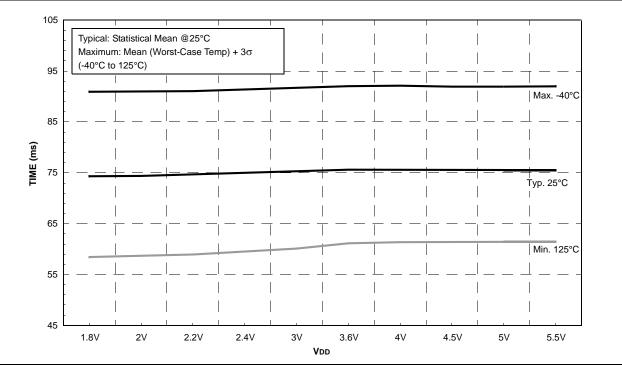

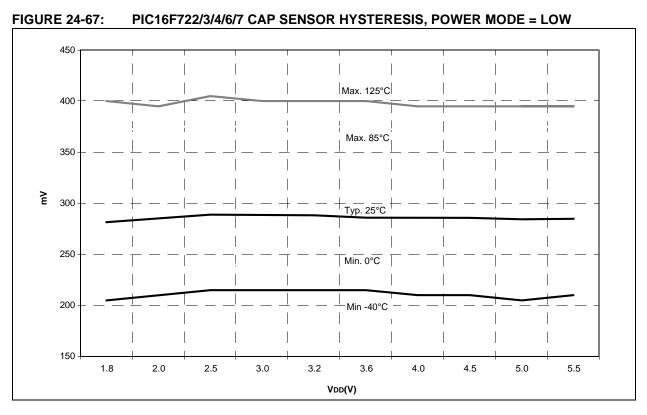

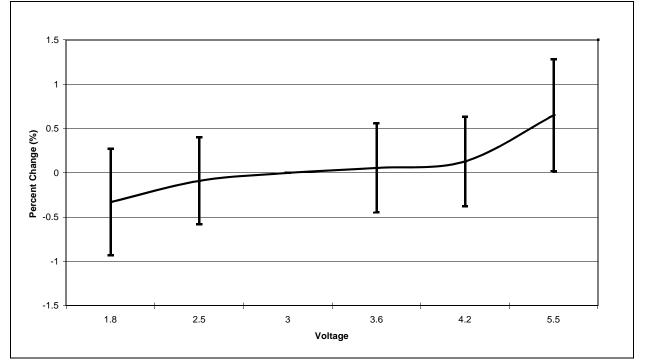

FIGURE 24-68: TYPICAL FVR (X1 AND X2) VS. SUPPLY VOLTAGE (V) NORMALIZED AT 3.0V

## 25.0 PACKAGING INFORMATION

## 25.1 Package Marking Information

#### 28-Lead SPDIP

#### 40-Lead PDIP

### Example

### Example

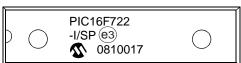

#### 28-Lead QFN/UQFN

Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                      | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC <sup>®</sup> designator (e3)<br>can be found on the outer packaging for this package. |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                           |

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

NOTES: