Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 11x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf726-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### PIC16(L)F72X Family Types

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data SRAM<br>(bytes) | High-Endurance Flash<br>Memory (bytes) | I/O's <sup>(2)</sup> | 8-bit ADC (ch) | CapSense (ch) | Timers<br>(8/16-bit) | AUSART | SSP (I <sup>2</sup> C/SPI) | ССР | Debug <sup>(1)</sup> | ХГР |

|---------------|------------------|---------------------------------|----------------------|----------------------------------------|----------------------|----------------|---------------|----------------------|--------|----------------------------|-----|----------------------|-----|

| PIC16(L)F707  | (1)              | 8192                            | 363                  | 0                                      | 36                   | 14             | 32            | 4/2                  | 1      | 1                          | 2   |                      | Y   |

| PIC16(L)F720  | (2)              | 2048                            | 128                  | 128                                    | 18                   | 12             | _             | 2/1                  | 1      | 1                          | 1   | I                    | Y   |

| PIC16(L)F721  | (2)              | 4096                            | 256                  | 128                                    | 18                   | 12             | _             | 2/1                  | 1      | 1                          | 1   | I                    | Y   |

| PIC16(L)F722  | (4)              | 2048                            | 128                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | -                    | Y   |

| PIC16(L)F722A | (3)              | 2048                            | 128                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

| PIC16(L)F723  | (4)              | 4096                            | 192                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | Ι                    | Y   |

| PIC16(L)F723A | (3)              | 4096                            | 192                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | -                    | Y   |

| PIC16(L)F724  | (4)              | 4096                            | 192                  | 0                                      | 36                   | 14             | 16            | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

| PIC16(L)F726  | (4)              | 8192                            | 368                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | Ι                    | Y   |

| PIC16(L)F727  | (4)              | 8192                            | 368                  | 0                                      | 36                   | 14             | 16            | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

**Note 1:** I - Debugging, Integrated on Chip; H - Debugging, Requires Debug Header.

2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

- 1: DS41418 PIC16(L)F707 Data Sheet, 40/44-Pin Flash, 8-bit Microcontrollers

- 2: DS41430 PIC16(L)F720/721 Data Sheet, 20-Pin Flash, 8-bit Microcontrollers

- 3: DS41417 PIC16(L)F722A/723A Data Sheet, 28-Pin Flash, 8-bit Microcontrollers

- 4: DS41341 PIC16(L)F72X Data Sheet, 28/40/44-Pin Flash, 8-bit Microcontrollers

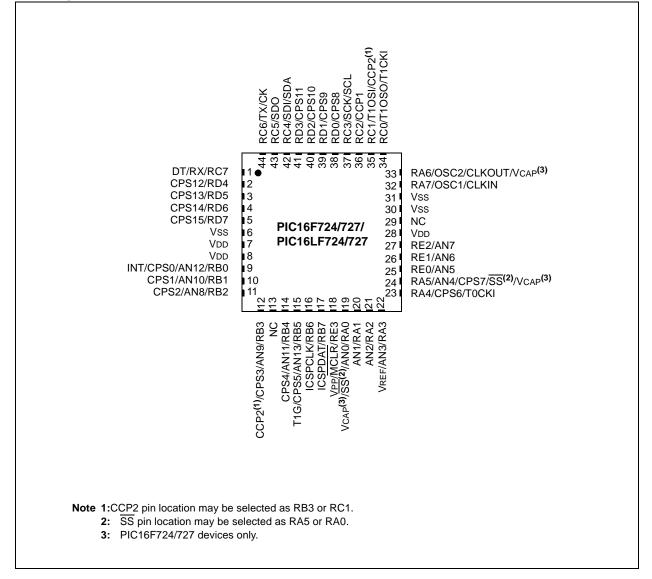

# PIC16(L)F722/3/4/6/7

| Name               | Function | Input<br>Type    | Output<br>Type | Description                                                                                          |

|--------------------|----------|------------------|----------------|------------------------------------------------------------------------------------------------------|

| RB4/AN11/CPS4      | RB4      | TTL              | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |

|                    | AN11     | AN               | _              | A/D Channel 11 input.                                                                                |

|                    | CPS4     | AN               | _              | Capacitive sensing input 4.                                                                          |

| RB5/AN13/CPS5/T1G  | RB5      | TTL              | CMOS           | General purpose I/O. Individually controlled inter-                                                  |

|                    |          |                  | CIVIOS         | rupt-on-change. Individually enabled pull-up.                                                        |

|                    | AN13     | AN               | —              | A/D Channel 13 input.                                                                                |

|                    | CPS5     | AN               | —              | Capacitive sensing input 5.                                                                          |

|                    | T1G      | ST               | —              | Timer1 Gate input.                                                                                   |

| RB6/ICSPCLK/ICDCLK | RB6      | TTL              | CMOS           | General purpose I/O. Individually controlled inter-<br>rupt-on-change. Individually enabled pull-up. |

|                    | ICSPCLK  | ST               | _              | Serial Programming Clock.                                                                            |

|                    | ICDCLK   | ST               | _              | In-Circuit Debug Clock.                                                                              |

| RB7/ICSPDAT/ICDDAT | RB7      | TTL              | CMOS           | General purpose I/O. Individually controlled inter-                                                  |

|                    |          |                  |                | rupt-on-change. Individually enabled pull-up.                                                        |

|                    | ICSPDAT  | ST               | CMOS           | ICSP™ Data I/O.                                                                                      |

|                    | ICDDAT   | ST               | —              | In-Circuit Data I/O.                                                                                 |

| RC0/T1OSO/T1CKI    | RC0      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | T1OSO    | XTAL             | XTAL           | Timer1 oscillator connection.                                                                        |

|                    | T1CKI    | ST               | _              | Timer1 clock input.                                                                                  |

| RC1/T1OSI/CCP2     | RC1      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | T10SI    | XTAL             | XTAL           | Timer1 oscillator connection.                                                                        |

|                    | CCP2     | ST               | CMOS           | Capture/Compare/PWM2.                                                                                |

| RC2/CCP1           | RC2      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | CCP1     | ST               | CMOS           | Capture/Compare/PWM1.                                                                                |

| RC3/SCK/SCL        | RC3      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | SCK      | ST               | CMOS           | SPI clock.                                                                                           |

|                    | SCL      | l <sup>2</sup> C | OD             | I <sup>2</sup> C clock.                                                                              |

| RC4/SDI/SDA        | RC4      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | SDI      | ST               | _              | SPI data input.                                                                                      |

|                    | SDA      | l <sup>2</sup> C | OD             | I <sup>2</sup> C data input/output.                                                                  |

| RC5/SDO            | RC5      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | SDO      | _                | CMOS           | SPI data output.                                                                                     |

| RC6/TX/CK          | RC6      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | ТХ       | _                | CMOS           | USART asynchronous transmit.                                                                         |

|                    | СК       | ST               | CMOS           | USART synchronous clock.                                                                             |

| RC7/RX/DT          | RC7      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | RX       | ST               | _              | USART asynchronous input.                                                                            |

|                    | DT       | ST               | CMOS           | USART synchronous data.                                                                              |

| RD0/CPS8           | RD0      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | CPS8     | AN               | _              | Capacitive sensing input 8.                                                                          |

| RD1/CPS9           | RD1      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    | CPS9     | AN               |                | Capacitive sensing input 9.                                                                          |

| RD2/CPS10          | RD2      | ST               | CMOS           | General purpose I/O.                                                                                 |

|                    |          |                  |                |                                                                                                      |

| TABLE 1-1: | PIC16(L)F722/3/4/6/7 PINOUT DESCRIPTION (CONTINUED) |

|------------|-----------------------------------------------------|

| IABLE 1-1: | PIC16(L)F/22/3/4/6/7 PINOUT DESCRIPTION (CONTINUED) |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output

XTAL = Crystal levels HV = High Voltage

| FIGURE 2-5: | PIC16F723/LF723 AND PIC16F724/LF724 SPECIAL FUNCTION REGISTERS |

|-------------|----------------------------------------------------------------|

|             |                                                                |

| Indirect addr. <sup>(*)</sup> | 00h     | Indirect addr. <sup>(*)</sup>   | 80h    | Indirect addr. <sup>(*)</sup>           | 100h         | Indirect addr.(*)     | 180h |

|-------------------------------|---------|---------------------------------|--------|-----------------------------------------|--------------|-----------------------|------|

| TMR0                          | 01h     | OPTION                          | 81h    | TMR0                                    | 101h         | OPTION                | 181h |

| PCL                           | 02h     | PCL                             | 82h    | PCL                                     | 102h         | PCL                   | 182h |

| STATUS                        | 03h     | STATUS                          | 83h    | STATUS                                  | 103h         | STATUS                | 183h |

| FSR                           | 04h     | FSR                             | 84h    | FSR                                     | 104h         | FSR                   | 184h |

| PORTA                         | 05h     | TRISA                           | 85h    |                                         | 105h         | ANSELA                | 185h |

| PORTB                         | 06h     | TRISB                           | 86h    |                                         | 106h         | ANSELB                | 186h |

| PORTC                         | 07h     | TRISC                           | 87h    |                                         | 107h         |                       | 187h |

| PORTD <sup>(1)</sup>          | 08h     | TRISD <sup>(1)</sup>            | 88h    | CPSCON0                                 | 108h         | ANSELD <sup>(1)</sup> | 188h |

| PORTE                         | 09h     | TRISE                           | 89h    | CPSCON1                                 | 109h         | ANSELE <sup>(1)</sup> | 189h |

| PCLATH                        | 0Ah     | PCLATH                          | 8Ah    | PCLATH                                  | 10Ah         | PCLATH                | 18Ah |

| INTCON                        | 0Bh     | INTCON                          | 8Bh    | INTCON                                  | 10Bh         | INTCON                | 18Bh |

| PIR1                          | 0Ch     | PIE1                            | 8Ch    | PMDATL                                  | 10Ch         | PMCON1                | 18Ch |

| PIR2                          | 0Dh     | PIE2                            | 8Dh    | PMADRL                                  | 10Dh         | Reserved              | 18Dh |

| TMR1L                         | 0Eh     | PCON                            | 8Eh    | PMDATH                                  | 10Eh         | Reserved              | 18Eh |

| TMR1H                         | 0Fh     | T1GCON                          | 8Fh    | PMADRH                                  | 10Fh         | Reserved              | 18Fh |

| T1CON                         | 10h     | OSCCON                          | 90h    |                                         | 110h         |                       | 190h |

| TMR2                          | 11h     | OSCTUNE                         | 91h    |                                         | 111h         |                       | 191h |

| T2CON                         | 12h     | PR2                             | 92h    |                                         | 112h         |                       | 192h |

| SSPBUF                        | 13h     | SSPADD/SSPMSK                   | 93h    |                                         | 113h         |                       | 193h |

| SSPCON                        | 14h     | SSPSTAT                         | 94h    |                                         | 114h         |                       | 194h |

| CCPR1L                        | 15h     | WPUB                            | 95h    |                                         | 115h         |                       | 195h |

| CCPR1H                        | 16h     | IOCB                            | 96h    | -                                       | 116h         |                       | 196h |

| CCP1CON                       | 17h     |                                 | 97h    | -                                       | 117h         |                       | 197h |

| RCSTA                         | 18h     | TXSTA                           | 98h    | -                                       | 118h         |                       | 198h |

| TXREG                         | 19h     | SPBRG                           | 99h    |                                         | 119h         |                       | 199h |

| RCREG                         | 1Ah     |                                 | 9Ah    |                                         | 11Ah         |                       | 19Ah |

| CCPR2L                        | 1Bh     |                                 | 9Bh    |                                         | 11Bh         |                       | 19Bh |

| CCPR2H                        | 1Ch     | APFCON                          | 9Ch    |                                         | 11Ch         |                       | 19Ch |

| CCP2CON                       | 1Dh     | FVRCON                          | 9Dh    |                                         | 11Dh         |                       | 19Dh |

| ADRES                         | 1Eh     |                                 | 9Eh    |                                         | 11Eh         |                       | 19Eh |

| ADCON0                        | 1Fh     | ADCON1                          | 9Fh    |                                         | 11Fh         |                       | 19Fh |

|                               | 20h     | General                         | A0h    | General Purpose<br>Register             | 120h         |                       | 1A0h |

| General<br>Purpose            |         | Purpose<br>Register<br>80 Bytes |        | 16 Bytes                                | 12Fh<br>130h |                       |      |

| Register                      |         |                                 | EFh    |                                         | 16Fh         |                       | 1EFh |

| 96 Bytes                      |         | Accesses<br>70h-7Fh             | F0h    | Accesses<br>70h-7Fh                     | 170h         | Accesses<br>70h-7Fh   | 1F0h |

|                               | 7Fh     | 701-7111                        | FFh    | / ///////////////////////////////////// | 17Fh         | 701-7111              | 1FFh |

| Bank 0                        | ],      | Bank 1                          | l      | Bank 2                                  | ]            | Bank 3                | J    |

| nd: = Unimple                 | emented | data memory locatio             | ns rea | d as '0'                                |              |                       |      |

# PIC16(L)F722/3/4/6/7

| Address               | Name                  | Bit 7         | Bit 6         | Bit 5                   | Bit 4          | Bit 3                   | Bit 2                 | Bit 1                 | Bit 0                 | Value on:<br>POR, BOR | Page   |

|-----------------------|-----------------------|---------------|---------------|-------------------------|----------------|-------------------------|-----------------------|-----------------------|-----------------------|-----------------------|--------|

| Bank 1                |                       |               |               |                         |                |                         |                       |                       |                       |                       |        |

| 80h <sup>(2)</sup>    | INDF                  | Addressing    | this location | uses conten             | ts of FSR to a | ddress data             | memory (not           | a physical re         | gister)               | xxxx xxxx             | 29,37  |

| 81h                   | OPTION_REG            | RBPU          | INTEDG        | TOCS                    | TOSE           | PSA                     | PS2                   | PS1                   | PS0                   | 1111 1111             | 26,37  |

| 82h <sup>(2)</sup>    | PCL                   | Program Co    | ounter (PC) L | east Signific           | ant Byte       | •                       | •                     |                       | •                     | 0000 0000             | 28,37  |

| 83h <sup>(2)</sup>    | STATUS                | IRP           | RP1           | RP0                     | TO             | PD                      | Z                     | DC                    | С                     | 0001 1xxx             | 25,37  |

| 84h <sup>(2)</sup>    | FSR                   | Indirect Data | a Memory Ad   | dress Point             | er             | •                       | •                     |                       | •                     | xxxx xxxx             | 29,37  |

| 85h                   | TRISA                 | TRISA7        | TRISA6        | TRISA5                  | TRISA4         | TRISA3                  | TRISA2                | TRISA1                | TRISA0                | 1111 1111             | 51,37  |

| 86h                   | TRISB                 | TRISB7        | TRISB6        | TRISB5                  | TRISB4         | TRISB3                  | TRISB2                | TRISB1                | TRISB0                | 1111 1111             | 60,37  |

| 87h                   | TRISC                 | TRISC7        | TRISC6        | TRISC5                  | TRISC4         | TRISC3                  | TRISC2                | TRISC1                | TRISC0                | 1111 1111             | 70,37  |

| 88h <sup>(3)</sup>    | TRISD                 | TRISD7        | TRISD6        | TRISD5                  | TRISD4         | TRISD3                  | TRISD2                | TRISD1                | TRISD0                | 1111 1111             | 78,37  |

| 89h                   | TRISE                 | _             | _             | _                       | _              | TRISE3 <sup>(6)</sup>   | TRISE2 <sup>(3)</sup> | TRISE1 <sup>(3)</sup> | TRISE0 <sup>(3)</sup> | 1111                  | 81,37  |

| 8Ah <sup>(1, 2)</sup> | PCLATH                | _             | _             | _                       | Write Buffer   | for the upper           | 5 bits of the F       | Program Cou           | nter                  | 0 0000                | 28,37  |

| 8Bh <sup>(2)</sup>    | INTCON                | GIE           | PEIE          | TOIE                    | INTE           | RBIE                    | T0IF                  | INTF                  | RBIF                  | 0000 000x             | 44,37  |

| 8Ch                   | PIE1                  | TMR1GIE       | ADIE          | RCIE                    | TXIE           | SSPIE                   | CCP1IE                | TMR2IE                | TMR1IE                | 0000 0000             | 45,37  |

| 8Dh                   | PIE2                  | _             | —             | —                       | _              | —                       | _                     | _                     | CCP2IE                | 0                     | 46,37  |

| 8Eh                   | PCON                  | _             | _             | _                       | _              | _                       | _                     | POR                   | BOR                   | qq                    | 27,38  |

| 8Fh                   | T1GCON                | TMR1GE        | T1GPOL        | T1GTM                   | T1GSPM         | T <u>1GGO</u> /<br>DONE | T1GVAL                | T1GSS1                | T1GSS0                | 0000 0x00             | 118,38 |

| 90h                   | OSCCON                | _             | _             | IRCF1                   | IRCF0          | ICSL                    | ICSS                  | _                     | _                     | 10 qq                 | 87,38  |

| 91h                   | OSCTUNE               | _             | _             | TUN5                    | TUN4           | TUN3                    | TUN2                  | TUN1                  | TUN0                  | 00 0000               | 88,38  |

| 92h                   | PR2                   | Timer2 Perio  | od Register   |                         |                |                         |                       |                       |                       | 1111 1111             | 120,38 |

| 93h                   | SSPADD <sup>(5)</sup> | Synchronou    | s Serial Port | (I <sup>2</sup> C mode) | Address Regi   | ster                    |                       |                       |                       | 0000 0000             | 169,38 |

| 93h                   | SSPMSK <sup>(4)</sup> | Synchronou    | s Serial Port | (I <sup>2</sup> C mode) | Address Mas    | k Register              |                       |                       |                       | 1111 1111             | 180,38 |

| 94h                   | SSPSTAT               | SMP           | CKE           | D/A                     | Р              | S                       | R/W                   | UA                    | BF                    | 0000 0000             | 179,38 |

| 95h                   | WPUB                  | WPUB7         | WPUB6         | WPUB5                   | WPUB4          | WPUB3                   | WPUB2                 | WPUB1                 | WPUB0                 | 1111 1111             | 61,38  |

| 96h                   | IOCB                  | IOCB7         | IOCB6         | IOCB5                   | IOCB4          | IOCB3                   | IOCB2                 | IOCB1                 | IOCB0                 | 0000 0000             | 61,38  |

| 97h                   | —                     | Unimplemer    | nted          |                         |                |                         |                       |                       |                       | _                     | —      |

| 98h                   | TXSTA                 | CSRC          | TX9           | TXEN                    | SYNC           | _                       | BRGH                  | TRMT                  | TX9D                  | 0000 -010             | 147,38 |

| 99h                   | SPBRG                 | BRG7          | BRG6          | BRG5                    | BRG4           | BRG3                    | BRG2                  | BRG1                  | BRG0                  | 0000 0000             | 149,38 |

| 9Ah                   | _                     | Unimplemer    | nted          |                         |                |                         |                       |                       |                       | —                     | —      |

| 9Bh                   | _                     | Unimplemer    | nted          |                         |                |                         |                       |                       |                       | —                     | —      |

| 9Ch                   | APFCON                | _             | —             | —                       | _              | —                       | —                     | SSSEL                 | CCP2SEL               | 00                    | 50,38  |

| 9Dh                   | FVRCON                | FVRRDY        | FVREN         | —                       | _              | —                       | —                     | ADFVR1                | ADFVR0                | q000                  | 104,38 |

| 9Eh                   | _                     | Unimplemer    | nted          |                         |                |                         |                       |                       |                       | —                     | —      |

| 9Fh                   | ADCON1                | _             | ADCS2         | ADCS1                   | ADCS0          | _                       | _                     | ADREF1                | ADREF0                | 000000                | 100,38 |

#### **TABLE 2-1:** PIC16(L)F722/3/4/6/7 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are 1: transferred to the upper byte of the program counter.

2:

These registers/bits are not implemented on PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'. 3:

Accessible only when SSPM<3:0>  $\pm$  1001. Accessible only when SSPM<3:0>  $\pm$  1001. This bit is always '1' as RE3 is input-only. 4:

5: 6:

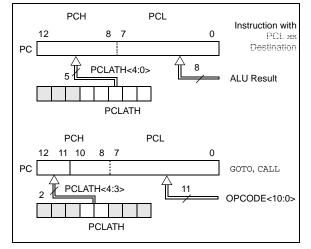

# 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-7 shows the two situations for the loading of the PC. The upper example in Figure 2-7 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-7 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 2-7: LOADING OF PC IN DIFFERENT SITUATIONS

#### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the Application Note *AN556, Implementing a Table Read* (DS00556).

#### 2.3.2 STACK

All devices have an 8-level x 13-bit wide hardware stack (refer to Figures 2-1 and 2-3). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth PUSH overwrites the value that was stored from the first PUSH. The tenth PUSH overwrites the second PUSH (and so on).

- Note 1: There are no Status bits to indicate Stack Overflow or Stack Underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

# 2.4 **Program Memory Paging**

All devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper two bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is POPed off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the RETURN instructions (which POPs the address from the stack).

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 500 | h       |                     |  |  |  |  |

|---------|---------|---------|---------------------|--|--|--|--|

|         | PAGESEL | SUB_P1  | ;Select page 1      |  |  |  |  |

|         |         |         | ;(800h-FFFh)        |  |  |  |  |

|         | CALL    | SUB1_P1 | ;Call subroutine in |  |  |  |  |

|         | :       |         | ;page 1 (800h-FFFh) |  |  |  |  |

|         | :       |         |                     |  |  |  |  |

|         | ORG     | 900h    | ;page 1 (800h-FFFh) |  |  |  |  |

| SUB1_P1 |         |         |                     |  |  |  |  |

|         | :       |         | ;called subroutine  |  |  |  |  |

|         |         |         | ;page 1 (800h-FFFh) |  |  |  |  |

|         | :       |         |                     |  |  |  |  |

|         | RETURN  |         | ;return to          |  |  |  |  |

|         |         |         | ;Call subroutine    |  |  |  |  |

|         |         |         | ;in page 0          |  |  |  |  |

|         |         |         | ;(000h-7FFh)        |  |  |  |  |

Note: The contents of the PCLATH register are unchanged after a RETURN or RETFIE instruction is executed. The user must rewrite the contents of the PCLATH register for any subsequent subroutine calls or GOTO instructions.

# 8.0 DEVICE CONFIGURATION

Device Configuration consists of Configuration Word 1 and Configuration Word 2 registers, Code Protection and Device ID.

#### 8.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 register at 2007h and Configuration Word 2 register at 2008h. These registers are only accessible during programming.

#### REGISTER 8-1: CONFIG1: CONFIGURATION WORD REGISTER 1

|        |   | R/P-1 | R/P-1 | U-1 <sup>(4)</sup> | R/P-1 | R/P-1  | R/P-1  |

|--------|---|-------|-------|--------------------|-------|--------|--------|

| —      | _ | DEBUG | PLLEN | _                  | BORV  | BOREN1 | BOREN0 |

| bit 15 |   |       |       |                    |       |        | bit 8  |

| U-1 <sup>(4)</sup> | R/P-1 |

|--------------------|-------|-------|-------|-------|-------|-------|-------|

| _                  | CP    | MCLRE | PWRTE | WDTE  | FOSC2 | FOSC1 | FOSC0 |

| bit 7              |       |       |       |       |       |       | bit 0 |

| Legend:           | P = Programmable bit |                                    |                    |  |

|-------------------|----------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 13              | <b>DEBUG:</b> In-Circuit Debugger Mode bit<br>1 = In-Circuit Debugger disabled, RB6/ICSPCLK and RB7/ICSPDAT are general purpose I/O pins<br>0 = In-Circuit Debugger enabled, RB6/ICSPCLK and RB7/ICSPDAT are dedicated to the debugger                            |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bit 12              | PLLEN: INTOSC PLL Enable bit<br>0 = INTOSC Frequency is 500 kHz<br>1 = INTOSC Frequency is 16 MHz (32x)                                                                                                                                                           |  |

| bit 11              | Unimplemented: Read as '1'                                                                                                                                                                                                                                        |  |

| bit 10              | <b>BORV:</b> Brown-out Reset Voltage selection bit<br>0 = Brown-out Reset Voltage (VBOR) set to 2.5 V nominal<br>1 = Brown-out Reset Voltage (VBOR) set to 1.9 V nominal                                                                                          |  |

| bit 9-8             | <b>BOREN&lt;1:0&gt;:</b> Brown-out Reset Selection bits <sup>(1)</sup><br>0x = BOR disabled (Preconditioned State)<br>10 = BOR enabled during operation and disabled in Sleep<br>11 = BOR enabled                                                                 |  |

| bit 7               | Unimplemented: Read as '1'                                                                                                                                                                                                                                        |  |

| bit 6               | <b>CP</b> : Code Protection bit <sup>(2)</sup><br>1 = Program memory code protection is disabled<br>0 = Program memory code protection is enabled                                                                                                                 |  |

| bit 5               | MCLRE: <u>RE3/MCLR</u> pin function select bit <sup>(3)</sup><br>1 = RE3/ <u>MCLR</u> pin function is MCLR<br>0 = RE3/MCLR pin function is digital input, MCLR internally tied to VDD                                                                             |  |

| Note 1:<br>2:<br>3: | Enabling Brown-out Reset does not automatically enable Power-up Timer.<br>The entire program memory will be erased when the code protection is turned off.<br>When $\overline{MCLR}$ is asserted in INTOSC or RC mode, the internal clock oscillator is disabled. |  |

**4:** MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

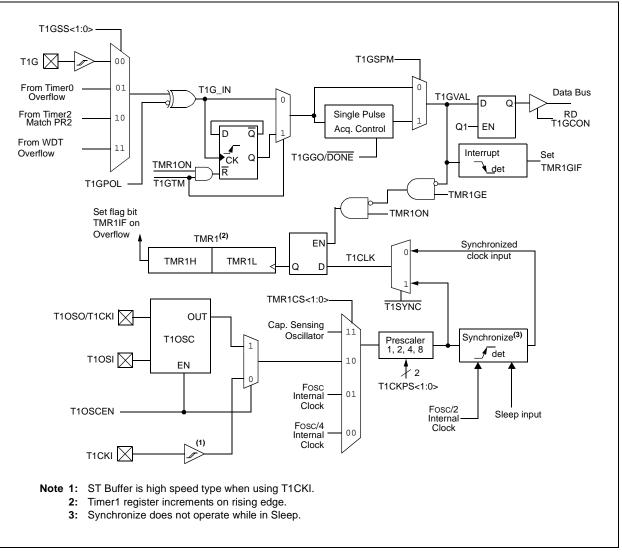

# 12.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- 3-bit prescaler

- Dedicated LP oscillator circuit

- Synchronous or asynchronous operation

- Multiple Timer1 gate (count enable) sources

- Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Time base for the Capture/Compare function

- Special Event Trigger (with CCP)

- Gate Single-pulse mode

- Gate Value StatusGate Event Interrupt

· Gate Toggle mode

Selectable Gate Source Polarity

Figure 12-1 is a block diagram of the Timer1 module.

#### FIGURE 12-1: TIMER1 BLOCK DIAGRAM

# 14.6 Operation during Sleep

The capacitive sensing oscillator will continue to run as long as the module is enabled, independent of the part being in Sleep. In order for the software to determine if a frequency change has occurred, the part must be awake. However, the part does not have to be awake when the timer resource is acquiring counts. One way to acquire the Timer1 counts while in Sleep is to have Timer1 gated with the overflow of the Watchdog Timer. This can be accomplished using the following steps:

- 1. Configure the Watchdog Time-out overflow as the Timer1's gate source T1GSS<1:0> = 11.

- 2. Set Timer1 Gate to toggle mode by setting the T1GTM bit of the T1GCON register.

- 3. Set the TMR1GE bit of the T1GCON register.

- 4. Set TMR1ON bit of the T1CON register.

- 5. Enable capacitive sensing module with the appropriate current settings and pin selection.

- 6. Clear Timer1.

- 7. Put the part to Sleep.

- 8. On the first WDT overflow, the capacitive sensing oscillator will begin to increment Timer1. Then put the part to Sleep.

- 9. On the second WDT overflow Timer1 will stop incrementing. Then run the software routine to determine if a frequency change has occurred.

Refer to Section 12.0 "Timer1 Module with Gate Control" for additional information.

- Note 1: When using the WDT to set the interval on Timer1, any other source that wakes the part up early will cause the WDT overflow to be delayed, affecting the value captured by Timer1.

- 2: Timer0 does not operate when in Sleep, and therefore cannot be used for capacitive sense measurements in Sleep.

| R/W-0           | U-0                                                                                                                                                                                                                                                                                                                                                    | U-0                                               | U-0                                             | R/W-0                                    | R/W-0                                      | R-0             | R/W-0 |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------|------------------------------------------|--------------------------------------------|-----------------|-------|--|

| CPSON           | —                                                                                                                                                                                                                                                                                                                                                      | —                                                 | _                                               | CPSRNG1                                  | CPSRNG0                                    | CPSOUT          | TOXCS |  |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                        |                                                   |                                                 |                                          |                                            |                 | bit 0 |  |

|                 |                                                                                                                                                                                                                                                                                                                                                        |                                                   |                                                 |                                          |                                            |                 |       |  |

| Legend:         |                                                                                                                                                                                                                                                                                                                                                        |                                                   |                                                 |                                          |                                            |                 |       |  |

| R = Readable I  | bit                                                                                                                                                                                                                                                                                                                                                    | W = Writable I                                    | oit                                             | U = Unimpler                             | nented bit, read                           | l as '0'        |       |  |

| -n = Value at P | OR                                                                                                                                                                                                                                                                                                                                                     | '1' = Bit is set                                  |                                                 | '0' = Bit is cle                         | ared                                       | x = Bit is unkn | own   |  |

| bit 7           | 1 = Capacitiv                                                                                                                                                                                                                                                                                                                                          | acitive Sensing<br>e sensing mod<br>e sensing mod | ule is operatii                                 | ng                                       | s no operating c                           | current         |       |  |

| bit 6-4         | Unimplement                                                                                                                                                                                                                                                                                                                                            | ted: Read as 'd                                   | )'                                              |                                          |                                            |                 |       |  |

| bit 3-2         | <b>CPSRNG&lt;1:0&gt;:</b> Capacitive Sensing Oscillator Range bits<br>00 = Oscillator is Off.<br>01 = Oscillator is in low range. Charge/discharge current is nominally 0.1 μA.<br>10 = Oscillator is in medium range. Charge/discharge current is nominally 1.2 μA.<br>11 = Oscillator is in high range. Charge/discharge current is nominally 18 μA. |                                                   |                                                 |                                          |                                            |                 |       |  |

| bit 1           | <b>CPSOUT:</b> Capacitive Sensing Oscillator Status bit<br>1 = Oscillator is sourcing current (Current flowing out the pin)<br>0 = Oscillator is sinking current (Current flowing into the pin)                                                                                                                                                        |                                                   |                                                 |                                          |                                            |                 |       |  |

| bit 0           | $\frac{\text{If TOCS} = 1}{\text{The TOXCS b}}$ $1 = \text{Timer0 C}$ $0 = \text{Timer0 C}$ $\frac{\text{If TOCS} = 0}{1 + 1 + 1 + 1 + 1 + 2}$                                                                                                                                                                                                         | Clock Source is<br>Clock Source is                | h clock extern<br>the capacitiv<br>the T0CKI pi | nal to the core/<br>e sensing osci<br>in | Timer0 module<br>llator<br>dule and is Fos |                 | ):    |  |

### REGISTER 14-1: CPSCON0: CAPACITIVE SENSING CONTROL REGISTER 0

#### 16.3.1.4 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the AUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit of the PIR1 register is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

#### 16.3.1.5 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/ CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

#### 16.3.1.6 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register.

#### 16.3.1.7 Receiving 9-bit Characters

The AUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set, the AUSART will shift 9-bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

Address detection in Synchronous modes is not supported, therefore, the ADDEN bit of the RCSTA register must be cleared.

# 16.3.1.8 Synchronous Master Reception Setup:

- 1. Initialize the SPBRG register for the appropriate baud rate. Set or clear the BRGH bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set bit RX9.

- 6. Verify address detection is disabled by clearing the ADDEN bit of the RCSTA register.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- Interrupt flag bit RCIF of the PIR1 register will be set when reception of a character is complete. An interrupt will be generated if the RCIE interrupt enable bit of the PIE1 register was set.

- 9. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit, which resets the AUSART.

#### 17.1.2.4 Slave Select Operation

The  $\overline{SS}$  pin allows Synchronous Slave mode operation. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPM<3:0> = 0100). The associated TRIS bit for the  $\overline{SS}$  pin must be set, making  $\overline{SS}$  an input.

In Slave Select mode, when:

- SS = 0, The device operates as specified in Section 17.1.2 "Slave Mode".

- $\overline{SS} = 1$ , The SPI module is held in Reset and the SDO pin will be tri-stated.

- Note 1: When the SPI is in Slave mode with  $\overline{SS}$  pin control enabled (SSPM<3:0> = 0100), the SPI module will reset if the  $\overline{SS}$  pin is driven high.

- 2: If the SPI is used in Slave mode with CKE set, the SS pin control must be enabled.

When the SPI module resets, the bit counter is cleared to '0'. This can be done by either forcing the SS pin to a high level or clearing the SSPEN bit. Figure 17-6 shows the timing waveform for such a synchronization event.

| Note: | SSPSR must be reinitialized by writing to |

|-------|-------------------------------------------|

|       | the SSPBUF register before the data can   |

|       | be clocked out of the slave again.        |

#### 17.1.2.5 Sleep in Slave Mode

While in Sleep mode, the slave can transmit/receive data. The SPI Transmit/Receive Shift register operates asynchronously to the device on the externally supplied clock source. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the SSP Interrupt Flag bit will be set and if enabled, will wake the device from Sleep.

| <u>83</u>                | •<br>•<br>•<br>•      | /////////////////////////////////////// |                                       |             |                                            |                                                                     |                          |  |  |

|--------------------------|-----------------------|-----------------------------------------|---------------------------------------|-------------|--------------------------------------------|---------------------------------------------------------------------|--------------------------|--|--|

| SCK<br>(CKP = 0          | ·<br>·<br>·<br>·<br>· |                                         |                                       |             |                                            |                                                                     |                          |  |  |

| SCK<br>(CKP = 1          | ;<br>,<br>,<br>;<br>; |                                         |                                       |             |                                            |                                                                     |                          |  |  |

| 99888-00<br>SSP8028      |                       |                                         |                                       |             | SSPSR must<br>the SSPBUF<br>be blocked out | be reinitistized by<br>register before the<br>t of the sligve again | writing to<br>s data can |  |  |

| 8043                     |                       | <u>8. 88 7 X</u>                        |                                       |             |                                            | ×                                                                   |                          |  |  |

| SDI                      |                       | -//////                                 |                                       |             |                                            | $\sim$                                                              |                          |  |  |

| nput<br>Sample           |                       | <b>1</b>                                | <b>^</b>                              |             |                                            | <u> </u>                                                            |                          |  |  |

| SBRHF<br>nterrupt<br>Røg | :                     |                                         | · · · · · · · · · · · · · · · · · · · | -<br>-<br>- |                                            |                                                                     | ·                        |  |  |

| SSPSR 0<br>SSPRE         |                       |                                         |                                       |             |                                            |                                                                     | <i>110</i>               |  |  |

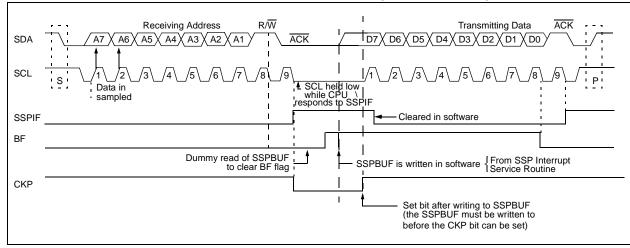

#### 17.2.6 TRANSMISSION

When the R/W bit of the received address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set and the slave will respond to the master by reading out data. After the address match, an ACK pulse is generated by the slave hardware and the SCL pin is held low (clock is automatically stretched) until the slave is ready to respond. See **Section 17.2.7 "Clock Stretching"**. The data the slave will transmit must be loaded into the SSPBUF register, which sets the BF bit. The SCL line is released by setting the CKP bit of the SSPCON register.

An SSP interrupt is generated for each transferred data byte. The SSPIF flag bit of the PIR1 register initiates an SSP interrupt, and must be cleared by software before the next byte is transmitted. The BF bit of the SSPSTAT register is cleared on the falling edge of the eighth received clock pulse. The SSPIF flag bit is set on the falling edge of the ninth clock pulse. Following the eighth falling clock edge, control of the SDA line is released back to the master so that the master can acknowledge or not acknowledge the response. If the master sends a not acknowledge, the slave's transmission is complete and the slave must monitor for the next Start condition. If the master acknowledges, control of the bus is returned to the slave to transmit another byte of data. Just as with the previous byte, the clock is stretched by the slave, data must be loaded into the SSPBUF and CKP must be set to release the clock line (SCL).

#### FIGURE 17-12: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

#### REGISTER 18-1: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

| R-1      | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/S-0 |

|----------|-----|-----|-----|-----|-----|-----|-------|

| Reserved | —   | —I  | —   | —   | —   | —   | RD    |

| bit 7    |     |     |     |     |     |     | bit 0 |

|          |     |     |     |     |     |     |       |

| Legend:           |                  | S = Setable bit, cleared in hardware |                    |  |  |

|-------------------|------------------|--------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'   |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                 | x = Bit is unknown |  |  |

bit 6-1 Unimplemented: Read as '0'

bit 0 RD: Read Control bit

1 = Initiates an program memory read (The RD is cleared in hardware; the RD bit can only be set (not cleared) in software).

0 = Does not initiate a program memory read

#### REGISTER 18-2: PMDATH: PROGRAM MEMORY DATA HIGH REGISTER

| U-0      | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|----------|-----|-------|-------|-------|-------|-------|-------|

| —        | —   | PMD13 | PMD12 | PMD11 | PMD10 | PMD9  | PMD8  |

| bit 7    |     |       |       |       |       |       | bit 0 |

|          |     |       |       |       |       |       |       |

| l egend. |     |       |       |       |       |       |       |

| Legena.                           |                  |                        |                    |

|-----------------------------------|------------------|------------------------|--------------------|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **PMD<13:8>:** The value of the program memory word pointed to by PMADRH and PMADRL after a program memory read command.

#### REGISTER 18-3: PMDATL: PROGRAM MEMORY DATA LOW REGISTER

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PMD7  | PMD6  | PMD5  | PMD4  | PMD3  | PMD2  | PMD1  | PMD0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                                    |  |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |

bit 7-0 **PMD<7:0>:** The value of the program memory word pointed to by PMADRH and PMADRL after a program memory read command.

# 23.0 ELECTRICAL SPECIFICATIONS

# Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40°C to +125°C                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Storage temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 65°C to +150°C                        |

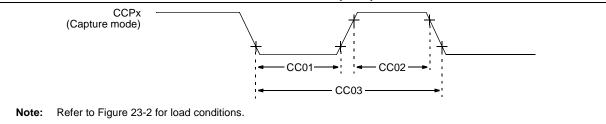

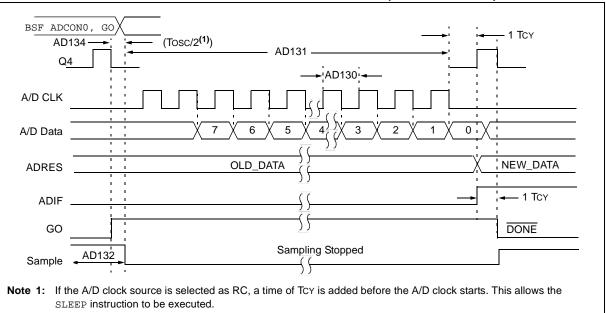

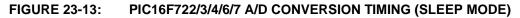

| Voltage on VDD with respect to Vss, PIC16F72X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0.3V to +6.5V                         |