Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

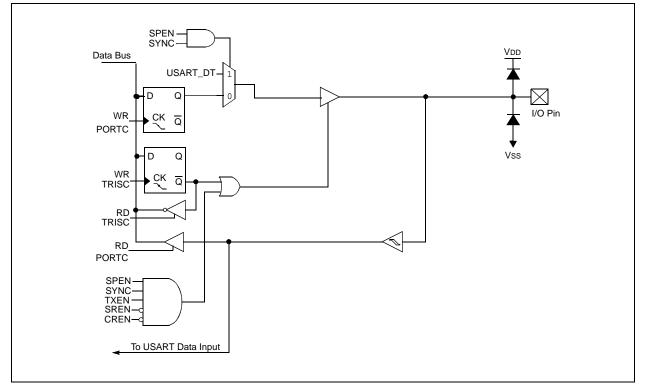

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 11x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf726-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F722/3/4/6/7

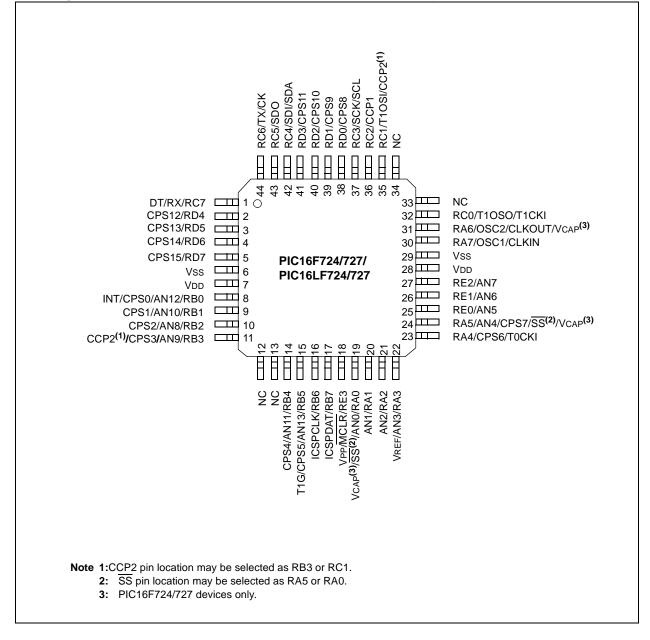

## Pin Diagrams – 44-PIN TQFP (PIC16F724/727/PIC16LF724/727)

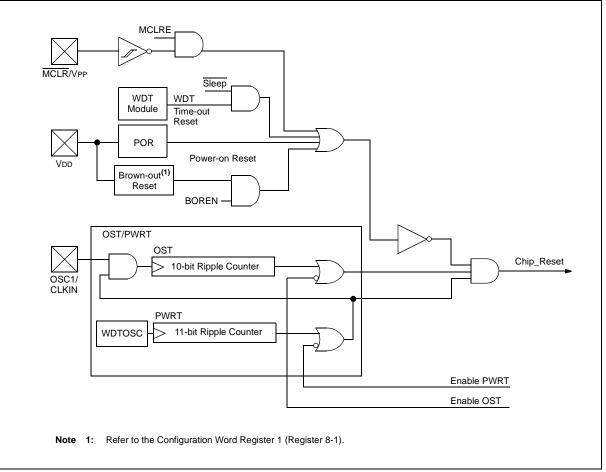

# 3.0 RESETS

The PIC16(L)F722/3/4/6/7 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- Power-on Reset (POR)

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

- Brown-out Reset (BOR)

Most registers are not affected by a WDT wake-up since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations, as indicated in Table 3-3. These bits are used in software to determine the nature of the Reset.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 3-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See **Section 23.0** "**Electrical Specifications**" for pulse-width specifications.

## FIGURE 3-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

# PIC16(L)F722/3/4/6/7

| REGISTER 6-13: | TRISD: PORTD TRI-STATE REGISTER <sup>(1)</sup> |

|----------------|------------------------------------------------|

|                |                                                |

| TRISD7         TRISD6         TRISD5         TRISD4         TRISD3         TRISD2         TRISD1         TRISD0           bit 7         bit 0 | R/W-1  | R/W-1                    | R/W-1 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------|-------|--------|--------|--------|--------|--------|

| bit 7 bit 0                                                                                                                                   | TRISD7 | TRISD7 TRISD6 TRISD5 TRI |       | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 |

|                                                                                                                                               | bit 7  |                          |       |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0

**TRISD<7:0>:** PORTD Tri-State Control bits 1 = PORTD pin configured as an input (tri-stated) 0 = PORTD pin configured as an output

Note 1: TRISD is not implemented on PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'.

#### REGISTER 6-14: ANSELD: PORTD ANALOG SELECT REGISTER<sup>(2)</sup>

| R/W-1             | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------------------|-------|-------|-------|-------|-------|-------|-------|

| ANSD7 ANSD6 ANSD5 |       | ANSD4 | ANSD3 | ANSD2 | ANSD1 | ANSD0 |       |

| bit 7             |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 **ANSD<7:0>**: Analog Select between Analog or Digital Function on Pins RD<7:0>, respectively 0 = Digital I/O. Pin is assigned to port or Digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital Input buffer disabled.

- **Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

- 2: ANSELD register is not implemented on the PIC16F722/723/726/PIC16LF722/723/726. Read as '0'.

Note: PORTD is available on PIC16F724/LF724 and PIC16F727/LF727 only.

#### 6.5.2 RD0/CPS8

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### 6.5.3 RD1/CPS9

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### 6.5.4 RD2/CPS10

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### 6.5.5 RD3/CPS11

Figure 6-21 shows the diagram for these pins. They are configurable to function as one of the following:

- a general purpose I/O

- · a capacitive sensing input

#### REGISTER 8-1: CONFIG1: CONFIGURATION WORD REGISTER 1 (CONTINUED)

- bit 4 **PWRTE:** Power-up Timer Enable bit 1 = PWRT disabled

- 1 = PWRT disabled0 = PWRT enabled

- bit 3 WDTE: Watchdog Timer Enable bit 1 = WDT enabled

- 1 = WDT enabled0 = WDT disabled

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = RC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, RC on RA7/OSC1/CLKIN

- 110 = RCIO oscillator: I/O function on RA6/OSC2/CLKOUT pin, RC on RA7/OSC1/CLKIN

- 101 = INTOSC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN

- 100 = INTOSCIO oscillator: I/O function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN

- 011 = EC: I/O function on RA6/OSC2/CLKOUT pin, CLKIN on RA7/OSC1/CLKIN

- 010 = HS oscillator: High-speed crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN

- 001 = XT oscillator: Crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN

- 000 = LP oscillator: Low-power crystal on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN

Note 1: Enabling Brown-out Reset does not automatically enable Power-up Timer.

- 2: The entire program memory will be erased when the code protection is turned off.

- 3: When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.

- 4: MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

#### REGISTER 8-2: CONFIG2: CONFIGURATION WORD REGISTER 2

|        |   |   | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> |

|--------|---|---|--------------------|--------------------|--------------------|--------------------|

|        | — | _ | _                  | —                  | —                  | —                  |

| bit 15 |   |   |                    |                    |                    | bit 8              |

| U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | R/P-1   | R/P-1   | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> | U-1 <sup>(1)</sup> |

|--------------------|--------------------|---------|---------|--------------------|--------------------|--------------------|--------------------|

| —                  | —                  | VCAPEN1 | VCAPEN0 | —                  | —                  | _                  | —                  |

| bit 7              |                    |         |         |                    |                    |                    | bit 0              |

| Legend:           | P = Programmable bit |                             |                    |

|-------------------|----------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared        | x = Bit is unknown |

bit 13-6 Unimplemented: Read as '1'

bit 5-4 VCAPEN<1:0>: Voltage Regulator Capacitor Enable bits For the PIC16LF72X: These bits are ignored. All VCAP pin functions are disabled. For the PIC16F72X: 00 = VCAP functionality is enabled on RA0 01 = VCAP functionality is enabled on RA5 10 = VCAP functionality is enabled on RA6 11 = All VCAP functions are disabled (not recommended) bit 3-0 Unimplemented: Read as '1'

**Note 1:** MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

# 9.3 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 9-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 9-3. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the source

impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 9-1 may be used. This equation assumes that 1/2 LSb error is used (256 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

# EQUATION 9-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V VDD$

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

$V_{APPLIED}\left(1 - \frac{1}{1-1}\right) = V_{CHOLD}$

$:[11VCHOLD charged to within 1/2 lsb$

$$(2^{n+1}) - 1'$$

$$V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{CHOLD}$$

;[2] V\_{CHOLD charge response to V\_{APPLIED}}

$$V_{APPLIED}\left(1-e^{\frac{-ic}{RC}}\right) = V_{APPLIED}\left(1-\frac{1}{(2^{n+1})-l}\right) \quad (combining [1] and [2])$$

*Note:* Where n = number of bits of the ADC.

Solving for TC:

$$T_{C} = -C_{HOLD}(R_{IC} + R_{SS} + R_{S}) \ln(1/511)$$

=  $-10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.001957)$

=  $1.12\mu s$

$$c_{O} = 2M_{S} + 1.12M_{S} + [(50^{\circ}C - 25^{\circ}C)(0.05M_{S}/^{\circ}C)]$$

Therefore:

$$TACQ = 2MS + 1.12MS + [(50°C-25°C)(0.05MS/°C)]$$

= 4.42MS

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

|         |                          |        |        |        |        |           | -         | -      | -                    | -                               |

|---------|--------------------------|--------|--------|--------|--------|-----------|-----------|--------|----------------------|---------------------------------|

| Name    | Bit 7                    | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2     | Bit 1     | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| ADCON0  | _                        |        | CHS3   | CHS2   | CHS1   | CHS0      | GO/DONE   | ADON   | 00 0000              | 00 0000                         |

| ADCON1  | _                        | ADCS2  | ADCS1  | ADCS0  | _      | _         | ADREF1    | ADREF0 | -00000               | -00000                          |

| ANSELA  | _                        | _      | ANSA5  | ANSA4  | ANSA3  | ANSA2     | ANSA1     | ANSA0  | 11 1111              | 11 1111                         |

| ANSELB  | _                        | _      | ANSB5  | ANSB4  | ANSB3  | ANSB2     | ANSB1     | ANSB0  | 11 1111              | 11 1111                         |

| ANSELE  | _                        | _      | _      | _      | _      | ANSE2     | ANSE1     | ANSE0  | 111                  | 111                             |

| ADRES   | A/D Result Register Byte |        |        |        |        | xxxx xxxx | uuuu uuuu |        |                      |                                 |

| CCP2CON | _                        | _      | DC2B1  | DC2B0  | CCP2M3 | CCP2M2    | CCP2M1    | CCP2M0 | 00 0000              | 00 0000                         |

| FVRCON  | FVRRDY                   | FVREN  | _      | _      | _      | _         | ADFVR1    | ADFVR0 | q000                 | q000                            |

| INTCON  | GIE                      | PEIE   | T0IE   | INTE   | RBIE   | T0IF      | INTF      | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1    | TMR1GIE                  | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE    | TMR2IE    | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1    | TMR1GIF                  | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF    | TMR2IF    | TMR1IF | 0000 0000            | 0000 0000                       |

| TRISA   | TRISA7                   | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2    | TRISA1    | TRISA0 | 1111 1111            | 1111 1111                       |

| TRISB   | TRISB7                   | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2    | TRISB1    | TRISB0 | 1111 1111            | 1111 1111                       |

| TRISE   | _                        | _      | _      | _      | TRISE3 | TRISE2    | TRISE1    | TRISE0 | 1111                 | 1111                            |

|         |                          |        |        |        |        |           |           |        |                      |                                 |

TABLE 9-2: SUMMARY OF ASSOCIATED ADC REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for ADC module.

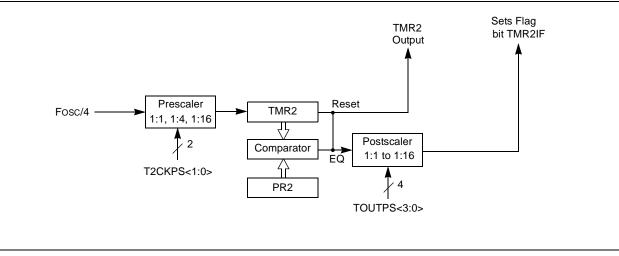

# 13.0 TIMER2 MODULE

The Timer2 module is an 8-bit timer with the following features:

- 8-bit timer register (TMR2)

- 8-bit period register (PR2)

- Interrupt on TMR2 match with PR2

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

See Figure 13-1 for a block diagram of Timer2.

# 13.1 Timer2 Operation

The clock input to the Timer2 module is the system instruction clock (Fosc/4). The clock is fed into the Timer2 prescaler, which has prescale options of 1:1, 1:4 or 1:16. The output of the prescaler is then used to increment the TMR2 register.

The values of TMR2 and PR2 are constantly compared to determine when they match. TMR2 will increment from 00h until it matches the value in PR2. When a match occurs, two things happen:

- TMR2 is reset to 00h on the next increment cycle.

- The Timer2 postscaler is incremented.

The match output of the Timer2/PR2 comparator is then fed into the Timer2 postscaler. The postscaler has postscale options of 1:1 to 1:16 inclusive. The output of the Timer2 postscaler is used to set the TMR2IF interrupt flag bit in the PIR1 register.

## FIGURE 13-1: TIMER2 BLOCK DIAGRAM

The TMR2 and PR2 registers are both fully readable and writable. On any Reset, the TMR2 register is set to 00h and the PR2 register is set to FFh.

Timer2 is turned on by setting the TMR2ON bit in the T2CON register to a '1'. Timer2 is turned off by clearing the TMR2ON bit to a '0'.

The Timer2 prescaler is controlled by the T2CKPS bits in the T2CON register. The Timer2 postscaler is controlled by the TOUTPS bits in the T2CON register. The prescaler and postscaler counters are cleared when:

- A write to TMR2 occurs.

- A write to T2CON occurs.

- Any device Reset occurs (Power-on Reset, MCLR Reset, Watchdog Timer Reset, or Brown-out Reset).

Note: TMR2 is not cleared when T2CON is written.

# 14.1 Analog MUX

The capacitive sensing module can monitor up to 16 inputs. The capacitive sensing inputs are defined as CPS<15:0>. To determine if a frequency change has occurred the user must:

- Select the appropriate CPS pin by setting the CPSCH<3:0> bits of the CPSCON1 register

- Set the corresponding ANSEL bit

- Set the corresponding TRIS bit

- Run the software algorithm

Selection of the CPSx pin while the module is enabled will cause the capacitive sensing oscillator to be on the CPSx pin. Failure to set the corresponding ANSEL and TRIS bits can cause the capacitive sensing oscillator to stop, leading to false frequency readings.

# 14.2 Capacitive Sensing Oscillator

The capacitive sensing oscillator consists of a constant current source and a constant current sink, to produce a triangle waveform. The CPSOUT bit of the CPSCON0 register shows the status of the capacitive sensing oscillator, whether it is a sinking or sourcing current. The oscillator is designed to drive a capacitive load (single PCB pad) and at the same time, be a clock source to either Timer0 or Timer1. The oscillator has three different current settings as defined by CPSRNG<1:0> of the CPSCON0 register. The different current settings for the oscillator serve two purposes:

- Maximize the number of counts in a timer for a fixed time base

- Maximize the count differential in the timer during a change in frequency

# 14.3 Timer resources

To measure the change in frequency of the capacitive sensing oscillator, a fixed time base is required. For the period of the fixed time base, the capacitive sensing oscillator is used to clock either Timer0 or Timer1. The frequency of the capacitive sensing oscillator is equal to the number of counts in the timer divided by the period of the fixed time base.

# 14.4 Fixed Time Base

To measure the frequency of the capacitive sensing oscillator, a fixed time base is required. Any timer resource or software loop can be used to establish the fixed time base. It is up to the end user to determine the method in which the fixed time base is generated.

Note: The fixed time base can not be generated by timer resource the capacitive sensing oscillator is clocking.

# 14.4.1 TIMER0

To select Timer0 as the timer resource for the capacitive sensing module:

- · Set the T0XCS bit of the CPSCON0 register

- · Clear the T0CS bit of the OPTION register

When Timer0 is chosen as the timer resource, the capacitive sensing oscillator will be the clock source for Timer0. Refer to **Section 11.0** "**Timer0 Module**" for additional information.

## 14.4.2 TIMER1

To select Timer1 as the timer resource for the capacitive sensing module, set the TMR1CS<1:0> of the T1CON register to '11'. When Timer1 is chosen as the timer resource, the capacitive sensing oscillator will be the clock source for Timer1. Because the Timer1 module has a gate control, developing a time base for the frequency measurement can be simplified using either:

- The Timer0 overflow flag

- The Timer2 overflow flag

- The WDT overflow flag

It is recommend that one of these flags, in conjunction with the toggle mode of the Timer1 Gate, is used to develop the fixed time base required by the software portion of the capacitive sensing module. Refer to **Section 12.0 "Timer1 Module with Gate Control**" for additional information.

#### TABLE 14-1: TIMER1 ENABLE FUNCTION

| TMR10N | TMR1GE | Timer1 Operation       |

|--------|--------|------------------------|

| 0      | 0      | Off                    |

| 0      | 1      | Off                    |

| 1      | 0      | On                     |

| 1      | 1      | Count Enabled by input |

| Name    | Bit 7        | Bit 6          | Bit 5          | Bit 4          | Bit 3                   | Bit 2    | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------------|----------------|----------------|----------------|-------------------------|----------|---------|---------|----------------------|---------------------------------|

| ADCON0  | _            |                | CHS3           | CHS2           | CHS1                    | CHS0     | GO/DONE | ADON    | 00 0000              | 00 0000                         |

| ANSELB  | _            | _              | ANSB5          | ANSB4          | ANSB3                   | ANSB2    | ANSB1   | ANSB0   | 11 1111              | 11 1111                         |

| APFCON  | _            | _              | _              | _              | _                       | _        | SSSEL   | CCP2SEL | 00                   | 00                              |

| CCP1CON | _            | _              | DC1B1          | DC1B0          | CCP1M3                  | CCP1M2   | CCP1M1  | CCP1M0  | 00 0000              | 00 0000                         |

| CCP2CON | _            | _              | DC2B1          | DC2B0          | CCP2M3                  | CCP2M2   | CCP2M1  | CCP2M0  | 00 0000              | 00 0000                         |

| CCPRxL  | Capture/Com  | npare/PWM R    | egister X Lov  | v Byte         |                         |          |         |         | xxxx xxxx            | uuuu uuuu                       |

| CCPRxH  | Capture/Com  | npare/PWM R    | egister X Hig  | h Byte         |                         |          |         |         | xxxx xxxx            | uuuu uuuu                       |

| INTCON  | GIE          | PEIE           | TOIE           | INTE           | RBIE                    | T0IF     | INTF    | RBIF    | 0000 000x            | 0000 000x                       |

| PIE1    | TMR1GIE      | ADIE           | RCIE           | TXIE           | SSPIE                   | CCP1IE   | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIE2    | —            | -              | —              | -              | —                       | —        | —       | CCP2IE  | 0                    | 0                               |

| PIR1    | TMR1GIF      | ADIF           | RCIF           | TXIF           | SSPIF                   | CCP1IF   | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| PIR2    | —            | -              | —              | -              | —                       | —        | —       | CCP2IF  | 0                    | 0                               |

| T1CON   | TMR1CS1      | TMR1CS0        | T1CKPS1        | T1CKPS0        | T1OSCEN                 | T1SYNC   | _       | TMR10N  | 0000 00-0            | uuuu uu-u                       |

| T1GCON  | TMR1GE       | T1GPOL         | T1GTM          | T1GSPM         | T <u>1GGO</u> /<br>DONE | T1GVAL   | T1GSS1  | T1GSS0  | 0000 0x00            | 00x0 0x00                       |

| TMR1L   | Holding Regi |                | xxxx xxxx      | uuuu uuuu      |                         |          |         |         |                      |                                 |

| TMR1H   | Holding Regi | ster for the M | ost Significar | nt Byte of the | 16-bit TMR1 F           | Register |         |         | xxxx xxxx            | uuuu uuuu                       |

| TRISB   | TRISB7       | TRISB6         | TRISB5         | TRISB4         | TRISB3                  | TRISB2   | TRISB1  | TRISB0  | 1111 1111            | 1111 1111                       |

| TRISC   | TRISC7       | TRISC6         | TRISC5         | TRISC4         | TRISC3                  | TRISC2   | TRISC1  | TRISC0  | 1111 1111            | 1111 1111                       |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Compare.

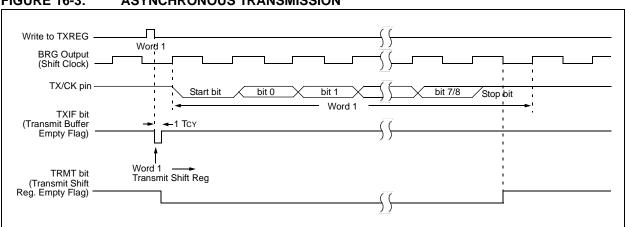

#### 16.1.1.4 TSR Status

The TRMT bit of the TXSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

Note: The TSR register is not mapped in data memory, so it is not available to the user.

#### 16.1.1.5 Transmitting 9-Bit Characters

The AUSART supports 9-bit character transmissions. When the TX9 bit of the TXSTA register is set the AUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXSTA register is the ninth, and Most Significant, data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXREG is written.

A special 9-bit Address mode is available for use with multiple receivers. Refer to **Section 16.1.2.7** "Address **Detection**" for more information on the Address mode.

#### 16.1.1.6 Asynchronous Transmission Set-up:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (Refer to Section 16.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 4. Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 7. Load 8-bit data into the TXREG register. This will start the transmission.

## FIGURE 16-3: ASYNCHRONOUS TRANSMISSION

#### 16.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (refer to Section 16.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit of the PIR1 register will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE bit of the PIE1 register was also set.

- 7. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 8. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 9. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 16.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (refer to Section 16.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. Enable 9-bit reception by setting the RX9 bit.

- 5. Enable address detection by setting the ADDEN bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit of the PIR1 register will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit of the PIE1 register was also set.

- 8. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

| RX/DT pin                          | Start<br>bit / bit 0 / bit 1 / ( / ybit 7/8/ Stop / bit / bit 0 / ( / ybit 7/8/ Stop / bit / ybit 7/8/ Stop                                               |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rcv Shift<br>Reg<br>Rcv Buffer Reg | → → → → → → → → → → → → → → → → → → →                                                                                                                     |

| Read Rcv<br>Buffer Reg –<br>RCREG  |                                                                                                                                                           |

| RCIF<br>(Interrupt Flag)           |                                                                                                                                                           |

| OERR bit -                         |                                                                                                                                                           |

|                                    | timing diagram shows three words appearing on the RX input. The RCREG (receive buffer) is read after the third word, ng the OERR (overrun) bit to be set. |

# FIGURE 16-5: ASYNCHRONOUS RECEPTION

# PIC16(L)F722/3/4/6/7

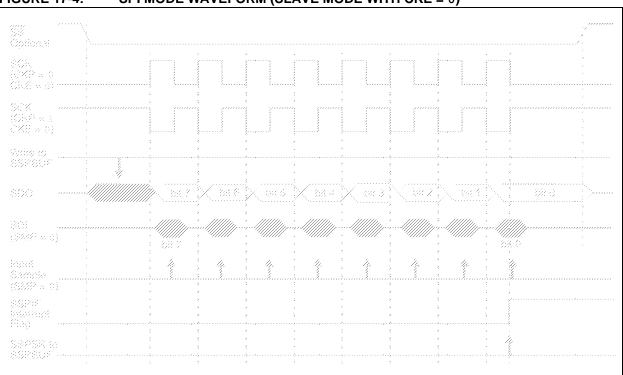

#### FIGURE 17-4: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 0)

#### SS SCK (CKP = 0 $\dot{C}KE = 1)$ SCK (CKP = 1 CKE = 1) Write to SSPBUF bit 6 bit 5 bit 4 bit 2 bit 1 bit 0 SDO bit '7 bit 3 ï SDI (SMP = 0)I bit 0 bit 7 Input Sample (SMP = 0)SSPIF Interrupt Flag SSPSR to SSPBUF 1 . i . . . .

## FIGURE 17-5: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

# 17.2.7 CLOCK STRETCHING

During any SCL low phase, any device on the  $I^2C$  bus may hold the SCL line low and delay, or pause, the transmission of data. This "stretching" of a transmission allows devices to slow down communication on the bus. The SCL line must be constantly sampled by the master to ensure that all devices on the bus have released SCL for more data.

Stretching usually occurs after an ACK bit of a transmission, delaying the first bit of the next byte. The SSP module hardware automatically stretches for two conditions:

- After a 10-bit address byte is received (update SSPADD register)

- Anytime the CKP bit of the SSPCON register is cleared by hardware

The module will hold SCL low until the CKP bit is set. This allows the user slave software to update SSPBUF with data that may not be readily available. In 10-bit addressing modes, the SSPADD register must be updated after receiving the first and second address bytes. The SSP module will hold the SCL line low until the SSPADD has a byte written to it. The UA bit of the SSPSTAT register will be set, along with SSPIF, indicating an address update is needed.

#### 17.2.8 FIRMWARE MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits of the SSPSTAT register are cleared from a Reset or when the SSP module is disabled (SSPEN cleared). The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set or the bus is Idle and both the S and P bits are clear.

In Firmware Master mode, the SCL and SDA lines are manipulated by setting/clearing the corresponding TRIS bit(s). The output level is always low, irrespective of the value(s) in the corresponding PORT register bit(s). When transmitting a '1', the TRIS bit must be set (input) and a '0', the TRIS bit must be clear (output).

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt will occur if enabled):

- Start condition

- Stop condition

- Data transfer byte transmitted/received

Firmware Master Mode of operation can be done with either the Slave mode Idle (SSPM<3:0 > = 1011), or with either of the Slave modes in which interrupts are enabled. When both master and slave functionality is enabled, the software needs to differentiate the source(s) of the interrupt. Refer to Application Note AN554, Software Implementation of  $l^2 C^{TM}$  Bus Master (DS00554) for more information.

#### 17.2.9 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allow the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSPSTAT register is set or when the bus is Idle, and both the S and P bits are clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the Stop condition occurs.

In Multi-Master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRIS bits). There are two stages where this arbitration of the bus can be lost. They are the Address Transfer and Data Transfer stages.

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an  $\overrightarrow{ACK}$  pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

Refer to Application Note AN578, Use of the SSP Module in the  $l^2 C^{TM}$  Multi-Master Environment (DS00578) for more information.

# 19.0 POWER-DOWN MODE (SLEEP)

The Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If the Watchdog Timer is enabled:

- WDT will be cleared but keeps running.

- PD bit of the STATUS register is cleared.

- TO bit of the STATUS register is set.

- Oscillator driver is turned off.

- Timer1 oscillator is unaffected

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSs, with no external circuitry drawing current from the I/O pin. I/O pins that are high-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level when external  $\overline{\text{MCLR}}$  is enabled.

**Note:** A Reset generated by a WDT time out does not drive MCLR pin low.

## 19.1 Wake-up from Sleep

The device can wake up from Sleep through one of the following events:

- 1. External Reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer wake-up (if WDT was enabled).

- 3. Interrupt from RB0/INT pin, PORTB change or a peripheral interrupt.

The first event will cause a device Reset. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. TO bit is cleared if WDT wake-up occurred.

The following peripheral interrupts can wake the device from Sleep:

- 1. TMR1 Interrupt. Timer1 must be operating as an asynchronous counter.

- USART Receive Interrupt (Synchronous Slave mode only)

- 3. A/D conversion (when A/D clock source is RC)

- 4. Interrupt-on-change

- 5. External Interrupt from INT pin

- 6. Capture event on CCP1 or CCP2

- 7. SSP Interrupt in SPI or I<sup>2</sup>C Slave mode

Other peripherals cannot generate interrupts since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction, then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

**Note:** If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from Sleep. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

# 21.0 INSTRUCTION SET SUMMARY

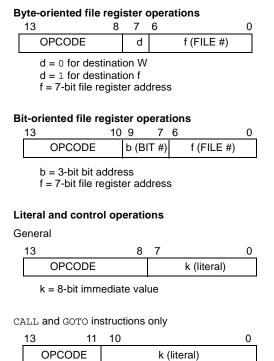

The PIC16(L)F722/3/4/6/7 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 21-1, while the various opcode fields are summarized in Table 21-1.

Table 21-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8-bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

# 21.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF PORTB instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended consequence of clearing the condition that set the RBIF flag.

#### TABLE 21-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |  |  |  |  |  |

| W     | Working register (accumulator)                                                                                                                                                    |  |  |  |  |  |

| b     | Bit address within an 8-bit file register                                                                                                                                         |  |  |  |  |  |

| k     | Literal field, constant data or label                                                                                                                                             |  |  |  |  |  |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ . It is<br>the recommended form of use for<br>compatibility with all Microchip software tools. |  |  |  |  |  |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                  |  |  |  |  |  |

| PC    | Program Counter                                                                                                                                                                   |  |  |  |  |  |

| TO    | Time-out bit                                                                                                                                                                      |  |  |  |  |  |

| С     | Carry bit                                                                                                                                                                         |  |  |  |  |  |

| DC    | Digit carry bit                                                                                                                                                                   |  |  |  |  |  |

| Z     | Zero bit                                                                                                                                                                          |  |  |  |  |  |

| PD    | Power-down bit                                                                                                                                                                    |  |  |  |  |  |

# FIGURE 21-1: GENERAL FORMAT FOR INSTRUCTIONS

# 23.2 DC Characteristics: PIC16(L)F722/3/4/6/7-I/E (Industrial, Extended) (Continued)

| PIC16LF722/3/4/6/7<br>PIC16F722/3/4/6/7 |                                     |    |      |      |    |     |                             |  |  |

|-----------------------------------------|-------------------------------------|----|------|------|----|-----|-----------------------------|--|--|

|                                         |                                     |    |      |      |    |     |                             |  |  |

| Vdd                                     | Note                                |    |      |      |    |     |                             |  |  |

|                                         | Supply Current (IDD) <sup>(1,</sup> | 2) |      |      |    |     |                             |  |  |

| D014                                    |                                     | _  | 290  | 330  | μA | 1.8 | Fosc = 4 MHz                |  |  |

|                                         |                                     | _  | 460  | 500  | μA | 3.0 | EC Oscillator mode          |  |  |

| D014                                    |                                     |    | 300  | 430  | μA | 1.8 | Fosc = 4 MHz                |  |  |

|                                         |                                     |    | 450  | 655  | μA | 3.0 | EC Oscillator mode (Note 5) |  |  |

|                                         |                                     | —  | 500  | 730  | μΑ | 5.0 |                             |  |  |

| D015                                    |                                     | _  | 100  | 130  | μA | 1.8 | Fosc = 500 kHz              |  |  |

|                                         |                                     | _  | 120  | 150  | μA | 3.0 | MFINTOSC mode               |  |  |

| D015                                    |                                     | _  | 115  | 195  | μA | 1.8 | Fosc = 500 kHz              |  |  |

|                                         |                                     | _  | 135  | 200  | μΑ | 3.0 | MFINTOSC mode (Note 5)      |  |  |

|                                         |                                     | —  | 150  | 220  | μA | 5.0 |                             |  |  |

| D016                                    |                                     | _  | 650  | 800  | μΑ | 1.8 | Fosc = 8 MHz                |  |  |

|                                         |                                     |    | 1000 | 1200 | μA | 3.0 | HFINTOSC mode               |  |  |

| D016                                    |                                     | _  | 625  | 850  | μA | 1.8 | Fosc = 8 MHz                |  |  |

|                                         |                                     | _  | 1000 | 1200 | μA | 3.0 | HFINTOSC mode (Note 5)      |  |  |

|                                         |                                     | —  | 1100 | 1500 | μA | 5.0 |                             |  |  |

| D017                                    |                                     |    | 1.0  | 1.2  | mA | 1.8 | Fosc = 16 MHz               |  |  |

|                                         |                                     |    | 1.5  | 1.85 | mA | 3.0 | HFINTOSC mode               |  |  |

| D017                                    |                                     | _  | 1    | 1.2  | mA | 1.8 | Fosc = 16 MHz               |  |  |

|                                         |                                     | _  | 1.5  | 1.7  | mA | 3.0 | HFINTOSC mode (Note 5)      |  |  |

|                                         |                                     | —  | 1.7  | 2.1  | mA | 5.0 |                             |  |  |

| D018                                    |                                     | _  | 210  | 240  | μA | 1.8 | Fosc = 4 MHz                |  |  |

|                                         |                                     | _  | 340  | 380  | μA | 3.0 | EXTRC mode (Note 3, Note 5) |  |  |

| D018                                    |                                     | _  | 225  | 320  | μA | 1.8 | Fosc = 4 MHz                |  |  |

|                                         |                                     |    | 360  | 445  | μA | 3.0 | EXTRC mode (Note 3, Note 5) |  |  |

|                                         |                                     | —  | 410  | 650  | μA | 5.0 |                             |  |  |

| D019                                    |                                     |    | 1.6  | 1.9  | mA | 3.0 | Fosc = 20 MHz               |  |  |

|                                         |                                     |    | 2.0  | 2.8  | mA | 3.6 | HS Oscillator mode          |  |  |

| D019                                    |                                     | _  | 1.6  | 2    | mA | 3.0 | Fosc = 20 MHz               |  |  |

|                                         | _                                   |    | 1.9  | 3.2  | mA | 5.0 | HS Oscillator mode (Note 5) |  |  |

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

4: FVR and BOR are disabled.

5: 0.1 μF capacitor on VCAP (RA0).

# TABLE 23-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET PARAMETERS

| Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature -40°C $\leq$ TA $\leq$ +125°C |        |                                                             |              |            |              |          |                                                |  |

|----------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------|--------------|------------|--------------|----------|------------------------------------------------|--|

| Param<br>No.                                                                                                   | Sym.   | Characteristic                                              | Min.         | Тур†       | Max.         | Units    | Conditions                                     |  |

| 30                                                                                                             | ТмсL   | MCLR Pulse Width (low)                                      | 2<br>5       |            |              | μS<br>μS | VDD = 3.3-5V, -40°C to +85°C<br>VDD = 3.3-5V   |  |

| 31                                                                                                             | TWDTLP | Low Power Watchdog Timer Time-<br>out Period (No Prescaler) | 10           | 18         | 27           | ms       | VDD = 3.3V-5V                                  |  |

| 32                                                                                                             | Tost   | Oscillator Start-up Timer Period <sup>(1), (2)</sup>        |              | 1024       |              | Tosc     | (Note 3)                                       |  |

| 33*                                                                                                            | TPWRT  | Power-up Timer Period, $\overline{PWRTE} = 0$               | 40           | 65         | 140          | ms       |                                                |  |

| 34*                                                                                                            | Tioz   | I/O high-impedance from MCLR Low or Watchdog Timer Reset    |              | —          | 2.0          | μS       |                                                |  |

| 35                                                                                                             | VBOR   | Brown-out Reset Voltage                                     | 2.38<br>1.80 | 2.5<br>1.9 | 2.73<br>2.11 | V        | BORV=2.5V<br>BORV=1.9V                         |  |

| 36*                                                                                                            | VHYST  | Brown-out Reset Hysteresis                                  | 0            | 25         | 50           | mV       | -40°C to +85°C                                 |  |

| 37*                                                                                                            | TBORDC | Brown-out Reset DC Response<br>Time                         | 1            | 3          | 5<br>10      | μS       | $VDD \le VBOR$ , -40°C to +85°C $VDD \le VBOR$ |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- 2: By design.

- **3:** Period of the slower clock.

- 4: To ensure these voltage tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

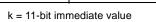

## FIGURE 23-10: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

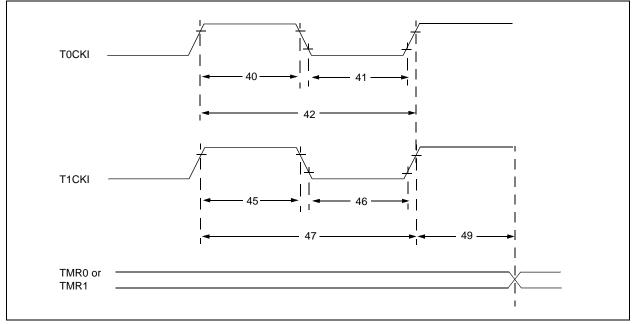

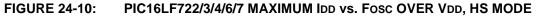

#### FIGURE 24-9: PIC16F722/3/4/6/7 MAXIMUM IDD vs. Fosc OVER VDD, HS MODE, VCAP = 0.1 µF

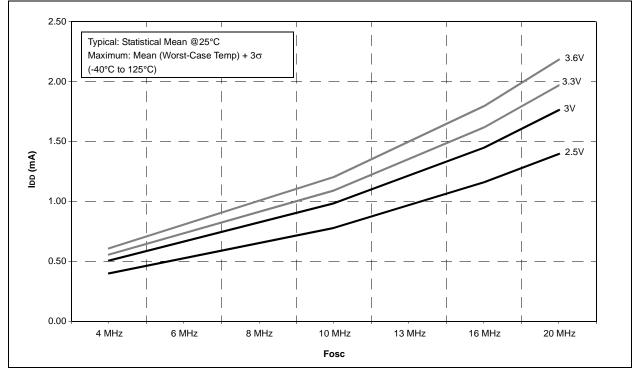

# 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Κ

0.20

\_

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

Contact-to-Exposed Pad

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103B

\_