Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 14x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf727-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address                | Name       | Bit 7                                                                                          | Bit 6         | Bit 5           | Bit 4           | Bit 3         | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR, BOR | Page   |

|------------------------|------------|------------------------------------------------------------------------------------------------|---------------|-----------------|-----------------|---------------|-----------------|---------------|-----------|-----------------------|--------|

| Bank 2                 | -          |                                                                                                |               |                 |                 |               |                 |               |           |                       |        |

| 100h <sup>(2)</sup>    | INDF       | Addressing this location uses contents of FSR to address data memory (not a physical register) |               |                 |                 |               |                 |               | XXXX XXXX | 29,37                 |        |

| 101h                   | TMR0       | Timer0 Mod                                                                                     | lule Register |                 |                 |               |                 |               |           | XXXX XXXX             | 105,37 |

| 102h <sup>(2)</sup>    | PCL        | Program Co                                                                                     | ounter's (PC) | Least Signif    | ficant Byte     |               |                 |               |           | 0000 0000             | 28,37  |

| 103h <sup>(2)</sup>    | STATUS     | IRP                                                                                            | RP1           | RP0             | TO              | PD            | Z               | DC            | С         | 0001 1xxx             | 25,37  |

| 104h <sup>(2)</sup>    | FSR        | Indirect Data                                                                                  | a Memory Ad   | ddress Point    | er              | •             |                 |               | •         | XXXX XXXX             | 29,37  |

| 105h                   | —          | Unimpleme                                                                                      | nted          |                 |                 |               |                 |               |           |                       |        |

| 106h                   | _          | Unimpleme                                                                                      | nted          |                 |                 |               |                 |               |           |                       |        |

| 107h                   | _          | Unimpleme                                                                                      | nted          |                 |                 |               |                 |               |           |                       |        |

| 108h                   | CPSCON0    | CPSON                                                                                          | _             | _               | _               | CPSRNG1       | CPSRNG0         | CPSOUT        | TOXCS     | 0 0000                | 126,38 |

| 109h                   | CPSCON1    | _                                                                                              | _             | _               | _               | CPSCH3        | CPSCH2          | CPSCH1        | CPSCH0    | 0000                  | 127,38 |

| 10Ah <sup>(1, 2)</sup> | PCLATH     | _                                                                                              | _             | _               | Write Buffer    | for the upper | 5 bits of the F | rogram Cou    | nter      | 0 0000                | 28,37  |

| 10Bh <sup>(2)</sup>    | INTCON     | GIE                                                                                            | PEIE          | T0IE            | INTE            | RBIE          | T0IF            | INTF          | RBIF      | 0000 000x             | 44,37  |

| 10Ch                   | PMDATL     | Program Me                                                                                     | emory Read    | Data Registe    | er Low Byte     | •             |                 |               | •         | XXXX XXXX             | 181,38 |

| 10Dh                   | PMADRL     | Program Me                                                                                     | emory Read    | Address Reg     | gister Low Byt  | e             |                 |               |           | XXXX XXXX             | 181,38 |

| 10Eh                   | PMDATH     | _                                                                                              | _             | Program M       | emory Read [    | Data Register | High Byte       |               |           | xx xxxx               | 181,38 |

| 10Fh                   | PMADRH     | — — Program Memory Read Address Register High Byte                                             |               |                 |                 |               |                 | x xxxx        | 181,38    |                       |        |

| Bank 3                 |            |                                                                                                |               |                 | •               |               |                 |               |           | •                     |        |

| 180h <sup>(2)</sup>    | INDF       | Addressing                                                                                     | this location | uses conten     | its of FSR to a | address data  | memory (not a   | a physical re | gister)   | xxxx xxxx             | 29,37  |

| 181h                   | OPTION_REG | RBPU                                                                                           | INTEDG        | TOCS            | TOSE            | PSA           | PS2             | PS1           | PS0       | 1111 1111             | 26,37  |

| 182h <sup>(2)</sup>    | PCL        | Program Co                                                                                     | ounter (PC) L | east Signific   | ant Byte        |               |                 |               |           | 0000 0000             | 28,37  |

| 183h <sup>(2)</sup>    | STATUS     | IRP                                                                                            | RP1           | RP0             | TO              | PD            | Z               | DC            | С         | 0001 1xxx             | 25,37  |

| 184h <sup>(2)</sup>    | FSR        | Indirect Data                                                                                  | a Memory Ad   | ddress Point    | er              |               |                 |               |           | xxxx xxxx             | 29,37  |

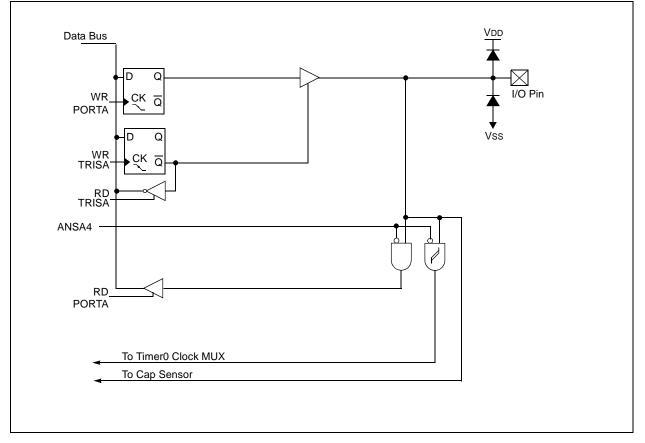

| 185h                   | ANSELA     | —                                                                                              | —             | ANSA5           | ANSA4           | ANSA3         | ANSA2           | ANSA1         | ANSA0     | 11 1111               | 52,38  |

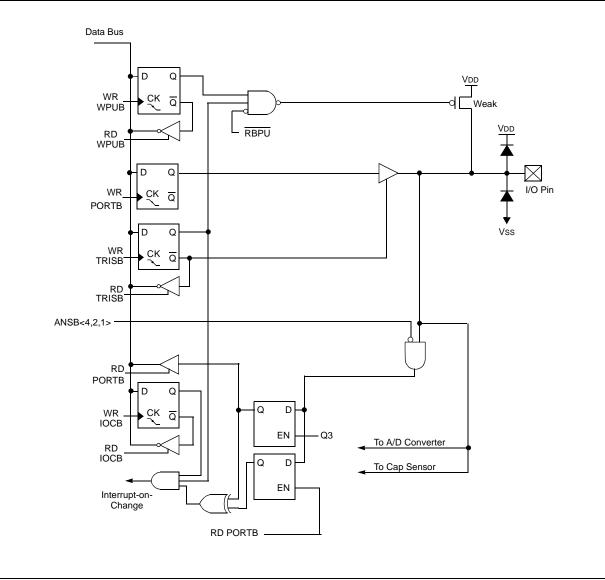

| 186h                   | ANSELB     | _                                                                                              | _             | ANSB5           | ANSB4           | ANSB3         | ANSB2           | ANSB1         | ANSB0     | 11 1111               | 61,38  |

| 187h                   | —          | Unimpleme                                                                                      | nted          |                 |                 |               |                 |               |           | —                     | _      |

| 188h                   | ANSELD     | ANSD7                                                                                          | ANSD6         | ANSD5           | ANSD4           | ANSD3         | ANSD2           | ANSD1         | ANSD0     | 1111 1111             | 78,38  |

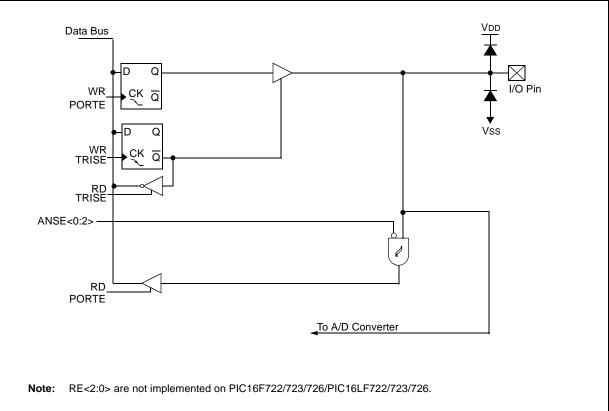

| 189h <sup>(3)</sup>    | ANSELE     | —                                                                                              | _             | _               | _               | _             | ANSE2           | ANSE1         | ANSE0     | 111                   | 82,38  |

| 18Ah <sup>(1, 2)</sup> | PCLATH     | —                                                                                              | —             | _               | Write Buffer    | for the upper | 5 bits of the F | rogram Cou    | nter      | 0 0000                | 28,37  |

| 18Bh <sup>(2)</sup>    | INTCON     | GIE                                                                                            | PEIE          | T0IE            | INTE            | RBIE          | T0IF            | INTF          | RBIF      | x000 0000             | 44,37  |

| 18Ch                   | PMCON1     | Reserved                                                                                       | _             | _               | —               | _             | _               | —             | RD        | 10                    | 182,38 |

| 18Dh                   | —          | Unimpleme                                                                                      | nted          |                 |                 |               |                 |               |           | _                     |        |

| 18Eh                   | —          | Unimplemented —                                                                                |               |                 |                 |               |                 | _             |           |                       |        |

|                        | 1          |                                                                                                | - 4 1         | Unimplemented — |                 |               |                 |               |           |                       |        |

#### **TABLE 2-1:** PIC16(L)F722/3/4/6/7 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter. Note 1:

These registers can be addressed from any bank. 2:

These registers/bits are not implemented on PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'. Accessible only when SSPM<3:0 > 1001. Accessible only when SSPM<3:0 > 1001. This bit is always '1' as RE3 is input-only. 3:

4:

5:

6:

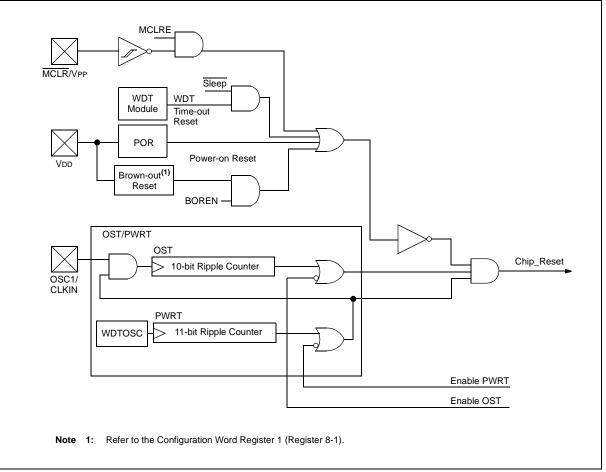

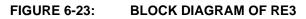

# 3.0 RESETS

The PIC16(L)F722/3/4/6/7 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- Power-on Reset (POR)

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

- Brown-out Reset (BOR)

Most registers are not affected by a WDT wake-up since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations, as indicated in Table 3-3. These bits are used in software to determine the nature of the Reset.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 3-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See **Section 23.0** "**Electrical Specifications**" for pulse-width specifications.

## FIGURE 3-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

# 5.0 LOW DROPOUT (LDO) VOLTAGE REGULATOR

The PIC16F722/3/4/6/7 devices differ from the PIC16LF722/3/4/6/7 devices due to an internal Low Dropout (LDO) voltage regulator. The PIC16F722/3/4/6/7 devices contain an internal LDO, while the PIC16LF722/3/4/6/7 ones do not.

The lithography of the die allows a maximum operating voltage of 3.6V on the internal digital logic. In order to continue to support 5.0V designs, a LDO voltage regulator is integrated on the die. The LDO voltage regulator allows for the internal digital logic to operate at 3.2V, while I/O's operate at 5.0V (VDD).

The LDO voltage regulator requires an external bypass capacitor for stability. One of three pins, denoted as VCAP, can be configured for the external bypass capacitor. It is recommended that the capacitor be a ceramic cap between 0.1 to  $1.0 \,\mu$ F. The VCAP pin is not intended to supply power to external loads. An external voltage regulator should be used if this functionality is required. In addition, external devices should not supply power to the VCAP pin.

On power-up, the external capacitor will look like a large load on the LDO voltage regulator. To prevent erroneous operation, the device is held in Reset while a constant current source charges the external capacitor. After the cap is fully charged, the device is released from Reset. For more information, refer to **Section 23.0 "Electrical Specifications"**.

See Configuration Word 2 register (Register 8-2) for VCAP enable bits.

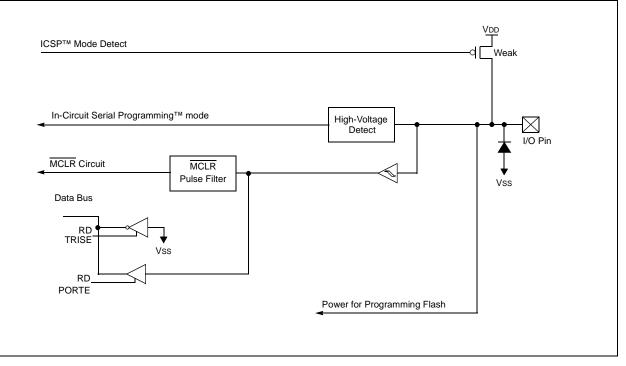

# 11.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (shared with Watchdog Timer)

- Programmable internal or external clock source

- Programmable external clock edge selection

- Interrupt on overflow

- TMR0 can be used to gate Timer1

Figure 11-1 is a block diagram of the Timer0 module.

# 11.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

### 11.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-Bit Timer mode is selected by clearing the T0CS bit of the OPTION register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

**Note:** The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

## 11.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin or the Capacitive Sensing Oscillator (CPSOSC) signal.

8-Bit Counter mode using the T0CKI pin is selected by setting the T0CS bit in the OPTION register to '1' and resetting the T0XCS bit in the CPSCON0 register to '0'.

8-Bit Counter mode using the Capacitive Sensing Oscillator (CPSOSC) signal is selected by setting the TOCS bit in the OPTION register to '1' and setting the T0XCS bit in the CPSCON0 register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the T0SE bit in the OPTION register.

## FIGURE 11-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

#### 11.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the OPTION register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

| Note: | When the prescaler is assigned to WDT, a    |

|-------|---------------------------------------------|

|       | CLRWDT instruction will clear the prescaler |

|       | along with the WDT.                         |

### 11.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The T0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The T0IF bit can only be cleared in software. The Timer0 interrupt enable is the T0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|

|       | processor from Sleep since the timer is |  |  |  |  |

|       | frozen during Sleep.                    |  |  |  |  |

#### 11.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 23.0** "**Electrical Specifications**".

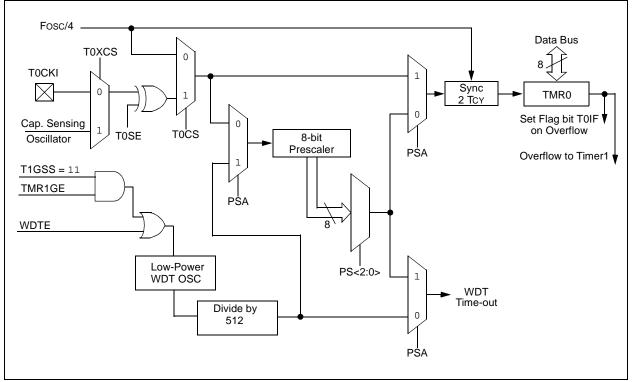

# 15.3 PWM Mode

The PWM mode generates a Pulse-Width Modulated signal on the CCPx pin. The duty cycle, period and resolution are determined by the following registers:

- PR2

- T2CON

- CCPRxL

- CCPxCON

In Pulse-Width Modulation (PWM) mode, the CCP module produces up to a 10-bit resolution PWM output on the CCPx pin.

Figure 15-3 shows a simplified block diagram of PWM operation.

Figure 15-4 shows a typical waveform of the PWM signal.

For a step-by-step procedure on how to set up the CCP module for PWM operation, refer to **Section 15.3.8** "Setup for PWM Operation".

FIGURE 15-3: SIMPLIFIED PWM BLOCK DIAGRAM

The PWM output (Figure 15-4) has a time base (period) and a time that the output stays high (duty cycle).

FIGURE 15-4: CCP PWM OUTPUT

## 15.3.1 CCPx PIN CONFIGURATION

In PWM mode, the CCPx pin is multiplexed with the PORT data latch. The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

Either RC1 or RB3 can be selected as the CCP2 pin. Refer to **Section 6.1** "Alternate Pin Function" for more information.

Note: Clearing the CCPxCON register will relinquish CCPx control of the CCPx pin.

# 16.4 AUSART Operation During Sleep

The AUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 16.4.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (refer to Section 16.3.2.4 "Synchronous Slave Reception Setup:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE global interrupt enable bit of the INTCON register is also set, then the Interrupt Service Routine at address 0004h will be called.

### 16.4.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Transmission (refer to Section 16.3.2.2 "Synchronous Slave Transmission Setup:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE global interrupt enable bit is also set then the Interrupt Service Routine at address 0004h will be called.

| R/W-0                 | R/W-0                                                                             | R/W-0                                                                                       | R/W-0                        | R/W-0                             | R/W-0                               | R/W-0                                 | R/W-0                         |

|-----------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------|-----------------------------------|-------------------------------------|---------------------------------------|-------------------------------|

| WCOL                  | SSPOV                                                                             | SSPEN                                                                                       | CKP                          | SSPM3                             | SSPM2                               | SSPM1                                 | SSPM0                         |

| bit 7                 | ·                                                                                 |                                                                                             |                              |                                   |                                     |                                       | bit (                         |

| Levendi               |                                                                                   |                                                                                             |                              |                                   |                                     |                                       |                               |

| Legend:<br>R = Readat | la hit                                                                            | M = Mritabla                                                                                | hit                          |                                   | monted hit rea                      | d oo 'O'                              |                               |

| -n = Value a          |                                                                                   | W = Writable bit<br>'1' = Bit is set                                                        |                              | 0 = 0 miniple<br>0' = Bit is cle  | mented bit, rea                     | x = Bit is unki                       | 0.011/0                       |

|                       |                                                                                   |                                                                                             |                              |                                   | aleu                                |                                       | IOWII                         |

| bit 7                 | WCOL: Writ                                                                        | te Collision Dete                                                                           | ct bit                       |                                   |                                     |                                       |                               |

|                       |                                                                                   | PBUF register is                                                                            |                              | e it is still transr              | nittina the prev                    | ious word (mus                        | t be cleared i                |

|                       | softwar                                                                           | •                                                                                           |                              |                                   | 5 1                                 | , , , , , , , , , , , , , , , , , , , |                               |

|                       | 0 = No colli                                                                      |                                                                                             |                              |                                   |                                     |                                       |                               |

| bit 6                 | SSPOV: Re                                                                         | ceive Overflow I                                                                            | ndicator bit                 |                                   |                                     |                                       |                               |

|                       | overflov<br>the SS<br>overflov<br>SSPBU                                           | byte is received<br>w, the data in SS<br>PBUF, even if o<br>w bit is not set s<br>register. | PSR is lost. Conly transmitt | Overflow can or<br>ing data, to a | nly occur in Sla<br>void setting ov | ve mode. The uverflow. In Mas         | user must rea<br>ter mode, th |

|                       | 0 = No ove                                                                        |                                                                                             |                              | 1.5                               |                                     |                                       |                               |

| bit 5                 | •                                                                                 | nchronous Seria                                                                             |                              |                                   |                                     | rt. m:m.a.(1)                         |                               |

|                       |                                                                                   | s serial port and on serial port and on serial port and                                     |                              |                                   |                                     | t pins <sup>(1)</sup>                 |                               |

| bit 4                 |                                                                                   | Polarity Select k                                                                           | •                            | ·                                 |                                     |                                       |                               |

|                       |                                                                                   | e for clock is a h                                                                          | 0                            |                                   |                                     |                                       |                               |

| <b>h</b> it 0 0       |                                                                                   |                                                                                             |                              | de Celesthite                     |                                     |                                       |                               |

| bit 3-0               | SSPM<3:0>: Synchronous Serial Port Mode Select bits                               |                                                                                             |                              |                                   |                                     |                                       |                               |

|                       | 0000 = SPI Master mode, clock = Fosc/4<br>0001 = SPI Master mode, clock = Fosc/16 |                                                                                             |                              |                                   |                                     |                                       |                               |

|                       |                                                                                   | Master mode, c                                                                              |                              |                                   |                                     |                                       |                               |

|                       |                                                                                   | Master mode, c                                                                              |                              |                                   |                                     |                                       |                               |

|                       |                                                                                   | Slave mode, clo                                                                             |                              |                                   |                                     |                                       |                               |

|                       |                                                                                   | Slave mode, clo                                                                             | -                            | -                                 |                                     | can be used as                        | i/O pin.                      |

| Note 1: V             | when enabled, th                                                                  | hese pins must b                                                                            | be properly co               | onfigured as inp                  | out or output.                      |                                       |                               |

# REGISTER 17-1: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (SPI MODE)

# 17.2 I<sup>2</sup>C Mode

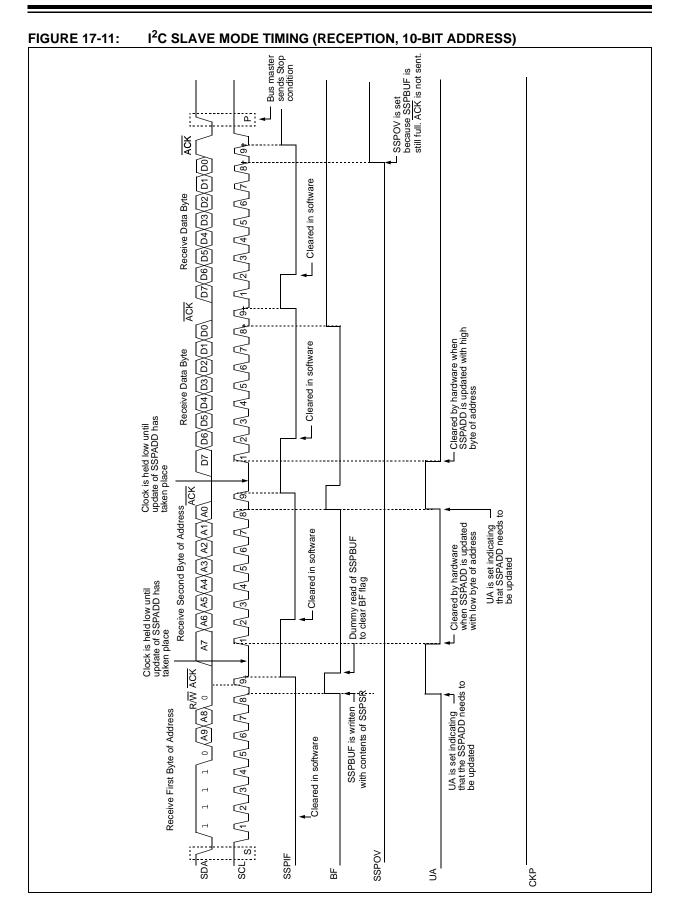

The SSP module, in  $I^2C$  mode, implements all slave functions, except general call support. It provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the  $I^2C$  Standard mode specifications:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- Start and Stop bit interrupts enabled to support firmware Master mode

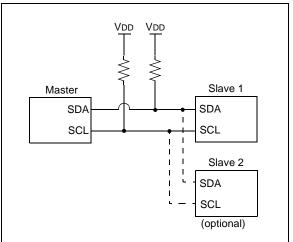

- Address masking

Two pins are used for data transfer; the SCL pin (clock line) and the SDA pin (data line). The user must configure the two pin's data direction bits as inputs in the appropriate TRIS register. Upon enabling  $I^2C$  mode, the  $I^2C$  slew rate limiters in the I/O pads are controlled by the SMP bit of SSPSTAT register. The SSP module functions are enabled by setting the SSPEN bit of SSPCON register.

Data is sampled on the rising edge and shifted out on the falling edge of the clock. This ensures that the SDA signal is valid during the SCL high time. The SCL clock input must have minimum high and low times for proper operation. Refer to **Section 23.0** "**Electrical Specifications**".

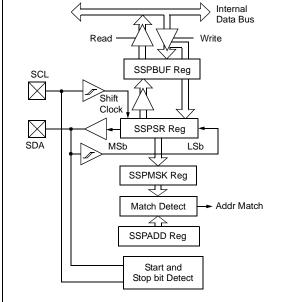

# FIGURE 17-7: I<sup>2</sup>C MODE BLOCK DIAGRAM

# FIGURE 17-8: TYPICAL I<sup>2</sup>C

## CONNECTIONS

The SSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. They are:

- SSP Control (SSPCON) register

- SSP Status (SSPSTAT) register

- Serial Receive/Transmit Buffer (SSPBUF) register

- SSP Shift Register (SSPSR), not directly accessible

- SSP Address (SSPADD) register

- SSP Address Mask (SSPMSK) register

## 17.2.1 HARDWARE SETUP

Selection of  $I^2C$  mode, with the SSPEN bit of the SSPCON register set, forces the SCL and SDA pins to be open drain, provided these pins are programmed as inputs by setting the appropriate TRISC bits. The SSP module will override the input state with the output data, when required, such as for Acknowledge and slave-transmitter sequences.

**Note:** Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module

## 17.2.5 RECEPTION

When the  $R/\overline{W}$  bit of the received address byte is clear, the master will write data to the slave. If an address match occurs, the received address is loaded into the SSPBUF register. An address byte overflow will occur if that loaded address is not read from the SSPBUF before the next complete byte is received.

An SSP interrupt is generated for each data transfer byte. The BF,  $R/\overline{W}$  and  $D/\overline{A}$  bits of the SSPSTAT register are used to determine the status of the last received byte.

### FIGURE 17-10: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| R/<br>Receiving Address    | $\overline{W} = 0$<br>$\overline{\Delta C K}$ Receiving Data $\overline{\Delta C K}$ Receiving Data |                                                                  |

|----------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| SDA 1 A7XA6XA5XA4XA3XA2XA1 | ACK Receiving Data ACK Receiving Data<br>/D7/D6/D5/D4/D3/D2/D1/D0//D7/D6/D5/D4/D3/                  |                                                                  |

|                            | 3, 9, 1, 2, 3, 4, 5, 6, 7, 8, 9, 1, 2, 3, 4, 5,                                                     | /6\_/7\_/8 <del>\_</del> _/9\_/ <sup>!</sup> ₽ <sup>!</sup><br>I |

| SSPIF                      | Cleared in software                                                                                 | Bus Master<br>sends Stop                                         |

| BF                         | <ul> <li>SSPBUF register is read</li> </ul>                                                         | condition                                                        |

| SSPOV                      |                                                                                                     |                                                                  |

|                            | Bit SSPOV is set because the SSPBUF register is                                                     | s still full. 🗕                                                  |

|                            |                                                                                                     | s not sent.                                                      |

| RETFIE           | Return from Interrupt                                                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                              |

| Status Affected: | None                                                                                                                                                                                                                 |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top-of-Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global<br>Interrupt Enable bit, GIE (INT-<br>CON<7>). This is a 2-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                                                    |

| Cycles:          | 2                                                                                                                                                                                                                    |

| Example:         | RETFIE                                                                                                                                                                                                               |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                               |

| RETLW            | Return with literal in W                                                                                                                                                                                                        |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                                                                        |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                                                             |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                                                                    |

| Status Affected: | None                                                                                                                                                                                                                            |

| Description:     | The W register is loaded with the<br>8-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a 2-cycle instruction.                                                   |

| Words:           | 1                                                                                                                                                                                                                               |

| Cycles:          | 2                                                                                                                                                                                                                               |

| Example:         | CALL TABLE;W contains table                                                                                                                                                                                                     |

| TABLE            | <pre>;offset value<br/>;W now has table value<br/>ADDWF PC ;W = offset<br/>RETLW k1 ;Begin table<br/>RETLW k2 ;<br/>RETLW kn ; End of table<br/>Before Instruction<br/>W = 0x07<br/>After Instruction<br/>W = value of k8</pre> |

| RETURN           | Return from Subroutine                                                                                                                                                                                                          |

| Syntax:          | [label] RETURN                                                                                                                                                                                                                  |

| Operands:        | None                                                                                                                                                                                                                            |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                            |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a 2-cycle instruc-<br>tion.                                                                      |

| RLF              | Rotate Left f through Carry                                                                                                                                                                                          |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                             |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                   |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                                |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                    |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is stored<br>back in register 'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                    |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                    |  |  |  |  |

| Example:         | RLF REG1,0                                                                                                                                                                                                           |  |  |  |  |

|                  | Before Instruction                                                                                                                                                                                                   |  |  |  |  |

|                  | REG1 = 1110 0110                                                                                                                                                                                                     |  |  |  |  |

|                  | C = 0                                                                                                                                                                                                                |  |  |  |  |

|                  | After Instruction                                                                                                                                                                                                    |  |  |  |  |

|                  | REG1 = 1110 0110                                                                                                                                                                                                     |  |  |  |  |

|                  | $W = 1100 \ 1100$                                                                                                                                                                                                    |  |  |  |  |

|                  | C = 1                                                                                                                                                                                                                |  |  |  |  |

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                      |

| Operands:        | None                                                                                                                                                                                                                               |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow \text{WDT,} \\ 0 \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$                                              |

| Status Affected: | TO, PD                                                                                                                                                                                                                             |

| Description:     | The power-down Status bit, $\overline{PD}$ is<br>cleared. Time-out Status bit, $\overline{TO}$<br>is set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                           |

| Operation:       | See description below                                                                                                                                                                                                 |

| Status Affected: | С                                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is placed<br>back in register 'f'. |

|                  | C Register f                                                                                                                                                                                                          |

| SUBLW            | Subtract W from literal                                                                                                  |            |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|

| Syntax:          | [label] SL                                                                                                               | JBLW k     |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                      |            |  |  |  |

| Operation:       | $k \text{ - } (W) \to (V)$                                                                                               | N)         |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                 |            |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the 8-bit literal 'k'. The result is placed in the W register. |            |  |  |  |

|                  | <b>C</b> = 0                                                                                                             | W > k      |  |  |  |

|                  | <b>C</b> = 1                                                                                                             | $W \leq k$ |  |  |  |

DC = 0

**DC** = 1

W<3:0> > k<3:0>

$W < 3:0 > \le k < 3:0 >$

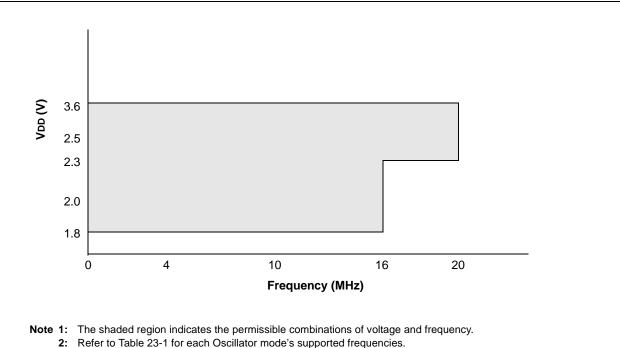

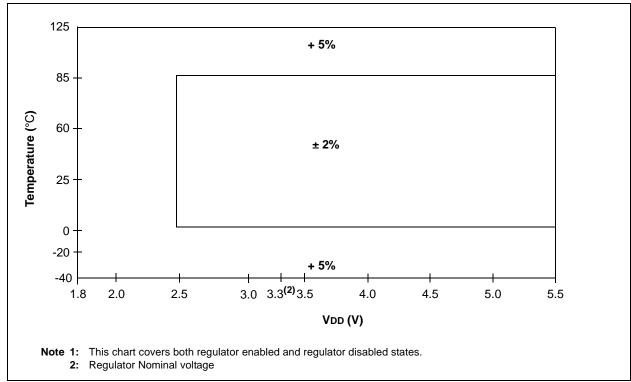

FIGURE 23-6: HFINTOSC FREQUENCY ACCURACY OVER DEVICE VDD AND TEMPERATURE

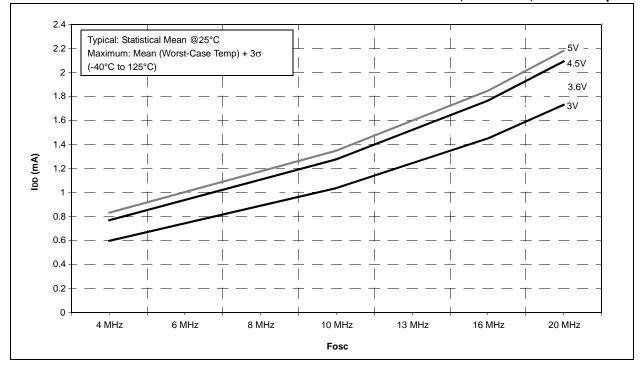

#### FIGURE 24-9: PIC16F722/3/4/6/7 MAXIMUM IDD vs. Fosc OVER VDD, HS MODE, VCAP = 0.1 µF

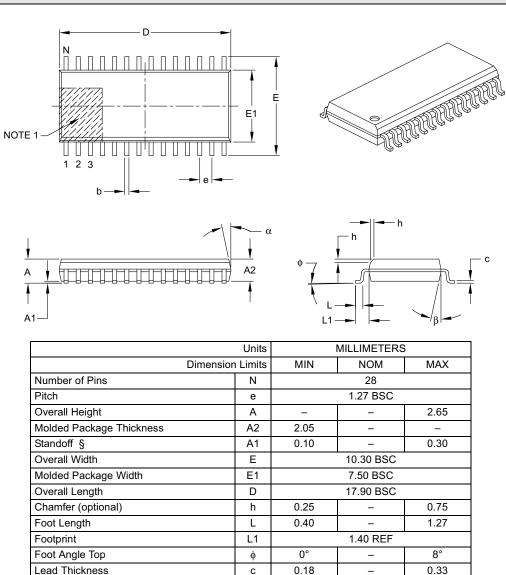

# 28-Lead Plastic Small Outline (SO) – Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

b

α

β

0.31

5°

5°

\_

\_

\_

4. Dimensioning and tolerancing per ASME Y14.5M.

Lead Width

Mold Draft Angle Top

Mold Draft Angle Bottom

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-052B

0.51

15°

15°

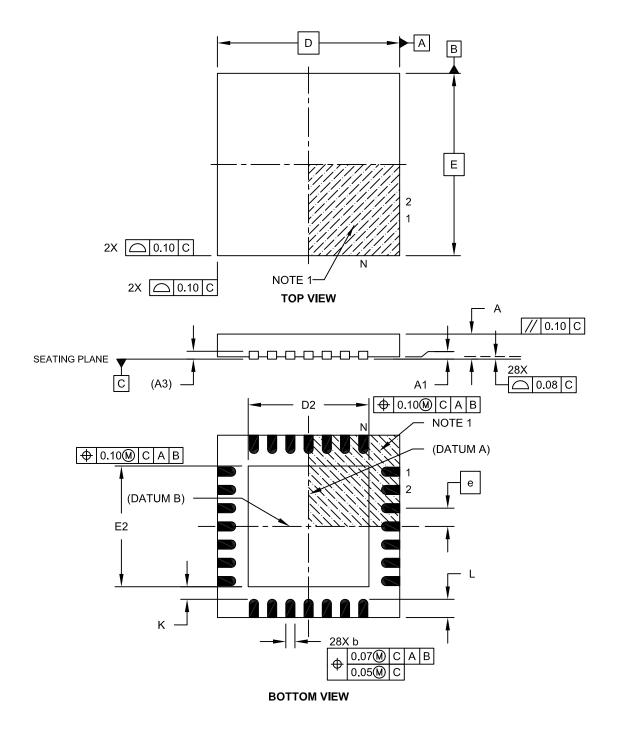

# 28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-152A Sheet 1 of 2