Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

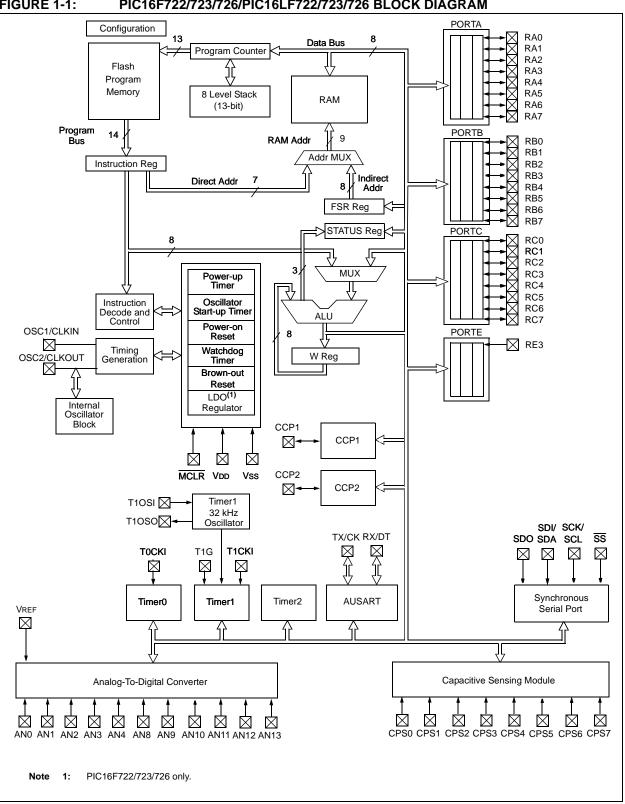

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 14x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf727t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                      | Function | Input<br>Type | Output<br>Type | Description                                                                                              |  |  |  |

|---------------------------------------------------------------------------|----------|---------------|----------------|----------------------------------------------------------------------------------------------------------|--|--|--|

| RD3/CPS11                                                                 | RD3      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |  |

|                                                                           | CPS11    | AN            | —              | Capacitive sensing input 11.                                                                             |  |  |  |

| RD4/CPS12                                                                 | RD4      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |  |

|                                                                           | CPS12    | AN            | —              | Capacitive sensing input 12.                                                                             |  |  |  |

| RD5/CPS13                                                                 | RD5      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |  |

|                                                                           | CPS13    | AN            | —              | Capacitive sensing input 13.                                                                             |  |  |  |

| RD6/CPS14                                                                 | RD6      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |  |

|                                                                           | CPS14    | AN            | _              | Capacitive sensing input 14.                                                                             |  |  |  |

| RD7/CPS15                                                                 | RD7      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |  |

|                                                                           | CPS15    | AN            | _              | Capacitive sensing input 15.                                                                             |  |  |  |

| RE0/AN5                                                                   | RE0      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |  |

|                                                                           | AN5      | AN            | —              | A/D Channel 5 input.                                                                                     |  |  |  |

| RE1/AN6                                                                   | RE1      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |  |

|                                                                           | AN6      | AN            | —              | A/D Channel 6 input.                                                                                     |  |  |  |

| RE2/AN7                                                                   | RE2      | ST            | CMOS           | General purpose I/O.                                                                                     |  |  |  |

|                                                                           | AN7      | AN            | _              | A/D Channel 7 input.                                                                                     |  |  |  |

| RE3/MCLR/Vpp                                                              | RE3      | TTL           | —              | General purpose input.                                                                                   |  |  |  |

|                                                                           | MCLR     | ST            | _              | Master Clear with internal pull-up.                                                                      |  |  |  |

|                                                                           | Vpp      | ΗV            | —              | Programming voltage.                                                                                     |  |  |  |

| VDD                                                                       | Vdd      | Power         | —              | - Positive supply.                                                                                       |  |  |  |

| Vss                                                                       | Vss      | Power         | _              | Ground reference.                                                                                        |  |  |  |

| Legend: AN = Analog input or<br>TTL = TTL compatible<br>HV = High Voltage | input ST |               | nitt Trigger   | ble input or output OD = Open Drain<br>input with CMOS levels $I^2C$ = Schmitt Trigger input with $I^2C$ |  |  |  |

#### TABLE 1-1: PIC16(L)F722/3/4/6/7 PINOUT DESCRIPTION (CONTINUED)

**Note:** The PIC16F722/3/4/6/7 devices have an internal low dropout voltage regulator. An external capacitor must be connected to one of the available VCAP pins to stabilize the regulator. For more information, see **Section 5.0 "Low Dropout (LDO) Voltage Regulator**". The PIC16LF722/3/4/6/7 devices do not have the voltage regulator and therefore no external capacitor is required.

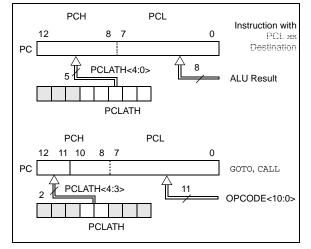

#### 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-7 shows the two situations for the loading of the PC. The upper example in Figure 2-7 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-7 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 2-7: LOADING OF PC IN DIFFERENT SITUATIONS

#### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the Application Note *AN556, Implementing a Table Read* (DS00556).

#### 2.3.2 STACK

All devices have an 8-level x 13-bit wide hardware stack (refer to Figures 2-1 and 2-3). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth PUSH overwrites the value that was stored from the first PUSH. The tenth PUSH overwrites the second PUSH (and so on).

- Note 1: There are no Status bits to indicate Stack Overflow or Stack Underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

#### 2.4 **Program Memory Paging**

All devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper two bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is POPed off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the RETURN instructions (which POPs the address from the stack).

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 500 |         |                     |  |  |  |  |

|---------|---------|---------|---------------------|--|--|--|--|

|         | PAGESEL | SUB_P1  | ;Select page 1      |  |  |  |  |

|         |         |         | ;(800h-FFFh)        |  |  |  |  |

|         | CALL    | SUB1_P1 | ;Call subroutine in |  |  |  |  |

|         | :       |         | ;page 1 (800h-FFFh) |  |  |  |  |

|         | :       |         |                     |  |  |  |  |

|         | ORG     | 900h    | ;page 1 (800h-FFFh) |  |  |  |  |

| SUB1_P1 |         |         |                     |  |  |  |  |

|         | :       |         | ;called subroutine  |  |  |  |  |

|         |         |         | ;page 1 (800h-FFFh) |  |  |  |  |

|         | :       |         |                     |  |  |  |  |

|         | RETURN  |         | ;return to          |  |  |  |  |

|         |         |         | ;Call subroutine    |  |  |  |  |

|         |         |         | ;in page 0          |  |  |  |  |

|         |         |         | ;(000h-7FFh)        |  |  |  |  |

Note: The contents of the PCLATH register are unchanged after a RETURN or RETFIE instruction is executed. The user must rewrite the contents of the PCLATH register for any subsequent subroutine calls or GOTO instructions.

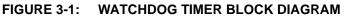

#### 3.4.2 WDT CONTROL

The WDTE bit is located in the Configuration Word Register 1. When set, the WDT runs continuously.

The PSA and PS<2:0> bits of the OPTION register control the WDT period. See **Section 11.0 "Timer0 Module"** for more information.

#### TABLE 3-1: WDT STATUS

| Conditions                                               | WDT                          |

|----------------------------------------------------------|------------------------------|

| WDTE = 0                                                 | Cleared                      |

| CLRWDT Command                                           |                              |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |

#### TABLE 3-5: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 0000h                 | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 0000h                 | 0001 Ouuu          | uu               |

| WDT Reset                          | 0000h                 | 0000 uuuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 0000h                 | 0001 1xxx          | 10               |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Interrupt Enable bit, GIE, is set, the PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

#### TABLE 3-6: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on POR,<br>BOR | Value on<br>all other<br>Resets <sup>(1)</sup> |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|----------------------|------------------------------------------------|

| STATUS | IRP   | RP1   | RP0   | TO    | PD    | Z     | DC    | С     | 0001 1xxx            | 000q quuu                                      |

| PCON   | _     | -     | _     | -     | -     | _     | POR   | BOR   | dd                   | uu                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition. Shaded cells are not used by Resets.

**Note 1:** Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

#### EXAMPLE 4-1: SAVING W, STATUS AND PCLATH REGISTERS IN RAM

| MOVWF<br>SWAPF          | W_TEMP<br>STATUS,W                                      | ;Copy W to W_TEMP register<br>;Swap status to be saved into W<br>;Swaps are used because they do not affect the status bits                           |

|-------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVWF<br>MOVF           | STATUS_TEMP<br>STATUS_TEMP<br>PCLATH,W<br>PCLATH_TEMP   | ;Select regardless of current bank<br>;Copy status to bank zero STATUS_TEMP register<br>;Copy PCLATH to W register<br>;Copy W register to PCLATH_TEMP |

| :(ISR)<br>:             |                                                         | ;Insert user code here                                                                                                                                |

| MOVF                    | STATUS_TEMP<br>PCLATH_TEMP,W<br>PCLATH<br>STATUS_TEMP,W | ;Select regardless of current bank<br>;<br>;Restore PCLATH<br>;Swap STATUS_TEMP register into W<br>;(sets bank to original state)                     |

| MOVWF<br>SWAPF<br>SWAPF | STATUS<br>W_TEMP,F<br>W_TEMP,W                          | ;Move W into STATUS register<br>;Swap W_TEMP<br>;Swap W_TEMP into W                                                                                   |

#### 4.5.1 INTCON REGISTER

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, PORTB change and external RB0/INT/SEG0 pin interrupts.

```

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

```

### 7.0 OSCILLATOR MODULE

#### 7.1 Overview

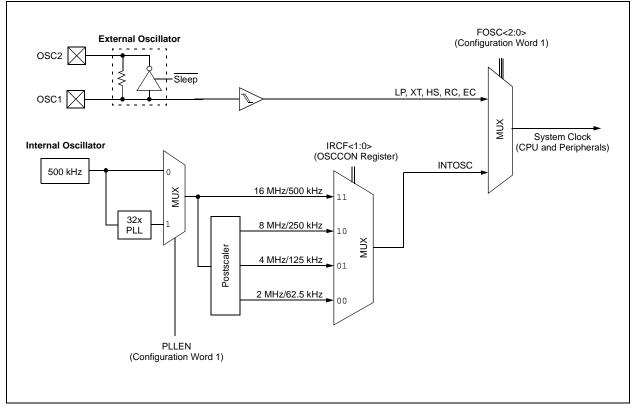

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 7-1 illustrates a block diagram of the oscillator module.

Clock sources can be configured from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system can be configured to use an internal calibrated high-frequency oscillator as clock source, with a choice of selectable speeds via software.

Clock source modes are configured by the FOSC bits in Configuration Word 1 (CONFIG1). The oscillator module can be configured for one of eight modes of operation.

- 1. RC External Resistor-Capacitor (RC) with Fosc/4 output on OSC2/CLKOUT.

- 2. RCIO External Resistor-Capacitor (RC) with I/O on OSC2/CLKOUT.

- 3. INTOSC Internal oscillator with Fosc/4 output on OSC2 and I/O on OSC1/CLKIN.

- 4. INTOSCIO Internal oscillator with I/O on OSC1/CLKIN and OSC2/CLKOUT.

- 5. EC External clock with I/O on OSC2/CLKOUT.

- 6. HS High Gain Crystal or Ceramic Resonator mode.

- 7. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode.

- 8. LP Low-Power Crystal mode.

FIGURE 7-1: SIMPLIFIED PIC<sup>®</sup> MCU CLOCK SOURCE BLOCK DIAGRAM

#### 11.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the OPTION register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

| Note: | When the prescaler is assigned to WDT, a    |

|-------|---------------------------------------------|

|       | CLRWDT instruction will clear the prescaler |

|       | along with the WDT.                         |

#### 11.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The T0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The T0IF bit can only be cleared in software. The Timer0 interrupt enable is the T0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |

|-------|-----------------------------------------|

|       | processor from Sleep since the timer is |

|       | frozen during Sleep.                    |

#### 11.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 23.0** "**Electrical Specifications**".

| FIGURE 12-6:           | TIMER1 GATE SINGLE                                          | -PULSE AND TOGGLE COMBINED MODE                  |

|------------------------|-------------------------------------------------------------|--------------------------------------------------|

| TMR1GE                 |                                                             |                                                  |

| T1GPOL                 |                                                             |                                                  |

| T1GSPM                 |                                                             |                                                  |

| T1GTM                  |                                                             |                                                  |

| T1GG <u>O/</u><br>DONE | ← Set by software<br>Counting enabled<br>rising edge of T10 | Cleared by hardware on<br>falling edge of T1GVAL |

| T1G_IN                 |                                                             |                                                  |

| т1СКІ                  |                                                             |                                                  |

| T1GVAL                 |                                                             |                                                  |

| TIMER1                 | Ν                                                           | N+1 $N+2$ $N+3$ $N+4$                            |

| TMR1GIF                | - Cleared by software                                       | Set by hardware on<br>falling edge of T1GVAL —   |

## 12.12 Timer1 Gate Control Register

The Timer1 Gate Control register (T1GCON), shown in Register 12-2, is used to control Timer1 Gate.

| R/W-0         | R/W-0              | R/W-0                                                                                                                           | R/W-0                            | R/W-0            | R-x             | R/W-0           | R/W-0  |  |  |  |  |

|---------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------|-----------------|-----------------|--------|--|--|--|--|

| TMR1GE        | T1GPOL             | T1GTM                                                                                                                           | T1GSPM                           | T1GGO/<br>DONE   | T1GVAL          | T1GSS1          | T1GSS0 |  |  |  |  |

| bit 7         | •                  |                                                                                                                                 |                                  |                  |                 |                 | bit    |  |  |  |  |

|               |                    |                                                                                                                                 |                                  |                  |                 |                 |        |  |  |  |  |

| Legend:       |                    |                                                                                                                                 |                                  |                  |                 |                 |        |  |  |  |  |

| R = Readable  |                    | W = Writable                                                                                                                    |                                  | -                | nented bit, rea |                 |        |  |  |  |  |

| -n = Value at | POR                | '1' = Bit is set                                                                                                                |                                  | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |  |  |  |  |

| h:+ 7         |                    | nor1 Coto Eng                                                                                                                   | hla hit                          |                  |                 |                 |        |  |  |  |  |

| bit 7         | If TMR1GE: If      | ner1 Gate Ena                                                                                                                   | DIE DIT                          |                  |                 |                 |        |  |  |  |  |

|               | This bit is ign    |                                                                                                                                 |                                  |                  |                 |                 |        |  |  |  |  |

|               | <u>If TMR10N =</u> | <u>1</u> :                                                                                                                      |                                  |                  |                 |                 |        |  |  |  |  |

|               |                    |                                                                                                                                 | rolled by the Ti                 |                  | ction           |                 |        |  |  |  |  |

| 1.11.0        |                    | -                                                                                                                               | ss of Timer1 ga                  | ate function     |                 |                 |        |  |  |  |  |

| bit 6         |                    | ner1 Gate Pola                                                                                                                  | •                                | into whon goto   | ic high)        |                 |        |  |  |  |  |

|               |                    |                                                                                                                                 | gh (Timer1 cou<br>w (Timer1 coui |                  |                 |                 |        |  |  |  |  |

| bit 5         |                    | er1 Gate Toggl                                                                                                                  |                                  | J                | /               |                 |        |  |  |  |  |

|               |                    | = Timer1 Gate Toggle mode is enabled.                                                                                           |                                  |                  |                 |                 |        |  |  |  |  |

|               |                    |                                                                                                                                 | de is disabled                   |                  | flop is cleared |                 |        |  |  |  |  |

| 1.11.4        | •                  |                                                                                                                                 | on every rising                  |                  |                 |                 |        |  |  |  |  |

| bit 4         |                    | <b>T1GSPM:</b> Timer1 Gate Single Pulse Mode bit<br>1 = Timer1 gate Single-Pulse mode is enabled and is controlling Timer1 gate |                                  |                  |                 |                 |        |  |  |  |  |

|               |                    |                                                                                                                                 | se mode is ena                   |                  | ntrolling Timer | i gate          |        |  |  |  |  |

| bit 3         |                    | _                                                                                                                               | e Single-Pulse                   |                  | atus bit        |                 |        |  |  |  |  |

|               |                    |                                                                                                                                 | e acquisition is                 | •                |                 |                 |        |  |  |  |  |

|               |                    |                                                                                                                                 | e acquisition h                  |                  |                 | n started       |        |  |  |  |  |

|               |                    | -                                                                                                                               | red when T1G                     | SPM is cleared   | d.              |                 |        |  |  |  |  |

| bit 2         |                    | ner1 Gate Curr                                                                                                                  |                                  |                  |                 |                 |        |  |  |  |  |

|               |                    |                                                                                                                                 | f the Timer1 ga<br>Enable (TMR1) |                  | e provided to   | IMR1H:TMR1L     |        |  |  |  |  |

| bit 1-0       | T1GSS<1:0>         | : Timer1 Gate                                                                                                                   | Source Select                    | bits             |                 |                 |        |  |  |  |  |

|               | 00 = Timer1        |                                                                                                                                 |                                  |                  |                 |                 |        |  |  |  |  |

|               |                    | Overflow outpu<br>latch PR2 outp                                                                                                |                                  |                  |                 |                 |        |  |  |  |  |

|               |                    | og Timer scale                                                                                                                  |                                  |                  |                 |                 |        |  |  |  |  |

|               | Watchde            |                                                                                                                                 |                                  |                  |                 |                 |        |  |  |  |  |

#### REGISTER 12-2: T1GCON: TIMER1 GATE CONTROL REGISTER

#### 15.3.4 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 15-4.

#### EQUATION 15-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2+1)]}{\log(2)}$$

bits

Note: If the pulse-width value is greater than the period, the assigned PWM pin(s) will remain unchanged.

#### TABLE 15-5: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 15-6: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 15.3.5 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 15.3.6 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency (Fosc). Any changes in the system clock frequency will result in changes to the PWM frequency. Refer to **Section 7.0** "**Oscillator Module**" for additional details.

#### 15.3.7 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 15.3.8 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Disable the PWM pin (CCPx) output driver(s) by setting the associated TRIS bit(s).

- 2. Load the PR2 register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- Load the CCPRxL register and the DCxBx bits of the CCPxCON register, with the PWM duty cycle value.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register. See Note below.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until Timer2 overflows, TMR2IF bit of the PIR1 register is set. See Note below.

- Enable the PWM pin (CCPx) output driver(s) by clearing the associated TRIS bit(s).

- **Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

#### 16.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the AUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive  |

|-------|-------------------------------------------|

|       | FIFO have framing errors, repeated reads  |

|       | of the RCREG will not clear the FERR bit. |

#### 16.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by setting the AUSART by clearing the SPEN bit of the RCSTA register.

#### 16.1.2.6 Receiving 9-bit Characters

The AUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the AUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

#### 16.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit of the PIR1 register. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

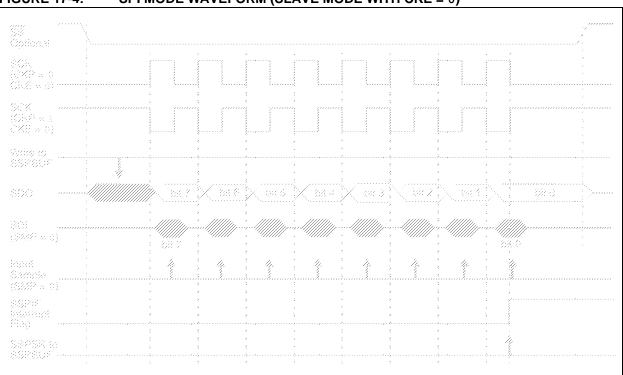

#### FIGURE 17-4: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 0)

#### SS SCK (CKP = 0 $\dot{C}KE = 1)$ SCK (CKP = 1 CKE = 1) Write to SSPBUF bit 6 bit 5 bit 4 bit 2 bit 1 bit 0 SDO bit '7 bit 3 ï SDI (SMP = 0)I bit 0 bit 7 Input Sample (SMP = 0)SSPIF Interrupt Flag SSPSR to SSPBUF 1 . i . . . .

#### FIGURE 17-5: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

#### 17.2.2 START AND STOP CONDITIONS

During times of no data transfer (Idle time), both the clock line (SCL) and the data line (SDA) are pulled high through external pull-up resistors. The Start and Stop conditions determine the start and stop of data transmission. The Start condition is defined as a high-to-low transition of the SDA line while SCL is high. The Stop condition is defined as a low-to-high transition of the SDA line while SCL is high.

Figure 17-9 shows the Start and Stop conditions. A master device generates these conditions for starting and terminating data transfer. Due to the definition of the Start and Stop conditions, when data is being transmitted, the SDA line can only change state when the SCL line is low.

#### 17.2.3 ACKNOWLEDGE

After the valid reception of an address or data byte, the hardware automatically will generate the Acknowledge (ACK) pulse and load the SSPBUF register with the received value currently in the SSPSR register. There are certain conditions that will cause the SSP module not to generate this ACK pulse. They include any or all of the following:

- The Buffer Full bit, BF of the SSPSTAT register, was set before the transfer was received.

- The SSP Overflow bit, SSPOV of the SSPCON register, was set before the transfer was received.

- The SSP Module is being operated in Firmware Master mode.

In such a case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF of the PIR1 register is set. Table 17-2 shows the results of when a data transfer byte is received, given the status of bits BF and SSPOV. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

# FIGURE 17-9: START AND STOP CONDITIONS

|  | TABLE 17-2: | DATA TRANSFER RECEIVED BYTE ACTIONS |

|--|-------------|-------------------------------------|

|--|-------------|-------------------------------------|

| Status Bits as Data<br>Transfer is Received |       | $SSPSR \to SSPBUF$ | Generate ACK | Set bit SSPIF<br>(SSP Interrupt occurs |  |

|---------------------------------------------|-------|--------------------|--------------|----------------------------------------|--|

| BF                                          | SSPOV |                    | Pulse        | if enabled)                            |  |

| 0                                           | 0     | Yes                | Yes          | Yes                                    |  |

| 1                                           | 0     | No                 | No           | Yes                                    |  |

| 1                                           | 1     | No                 | No           | Yes                                    |  |

| 0                                           | 1     | No                 | No           | Yes                                    |  |

Note 1: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

| RETFIE           | Return from Interrupt                                                                                                                                                                                                |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                       |  |  |  |

| Operands:        | None                                                                                                                                                                                                                 |  |  |  |

| Operation:       | $TOS \rightarrow PC, \\ 1 \rightarrow GIE$                                                                                                                                                                           |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                 |  |  |  |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top-of-Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global<br>Interrupt Enable bit, GIE (INT-<br>CON<7>). This is a 2-cycle<br>instruction. |  |  |  |

| Words:           | 1                                                                                                                                                                                                                    |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                    |  |  |  |

| Example:         | RETFIE                                                                                                                                                                                                               |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                               |  |  |  |

| RETLW            | Return with literal in W                                                                                                                                                                                                        |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                                                                        |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                                                             |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                                                                    |

| Status Affected: | None                                                                                                                                                                                                                            |

| Description:     | The W register is loaded with the<br>8-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a 2-cycle instruction.                                                   |

| Words:           | 1                                                                                                                                                                                                                               |

| Cycles:          | 2                                                                                                                                                                                                                               |

| Example:         | CALL TABLE;W contains table                                                                                                                                                                                                     |

| TABLE            | <pre>;offset value<br/>;W now has table value<br/>ADDWF PC ;W = offset<br/>RETLW k1 ;Begin table<br/>RETLW k2 ;<br/>RETLW kn ; End of table<br/>Before Instruction<br/>W = 0x07<br/>After Instruction<br/>W = value of k8</pre> |

| RETURN           | Return from Subroutine                                                                                                                                                                                                          |

| Syntax:          | [label] RETURN                                                                                                                                                                                                                  |

| Operands:        | None                                                                                                                                                                                                                            |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                            |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a 2-cycle instruc-<br>tion.                                                                      |

| RLF              | Rotate Left f through Carry                                                                                                                                                                                          |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                             |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                   |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                                |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                    |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is stored<br>back in register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                    |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                    |  |  |  |  |  |

| Example:         | RLF REG1,0                                                                                                                                                                                                           |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                                                                                   |  |  |  |  |  |

|                  | REG1 = 1110 0110                                                                                                                                                                                                     |  |  |  |  |  |

|                  | C = 0                                                                                                                                                                                                                |  |  |  |  |  |

|                  | After Instruction                                                                                                                                                                                                    |  |  |  |  |  |

|                  | REG1 = 1110 0110                                                                                                                                                                                                     |  |  |  |  |  |

|                  | $W = 1100 \ 1100$                                                                                                                                                                                                    |  |  |  |  |  |

|                  | C = 1                                                                                                                                                                                                                |  |  |  |  |  |

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                      |

| Operands:        | None                                                                                                                                                                                                                               |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow \text{WDT,} \\ 0 \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$                                              |

| Status Affected: | TO, PD                                                                                                                                                                                                                             |

| Description:     | The power-down Status bit, $\overline{PD}$ is<br>cleared. Time-out Status bit, $\overline{TO}$<br>is set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                              |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                           |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                                 |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                     |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is placed<br>back in register 'f'. |  |  |  |  |

|                  | C Register f                                                                                                                                                                                                          |  |  |  |  |

| SUBLW            | Subtract W from literal                                                                                                  |        |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|

| Syntax:          | [label] SL                                                                                                               | JBLW k |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                      |        |  |  |  |

| Operation:       | $k \text{-} (W) \to (V)$                                                                                                 | N)     |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                 |        |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the 8-bit literal 'k'. The result is placed in the W register. |        |  |  |  |

|                  | <b>C</b> = 0                                                                                                             | W > k  |  |  |  |

|                  | $C = 1$ $W \le k$                                                                                                        |        |  |  |  |

DC = 0

**DC** = 1

W<3:0> > k<3:0>

$W < 3:0 > \le k < 3:0 >$

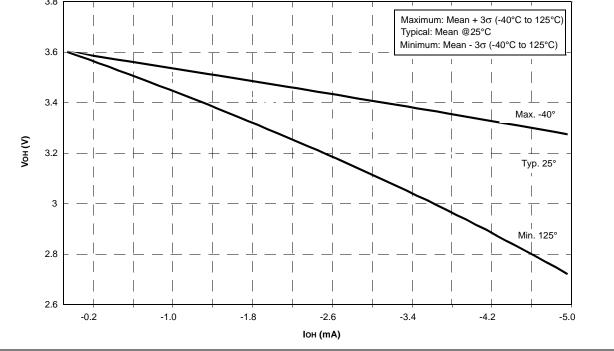

## 23.0 ELECTRICAL SPECIFICATIONS

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40°C to +125°C                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Storage temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 65°C to +150°C                        |

| Voltage on VDD with respect to Vss, PIC16F72X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0.3V to +6.5V                         |

| Voltage on VCAP pin with respect to Vss, PIC16F72X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -0.3V to +4.0V                        |

| Voltage on VDD with respect to Vss, PIC16LF72X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -0.3V to +4.0V                        |

| Voltage on MCLR with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -0.3V to +9.0V                        |