Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 368 x 8                                                                    |

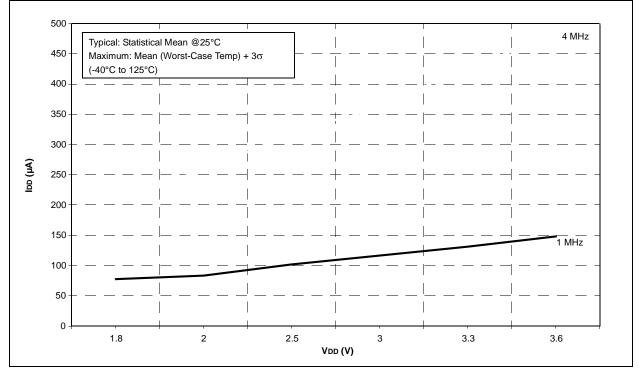

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 14x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 40-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 40-UQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf727t-i-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

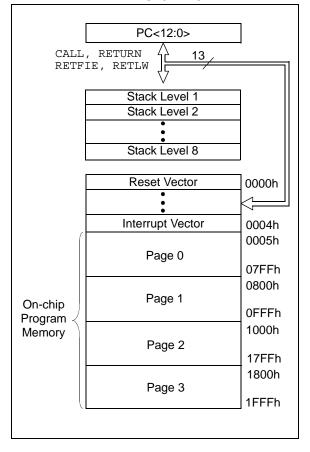

# FIGURE 2-3:

### PROGRAM MEMORY MAP AND STACK FOR THE PIC16F726/LF726 AND PIC16F727/LF727

# 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers (GPRs) and the Special Function Registers (SFRs). Bits RP0 and RP1 are bank select bits.

| <u>RP1</u> | <u>RP0</u> |

|------------|------------|

|            |            |

| 0 | 0 | $\rightarrow$ | Bank 0 is selected |

|---|---|---------------|--------------------|

| 0 | 1 | $\rightarrow$ | Bank 1 is selected |

| 1 | 0 | $\rightarrow$ | Bank 2 is selected |

| 1 | 1 | $\rightarrow$ | Bank 3 is selected |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are the General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank are mirrored in another bank for code reduction and quicker access.

# 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 128 x 8 bits in the PIC16F722/LF722, 192 x 8 bits in the PIC16F723/LF723 and PIC16F724/LF724, and 368 x 8 bits in the PIC16F726/LF726 and PIC16F727/LF727. Each register is accessed either directly or indirectly through the File Select Register (FSR), (Refer to **Section 2.5** "Indirect Addressing, INDF and FSR Registers").

# 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (refer to Table 2-1). These registers are static RAM.

The Special Function Registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the "core" are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

### FIGURE 2-4:

# PIC16F722/LF722 SPECIAL FUNCTION REGISTERS

| Indirect addr. <sup>(*)</sup> | 00h    | Indirect addr. <sup>(*)</sup> | 80h      | Indirect addr. <sup>(*)</sup> | 100h | Indirect addr.(*) | 180h |

|-------------------------------|--------|-------------------------------|----------|-------------------------------|------|-------------------|------|

| TMR0                          | 01h    | OPTION                        | 81h      | TMR0                          | 101h | OPTION            | 181h |

| PCL                           | 02h    | PCL                           | 82h      | PCL                           | 102h | PCL               | 182h |

| STATUS                        | 03h    | STATUS                        | 83h      | STATUS                        | 103h | STATUS            | 183h |

| FSR                           | 04h    | FSR                           | 84h      | FSR                           | 104h | FSR               | 184h |

| PORTA                         | 05h    | TRISA                         | 85h      |                               | 105h | ANSELA            | 185h |

| PORTB                         | 06h    | TRISB                         | 86h      |                               | 106h | ANSELB            | 186h |

| PORTC                         | 07h    | TRISC                         | 87h      |                               | 107h |                   | 187h |

|                               | 08h    | -                             | 88h      | CPSCON0                       | 108h |                   | 188h |

| PORTE                         | 09h    | TRISE                         | 89h      | CPSCON1                       | 109h |                   | 189h |

| PCLATH                        | 0Ah    | PCLATH                        | 8Ah      | PCLATH                        | 10Ah | PCLATH            | 18Ah |

| INTCON                        | 0Bh    | INTCON                        | 8Bh      | INTCON                        | 10Bh | INTCON            | 18Bh |

| PIR1                          | 0Ch    | PIE1                          | 8Ch      | PMDATL                        | 10Ch | PMCON1            | 18Ch |

| PIR2                          | 0Dh    | PIE2                          | 8Dh      | PMADRL                        | 10Dh | Reserved          | 18Dh |

| TMR1L                         | 0Eh    | PCON                          | 8Eh      | PMDATH                        | 10Eh | Reserved          | 18Eh |

| TMR1H                         | 0Fh    | T1GCON                        | 8Fh      | PMADRH                        | 10Fh | Reserved          | 18Fh |

| T1CON                         | 10h    | OSCCON                        | 90h      |                               | 110h |                   | 190h |

| TMR2                          | 11h    | OSCTUNE                       | 91h      |                               | 111h |                   | 191h |

| T2CON                         | 12h    | PR2                           | 92h      |                               | 112h |                   | 192h |

| SSPBUF                        | 13h    | SSPADD/SSPMSK                 | 93h      |                               | 113h |                   | 193h |

| SSPCON                        | 14h    | SSPSTAT                       | 94h      |                               | 114h |                   | 194h |

| CCPR1L                        | 15h    | WPUB                          | 95h      |                               | 115h |                   | 195h |

| CCPR1H                        | 16h    | IOCB                          | 96h      |                               | 116h |                   | 196h |

| CCP1CON                       | 17h    | -                             | 97h      |                               | 117h |                   | 197h |

| RCSTA                         | 18h    | TXSTA                         | 98h      |                               | 118h |                   | 198h |

| TXREG                         | 19h    | SPBRG                         | 99h      |                               | 119h |                   | 199h |

| RCREG                         | 1Ah    |                               | 9Ah      |                               | 11Ah |                   | 19Ah |

| CCPR2L                        | 1Bh    |                               | 9Bh      |                               | 11Bh |                   | 19Bh |

| CCPR2H                        | 1Ch    | APFCON                        | 9Ch      |                               | 11Ch |                   | 19Ch |

| CCP2CON                       | 1Dh    | FVRCON                        | 9Dh      |                               | 11Dh |                   | 19Dh |

| ADRES                         | 1Eh    |                               | 9Eh      |                               | 11Eh |                   | 19Eh |

| ADCON0                        | 1Fh    | ADCON1                        | 9Fh      |                               | 11Fh |                   | 19Fh |

|                               | 20h    | -                             | A0h      |                               | 120h |                   | 1A0h |

|                               |        | General                       |          |                               |      |                   |      |

|                               |        | Purpose                       |          |                               |      |                   |      |

|                               |        | Register                      |          |                               |      |                   |      |

| General                       |        | 32 Bytes                      |          |                               |      |                   |      |

| Purpose                       |        |                               | BFh      |                               |      |                   |      |

| Register                      |        |                               | C0h      |                               |      |                   |      |

| 96 Bytes                      |        |                               | EFh      |                               | 16Fh |                   | 1EFh |

|                               |        |                               | F0h      |                               | 170h |                   | 1F0h |

|                               |        | Accesses                      |          | Accesses                      |      | Accesses          |      |

|                               |        | 70h-7Fh                       |          | 70h-7Fh                       |      | 70h-7Fh           |      |

|                               | 7Fh    |                               | FFh      |                               | 17Fh |                   | 1FFh |

| Bank 0                        | 1,411  | Bank 1                        |          | Bank 2                        |      | Bank 3            |      |

| Dalik U                       |        | Ddiik I                       |          | Dalik Z                       |      | Dalik J           |      |

| gend: = Un                    | implem | ented data memory lo          | cations. | read as '0'.                  |      |                   |      |

| Address                | Name       | Bit 7         | Bit 6         | Bit 5         | Bit 4           | Bit 3         | Bit 2           | Bit 1         | Bit 0   | Value on:<br>POR, BOR | Page   |

|------------------------|------------|---------------|---------------|---------------|-----------------|---------------|-----------------|---------------|---------|-----------------------|--------|

| Bank 2                 | -          |               |               |               |                 |               |                 |               |         |                       |        |

| 100h <sup>(2)</sup>    | INDF       | Addressing    | this location | uses conten   | its of FSR to a | address data  | memory (not a   | a physical re | gister) | XXXX XXXX             | 29,37  |

| 101h                   | TMR0       | Timer0 Mod    | lule Register |               |                 |               |                 |               |         | XXXX XXXX             | 105,37 |

| 102h <sup>(2)</sup>    | PCL        | Program Co    | ounter's (PC) | Least Signif  | ficant Byte     |               |                 |               |         | 0000 0000             | 28,37  |

| 103h <sup>(2)</sup>    | STATUS     | IRP           | RP1           | RP0           | TO              | PD            | Z               | DC            | С       | 0001 1xxx             | 25,37  |

| 104h <sup>(2)</sup>    | FSR        | Indirect Data | a Memory Ad   | ddress Point  | er              | •             |                 |               | •       | XXXX XXXX             | 29,37  |

| 105h                   | —          | Unimpleme     | nted          |               |                 |               |                 |               |         |                       |        |

| 106h                   | —          | Unimpleme     | nted          |               |                 |               |                 |               |         |                       |        |

| 107h                   | —          | Unimpleme     | nted          |               |                 |               |                 |               |         |                       |        |

| 108h                   | CPSCON0    | CPSON         | _             | _             | _               | CPSRNG1       | CPSRNG0         | CPSOUT        | TOXCS   | 0 0000                | 126,38 |

| 109h                   | CPSCON1    | _             | _             | _             | _               | CPSCH3        | CPSCH2          | CPSCH1        | CPSCH0  | 0000                  | 127,38 |

| 10Ah <sup>(1, 2)</sup> | PCLATH     | _             | _             | _             | Write Buffer    | for the upper | 5 bits of the F | rogram Cou    | nter    | 0 0000                | 28,37  |

| 10Bh <sup>(2)</sup>    | INTCON     | GIE           | PEIE          | T0IE          | INTE            | RBIE          | T0IF            | INTF          | RBIF    | 0000 000x             | 44,37  |

| 10Ch                   | PMDATL     | Program Me    | emory Read    | Data Registe  | er Low Byte     | •             |                 |               | •       | XXXX XXXX             | 181,38 |

| 10Dh                   | PMADRL     | Program Me    | emory Read    | Address Reg   | gister Low Byt  | e             |                 |               |         | XXXX XXXX             | 181,38 |

| 10Eh                   | PMDATH     | _             | _             | Program M     | emory Read [    | Data Register | High Byte       |               |         | xx xxxx               | 181,38 |

| 10Fh                   | PMADRH     | _             | _             | _             | Program Me      | mory Read A   | ddress Regist   | er High Byte  | )       | x xxxx                | 181,38 |

| Bank 3                 |            |               |               |               | •               |               |                 |               |         | •                     |        |

| 180h <sup>(2)</sup>    | INDF       | Addressing    | this location | uses conten   | its of FSR to a | address data  | memory (not a   | a physical re | gister) | xxxx xxxx             | 29,37  |

| 181h                   | OPTION_REG | RBPU          | INTEDG        | TOCS          | TOSE            | PSA           | PS2             | PS1           | PS0     | 1111 1111             | 26,37  |

| 182h <sup>(2)</sup>    | PCL        | Program Co    | ounter (PC) L | east Signific | ant Byte        |               |                 |               |         | 0000 0000             | 28,37  |

| 183h <sup>(2)</sup>    | STATUS     | IRP           | RP1           | RP0           | TO              | PD            | Z               | DC            | С       | 0001 1xxx             | 25,37  |

| 184h <sup>(2)</sup>    | FSR        | Indirect Data | a Memory Ad   | ddress Point  | er              |               |                 |               |         | xxxx xxxx             | 29,37  |

| 185h                   | ANSELA     | —             | —             | ANSA5         | ANSA4           | ANSA3         | ANSA2           | ANSA1         | ANSA0   | 11 1111               | 52,38  |

| 186h                   | ANSELB     | _             | _             | ANSB5         | ANSB4           | ANSB3         | ANSB2           | ANSB1         | ANSB0   | 11 1111               | 61,38  |

| 187h                   | —          | Unimpleme     | nted          |               |                 |               |                 |               |         | —                     | _      |

| 188h                   | ANSELD     | ANSD7         | ANSD6         | ANSD5         | ANSD4           | ANSD3         | ANSD2           | ANSD1         | ANSD0   | 1111 1111             | 78,38  |

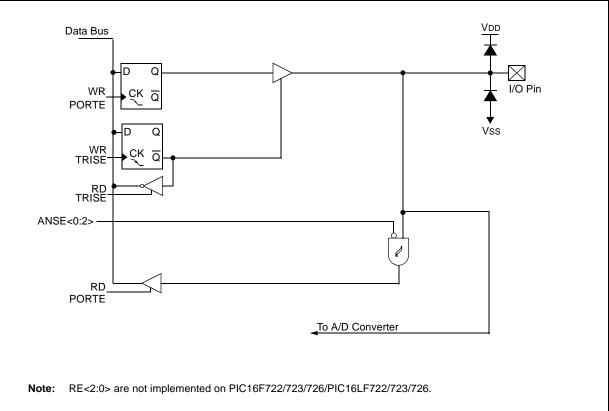

| 189h <sup>(3)</sup>    | ANSELE     | —             | _             | _             | _               | _             | ANSE2           | ANSE1         | ANSE0   | 111                   | 82,38  |

| 18Ah <sup>(1, 2)</sup> | PCLATH     | —             | —             | _             | Write Buffer    | for the upper | 5 bits of the F | rogram Cou    | nter    | 0 0000                | 28,37  |

| 18Bh <sup>(2)</sup>    | INTCON     | GIE           | PEIE          | T0IE          | INTE            | RBIE          | T0IF            | INTF          | RBIF    | x000 0000             | 44,37  |

| 18Ch                   | PMCON1     | Reserved      | _             | _             | —               | _             | _               | —             | RD      | 10                    | 182,38 |

| 18Dh                   | —          | Unimpleme     | nted          |               |                 |               |                 |               |         | _                     |        |

| 18Eh                   | —          | Unimpleme     | nted          |               |                 |               |                 |               |         | —                     | _      |

|                        | 1          | Unimplemented |               |               |                 |               |                 |               |         |                       |        |

#### **TABLE 2-1:** PIC16(L)F722/3/4/6/7 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter. Note 1:

These registers can be addressed from any bank. 2:

These registers/bits are not implemented on PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'. Accessible only when SSPM<3:0 > 1001. Accessible only when SSPM<3:0 > 1001. This bit is always '1' as RE3 is input-only. 3:

4:

5:

6:

| TABLE 51. STATUS BITS AND THEIR SIGNIFICANCE |     |    |    |                                                         |  |  |  |  |  |

|----------------------------------------------|-----|----|----|---------------------------------------------------------|--|--|--|--|--|

| POR                                          | BOR | то | PD | Condition                                               |  |  |  |  |  |

| 0                                            | x   | 1  | 1  | Power-on Reset or LDO Reset                             |  |  |  |  |  |

| 0                                            | x   | 0  | x  | Illegal, TO is set on POR                               |  |  |  |  |  |

| 0                                            | x   | x  | 0  | Illegal, PD is set on POR                               |  |  |  |  |  |

| 1                                            | 0   | 1  | 1  | Brown-out Reset                                         |  |  |  |  |  |

| 1                                            | 1   | 0  | 1  | WDT Reset                                               |  |  |  |  |  |

| 1                                            | 1   | 0  | 0  | WDT Wake-up                                             |  |  |  |  |  |

| 1                                            | 1   | u  | u  | MCLR Reset during normal operation                      |  |  |  |  |  |

| 1                                            | 1   | 1  | 0  | MCLR Reset during Sleep or interrupt wake-up from Sleep |  |  |  |  |  |

# TABLE 3-1: STATUS BITS AND THEIR SIGNIFICANCE

# TABLE 3-2: RESET CONDITION FOR SPECIAL REGISTERS<sup>(2)</sup>

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 0000h                 | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 0000h                 | 0001 Ouuu          | uu               |

| WDT Reset                          | 0000h                 | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | uu               |

| Brown-out Reset                    | 0000h                 | 0001 luuu          | u0               |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

**2:** If a Status bit is not implemented, that bit will be read as '0'.

| Name    | Bit 7       | Bit 6          | Bit 5         | Bit 4          | Bit 3                   | Bit 2       | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------|----------------|---------------|----------------|-------------------------|-------------|--------|--------|----------------------|---------------------------------|

| ANSELB  | —           | —              | ANSB5         | ANSB4          | ANSB3                   | ANSB2       | ANSB1  | ANSB0  | 11 1111              | 11 1111                         |

| CCP1CON | _           | _              | DC1B1         | DC1B0          | CCP1M3                  | CCP1M2      | CCP1M1 | CCP1M0 | 00 0000              | 00 0000                         |

| CCP2CON | _           | _              | DC2B1         | DC2B0          | CCP2M3                  | CCP2M2      | CCP2M1 | CCP2M0 | 00 0000              | 00 0000                         |

| INTCON  | GIE         | PEIE           | T0IE          | INTE           | RBIE                    | T0IF        | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1    | TMR1GIE     | ADIE           | RCIE          | TXIE           | SSPIE                   | CCP1IE      | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1    | TMR1GIF     | ADIF           | RCIF          | TXIF           | SSPIF                   | CCP1IF      | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PORTB   | RB7         | RB6            | RB5           | RB4            | RB3                     | RB2         | RB1    | RB0    | XXXX XXXX            | xxxx xxxx                       |

| TMR1H   | Holding Reg | gister for the | Most Signific | ant Byte of th | he 16-bit TMI           | R1 Register |        |        | XXXX XXXX            | uuuu uuuu                       |

| TMR1L   | Holding Reg | gister for the | Least Signifi | cant Byte of   | the 16-bit TM           | R1 Register |        |        | XXXX XXXX            | uuuu uuuu                       |

| TRISB   | TRISB7      | TRISB6         | TRISB5        | TRISB4         | TRISB3                  | TRISB2      | TRISB1 | TRISB0 | 1111 1111            | 1111 1111                       |

| TRISC   | TRISC7      | TRISC6         | TRISC5        | TRISC4         | TRISC3                  | TRISC2      | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| T1CON   | TMR1CS1     | TMR1CS0        | T1CKPS1       | T1CKPS0        | T1OSCEN                 | T1SYNC      | —      | TMR1ON | 0000 00-0            | uuuu uu-u                       |

| T1GCON  | TMR1GE      | T1GPOL         | T1GTM         | T1GSPM         | T <u>1GGO</u> /<br>DONE | T1GVAL      | T1GSS1 | T1GSS0 | 00x0 0x00            | uuuu uxuu                       |

### TABLE 12-6: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

| U-0             | R/W-0                        | R/W-0            | R/W-0          | R/W-0             | R/W-0           | R/W-0           | R/W-0   |

|-----------------|------------------------------|------------------|----------------|-------------------|-----------------|-----------------|---------|

|                 | TOUTPS3                      | TOUTPS2          | TOUTPS1        | TOUTPS0           | TMR2ON          | T2CKPS1         | T2CKPS0 |

| bit 7           |                              |                  |                |                   |                 |                 | bit 0   |

|                 |                              |                  |                |                   |                 |                 |         |

| Legend:         |                              |                  |                |                   |                 |                 |         |

| R = Readable    | bit                          | W = Writable     | bit            | U = Unimplen      | nented bit, rea | d as '0'        |         |

| -n = Value at P | POR                          | '1' = Bit is set |                | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |

| bit 7           | Unimplemen                   | ted: Read as '   | 0'             |                   |                 |                 |         |

| bit 6-3         | TOUTPS<3:0                   | >: Timer2 Out    | out Postscaler | Select bits       |                 |                 |         |

|                 | 0000 = 1:1 P                 | -                |                |                   |                 |                 |         |

|                 | 0001 = 1:2 P                 | ostscaler        |                |                   |                 |                 |         |

|                 | 0010 = 1:3 P                 | ostscaler        |                |                   |                 |                 |         |

|                 | 0011 = 1:4 P                 |                  |                |                   |                 |                 |         |

|                 | 0100 = 1:5 P                 |                  |                |                   |                 |                 |         |

|                 | 0101 = 1:6 P                 |                  |                |                   |                 |                 |         |

|                 | 0110 = 1:7 P<br>0111 = 1:8 P |                  |                |                   |                 |                 |         |

|                 | 1000 = 1.9 P                 |                  |                |                   |                 |                 |         |

|                 | 1000 = 1.31                  |                  |                |                   |                 |                 |         |

|                 | 1010 = 1:11                  |                  |                |                   |                 |                 |         |

|                 | 1011 = <b>1:12</b>           | Postscaler       |                |                   |                 |                 |         |

|                 | 1100 <b>= 1:13</b>           | Postscaler       |                |                   |                 |                 |         |

|                 | 1101 <b>= 1:14</b>           |                  |                |                   |                 |                 |         |

|                 | 1110 <b>= 1:15</b>           |                  |                |                   |                 |                 |         |

|                 | 1111 = 1:16                  |                  |                |                   |                 |                 |         |

| bit 2           | TMR2ON: Tir                  | ner2 On bit      |                |                   |                 |                 |         |

|                 | 1 = Timer2 is                |                  |                |                   |                 |                 |         |

|                 | 0 = Timer2 is                | s off            |                |                   |                 |                 |         |

| bit 1-0         | T2CKPS<1:0                   | >: Timer2 Cloc   | k Prescale Sel | ect bits          |                 |                 |         |

|                 | 00 = Prescale                |                  |                |                   |                 |                 |         |

|                 | 01 = Prescale                | -                |                |                   |                 |                 |         |

|                 | 1x = Prescale                | er is 16         |                |                   |                 |                 |         |

| TABLE 13-1:     | SUMMAR                       |                  | FRS ASSO       | CIATED WITH       | H TIMER2        |                 |         |

# REGISTER 13-1: T2CON: TIMER2 CONTROL REGISTER

| IADEE  |            |                |               |         |         |        |         |         |                      |                                 |

|--------|------------|----------------|---------------|---------|---------|--------|---------|---------|----------------------|---------------------------------|

| Name   | Bit 7      | Bit 6          | Bit 5         | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| INTCON | GIE        | PEIE           | T0IE          | INTE    | RBIE    | T0IF   | INTF    | RBIF    | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE    | ADIE           | RCIE          | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF    | ADIF           | RCIF          | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| PR2    | Timer2 Mod | dule Period R  | egister       |         |         |        |         |         | 1111 1111            | 1111 1111                       |

| TMR2   | Holding Re | gister for the | 8-bit TMR2 Re | egister |         |        |         |         | 0000 0000            | 0000 0000                       |

| T2CON  | _          | TOUTPS3        | TOUTPS2       | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module. Legend:

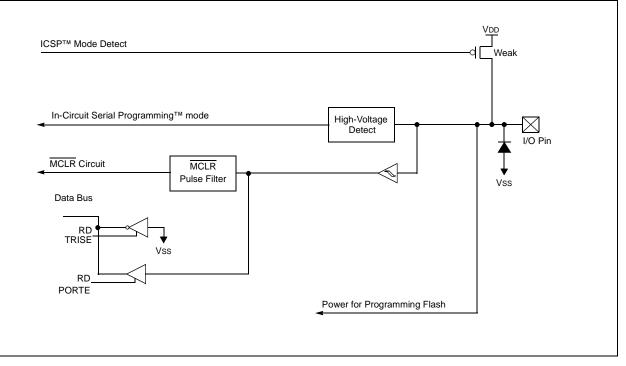

### TABLE 16-1: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name   | Bit 7     | Bit 6       | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-----------|-------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE       | PEIE        | TOIE       | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE   | ADIE        | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF   | ADIF        | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN      | RX9         | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7      | BRG6        | BRG5       | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7    | TRISC6      | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXREG  | AUSART TI | ransmit Dat | a Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA  | CSRC      | TX9         | TXEN       | SYNC   | —      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Asynchronous Transmission.

# 16.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (refer to Section 16.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit of the PIR1 register will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE bit of the PIE1 register was also set.

- 7. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 8. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 9. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

# 16.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (refer to Section 16.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. Enable 9-bit reception by setting the RX9 bit.

- 5. Enable address detection by setting the ADDEN bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit of the PIR1 register will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit of the PIE1 register was also set.

- 8. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

| RX/DT pin                          | Start<br>bit / bit 0 / bit 1 / ( / ybit 7/8/ Stop / bit / bit 0 / ( / ybit 7/8/ Stop / bit / / / ybit 7/8/ Stop                                           |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rcv Shift<br>Reg<br>Rcv Buffer Reg | → → → → → → → → → → → → → → → → → → →                                                                                                                     |

| Read Rcv<br>Buffer Reg –<br>RCREG  |                                                                                                                                                           |

| RCIF<br>(Interrupt Flag)           |                                                                                                                                                           |

| OERR bit _<br>CREN _               |                                                                                                                                                           |

|                                    | timing diagram shows three words appearing on the RX input. The RCREG (receive buffer) is read after the third word, ng the OERR (overrun) bit to be set. |

# FIGURE 16-5: ASYNCHRONOUS RECEPTION

| R/W-0                              | R/W-0                                                                                                 | R/W-0                                                   | R/W-0            | U-0          | R/W-0           | R-1       | R/W-0 |

|------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------|--------------|-----------------|-----------|-------|

| CSRC                               | TX9                                                                                                   | TXEN <sup>(1)</sup>                                     | SYNC             |              | BRGH            | TRMT      | TX9D  |

| bit 7                              |                                                                                                       |                                                         |                  |              |                 |           | bit   |

| Legend:                            |                                                                                                       |                                                         |                  |              |                 |           |       |

| R = Readal                         | ole bit                                                                                               | W = Writable                                            | bit              | U = Unimpler | mented bit, rea | ıd as '0' |       |

| -n = Value at POR '1' = Bit is set |                                                                                                       |                                                         | '0' = Bit is cle |              | x = Bit is unki | nown      |       |

| bit 7                              | Asynchronou<br>Don't care<br>Synchronous<br>1 = Master                                                |                                                         | nerated intern   |              | )               |           |       |

| bit 6                              | <b>TX9:</b> 9-bit Tr<br>1 = Selects                                                                   | ansmit Enable b<br>9-bit transmissi<br>8-bit transmissi | oit<br>on        | ,            |                 |           |       |

| bit 5                              | <b>TXEN:</b> Trans<br>1 = Transmi<br>0 = Transmi                                                      |                                                         | )                |              |                 |           |       |

| bit 4                              | 1 = Synchro                                                                                           | ART Mode Sele<br>mous mode<br>onous mode                | ct bit           |              |                 |           |       |

| bit 3                              | Unimpleme                                                                                             | nted: Read as '                                         | כי               |              |                 |           |       |

| bit 2                              | BRGH: High<br><u>Asynchronou</u><br>1 = High spe<br>0 = Low spe<br><u>Synchronous</u><br>Unused in th | eed<br>eed<br><u>s mode:</u>                            | ect bit          |              |                 |           |       |

| bit 1                              | <b>TRMT:</b> Trans<br>1 = TSR em<br>0 = TSR full                                                      |                                                         | er Status bit    |              |                 |           |       |

| bit 0                              |                                                                                                       | bit of Transmit I<br>ess/data bit or a                  |                  |              |                 |           |       |

# REGISTER 16-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

| Name    | Bit 7       | Bit 6          | Bit 5       | Bit 4        | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on all<br>other Resets |

|---------|-------------|----------------|-------------|--------------|----------|--------|---------|---------|----------------------|------------------------------|

| ANSELA  | —           | —              | ANSA5       | ANSA4        | ANSA3    | ANSA2  | ANSA1   | ANSA0   | 11 1111              | 11 1111                      |

| APFCON  | —           | —              | _           | —            | _        | _      | SSSEL   | CCP2SEL | 00                   | 00                           |

| INTCON  | GIE         | PEIE           | T0IE        | INTE         | RBIE     | T0IF   | INTF    | RBIF    | 0000 000x            | 0000 000x                    |

| PIE1    | TMR1GIE     | ADIE           | RCIE        | TXIE         | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                    |

| PIR1    | TMR1GIF     | ADIF           | RCIF        | TXIF         | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                    |

| PR2     | Timer2 Peri | iod Register   | •           | •            |          |        |         | •       | 1111 1111            | 1111 1111                    |

| SSPBUF  | Synchronou  | us Serial Port | Receive But | fer/Transmit | Register |        |         |         | XXXX XXXX            | uuuu uuuu                    |

| SSPCON  | WCOL        | SSPOV          | SSPEN       | CKP          | SSPM3    | SSPM2  | SSPM1   | SSPM0   | 0000 0000            | 0000 0000                    |

| SSPSTAT | SMP         | CKE            | D/A         | Р            | S        | R/W    | UA      | BF      | 0000 0000            | 0000 0000                    |

| TRISA   | TRISA7      | TRISA6         | TRISA5      | TRISA4       | TRISA3   | TRISA2 | TRISA1  | TRISA0  | 1111 1111            | 1111 1111                    |

| TRISC   | TRISC7      | TRISC6         | TRISC5      | TRISC4       | TRISC3   | TRISC2 | TRISC1  | TRISC0  | 1111 1111            | 1111 1111                    |

| T2CON   | _           | TOUTPS3        | TOUTPS2     | TOUTPS1      | TOUTPS0  | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                    |

# TABLE 17-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode.

# REGISTER 17-5: SSPMSK: SSP MASK REGISTER

| R/W-1                                | R/W-1 | R/W-1 | R/W-1                                   | R/W-1 | R/W-1 | R/W-1 | R/W-1 |  |

|--------------------------------------|-------|-------|-----------------------------------------|-------|-------|-------|-------|--|

| MSK7                                 | MSK6  | MSK5  | MSK4                                    | MSK3  | MSK2  | MSK1  | MSK0  |  |

| bit 7                                |       |       |                                         |       | -     |       | bit   |  |

| Legend:                              |       |       |                                         |       |       |       |       |  |

| R = Readable bit 		 W = Writable bit |       | t     | U = Unimplemented bit, read as '0'      |       |       |       |       |  |

| -n = Value at POR '1' = Bit is set   |       |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |       |  |

|       | 0 = 110 received address bit instructused to detect i C address match                              |

|-------|----------------------------------------------------------------------------------------------------|

| bit 0 | MSK<0>: Mask bit for I <sup>2</sup> C Slave Mode, 10-bit Address                                   |

|       | I <sup>2</sup> C Slave Mode, 10-bit Address (SSPM<3:0> = 0111):                                    |

|       | 1 = The received address bit '0' is compared to SSPADD<0> to detect I <sup>2</sup> C address match |

|       | $0 =$ The received address bit '0' is not used to detect $1^2$ C address match                     |

|       | All other SSP modes: this bit has no effect.                                                       |

|       |                                                                                                    |

# REGISTER 17-6: SSPADD: SSP I<sup>2</sup>C ADDRESS REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ADD7  | ADD6  | ADD5  | ADD4  | ADD3  | ADD2  | ADD1  | ADD0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

|       |       |       |       |       |       |       |       |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | ʻ0'                |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-0 **ADD<7:0>:** Address bits Received address

# TABLE 17-7: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

| Name                  | Bit 7                                                                                     | Bit 6              | Bit 5  | Bit 4  | Bit 3  | Bit 2     | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|-------------------------------------------------------------------------------------------|--------------------|--------|--------|--------|-----------|-----------|-----------|----------------------|---------------------------------|

| INTCON                | GIE                                                                                       | PEIE               | TOIE   | INTE   | RBIE   | TOIF      | INTF      | RBIF      | x000 0000x           | 0000 000u                       |

| PIR1                  | TMR1GIF                                                                                   | ADIF               | RCIF   | TXIF   | SSPIF  | CCP1IF    | TMR2IF    | TMR1IF    | 0000 0000            | 0000 0000                       |

| PIE1                  | TMR1GIE                                                                                   | ADIE               | RCIE   | TXIE   | SSPIE  | CCP1IE    | TMR2IE    | TMR1IE    | 0000 0000            | 0000 0000                       |

| SSPBUF                | Synchronous Serial Port Receive Buffer/Transmit Register                                  |                    |        |        |        |           | xxxx xxxx | uuuu uuuu |                      |                                 |

| SSPADD                | Synchronous Serial Port (I <sup>2</sup> C mode) Address Register 0000 000                 |                    |        |        |        | 0000 0000 | 0000 0000 |           |                      |                                 |

| SSPCON                | WCOL                                                                                      | SSPOV              | SSPEN  | CKP    | SSPM3  | SSPM2     | SSPM1     | SSPM0     | 0000 0000            | 0000 0000                       |

| SSPMSK <sup>(2)</sup> | Synchronous Serial Port (I <sup>2</sup> C mode) Address Mask Register 1111 1111 1111 1111 |                    |        |        |        | 1111 1111 |           |           |                      |                                 |

| SSPSTAT               | SMP <sup>(1)</sup>                                                                        | CKE <sup>(1)</sup> | D/A    | Р      | S      | R/W       | UA        | BF        | 0000 0000            | 0000 0000                       |

| TRISC                 | TRISC7                                                                                    | TRISC6             | TRISC5 | TRISC4 | TRISC3 | TRISC2    | TRISC1    | TRISC0    | 1111 1111            | 1111 1111                       |

| المسمسيان             |                                                                                           |                    |        |        |        |           |           |           |                      | 1 1 2 2                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in I<sup>2</sup>C mode.

**Note 1:** Maintain these bits clear in  $I^2C$  mode.

**2:** Accessible only when SSPM<3:0> = 1001.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                      |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                                                                                                             |

| Description:     | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.<br>If the result is '1', the next instruction is executed. If the result is '0', then a NOP is executed instead, making it a 2-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                     |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                          |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a 2-cycle<br>instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                    |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                       |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                       |

| Description:     | GOTO is an unconditional branch.<br>The 11-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>2-cycle instruction. |

| IORLW            | Inclusive OR literal with W                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                              |

| Operands:        | $0 \leq k \leq 255$                                                                                                   |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                          |

| Status Affected: | Z                                                                                                                     |

| Description:     | The contents of the W register are<br>OR'ed with the 8-bit literal 'k'. The<br>result is placed in the<br>W register. |

| INCF             | Increment f                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                            |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        |

| Status Affected: | Z                                                                                                                                                                          |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                                         |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                          |  |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                    |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |  |  |

| PIC16LF722/3/4/6/7<br>PIC16F722/3/4/6/7 |        |                                                        |                          |                                                      |                          |                  |                                                                                                                                                                                                                                                              |  |  |

|-----------------------------------------|--------|--------------------------------------------------------|--------------------------|------------------------------------------------------|--------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                         |        |                                                        |                          | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                          |                  |                                                                                                                                                                                                                                                              |  |  |

| Param.<br>No.                           | Sym.   | Characteristic                                         | Min.                     | Тур†                                                 | Max.                     | Units            | Conditions                                                                                                                                                                                                                                                   |  |  |

| D001                                    | Vdd    | Supply Voltage                                         |                          |                                                      |                          |                  |                                                                                                                                                                                                                                                              |  |  |

|                                         |        | PIC16LF722/3/4/6/7                                     | 1.8<br>1.8<br>2.3<br>2.5 |                                                      | 3.6<br>3.6<br>3.6<br>3.6 | V<br>V<br>V<br>V | Fosc $\leq$ 16 MHz: HFINTOSC, EC<br>Fosc $\leq$ 4 MHz<br>Fosc $\leq$ 20 MHz, EC<br>Fosc $\leq$ 20 MHz, HS                                                                                                                                                    |  |  |

| D001                                    |        | PIC16F722/3/4/6/7                                      | 1.8<br>1.8<br>2.3<br>2.5 |                                                      | 5.5<br>5.5<br>5.5<br>5.5 | V<br>V<br>V<br>V | Fosc $\leq$ 16 MHz: HFINTOSC, EC<br>Fosc $\leq$ 4 MHz<br>Fosc $\leq$ 20 MHz, EC<br>Fosc $\leq$ 20 MHz, HS                                                                                                                                                    |  |  |

| D002*                                   | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>              |                          |                                                      |                          |                  |                                                                                                                                                                                                                                                              |  |  |

|                                         |        | PIC16LF722/3/4/6/7                                     | 1.5                      |                                                      | _                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |  |

| D002*                                   |        | PIC16F722/3/4/6/7                                      | 1.7                      | _                                                    | _                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |  |

|                                         | VPOR*  | Power-on Reset Release Voltage                         | _                        | 1.6                                                  | _                        | V                |                                                                                                                                                                                                                                                              |  |  |

|                                         | VPORR* | Power-on Reset Rearm Voltage                           |                          |                                                      |                          |                  |                                                                                                                                                                                                                                                              |  |  |

|                                         |        | PIC16LF722/3/4/6/7                                     | _                        | 0.8                                                  | _                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |  |

|                                         |        | PIC16F722/3/4/6/7                                      |                          | 1.7                                                  | —                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |  |

| D003                                    | Vfvr   | Fixed Voltage Reference Voltage,<br>Initial Accuracy   | -8<br>-8<br>-8           | <br>                                                 | 6<br>6<br>6              | %<br>%<br>%      | $ \begin{array}{l} {\sf VFVR} = 1.024{\sf V},  {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 2.048{\sf V},  {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 4.096{\sf V},  {\sf VDD} \geq 4.75{\sf V}; \\ {\sf -40} \leq {\sf TA} \leq 85^{\circ}{\sf C} \end{array} $ |  |  |

|                                         |        |                                                        | -8<br>-8<br>-8           |                                                      | 6<br>6<br>6              | %<br>%<br>%      | $ \begin{array}{l} V{\sf FVR} = 1.024V, \ V{\sf DD} \geq 2.5V \\ V{\sf FVR} = 2.048V, \ V{\sf DD} \geq 2.5V \\ V{\sf FVR} = 4.096V, \ V{\sf DD} \geq 4.75V; \\ -40 \leq {\sf TA} \leq 125^{\circ}{\sf C} \end{array} $                                       |  |  |

| D004*                                   | SVDD   | VDD Rise Rate to ensure internal Power-on Reset signal | 0.05                     | —                                                    | —                        | V/ms             | See Section 3.2 "Power-on Reset (POR)" for details.                                                                                                                                                                                                          |  |  |

# 23.1 DC Characteristics: PIC16(L)F722/3/4/6/7-I/E (Industrial, Extended)

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

#### 23.5 **Thermal Considerations**

| Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |           |                                        |      |       |                                                          |  |

|--------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------|------|-------|----------------------------------------------------------|--|

| Param<br>No.                                                                                                             | Sym.      | Characteristic                         | Тур. | Units | Conditions                                               |  |

| TH01                                                                                                                     | θJA       | Thermal Resistance Junction to Ambient | 60   | °C/W  | 28-pin SPDIP package                                     |  |

|                                                                                                                          |           |                                        | 80   | °C/W  | 28-pin SOIC package                                      |  |

|                                                                                                                          |           |                                        | 90   | °C/W  | 28-pin SSOP package                                      |  |

|                                                                                                                          |           |                                        | 27.5 | °C/W  | 28-pin UQFN 4x4mm package                                |  |

|                                                                                                                          |           |                                        | 27.5 | °C/W  | 28-pin QFN 6x6mm package                                 |  |

|                                                                                                                          |           |                                        | 47.2 | °C/W  | 40-pin PDIP package                                      |  |

|                                                                                                                          |           |                                        | 46   | °C/W  | 44-pin TQFP package                                      |  |

|                                                                                                                          |           |                                        | 24.4 | °C/W  | 44-pin QFN 8x8mm package                                 |  |

| TH02 0JC                                                                                                                 | θJC       | Thermal Resistance Junction to Case    | 31.4 | °C/W  | 28-pin SPDIP package                                     |  |

|                                                                                                                          |           |                                        | 24   | °C/W  | 28-pin SOIC package                                      |  |

|                                                                                                                          |           |                                        | 24   | °C/W  | 28-pin SSOP package                                      |  |

|                                                                                                                          |           |                                        | 24   | °C/W  | 28-pin UQFN 4x4mm package                                |  |

|                                                                                                                          |           |                                        | 24   | °C/W  | 28-pin QFN 6x6mm package                                 |  |

|                                                                                                                          |           |                                        | 24.7 | °C/W  | 40-pin PDIP package                                      |  |

|                                                                                                                          |           |                                        | 14.5 | °C/W  | 44-pin TQFP package                                      |  |

|                                                                                                                          |           |                                        | 20   | °C/W  | 44-pin QFN 8x8mm package                                 |  |

| TH03                                                                                                                     | Тјмах     | Maximum Junction Temperature           | 150  | °C    |                                                          |  |

| TH04                                                                                                                     | PD        | Power Dissipation                      | _    | W     | PD = PINTERNAL + PI/O                                    |  |

| TH05                                                                                                                     | PINTERNAL | Internal Power Dissipation             | _    | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |  |

| TH06                                                                                                                     | Pi/o      | I/O Power Dissipation                  | _    | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |  |

| TH07                                                                                                                     | Pder      | Derated Power                          | _    | W     | Pder = PDmax (Tj - Ta)/θja <sup>(2)</sup>                |  |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

**2:** TA = Ambient Temperature

**3:** T<sub>J</sub> = Junction Temperature

#### TABLE 23-2: **OSCILLATOR PARAMETERS**

| Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |          |                                                          |                    |      |      |      |       |                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------|--------------------|------|------|------|-------|---------------------------------------------------------------------------------------|

| Param<br>No.                                                                                                             | Sym.     | Characteristic                                           | Freq.<br>Tolerance | Min. | Тур† | Max. | Units | Conditions                                                                            |