Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 14x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf727t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### PIC16(L)F72X Family Types

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data SRAM<br>(bytes) | High-Endurance Flash<br>Memory (bytes) | I/O's <sup>(2)</sup> | 8-bit ADC (ch) | CapSense (ch) | Timers<br>(8/16-bit) | AUSART | SSP (I <sup>2</sup> C/SPI) | ССР | Debug <sup>(1)</sup> | ХГР |

|---------------|------------------|---------------------------------|----------------------|----------------------------------------|----------------------|----------------|---------------|----------------------|--------|----------------------------|-----|----------------------|-----|

| PIC16(L)F707  | (1)              | 8192                            | 363                  | 0                                      | 36                   | 14             | 32            | 4/2                  | 1      | 1                          | 2   |                      | Y   |

| PIC16(L)F720  | (2)              | 2048                            | 128                  | 128                                    | 18                   | 12             | _             | 2/1                  | 1      | 1                          | 1   | I                    | Y   |

| PIC16(L)F721  | (2)              | 4096                            | 256                  | 128                                    | 18                   | 12             | _             | 2/1                  | 1      | 1                          | 1   | I                    | Y   |

| PIC16(L)F722  | (4)              | 2048                            | 128                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | -                    | Y   |

| PIC16(L)F722A | (3)              | 2048                            | 128                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

| PIC16(L)F723  | (4)              | 4096                            | 192                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | Ι                    | Y   |

| PIC16(L)F723A | (3)              | 4096                            | 192                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | -                    | Y   |

| PIC16(L)F724  | (4)              | 4096                            | 192                  | 0                                      | 36                   | 14             | 16            | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

| PIC16(L)F726  | (4)              | 8192                            | 368                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | Ι                    | Y   |

| PIC16(L)F727  | (4)              | 8192                            | 368                  | 0                                      | 36                   | 14             | 16            | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

**Note 1:** I - Debugging, Integrated on Chip; H - Debugging, Requires Debug Header.

2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

- 1: DS41418 PIC16(L)F707 Data Sheet, 40/44-Pin Flash, 8-bit Microcontrollers

- 2: DS41430 PIC16(L)F720/721 Data Sheet, 20-Pin Flash, 8-bit Microcontrollers

- 3: DS41417 PIC16(L)F722A/723A Data Sheet, 28-Pin Flash, 8-bit Microcontrollers

- 4: DS41341 PIC16(L)F72X Data Sheet, 28/40/44-Pin Flash, 8-bit Microcontrollers

# 1.0 DEVICE OVERVIEW

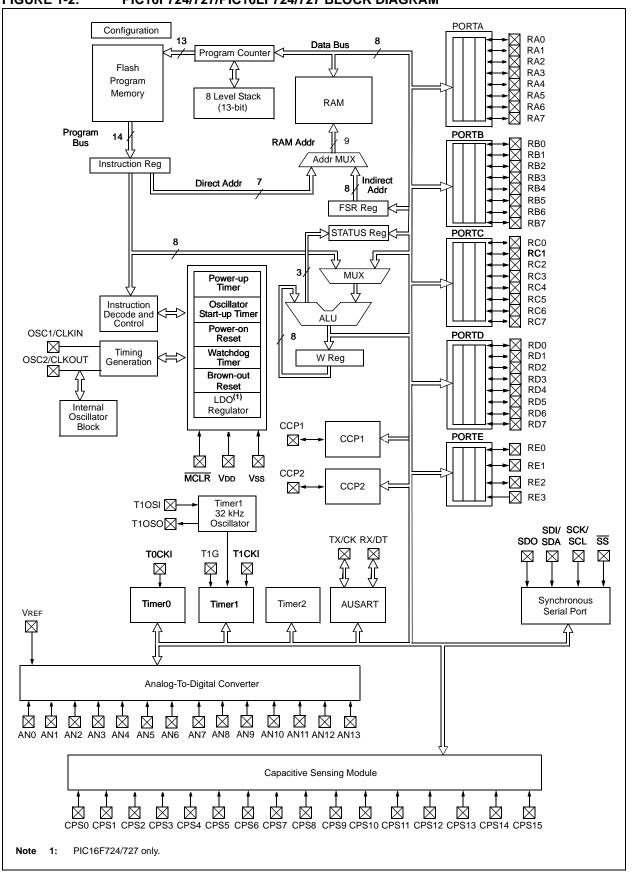

The PIC16(L)F722/3/4/6/7 devices are covered by this data sheet. They are available in 28/40/44-pin packages. Figure 1-1 shows a block diagram of the PIC16F722/723/726/PIC16LF722/723/726 devices and Figure 1-2 shows a block diagram of the PIC16F724/727/PIC16LF724/727 devices. Table 1-1 shows the pinout descriptions.

FIGURE 1-2: PIC16F724/727/PIC16LF724/727 BLOCK DIAGRAM

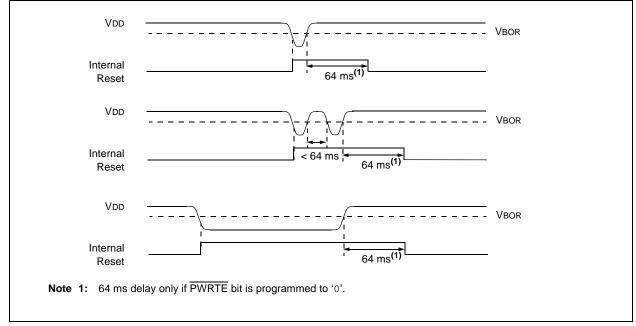

#### 3.5 Brown-Out Reset (BOR)

Brown-out Reset is enabled by programming the BOREN<1:0> bits in the Configuration register. The brown-out trip point is selectable from two trip points via the BORV bit in the Configuration register.

Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

Two bits are used to enable the BOR. When BOREN = 11, the BOR is always enabled. When BOREN = 10, the BOR is enabled, but disabled during Sleep. When BOREN = 0X, the BOR is disabled.

If VDD falls below VBOR for greater than parameter (TBOR) (see **Section 23.0** "**Electrical Specifica-tions**"), the brown-out situation will reset the device. This will occur regardless of VDD slew rate. A Reset is not ensured to occur if VDD falls below VBOR for more than TBOR.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

**Note:** When erasing Flash program memory, the BOR is forced to enabled at the minimum BOR setting to ensure that any code protection circuitry is operating properly.

#### FIGURE 3-3: BROWN-OUT SITUATIONS

#### 4.5.2 PIE1 REGISTER

The PIE1 register contains the interrupt enable bits, as shown in Register 4-2.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|---------|-------|-------|-------|-------|--------|--------|--------|

| TMR1GIE | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE |

| bit 7   |       |       |       |       |        |        | bit 0  |

| Legend:          |                                                                                        |                          |                    |

|------------------|----------------------------------------------------------------------------------------|--------------------------|--------------------|

| R = Readable b   | w = Writable bit                                                                       | U = Unimplemented bit,   | read as '0'        |

| -n = Value at PO | OR '1' = Bit is set                                                                    | '0' = Bit is cleared     | x = Bit is unknown |

|                  |                                                                                        |                          |                    |

| oit 7            | TMR1GIE: Timer1 Gate Interrupt En                                                      |                          |                    |

|                  | 1 = Enable the Timer1 Gate Acquis<br>0 = Disable the Timer1 Gate Acquis                |                          |                    |

| bit 6            | ADIE: A/D Converter (ADC) Interrup                                                     | pt Enable bit            |                    |

|                  | <ul><li>1 = Enables the ADC interrupt</li><li>0 = Disables the ADC interrupt</li></ul> |                          |                    |

| bit 5            | RCIE: USART Receive Interrupt En                                                       | able bit                 |                    |

|                  | 1 = Enables the USART receive inte                                                     |                          |                    |

|                  | 0 = Disables the USART receive int                                                     | terrupt                  |                    |

| bit 4            | TXIE: USART Transmit Interrupt Er                                                      | hable bit                |                    |

|                  | 1 = Enables the USART transmit in<br>0 = Disables the USART transmit in                | •                        |                    |

| bit 3            | SSPIE: Synchronous Serial Port (S                                                      | SP) Interrupt Enable bit |                    |

|                  | 1 = Enables the SSP interrupt<br>0 = Disables the SSP interrupt                        |                          |                    |

| bit 2            | <b>CCP1IE:</b> CCP1 Interrupt Enable bit                                               |                          |                    |

|                  | 1 = Enables the CCP1 interrupt                                                         |                          |                    |

|                  | 0 = Disables the CCP1 interrupt                                                        |                          |                    |

| bit 1            | TMR2IE: TMR2 to PR2 Match Inter                                                        | rupt Enable bit          |                    |

|                  | 1 = Enables the Timer2 to PR2 mat                                                      |                          |                    |

|                  | 0 = Disables the Timer2 to PR2 ma                                                      | tch interrupt            |                    |

| bit 0            | TMR1IE: Timer1 Overflow Interrupt                                                      | Enable bit               |                    |

|                  | 1 = Enables the Timer1 overflow int                                                    | •                        |                    |

|                  | 0 = Disables the Timer1 overflow in                                                    | terrupt                  |                    |

#### REGISTER 6-17: ANSELE: PORTE ANALOG SELECT REGISTER

| U-0             | U-0 | U-0              | U-0 | U-0                  | R/W-1                | R/W-1                | R/W-1                |  |  |

|-----------------|-----|------------------|-----|----------------------|----------------------|----------------------|----------------------|--|--|

| —               | _   |                  | _   | _                    | ANSE2 <sup>(2)</sup> | ANSE1 <sup>(2)</sup> | ANSE0 <sup>(2)</sup> |  |  |

| bit 7           |     |                  |     |                      |                      |                      | bit 0                |  |  |

|                 |     |                  |     |                      |                      |                      |                      |  |  |

| Legend:         |     |                  |     |                      |                      |                      |                      |  |  |

| R = Readable    | bit | W = Writable     | bit | U = Unimpler         |                      |                      |                      |  |  |

| -n = Value at F | POR | '1' = Bit is set |     | '0' = Bit is cleared |                      |                      | x = Bit is unknown   |  |  |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 **ANSE<2:0>:** Analog Select between Analog or Digital Function on Pins RE<2:0>, respectively 0 = Digital I/O. Pin is assigned to port or Digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital Input buffer disabled.

2: ANSELE register is not implemented on the PIC16F722/723/726/PIC16LF722/723/726. Read as '0'

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3                 | Bit 2                 | Bit 1                 | Bit 0                 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-------|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|----------------------|---------------------------------|

| ADCON0 |       |       | CHS3  | CHS2  | CHS1                  | CHS0                  | GO/DONE               | ADON                  | 00 0000              | 00 0000                         |

| ANSELE | _     |       | _     | _     | _                     | ANSE2                 | ANSE1                 | ANSE0                 | 111                  | 111                             |

| PORTE  | _     | _     | _     | _     | RE3                   | RE2                   | RE1                   | RE0                   | xxxx                 | xxxx                            |

| TRISE  | _     |       | _     | _     | TRISE3 <sup>(2)</sup> | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> | 1111                 | 1111                            |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE

Note 1: These registers are not implemented on the PIC16F722/723/726/PIC16LF722/723/726 devices, read as '0'.

**2:** This bit is always '1' as RE3 is input only.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

# PIC16(L)F722/3/4/6/7

| REGISTER      | <b>19-2.</b> ADCO              |                        | ITROL REG        |                    |                    |                  |        |

|---------------|--------------------------------|------------------------|------------------|--------------------|--------------------|------------------|--------|

| U-0           | R/W-0                          | R/W-0                  | R/W-0            | U-0                | U-0                | R/W-0            | R/W-0  |

| _             | ADCS2                          | ADCS1                  | ADCS0            | _                  | _                  | ADREF1           | ADREF0 |

| bit 7         |                                |                        |                  |                    |                    |                  | bit 0  |

| Legend:       |                                |                        |                  |                    |                    |                  |        |

| R = Readabl   | le bit                         | W = Writable bi        | t                | U = Unimpleme      | ented bit, read as | s 'O'            |        |

| -n = Value at | t POR                          | '1' = Bit is set       |                  | '0' = Bit is clear | red                | x = Bit is unkno | wn     |

|               |                                |                        |                  |                    |                    |                  |        |

| bit 7         | Unimplemente                   | ed: Read as '0'        |                  |                    |                    |                  |        |

| bit 6-4       | ADCS<2:0>: A                   | /D Conversion C        | lock Select bits |                    |                    |                  |        |

|               | 000 = Fosc/2                   |                        |                  |                    |                    |                  |        |

|               | 001 = Fosc/8                   |                        |                  |                    |                    |                  |        |

|               | 010 = Fosc/32                  | -                      |                  |                    |                    |                  |        |

|               | · · ·                          | ock supplied from      | a dedicated RC   | Coscillator)       |                    |                  |        |

|               | 100 = Fosc/4<br>101 = Fosc/16  |                        |                  |                    |                    |                  |        |

|               | 101 = FOSC/10<br>110 = FOSC/64 | -                      |                  |                    |                    |                  |        |

|               |                                | ,<br>ock supplied from | a dedicated RC   | coscillator)       |                    |                  |        |

| bit 3-2       | Unimplemente                   | ••                     |                  | ,                  |                    |                  |        |

| bit 1-0       | ADREF<1:0>:                    | Voltage Referend       | e Configuration  | bits               |                    |                  |        |

|               |                                | connected to VDD       | 0                |                    |                    |                  |        |

|               | 10 = VREF is c                 | connected to exte      | rnal VREF (RA3   | /AN3)              |                    |                  |        |

|               |                                |                        | nal Fixed Voltag |                    |                    |                  |        |

### REGISTER 9-2: ADCON1: A/D CONTROL REGISTER 1

#### REGISTER 9-3: ADRES: ADC RESULT REGISTER

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 | ADRES1 | ADRES0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

bit 7-0 **ADRES<7:0>**: ADC Result Register bits 8-bit conversion result.

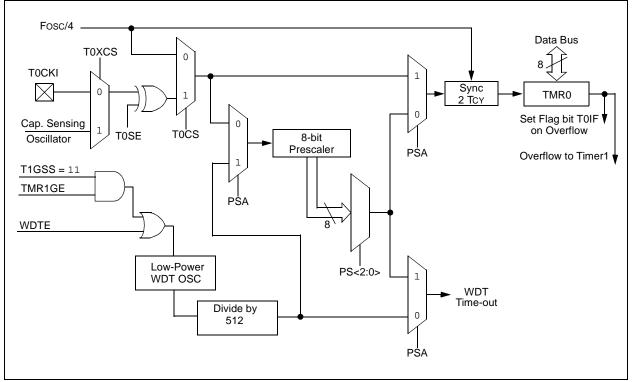

# 11.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (shared with Watchdog Timer)

- Programmable internal or external clock source

- Programmable external clock edge selection

- Interrupt on overflow

- TMR0 can be used to gate Timer1

Figure 11-1 is a block diagram of the Timer0 module.

# 11.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 11.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-Bit Timer mode is selected by clearing the T0CS bit of the OPTION register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

**Note:** The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

#### 11.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin or the Capacitive Sensing Oscillator (CPSOSC) signal.

8-Bit Counter mode using the T0CKI pin is selected by setting the T0CS bit in the OPTION register to '1' and resetting the T0XCS bit in the CPSCON0 register to '0'.

8-Bit Counter mode using the Capacitive Sensing Oscillator (CPSOSC) signal is selected by setting the TOCS bit in the OPTION register to '1' and setting the T0XCS bit in the CPSCON0 register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the T0SE bit in the OPTION register.

#### FIGURE 11-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

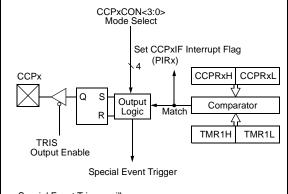

### 15.2 Compare Mode

In Compare mode, the 16-bit CCPRx register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCPx module may:

- Toggle the CCPx output

- Set the CCPx output

- Clear the CCPx output

- Generate a Special Event Trigger

- Generate a Software Interrupt

The action on the pin is based on the value of the CCPxM<3:0> control bits of the CCPxCON register.

All Compare modes can generate an interrupt.

#### FIGURE 15-2: COMPARE MODE OPERATION BLOCK DIAGRAM

- Special Event Trigger will:

- Clear TMR1H and TMR1L registers.

- NOT set interrupt flag bit TMR1IF of the PIR1 register.

Set the GO/DONE bit to start the ADC conversion

- (CCP2 only).

#### 15.2.1 CCPx PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

Either RC1 or RB3 can be selected as the CCP2 pin. Refer to **Section 6.1** "Alternate Pin Function" for more information.

| Note: | Clearing the CCPxCON register will force    |

|-------|---------------------------------------------|

|       | the CCPx compare output latch to the        |

|       | default low level. This is not the PORT I/O |

|       | data latch.                                 |

#### 15.2.2 TIMER1 MODE SELECTION

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode. Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. For the Compare operation of the TMR1 register to the CCPRx register to occur, Timer1 must be clocked from the Instruction Clock (Fosc/4) or from an external clock source.

#### 15.2.3 SOFTWARE INTERRUPT MODE

When Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPxIF bit in the PIRx register is set and the CCPx module does not assert control of the CCPx pin (refer to the CCPxCON register).

#### 15.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is chosen (CCPxM<3:0> = 1011), the CCPx module does the following:

- Resets Timer1

- Starts an ADC conversion if ADC is enabled (CCP2 only)

The CCPx module does not assert control of the CCPx pin in this mode (refer to the CCPxCON register).

The Special Event Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPRxH, CCPRxL register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. This allows the CCPRxH, CCPRxL register pair to effectively provide a 16-bit programmable period register for Timer1.

Note 1: The Special Event Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

2: Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Special Event Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

#### 15.2.5 COMPARE DURING SLEEP

The Compare Mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

| Name    | Bit 7                                                                       | Bit 6          | Bit 5          | Bit 4          | Bit 3                   | Bit 2    | Bit 1   | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-----------------------------------------------------------------------------|----------------|----------------|----------------|-------------------------|----------|---------|-----------|----------------------|---------------------------------|

| ADCON0  | _                                                                           |                | CHS3           | CHS2           | CHS1                    | CHS0     | GO/DONE | ADON      | 00 0000              | 00 0000                         |

| ANSELB  | _                                                                           | _              | ANSB5          | ANSB4          | ANSB3                   | ANSB2    | ANSB1   | ANSB0     | 11 1111              | 11 1111                         |

| APFCON  | _                                                                           | _              | _              | _              | _                       | _        | SSSEL   | CCP2SEL   | 00                   | 00                              |

| CCP1CON | _                                                                           | _              | DC1B1          | DC1B0          | CCP1M3                  | CCP1M2   | CCP1M1  | CCP1M0    | 00 0000              | 00 0000                         |

| CCP2CON | _                                                                           | _              | DC2B1          | DC2B0          | CCP2M3                  | CCP2M2   | CCP2M1  | CCP2M0    | 00 0000              | 00 0000                         |

| CCPRxL  | Capture/Com                                                                 | npare/PWM R    | egister X Lov  | v Byte         |                         |          |         |           | xxxx xxxx            | uuuu uuuu                       |

| CCPRxH  | Capture/Compare/PWM Register X High Byte                                    |                |                |                |                         |          |         | xxxx xxxx | uuuu uuuu            |                                 |

| INTCON  | GIE                                                                         | PEIE           | TOIE           | INTE           | RBIE                    | T0IF     | INTF    | RBIF      | 0000 000x            | 0000 000x                       |

| PIE1    | TMR1GIE                                                                     | ADIE           | RCIE           | TXIE           | SSPIE                   | CCP1IE   | TMR2IE  | TMR1IE    | 0000 0000            | 0000 0000                       |

| PIE2    | —                                                                           | -              | —              | -              | —                       | —        | —       | CCP2IE    | 0                    | 0                               |

| PIR1    | TMR1GIF                                                                     | ADIF           | RCIF           | TXIF           | SSPIF                   | CCP1IF   | TMR2IF  | TMR1IF    | 0000 0000            | 0000 0000                       |

| PIR2    | —                                                                           | -              | —              | -              | —                       | —        | —       | CCP2IF    | 0                    | 0                               |

| T1CON   | TMR1CS1                                                                     | TMR1CS0        | T1CKPS1        | T1CKPS0        | T1OSCEN                 | T1SYNC   | _       | TMR10N    | 0000 00-0            | uuuu uu-u                       |

| T1GCON  | TMR1GE                                                                      | T1GPOL         | T1GTM          | T1GSPM         | T <u>1GGO</u> /<br>DONE | T1GVAL   | T1GSS1  | T1GSS0    | 0000 0x00            | 00x0 0x00                       |

| TMR1L   | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                |                |                |                         |          |         |           |                      | uuuu uuuu                       |

| TMR1H   | Holding Regi                                                                | ster for the M | ost Significar | nt Byte of the | 16-bit TMR1 F           | Register |         |           | xxxx xxxx            | uuuu uuuu                       |

| TRISB   | TRISB7                                                                      | TRISB6         | TRISB5         | TRISB4         | TRISB3                  | TRISB2   | TRISB1  | TRISB0    | 1111 1111            | 1111 1111                       |

| TRISC   | TRISC7                                                                      | TRISC6         | TRISC5         | TRISC4         | TRISC3                  | TRISC2   | TRISC1  | TRISC0    | 1111 1111            | 1111 1111                       |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Compare.

|        |                   | <b>SYNC</b> = 0, <b>BRGH</b> = 0 |                             |                   |            |                             |                    |            |                             |                    |            |                             |  |

|--------|-------------------|----------------------------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 20.000 MHz |                                  |                             | Fosc = 18.432 MHz |            |                             | Fosc = 16.0000 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |  |

| RATE   | Actual<br>Rate    | %<br>Error                       | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    |                   | _                                | _                           |                   | _          | _                           |                    | —          | —                           |                    | _          | _                           |  |

| 1200   | 1221              | 1.73                             | 255                         | 1200              | 0.00       | 239                         | 1201               | 0.08       | 207                         | 1200               | 0.00       | 143                         |  |

| 2400   | 2404              | 0.16                             | 129                         | 2400              | 0.00       | 119                         | 2403               | 0.16       | 103                         | 2400               | 0.00       | 71                          |  |

| 9600   | 9470              | -1.36                            | 32                          | 9600              | 0.00       | 29                          | 9615               | 0.16       | 25                          | 9600               | 0.00       | 17                          |  |

| 10417  | 10417             | 0.00                             | 29                          | 10286             | -1.26      | 27                          | 10416              | -0.01      | 23                          | 10165              | -2.42      | 16                          |  |

| 19.2k  | 19.53k            | 1.73                             | 15                          | 19.20k            | 0.00       | 14                          | 19.23k             | 0.16       | 12                          | 19.20k             | 0.00       | 8                           |  |

| 57.6k  | _                 | —                                | _                           | 57.60k            | 0.00       | 7                           | _                  | —          | _                           | 57.60k             | 0.00       | 2                           |  |

| 115.2k | —                 | _                                | —                           | _                 | _          | —                           | _                  | —          | —                           | _                  | _          | —                           |  |

#### TABLE 16-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        |                  | <b>SYNC</b> = 0, <b>BRGH</b> = 0 |                             |                  |            |                             |                   |            |                             |                  |            |                             |  |

|--------|------------------|----------------------------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 8.000 MHz |                                  |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |  |

| RATE   | Actual<br>Rate   | %<br>Error                       | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | _                | _                                | _                           | 300              | 0.16       | 207                         | 300               | 0.00       | 191                         | 300              | 0.16       | 51                          |  |

| 1200   | 1202             | 0.16                             | 103                         | 1202             | 0.16       | 51                          | 1200              | 0.00       | 47                          | 1202             | 0.16       | 12                          |  |

| 2400   | 2404             | 0.16                             | 51                          | 2404             | 0.16       | 25                          | 2400              | 0.00       | 23                          | —                | _          | _                           |  |

| 9600   | 9615             | 0.16                             | 12                          | _                | _          | _                           | 9600              | 0.00       | 5                           | —                | _          | _                           |  |

| 10417  | 10417            | 0.00                             | 11                          | 10417            | 0.00       | 5                           | —                 | _          | _                           | —                | _          | _                           |  |

| 19.2k  | _                | _                                | _                           | —                | _          | _                           | 19.20k            | 0.00       | 2                           | —                | _          | _                           |  |

| 57.6k  | —                | _                                | —                           | —                | _          | —                           | 57.60k            | 0.00       | 0                           | —                | _          | —                           |  |

| 115.2k |                  | —                                | —                           |                  | —          | —                           |                   | _          | —                           |                  | —          | —                           |  |

| BAUD   | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 16.0000 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |

|--------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| RATE   | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | —                 |            | _                           |                   | _          | _                           | _                  | —          | _                           | —                  | —          | —                           |

| 1200   | —                 | —          | —                           | —                 | —          | —                           | —                  | —          | —                           | —                  | —          | —                           |

| 2400   | —                 | _          | _                           | _                 | _          | _                           | _                  | _          | _                           | —                  | —          | _                           |

| 9600   | 9615              | 0.16       | 129                         | 9600              | 0.00       | 119                         | 9615               | 0.16       | 103                         | 9600               | 0.00       | 71                          |

| 10417  | 10417             | 0.00       | 119                         | 10378             | -0.37      | 110                         | 10417              | 0.00       | 95                          | 10473              | 0.53       | 65                          |

| 19.2k  | 19.23k            | 0.16       | 64                          | 19.20k            | 0.00       | 59                          | 19.23k             | 0.16       | 51                          | 19.20k             | 0.00       | 35                          |

| 57.6k  | 56.82k            | -1.36      | 21                          | 57.60k            | 0.00       | 19                          | 58.8k              | 2.12       | 16                          | 57.60k             | 0.00       | 11                          |

| 115.2k | 113.64k           | -1.36      | 10                          | 115.2k            | 0.00       | 9                           | _                  | _          | _                           | 115.2k             | 0.00       | 5                           |

## 16.4 AUSART Operation During Sleep

The AUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 16.4.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (refer to Section 16.3.2.4 "Synchronous Slave Reception Setup:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE global interrupt enable bit of the INTCON register is also set, then the Interrupt Service Routine at address 0004h will be called.

#### 16.4.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Transmission (refer to Section 16.3.2.2 "Synchronous Slave Transmission Setup:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE global interrupt enable bit is also set then the Interrupt Service Routine at address 0004h will be called.

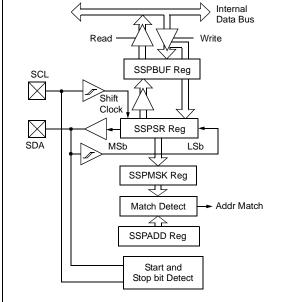

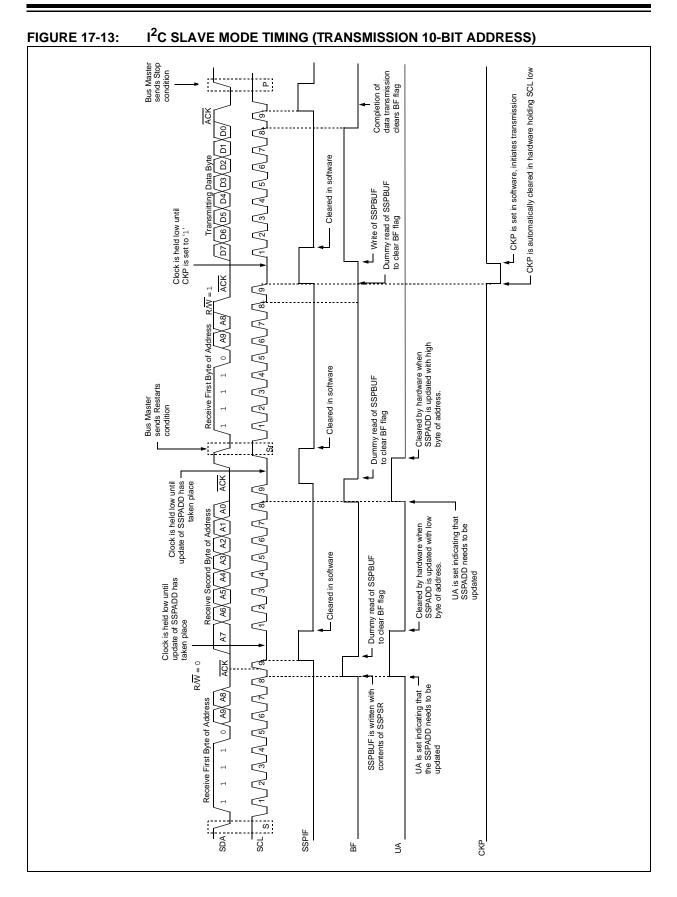

# 17.2 I<sup>2</sup>C Mode

The SSP module, in  $I^2C$  mode, implements all slave functions, except general call support. It provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the  $I^2C$  Standard mode specifications:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- Start and Stop bit interrupts enabled to support firmware Master mode

- Address masking

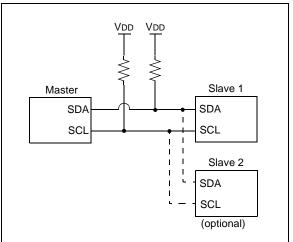

Two pins are used for data transfer; the SCL pin (clock line) and the SDA pin (data line). The user must configure the two pin's data direction bits as inputs in the appropriate TRIS register. Upon enabling  $I^2C$  mode, the  $I^2C$  slew rate limiters in the I/O pads are controlled by the SMP bit of SSPSTAT register. The SSP module functions are enabled by setting the SSPEN bit of SSPCON register.

Data is sampled on the rising edge and shifted out on the falling edge of the clock. This ensures that the SDA signal is valid during the SCL high time. The SCL clock input must have minimum high and low times for proper operation. Refer to **Section 23.0** "**Electrical Specifications**".

# FIGURE 17-7: I<sup>2</sup>C MODE BLOCK DIAGRAM

# FIGURE 17-8: TYPICAL I<sup>2</sup>C

#### CONNECTIONS

The SSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. They are:

- SSP Control (SSPCON) register

- SSP Status (SSPSTAT) register

- Serial Receive/Transmit Buffer (SSPBUF) register

- SSP Shift Register (SSPSR), not directly accessible

- SSP Address (SSPADD) register

- SSP Address Mask (SSPMSK) register

#### 17.2.1 HARDWARE SETUP

Selection of  $I^2C$  mode, with the SSPEN bit of the SSPCON register set, forces the SCL and SDA pins to be open drain, provided these pins are programmed as inputs by setting the appropriate TRISC bits. The SSP module will override the input state with the output data, when required, such as for Acknowledge and slave-transmitter sequences.

**Note:** Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module

PIC16(L)F722/3/4/6/7

#### REGISTER 18-1: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

| R-1      | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/S-0 |

|----------|-----|-----|-----|-----|-----|-----|-------|

| Reserved | —   | —I  | —   | —   | —   | —   | RD    |

| bit 7    |     |     |     |     |     |     | bit 0 |

|          |     |     |     |     |     |     |       |

| Legend:           |                  | S = Setable bit, cleared in h | ardware            |

|-------------------|------------------|-------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea    | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared          | x = Bit is unknown |

bit 6-1 Unimplemented: Read as '0'

bit 0 RD: Read Control bit

1 = Initiates an program memory read (The RD is cleared in hardware; the RD bit can only be set (not cleared) in software).

0 = Does not initiate a program memory read

#### REGISTER 18-2: PMDATH: PROGRAM MEMORY DATA HIGH REGISTER

| U-0      | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|----------|-----|-------|-------|-------|-------|-------|-------|

| —        | —   | PMD13 | PMD12 | PMD11 | PMD10 | PMD9  | PMD8  |

| bit 7    |     |       |       |       |       |       | bit 0 |

|          |     |       |       |       |       |       |       |

| l egend. |     |       |       |       |       |       |       |

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **PMD<13:8>:** The value of the program memory word pointed to by PMADRH and PMADRL after a program memory read command.

#### REGISTER 18-3: PMDATL: PROGRAM MEMORY DATA LOW REGISTER

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PMD7  | PMD6  | PMD5  | PMD4  | PMD3  | PMD2  | PMD1  | PMD0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 **PMD<7:0>:** The value of the program memory word pointed to by PMADRH and PMADRL after a program memory read command.

#### 23.2 DC Characteristics: PIC16(L)F722/3/4/6/7-I/E (Industrial, Extended) (Continued)

| PIC16LF7          | 722/3/4/6/7                         |      |                                         |      |       |            |                                                                                                      |  |  |

|-------------------|-------------------------------------|------|-----------------------------------------|------|-------|------------|------------------------------------------------------------------------------------------------------|--|--|

| PIC16F722/3/4/6/7 |                                     |      |                                         |      |       |            | ess otherwise stated)<br>$x \le +85^{\circ}$ C for industrial<br>$x \le +125^{\circ}$ C for extended |  |  |

| Param             | Device                              | Min. | Typt                                    | Max. | Units | Conditions |                                                                                                      |  |  |

| No.               | Characteristics                     |      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |      |       | Vdd        | Note                                                                                                 |  |  |

|                   | Supply Current (IDD) <sup>(1,</sup> | 2)   |                                         |      |       |            |                                                                                                      |  |  |

| D014              |                                     | _    | 290                                     | 330  | μA    | 1.8        | Fosc = 4 MHz                                                                                         |  |  |

|                   |                                     | _    | 460                                     | 500  | μA    | 3.0        | EC Oscillator mode                                                                                   |  |  |

| D014              |                                     |      | 300                                     | 430  | μA    | 1.8        | Fosc = 4 MHz                                                                                         |  |  |

|                   |                                     |      | 450                                     | 655  | μA    | 3.0        | EC Oscillator mode (Note 5)                                                                          |  |  |

|                   |                                     | —    | 500                                     | 730  | μΑ    | 5.0        |                                                                                                      |  |  |

| D015              |                                     | _    | 100                                     | 130  | μA    | 1.8        | Fosc = 500 kHz                                                                                       |  |  |

|                   |                                     | _    | 120                                     | 150  | μA    | 3.0        | MFINTOSC mode                                                                                        |  |  |

| D015              |                                     | _    | 115                                     | 195  | μA    | 1.8        | Fosc = 500 kHz                                                                                       |  |  |

|                   |                                     | _    | 135                                     | 200  | μΑ    | 3.0        | MFINTOSC mode (Note 5)                                                                               |  |  |

|                   |                                     | —    | 150                                     | 220  | μA    | 5.0        |                                                                                                      |  |  |

| D016              |                                     | _    | 650                                     | 800  | μΑ    | 1.8        | Fosc = 8 MHz                                                                                         |  |  |

|                   |                                     |      | 1000                                    | 1200 | μA    | 3.0        | HFINTOSC mode                                                                                        |  |  |

| D016              |                                     | _    | 625                                     | 850  | μA    | 1.8        | Fosc = 8 MHz                                                                                         |  |  |

|                   |                                     | _    | 1000                                    | 1200 | μA    | 3.0        | HFINTOSC mode (Note 5)                                                                               |  |  |

|                   |                                     | —    | 1100                                    | 1500 | μA    | 5.0        |                                                                                                      |  |  |

| D017              |                                     |      | 1.0                                     | 1.2  | mA    | 1.8        | Fosc = 16 MHz                                                                                        |  |  |

|                   |                                     |      | 1.5                                     | 1.85 | mA    | 3.0        | HFINTOSC mode                                                                                        |  |  |

| D017              |                                     | _    | 1                                       | 1.2  | mA    | 1.8        | Fosc = 16 MHz                                                                                        |  |  |

|                   |                                     | _    | 1.5                                     | 1.7  | mA    | 3.0        | HFINTOSC mode (Note 5)                                                                               |  |  |

|                   |                                     | —    | 1.7                                     | 2.1  | mA    | 5.0        |                                                                                                      |  |  |

| D018              |                                     | _    | 210                                     | 240  | μA    | 1.8        | Fosc = 4 MHz                                                                                         |  |  |

|                   |                                     | _    | 340                                     | 380  | μA    | 3.0        | EXTRC mode (Note 3, Note 5)                                                                          |  |  |

| D018              |                                     | _    | 225                                     | 320  | μA    | 1.8        | Fosc = 4 MHz                                                                                         |  |  |

|                   |                                     |      | 360                                     | 445  | μA    | 3.0        | EXTRC mode (Note 3, Note 5)                                                                          |  |  |

|                   |                                     | —    | 410                                     | 650  | μA    | 5.0        |                                                                                                      |  |  |

| D019              |                                     |      | 1.6                                     | 1.9  | mA    | 3.0        | Fosc = 20 MHz                                                                                        |  |  |

|                   |                                     |      | 2.0                                     | 2.8  | mA    | 3.6        | HS Oscillator mode                                                                                   |  |  |

| D019              |                                     | _    | 1.6                                     | 2    | mA    | 3.0        | Fosc = 20 MHz                                                                                        |  |  |

|                   | —                                   |      | 1.9                                     | 3.2  | mA    | 5.0        | HS Oscillator mode (Note 5)                                                                          |  |  |

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

4: FVR and BOR are disabled.

5: 0.1 μF capacitor on VCAP (RA0).

# 23.6 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| 2. Tpp3 |                                      |     |                |

|---------|--------------------------------------|-----|----------------|

| т       |                                      |     |                |

| F       | Frequency                            | Т   | Time           |

| Lowerc  | ase letters (pp) and their meanings: |     |                |

| рр      |                                      |     |                |

| сс      | CCP1                                 | osc | OSC1           |

| ck      | CLKOUT                               | rd  | RD             |

| CS      | CS                                   | rw  | RD or WR       |

| di      | SDI                                  | sc  | SCK            |

| do      | SDO                                  | SS  | SS             |

| dt      | Data in                              | tO  | TOCKI          |

| io      | I/O PORT                             | t1  | T1CKI          |

| mc      | MCLR                                 | wr  | WR             |

| Upperc  | ase letters and their meanings:      |     |                |

| S       |                                      |     |                |

| F       | Fall                                 | Р   | Period         |

| н       | High                                 | R   | Rise           |

| I       | Invalid (High-impedance)             | V   | Valid          |

| L       | Low                                  | Z   | High-impedance |

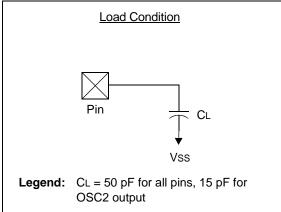

#### FIGURE 23-2: LOAD CONDITIONS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |          |                                                              |               |          |          |       |                              |  |

|----------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------|---------------|----------|----------|-------|------------------------------|--|

| Param<br>No.                                                                                                         | Sym.     | Characteristic                                               | Min.          | Тур†     | Max.     | Units | Conditions                   |  |

| OS11                                                                                                                 | TosH2ckL | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                              | _             |          | 70       | ns    | VDD = 3.3-5.0V               |  |

| OS12                                                                                                                 | TosH2ckH | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                              | —             |          | 72       | ns    | VDD = 3.3-5.0V               |  |

| OS13                                                                                                                 | TckL2ioV | CLKOUT↓ to Port out valid <sup>(1)</sup>                     | —             | _        | 20       | ns    |                              |  |

| OS14                                                                                                                 | TioV2ckH | Port input valid before CLKOUT <sup>(1)</sup>                | Tosc + 200 ns |          | _        | ns    |                              |  |

| OS15                                                                                                                 | TosH2ioV | Fosc↑ (Q1 cycle) to Port out valid                           | —             | 50       | 70*      | ns    | VDD = 3.3-5.0V               |  |

| OS16                                                                                                                 | TosH2iol | Fosc↑ (Q2 cycle) to Port input invalid<br>(I/O in hold time) | 50            | —        | —        | ns    | VDD = 3.3-5.0V               |  |

| OS17                                                                                                                 | TioV2osH | Port input valid to Fosc↑ (Q2 cycle)<br>(I/O in setup time)  | 20            | —        | _        | ns    |                              |  |

| OS18                                                                                                                 | TioR     | Port output rise time <sup>(2)</sup>                         |               | 40<br>15 | 72<br>32 | ns    | VDD = 2.0V<br>VDD = 3.3-5.0V |  |

| OS19                                                                                                                 | TioF     | Port output fall time <sup>(2)</sup>                         |               | 28<br>15 | 55<br>30 | ns    | VDD = 2.0V<br>VDD = 3.3-5.0V |  |

| OS20*                                                                                                                | Tinp     | INT pin input high or low time                               | 25            | —        | —        | ns    |                              |  |

| OS21*                                                                                                                | Trbp     | PORTB interrupt-on-change new input level time               | Тсү           | —        | —        | ns    |                              |  |

#### TABLE 23-3: CLKOUT AND I/O TIMING PARAMETERS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

**Note 1:** Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

2: Includes OSC2 in CLKOUT mode.

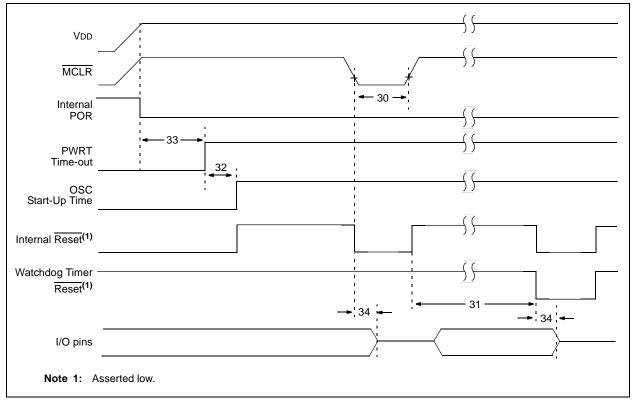

# FIGURE 23-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

#### TABLE 23-7: PIC16F722/3/4/6/7 A/D CONVERTER (ADC) CHARACTERISTICS:

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                                   |      |      |      |       |                                                                     |  |

|----------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------|------|------|------|-------|---------------------------------------------------------------------|--|

| Param<br>No.                                                                                                         | Sym. | Characteristic                                    | Min. | Тур† | Max. | Units | Conditions                                                          |  |

| AD01                                                                                                                 | Nr   | Resolution                                        | —    | _    | 8    | bit   |                                                                     |  |

| AD02                                                                                                                 | EIL  | Integral Error                                    | —    |      | ±1.7 | LSb   | VREF = 3.0V                                                         |  |

| AD03                                                                                                                 | Edl  | Differential Error                                | -    | —    | ±1   | LSb   | No missing codes<br>VREF = 3.0V                                     |  |

| AD04                                                                                                                 | EOFF | Offset Error                                      | —    |      | ±2.2 | LSb   | VREF = 3.0V                                                         |  |

| AD05                                                                                                                 | Egn  | Gain Error                                        | _    | _    | ±1.5 | LSb   | VREF = 3.0V                                                         |  |

| AD06                                                                                                                 | VREF | Reference Voltage <sup>(3)</sup>                  | 1.8  | _    | Vdd  | V     |                                                                     |  |

| AD07                                                                                                                 | VAIN | Full-Scale Range                                  | Vss  | —    | VREF | V     |                                                                     |  |

| AD08                                                                                                                 | ZAIN | Recommended Impedance of<br>Analog Voltage Source | -    | _    | 50   | kΩ    | Can go higher if external 0.01µF capacitor is present on input pin. |  |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Total Absolute Error includes integral, differential, offset and gain errors.

- 2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

- 3: When ADC is off, it will not consume any current other than leakage current. The power-down current specification includes any such leakage from the ADC module.

#### TABLE 23-8: PIC16F722/3/4/6/7 A/D CONVERSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)         Operating temperature       -40°C ≤ TA ≤ +125°C |                                                  |                                                                 |            |         |            |          |                                          |  |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------|------------|---------|------------|----------|------------------------------------------|--|

| Param<br>No.                                                                                                    | Sym Characteristic Min Typt Max Units Conditions |                                                                 |            |         |            |          |                                          |  |

| AD130*                                                                                                          | Tad                                              | A/D Clock Period<br>A/D Internal RC Oscillator<br>Period        | 1.0<br>1.0 | <br>2.0 | 9.0<br>6.0 | μs<br>μs | Tosc-based<br>ADCS<1:0> = 11 (ADRC mode) |  |

| AD131                                                                                                           | TCNV                                             | Conversion Time (not including Acquisition Time) <sup>(1)</sup> | _          | 10.5    | —          | Tad      | Set GO/DONE bit to conversion complete   |  |

| AD132*                                                                                                          | TACQ                                             | Acquisition Time                                                | —          | 1.0     | _          | μS       |                                          |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The ADRES register may be read on the following TCY cycle.

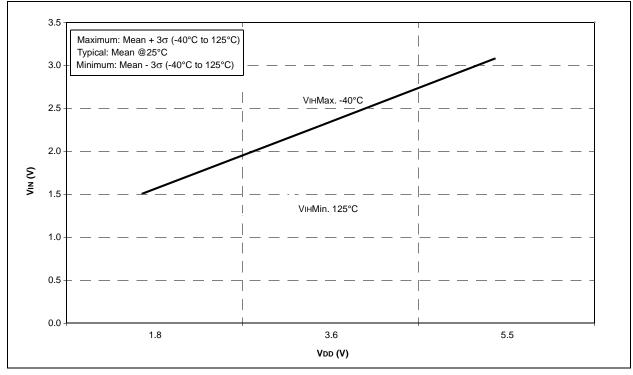

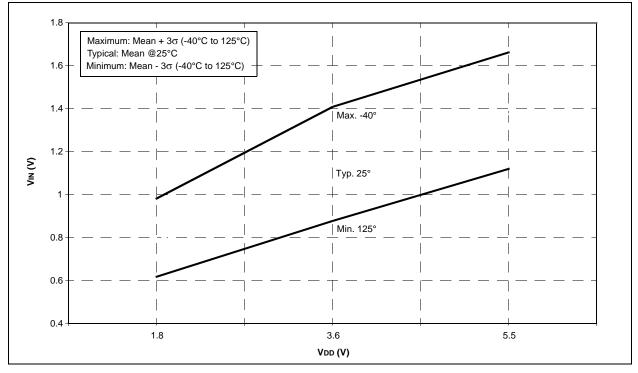

#### FIGURE 24-49: TTL INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE