Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

Ξ·ΧΕΙ

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

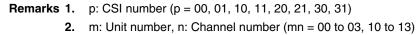

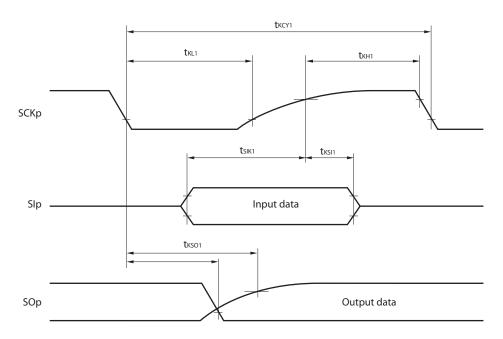

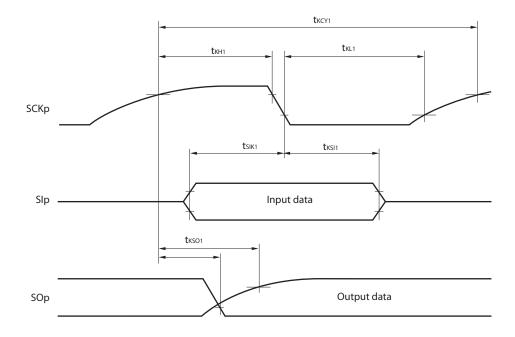

| Connectivity               | CSI, I <sup>2</sup> C, LINbus, UART/USART                                       |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 48                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 4K x 8                                                                          |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 5.5V                                                                     |

| Data Converters            | A/D 12x8/10b                                                                    |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f100leafa-v0 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

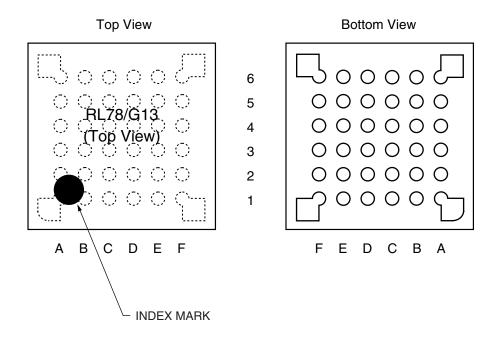

# 1.3.6 36-pin products

• 36-pin plastic WFLGA (4 × 4 mm, 0.5 mm pitch)

|   | А                         | В                              | С                                                 | D                                                     | E                   | F                   | _ |

|---|---------------------------|--------------------------------|---------------------------------------------------|-------------------------------------------------------|---------------------|---------------------|---|

|   | P60/SCLA0                 | Vdd                            | P121/X1                                           | P122/X2/EXCLK                                         | P137/INTP0          | P40/TOOL0           |   |

| 6 |                           |                                |                                                   |                                                       |                     |                     | 6 |

|   | P62                       | P61/SDAA0                      | Vss                                               | REGC                                                  | RESET               | P120/ANI19          |   |

| 5 |                           |                                |                                                   |                                                       |                     |                     | 5 |

| 4 | P72/SO21                  | P71/SI21/<br>SDA21             | P14/RxD2/SI20/<br>SDA20/(SCLA0)<br>/(TI03)/(TO03) | P31/TI03/TO03/<br>INTP4/<br>PCLBUZ0                   | P00/TI00/TxD1       | P01/TO00/RxD1       | 4 |

| 3 | P50/INTP1/<br>SI11/SDA11  | P70/SCK21/<br>SCL21            | P15/PCLBUZ1/<br>SCK20/SCL20/<br>(TI02)/(TO02)     | P22/ANI2                                              | P20/ANI0/<br>AVrefp | P21/ANI1/<br>AVREFM | 3 |

| 2 | P30/INTP3/<br>SCK11/SCL11 | P16/TI01/TO01/<br>INTP5/(RxD0) | P12/SO00/<br>TxD0/TOOLTxD<br>/(TI05)/(TO05)       | P11/SI00/RxD0/<br>TOOLRxD/<br>SDA00/(TI06)/<br>(TO06) | P24/ANI4            | P23/ANI3            | 2 |

| 1 | P51/INTP2/<br>SO11        | P17/TI02/TO02/<br>(TxD0)       | P13/TxD2/<br>SO20/(SDAA0)/<br>(TI04)/(TO04)       | P10/SCK00/<br>SCL00/(TI07)/<br>(TO07)                 | P147/ANI18          | P25/ANI5            | 1 |

|   | А                         | В                              | С                                                 | D                                                     | E                   | F                   |   |

#### Caution Connect the REGC pin to Vss via a capacitor (0.47 to 1 $\mu$ F).

Remarks 1. For pin identification, see 1.4 Pin Identification.

Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR). Refer to Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR) in the RL78/G13 User's Manual.

# 1.6 Outline of Functions

[20-pin, 24-pin, 25-pin, 30-pin, 32-pin, 36-pin products]

Caution This outline describes the functions at the time when Peripheral I/O redirection register (PIOR) is set to 00H.

|                      | Item                                                                                                                                                                                                                                                                            | 20-p                                                                         | oin                                                                                                                          | 24-                                              | pin                                      | 25                                                       | -pin                                                                    | 30-                                                                                                                | pin                 | 32-                                                        | pin                 | (1/2<br>36-                                   | pin                |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------|---------------------|-----------------------------------------------|--------------------|--|

|                      |                                                                                                                                                                                                                                                                                 | , ד                                                                          | Ъ                                                                                                                            | Я                                                | גר                                       | д                                                        | גר                                                                      | Ъ                                                                                                                  | דג                  | Ъ                                                          | ភ្ល                 | Ъ                                             |                    |  |

|                      |                                                                                                                                                                                                                                                                                 | 5F1                                                                          | 5F1                                                                                                                          | 5F10                                             | 5F10                                     | 5F10                                                     | 5F10                                                                    | 5F10                                                                                                               | 5F10                | 5F10                                                       | 5F10                | 5F10                                          | 5F1(               |  |

|                      |                                                                                                                                                                                                                                                                                 | R5F1006x                                                                     | R5F1016x                                                                                                                     | R5F1007x                                         | R5F1017x                                 | R5F1008x                                                 | R5F1018x                                                                | R5F100Ax                                                                                                           | R5F101Ax            | R5F100Bx                                                   | R5F101Bx            | R5F100Cx                                      | R5F101Cx           |  |

| Code flash me        | emory (KB)                                                                                                                                                                                                                                                                      | 16 to                                                                        | 64                                                                                                                           | 16 t                                             | o 64                                     | 161                                                      | o 64                                                                    | 16 to                                                                                                              | 128                 |                                                            | 128                 | 16 to                                         | 128                |  |

| Data flash me        | emory (KB)                                                                                                                                                                                                                                                                      | 4                                                                            | _                                                                                                                            | 4                                                | _                                        | 4                                                        | _                                                                       | 4 to 8                                                                                                             | _                   | 4 to 8                                                     | _                   | 4 to 8                                        | -                  |  |

| RAM (KB)             |                                                                                                                                                                                                                                                                                 | 2 to 4                                                                       | Note1                                                                                                                        | 2 to                                             | 4 <sup>Note1</sup>                       | 2 to                                                     | 4 <sup>Note1</sup>                                                      | 2 to <sup>-</sup>                                                                                                  | 12 <sup>Note1</sup> | 2 to 1                                                     | 2 <sup>Note1</sup>  | 2 to <sup>-</sup>                             | 2 <sup>Note1</sup> |  |

| Address spac         | e                                                                                                                                                                                                                                                                               | 1 MB                                                                         |                                                                                                                              | •                                                |                                          | L                                                        |                                                                         |                                                                                                                    |                     |                                                            |                     |                                               |                    |  |

| Main system<br>clock | High-speed system<br>clock                                                                                                                                                                                                                                                      | HS (High<br>HS (High<br>LS (Low                                              | n-speed<br>n-speed<br>-speed                                                                                                 | l main) m<br>l main) m<br>main) m                | node: 1 t<br>node: 1 t<br>ode: 1 to      | o 20 MH<br>o 16 MH<br>o 8 MHz                            | Iz (V <sub>DD</sub> =<br>Iz (V <sub>DD</sub> =<br>(V <sub>DD</sub> = 1. | system clock input (EXCLK)<br>DD = 2.7 to 5.5 V),<br>DD = 2.4 to 5.5 V),<br>= 1.8 to 5.5 V),<br>DD = 1.6 to 5.5 V) |                     |                                                            |                     |                                               |                    |  |

|                      | High-speed on-chip oscillator                                                                                                                                                                                                                                                   | HS (High<br>HS (High<br>LS (Low-<br>LV (Low-                                 | n-speed<br>-speed                                                                                                            | l main) m<br>main) m                             | node: 1 f<br>ode: 1 f                    | to 16 MH<br>to 8 MHz                                     | Iz (Vdd =<br>2 (Vdd = 1                                                 | 2.4 to 5<br>1.8 to 5.5                                                                                             | .5 V),<br>5 V),     |                                                            |                     |                                               |                    |  |

| Subsystem cl         | ock                                                                                                                                                                                                                                                                             |                                                                              |                                                                                                                              |                                                  |                                          |                                                          |                                                                         |                                                                                                                    |                     |                                                            |                     |                                               |                    |  |

| Low-speed or         | n-chip oscillator                                                                                                                                                                                                                                                               | 15 kHz (                                                                     | TYP.)                                                                                                                        |                                                  |                                          |                                                          |                                                                         |                                                                                                                    |                     |                                                            |                     |                                               |                    |  |

| General-purp         | ose registers                                                                                                                                                                                                                                                                   | (8-bit reg                                                                   | gister ×                                                                                                                     | 8) × 4 ba                                        | anks                                     |                                                          |                                                                         |                                                                                                                    |                     |                                                            |                     |                                               |                    |  |

| Minimum inst         | ruction execution time                                                                                                                                                                                                                                                          | 0.03125                                                                      | μs (Hig                                                                                                                      | h-speed                                          | on-chip                                  | oscillato                                                | or: fін = 3                                                             | 2 MHz o                                                                                                            | peration            | eration)                                                   |                     |                                               |                    |  |

|                      |                                                                                                                                                                                                                                                                                 | 0.05 μs (                                                                    | (High-sp                                                                                                                     | beed sys                                         | tem cloo                                 | ck: fмx =                                                | f <sub>MX</sub> = 20 MHz operation)                                     |                                                                                                                    |                     |                                                            |                     |                                               |                    |  |

| Instruction set      |                                                                                                                                                                                                                                                                                 | <ul> <li>Data ti</li> <li>Adder</li> <li>Multipli</li> <li>Rotate</li> </ul> | and su<br>lication                                                                                                           | btractor/<br>(8 bits ×                           | logical o<br>8 bits)                     |                                                          |                                                                         |                                                                                                                    | t, and B            | oolean o                                                   | peration            | ), etc.                                       |                    |  |

| I/O port             | Total                                                                                                                                                                                                                                                                           | 16                                                                           | ;                                                                                                                            | 2                                                | 0                                        | 2                                                        | 21                                                                      | 2                                                                                                                  | 6                   | 2                                                          | 8                   | 3                                             | 2                  |  |

|                      | CMOS I/O                                                                                                                                                                                                                                                                        | 13<br>(N-ch O<br>[V₀₀ with<br>voltage                                        | .D. I/O<br>nstand                                                                                                            | (N-ch C                                          | thstand                                  | (N-ch (<br>[V <sub>DD</sub> w                            | 5<br>D.D. I/O<br>thstand<br>ge]: 6)                                     | 2<br>(N-ch C<br>[V⊳⊳ wi<br>voltag                                                                                  | D.D. I/O<br>thstand | 2<br>(N-ch C<br>[V <sub>DD</sub> wi <sup>*</sup><br>voltag | D.D. I/O<br>thstand | 2<br>(N-ch C<br>[V <sub>DD</sub> wi<br>voltag | D.D. I/C           |  |

|                      | CMOS input                                                                                                                                                                                                                                                                      | 3                                                                            |                                                                                                                              | :                                                | 3                                        |                                                          | 3                                                                       | :                                                                                                                  | 3                   | 3                                                          | 3                   | 3                                             | 3                  |  |

|                      | CMOS output                                                                                                                                                                                                                                                                     | -                                                                            |                                                                                                                              | -                                                | -                                        |                                                          | 1                                                                       | -                                                                                                                  | -                   | -                                                          | -                   | -                                             | -                  |  |

|                      | N-ch O.D. I/O<br>(withstand voltage: 6 V)                                                                                                                                                                                                                                       | -                                                                            |                                                                                                                              | 2                                                | 2                                        |                                                          | 2                                                                       | 2                                                                                                                  | 2                   | 3                                                          | 3                   | 3                                             | 3                  |  |

| Timer                | 16-bit timer                                                                                                                                                                                                                                                                    |                                                                              |                                                                                                                              |                                                  |                                          |                                                          | 8 cha                                                                   | nnels                                                                                                              |                     |                                                            |                     |                                               |                    |  |

|                      | Watchdog timer                                                                                                                                                                                                                                                                  |                                                                              |                                                                                                                              |                                                  |                                          |                                                          | 1 cha                                                                   | nnel                                                                                                               |                     |                                                            |                     |                                               |                    |  |

|                      | Real-time clock (RTC)                                                                                                                                                                                                                                                           |                                                                              |                                                                                                                              |                                                  |                                          |                                                          | 1 chan                                                                  | nel Note 2                                                                                                         |                     |                                                            |                     |                                               |                    |  |

|                      | 12-bit interval timer (IT)                                                                                                                                                                                                                                                      |                                                                              |                                                                                                                              |                                                  |                                          |                                                          | 1 cha                                                                   | nnel                                                                                                               |                     |                                                            |                     |                                               |                    |  |

|                      | Timer output     3 channels     4 channels     4 channels     4 channels (PWM outputs: 3 <sup>Note 3</sup> ),       (PWM outputs:     (PWM outputs: 3 <sup>Note 3</sup> )     8 channels (PWM outputs: 7 <sup>Note 3</sup> )     8 channels (PWM outputs: 7 <sup>Note 3</sup> ) |                                                                              |                                                                                                                              |                                                  |                                          |                                                          |                                                                         |                                                                                                                    |                     |                                                            |                     |                                               |                    |  |

|                      | RTC output                                                                                                                                                                                                                                                                      |                                                                              |                                                                                                                              | •                                                |                                          |                                                          |                                                                         | -                                                                                                                  |                     |                                                            |                     |                                               |                    |  |

| Notes 1.             | The flash library us<br>The target products<br>R5F100xD, R5F<br>R5F100xE, R5F<br>For the RAM areas<br><b>for RL78 Family (I</b><br>Only the constant                                                                                                                            | s and sta<br>101xD (:<br>101xE ()<br>used by<br><b>R20UT29</b>               | $\begin{array}{l} \text{rt addr} \\ x = 6 \text{ to} \\ x = 6 \text{ to} \\ \text{r the flate} \\ \textbf{944}. \end{array}$ | ress of t<br>o 8, A to<br>o 8, A to<br>ash libra | he RAN<br>o C): S<br>o C): S<br>ury, see | A areas<br>Start add<br>Start add<br>Start add<br>Self R | used by<br>dress Ff<br>dress Ff<br>AM list                              | y the fla<br>F300H<br>EF00H<br><b>of Flas</b>                                                                      | sh libra<br>h Self- | ry are s<br><b>Progra</b> i                                | hown b<br>mming     | Library                                       |                    |  |

<sup>2.</sup> Only the constant-period interrupt function when the low-speed on-chip oscillator clock (fiL) is selected

[40-pin, 44-pin, 48-pin, 52-pin, 64-pin products]

#### Caution This outline describes the functions at the time when Peripheral I/O redirection register (PIOR) is set to 00H.

|                      | lt a sa                                          | 40                                                   |                                                                                     |                                                  |                                        | 40                                               |                                                                                                                     | 50                             |                                        | (1/2                               | /                   |  |  |

|----------------------|--------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------|------------------------------------|---------------------|--|--|

|                      | Item                                             | 40-                                                  |                                                                                     | 44-                                              | pin                                    |                                                  | pin                                                                                                                 | 52-                            | pin                                    | İ                                  | pin                 |  |  |

|                      |                                                  | R5F100Ex                                             | R5F101Ex                                                                            | R5F100Fx                                         | R5F101Fx                               | R5F100Gx                                         | R5F101Gx                                                                                                            | R5F100Jx                       | R5F101Jx                               | R5F100Lx                           | R5F101Lx            |  |  |

| Code flash m         | nemory (KB)                                      | 16 to                                                | o 192                                                                               | 16 t                                             | o 512                                  | 16 t                                             | o 512                                                                                                               | 32 to                          | o 512                                  | 32 to                              | 512                 |  |  |

| Data flash m         | emory (KB)                                       | 4 to 8                                               | _                                                                                   | 4 to 8                                           | -                                      | 4 to 8                                           | _                                                                                                                   | 4 to 8                         | _                                      | 4 to 8                             | -                   |  |  |

| RAM (KB)             |                                                  | 2 to 1                                               | 16 <sup>Note1</sup>                                                                 | 2 to 3                                           | 32 <sup>Note1</sup>                    | 2 to 3                                           | 32 <sup>Note1</sup>                                                                                                 | 2 to 3                         | 32 <sup>Note1</sup>                    | ation), etc.                       | 2 <sup>Note1</sup>  |  |  |

| Address spa          | ce                                               | 1 MB                                                 |                                                                                     |                                                  |                                        |                                                  |                                                                                                                     |                                |                                        |                                    |                     |  |  |

| Main system<br>clock | High-speed system clock                          | HS (High<br>HS (High<br>LS (Low-                     | -speed m<br>-speed m<br>speed ma                                                    | ain) mode<br>ain) mode<br>in) mode:              | 1 to 20 l<br>1 to 16 l<br>1 to 8 M     | MHz (Vdd =<br>MHz (Vdd =<br>Hz (Vdd =            | system clock input (EXCLK)<br>pp = 2.7 to 5.5 V),<br>pp = 2.4 to 5.5 V),<br>p = 1.8 to 5.5 V),<br>p = 1.6 to 5.5 V) |                                |                                        |                                    |                     |  |  |

|                      | High-speed on-chip<br>oscillator                 | HS (High<br>LS (Low-                                 | -speed m<br>speed ma                                                                | ain) mode<br>ain) mode<br>in) mode:<br>ain) mode | 1 to 16 M<br>1 to 8 M                  | MHz (Vdd =<br>Hz (Vdd =                          | = 2.4 to 5.5<br>1.8 to 5.5                                                                                          | 5 V),<br>V),                   | ),                                     |                                    |                     |  |  |

| Subsystem c          | lock                                             | XT1 (crys<br>32.768 k                                | ,                                                                                   | ation, exte                                      | rnal subsy                             | /stem cloc                                       | k input (E)                                                                                                         | KCLKS)                         |                                        |                                    |                     |  |  |

| Low-speed o          | n-chip oscillator                                | 15 kHz (                                             | ΓYP.)                                                                               |                                                  |                                        |                                                  |                                                                                                                     |                                |                                        |                                    |                     |  |  |

| General-purp         | burpose registers (8-bit register × 8) × 4 banks |                                                      |                                                                                     |                                                  |                                        |                                                  |                                                                                                                     |                                |                                        |                                    |                     |  |  |

| Minimum ins          | truction execution time                          | 0.03125                                              | 0.03125 $\mu$ s (High-speed on-chip oscillator: f <sub>IH</sub> = 32 MHz operation) |                                                  |                                        |                                                  |                                                                                                                     |                                |                                        |                                    |                     |  |  |

|                      |                                                  | 0.05 <i>μ</i> s (                                    | High-spee                                                                           | ed system                                        | clock: f <sub>MX</sub>                 | = 20 MHz                                         | operation)                                                                                                          |                                |                                        |                                    |                     |  |  |

|                      |                                                  | 30.5 μs (                                            | Subsyster                                                                           | n clock: fs                                      | ив = 32.76                             | 8 kHz ope                                        | ration)                                                                                                             |                                |                                        |                                    |                     |  |  |

| Instruction se       | ət                                               | <ul><li>Adder</li><li>Multipl</li></ul>              | ication (8                                                                          | actor/logic<br>bits $\times$ 8 bit               | s)                                     |                                                  |                                                                                                                     | and Boole                      | ean opera                              | tion), etc.                        |                     |  |  |

| I/O port             | Total                                            | 0                                                    | 36                                                                                  | 4                                                | 10                                     | 4                                                | 14                                                                                                                  | 2                              | 18                                     | 5                                  | 8                   |  |  |

|                      | CMOS I/O                                         | (N-ch (<br>[V <sub>DD</sub> wi                       | 28<br>D.D. I/O<br>ithstand<br>je]: 10)                                              | (N-ch (<br>[V <sub>DD</sub> w                    | 31<br>D.D. I/O<br>ithstand<br>je]: 10) | (N-ch (<br>[V <sub>DD</sub> w                    | 34<br>D.D. I/O<br>ithstand<br>je]: 11)                                                                              | (N-ch (<br>[V <sub>DD</sub> wi | 38<br>D.D. I/O<br>ithstand<br>je]: 13) | 4<br>(N-ch C<br>[V₀⊳ wit<br>voltag | D.D. I/C<br>thstanc |  |  |

|                      | CMOS input                                       |                                                      | 5                                                                                   |                                                  | 5                                      |                                                  | 5                                                                                                                   |                                | 5                                      | 5                                  | 5                   |  |  |

|                      | CMOS output                                      |                                                      |                                                                                     |                                                  | _                                      |                                                  | 1                                                                                                                   |                                | 1                                      | 1                                  | 1                   |  |  |

|                      | N-ch O.D. I/O<br>(withstand voltage: 6 V)        | :                                                    | 3                                                                                   |                                                  | 4                                      |                                                  | 4                                                                                                                   |                                | 4                                      | 4                                  | 1                   |  |  |

| Timer                | 16-bit timer                                     |                                                      |                                                                                     |                                                  |                                        | 8 cha                                            | nnels                                                                                                               |                                |                                        |                                    |                     |  |  |

|                      | Watchdog timer                                   |                                                      |                                                                                     |                                                  |                                        | 1 cha                                            | annel                                                                                                               |                                |                                        |                                    |                     |  |  |

|                      | Real-time clock (RTC)                            |                                                      |                                                                                     |                                                  |                                        | 1 cha                                            | annel                                                                                                               |                                |                                        |                                    |                     |  |  |

|                      | 12-bit interval timer (IT)                       |                                                      |                                                                                     |                                                  |                                        |                                                  | annel                                                                                                               |                                |                                        |                                    |                     |  |  |

|                      | Timer output                                     | 4 channels<br>outputs: 3<br>8 channels<br>outputs: 7 | <sup>Note 2</sup> ),<br>s (PWM                                                      | 5 channe<br>8 channe                             | ls (PWM o<br>ls (PWM o                 | utputs: 4 <sup>∾</sup><br>utputs: 7 <sup>∾</sup> | ote <sup>2</sup> ),<br>ote <sup>2</sup> ) Note <sup>3</sup>                                                         |                                |                                        | 8 channels<br>outputs: 7           |                     |  |  |

|                      | RTC output                                       | 1 channe<br>• 1 Hz (s                                |                                                                                     | i clock: fsu                                     | B = 32 768                             | kHz)                                             |                                                                                                                     |                                |                                        |                                    |                     |  |  |

The target products and start address of the RAM areas used by the flash library are shown below.

R5F100xD, R5F101xD (x = E to G, J, L): Start address FF300H

- R5F100xE, R5F101xE (x = E to G, J, L): Start address FEF00H

- R5F100xJ, R5F101xJ (x = F, G, J, L): Start address FAF00H

- Start address F7F00H

R5F100xL, R5F101xL (x = F, G, J, L): For the RAM areas used by the flash library, see Self RAM list of Flash Self-Programming Library for RL78 Family (R20UT2944).

The number of PWM outputs varies depending on the setting of channels in use (the number of masters and slaves) (see 6.9.3 Operation as multiple PWM output function in the RL78/G13 User's Manual).

<sup>3.</sup> When setting to PIOR = 1

| lt a                 | m                    | 40                                                                                                                                                                                                                                                                                  | nin                                                                                                               | 11                                                                                                                                     | nin                                                                                                                                                                  | 10                                                            | nin                                                                                     | EO                                               | nin                                       | 64        | (2)<br>nin |  |

|----------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------|-----------|------------|--|

| Ite                  |                      | 40-                                                                                                                                                                                                                                                                                 |                                                                                                                   |                                                                                                                                        | -pin                                                                                                                                                                 |                                                               | -pin                                                                                    | 52                                               | -pin<br>I                                 |           | -pin       |  |

|                      |                      | R5F100Ex                                                                                                                                                                                                                                                                            | R5F101Ex                                                                                                          | R5F100Fx                                                                                                                               | R5F101Fx                                                                                                                                                             | R5F100Gx                                                      | R5F101Gx                                                                                | R5F100Jx                                         | R5F101Jx                                  | R5F100Lx  | R5F101Lx   |  |

| Clock output/buzz    | er output            | :                                                                                                                                                                                                                                                                                   | 2                                                                                                                 |                                                                                                                                        | 2                                                                                                                                                                    |                                                               | 2                                                                                       |                                                  | 2                                         |           | 2          |  |

| ·                    |                      | <ul> <li>2.44 kHz, 4.88 kHz, 9.76 kHz, 1.25 MHz, 2.5 MHz, 5 MHz, 10 MHz<br/>(Main system clock: fmain = 20 MHz operation)</li> <li>256 Hz, 512 Hz, 1.024 kHz, 2.048 kHz, 4.096 kHz, 8.192 kHz, 16.384 kHz, 32.768 kHz<br/>(Subsystem clock: fsuB = 32.768 kHz operation)</li> </ul> |                                                                                                                   |                                                                                                                                        |                                                                                                                                                                      |                                                               |                                                                                         |                                                  |                                           |           |            |  |

| 8/10-bit resolution  | A/D converter        | 9 channe                                                                                                                                                                                                                                                                            | ls                                                                                                                | 10 chanr                                                                                                                               | nels                                                                                                                                                                 | 10 chanr                                                      | nels                                                                                    | 12 chan                                          | nels                                      | 12 chanr  | nels       |  |

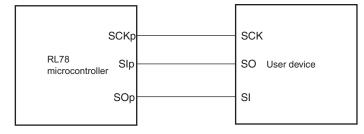

| Serial interface     |                      | [40-pin, 4                                                                                                                                                                                                                                                                          | 4-pin prod                                                                                                        | ducts]                                                                                                                                 |                                                                                                                                                                      | J                                                             |                                                                                         |                                                  |                                           | J         |            |  |

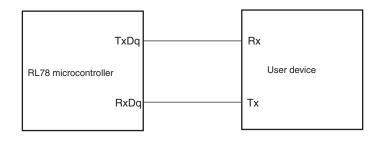

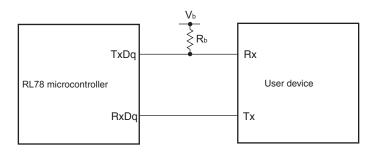

|                      |                      | <ul> <li>CSI: 1</li> <li>CSI: 2</li> <li>[48-pin, 5</li> <li>CSI: 2</li> <li>CSI: 1</li> <li>CSI: 2</li> <li>[64-pin pi</li> <li>CSI: 2</li> <li>CSI: 2</li> <li>CSI: 2</li> </ul>                                                                                                  | channel/s<br>channels/<br>2-pin proo<br>channels/<br>channels/<br>roducts]<br>channels/<br>channels/<br>channels/ | implified I <sup>2</sup><br>simplified<br>ducts]<br>simplified I <sup>2</sup><br>simplified I <sup>2</sup><br>simplified<br>simplified | C: 1 chani<br>I <sup>2</sup> C: 2 chai<br>I <sup>2</sup> C: 2 chai<br>C: 1 chani<br>I <sup>2</sup> C: 2 chai<br>I <sup>2</sup> C: 2 chai<br>I <sup>2</sup> C: 2 chai | nnels/UAR<br>nel/UART:<br>nnels/UAR<br>nnels/UAR<br>nnels/UAR | 1 channe<br>T (UART :<br>1 channe<br>T (UART :<br>T (UART :<br>T: 1 chann<br>T: 1 chann | l<br>supporting<br>nel<br>l<br>supporting<br>nel | g LIN-bus):<br>g LIN-bus):<br>g LIN-bus): | 1 channel | I          |  |

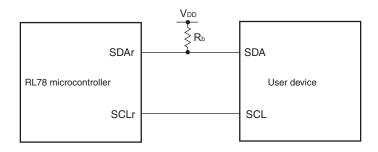

|                      | I <sup>2</sup> C bus | 1 channe                                                                                                                                                                                                                                                                            |                                                                                                                   | 1 channe                                                                                                                               |                                                                                                                                                                      | 1 channe                                                      |                                                                                         | 1 channe                                         |                                           | 1         |            |  |

| Multiplier and divid |                      | • 16 bits                                                                                                                                                                                                                                                                           | × 16 bits =                                                                                                       | = 32 bits (L<br>= 32 bits (L                                                                                                           | Jnsigned o                                                                                                                                                           |                                                               | ,                                                                                       | 1 onanna                                         |                                           |           |            |  |

|                      |                      | • 16 bits                                                                                                                                                                                                                                                                           | × 16 bits +                                                                                                       | - 32 bits =                                                                                                                            | 32 bits (U                                                                                                                                                           | nsigned or                                                    | r signed)                                                                               |                                                  |                                           |           |            |  |

| DMA controller       |                      | 2 channe                                                                                                                                                                                                                                                                            | ls                                                                                                                |                                                                                                                                        |                                                                                                                                                                      |                                                               |                                                                                         |                                                  |                                           |           |            |  |

| Vectored             | Internal             | 2                                                                                                                                                                                                                                                                                   | 27                                                                                                                | :                                                                                                                                      | 27                                                                                                                                                                   | 2                                                             | 27                                                                                      |                                                  | 27                                        | 2         | 27         |  |

| interrupt sources    | External             |                                                                                                                                                                                                                                                                                     | 7                                                                                                                 |                                                                                                                                        | 7                                                                                                                                                                    |                                                               | 10                                                                                      |                                                  | 12                                        |           | 13         |  |

| Key interrupt        |                      |                                                                                                                                                                                                                                                                                     | 4                                                                                                                 |                                                                                                                                        | 4                                                                                                                                                                    |                                                               | 6                                                                                       |                                                  | 8                                         |           | 8          |  |

| Reset                |                      | <ul> <li>Interna</li> <li>Interna</li> <li>Interna</li> <li>Interna</li> <li>Interna</li> </ul>                                                                                                                                                                                     | I reset by<br>I reset by<br>I reset by<br>I reset by                                                              | watchdog<br>power-on-<br>voltage de                                                                                                    | reset<br>etector<br>ruction ex<br>sy error                                                                                                                           | ecution <sup>Note</sup>                                       |                                                                                         |                                                  |                                           |           |            |  |

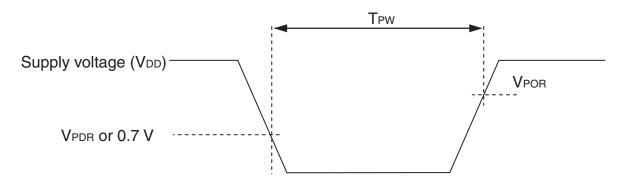

| Power-on-reset ci    | rcuit                |                                                                                                                                                                                                                                                                                     | on-reset:<br>down-res                                                                                             | 1.51 V<br>et: 1.50 V                                                                                                                   | . ,                                                                                                                                                                  |                                                               |                                                                                         |                                                  |                                           |           |            |  |

| Voltage detector     |                      | <ul><li>Rising</li><li>Falling</li></ul>                                                                                                                                                                                                                                            | -                                                                                                                 |                                                                                                                                        |                                                                                                                                                                      | 14 stages<br>14 stages                                        |                                                                                         |                                                  |                                           |           |            |  |

| On-chip debug fur    | nction               | Provided                                                                                                                                                                                                                                                                            |                                                                                                                   |                                                                                                                                        |                                                                                                                                                                      |                                                               |                                                                                         |                                                  |                                           |           |            |  |

| Power supply volta   |                      |                                                                                                                                                                                                                                                                                     |                                                                                                                   | $T_A = -40 \text{ to}$<br>$T_A = -40 \text{ to}$                                                                                       |                                                                                                                                                                      |                                                               |                                                                                         |                                                  |                                           |           |            |  |

| Operating ambien     | t temperature        | $T_A = 40 to$                                                                                                                                                                                                                                                                       | o +85°C (/                                                                                                        |                                                                                                                                        | ner applica                                                                                                                                                          | itions, D: Ii<br>ations)                                      | ndustrial a                                                                             | pplication                                       | s)                                        |           |            |  |

<R>

Note The illegal instruction is generated when instruction code FFH is executed.

Reset by the illegal instruction execution not issued by emulation with the in-circuit emulator or on-chip debug emulator.

#### [80-pin, 100-pin, 128-pin products]

# Caution This outline describes the functions at the time when Peripheral I/O redirection register (PIOR) is set to 00H.

|                      |                                              |                                                                                                                                                                                                                                                         |                                                                                             |                                                                       |                                    |                              | (1/2)                                         |  |  |  |

|----------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------|------------------------------|-----------------------------------------------|--|--|--|

|                      | Item                                         | 80-                                                                                                                                                                                                                                                     | •                                                                                           | 100                                                                   | )-pin                              | 128                          | -pin                                          |  |  |  |