Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, LINbus, UART/USART                                       |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 48                                                                              |

| Program Memory Size        | 96KB (96K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 5.5V                                                                     |

| Data Converters            | A/D 12x8/10b                                                                    |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

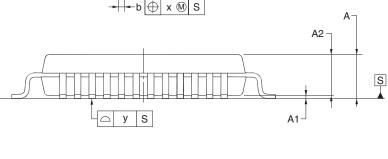

| Package / Case             | 64-VFBGA                                                                        |

| Supplier Device Package    | 64-VFBGA (4x4)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f101lfabg-u0 |

O ROM, RAM capacities

| Flash    | Data  | RAM          |          |          | RL78     | /G13     |          |          |

|----------|-------|--------------|----------|----------|----------|----------|----------|----------|

| ROM      | flash |              | 20 pins  | 24 pins  | 25 pins  | 30 pins  | 32 pins  | 36 pins  |

| 128      | 8 KB  | 12           | -        | -        | -        | R5F100AG | R5F100BG | R5F100CG |

| KB       | -     | KB           | -        | -        | -        | R5F101AG | R5F101BG | R5F101CG |

| 96       | 8 KB  | 8 KB         | =        | =        | =        | R5F100AF | R5F100BF | R5F100CF |

| KB       | -     |              | -        | -        | -        | R5F101AF | R5F101BF | R5F101CF |

| 64       | 4 KB  | 4 KB         | R5F1006E | R5F1007E | R5F1008E | R5F100AE | R5F100BE | R5F100CE |

| KB       | =     | Note         | R5F1016E | R5F1017E | R5F1018E | R5F101AE | R5F101BE | R5F101CE |

| 48       | 4 KB  | 3 KB<br>Note | R5F1006D | R5F1007D | R5F1008D | R5F100AD | R5F100BD | R5F100CD |

| KB       | _     | 1.0.0        | R5F1016D | R5F1017D | R5F1018D | R5F101AD | R5F101BD | R5F101CD |

| 32       | 4 KB  | 2 KB         | R5F1006C | R5F1007C | R5F1008C | R5F100AC | R5F100BC | R5F100CC |

| KB       | =     |              | R5F1016C | R5F1017C | R5F1018C | R5F101AC | R5F101BC | R5F101CC |

| 16<br>KB | 4 KB  | 2 KB         | R5F1006A | R5F1007A | R5F1008A | R5F100AA | R5F100BA | R5F100CA |

| KB       | -     |              | R5F1016A | R5F1017A | R5F1018A | R5F101AA | R5F101BA | R5F101CA |

| Flash | Data  | RAM           |          |          |          | RL78     | 3/G13    |          |          |          |

|-------|-------|---------------|----------|----------|----------|----------|----------|----------|----------|----------|

| ROM   | flash |               | 40 pins  | 44 pins  | 48 pins  | 52 pins  | 64 pins  | 80 pins  | 100 pins | 128 pins |

| 512   | 8 KB  | 32 KB<br>Note | =        | R5F100FL | R5F100GL | R5F100JL | R5F100LL | R5F100ML | R5F100PL | R5F100SL |

| KB    | -     | Note          | -        | R5F101FL | R5F101GL | R5F101JL | R5F101LL | R5F101ML | R5F101PL | R5F101SL |

| 384   | 8 KB  | 24 KB         | -        | R5F100FK | R5F100GK | R5F100JK | R5F100LK | R5F100MK | R5F100PK | R5F100SK |

| KB    | -     |               | -        | R5F101FK | R5F101GK | R5F101JK | R5F101LK | R5F101MK | R5F101PK | R5F101SK |

| 256   | 8 KB  | 20 KB<br>Note | -        | R5F100FJ | R5F100GJ | R5F100JJ | R5F100LJ | R5F100MJ | R5F100PJ | R5F100SJ |

| KB    | _     | Note          | -        | R5F101FJ | R5F101GJ | R5F101JJ | R5F101LJ | R5F101MJ | R5F101PJ | R5F101SJ |

| 192   | 8 KB  | 16 KB         | R5F100EH | R5F100FH | R5F100GH | R5F100JH | R5F100LH | R5F100MH | R5F100PH | R5F100SH |

| KB    | =     |               | R5F101EH | R5F101FH | R5F101GH | R5F101JH | R5F101LH | R5F101MH | R5F101PH | R5F101SH |

| 128   | 8 KB  | 12 KB         | R5F100EG | R5F100FG | R5F100GG | R5F100JG | R5F100LG | R5F100MG | R5F100PG | -        |

| KB    | -     |               | R5F101EG | R5F101FG | R5F101GG | R5F101JG | R5F101LG | R5F101MG | R5F101PG | -        |

| 96    | 8 KB  | 8 KB          | R5F100EF | R5F100FF | R5F100GF | R5F100JF | R5F100LF | R5F100MF | R5F100PF | =        |

| KB    | _     |               | R5F101EF | R5F101FF | R5F101GF | R5F101JF | R5F101LF | R5F101MF | R5F101PF | -        |

| 64    | 4 KB  | 4 KB<br>Note  | R5F100EE | R5F100FE | R5F100GE | R5F100JE | R5F100LE | =        | =        | =        |

| KB    | _     | Note          | R5F101EE | R5F101FE | R5F101GE | R5F101JE | R5F101LE | -        | =        | -        |

| 48    | 4 KB  | 3 KB Note     | R5F100ED | R5F100FD | R5F100GD | R5F100JD | R5F100LD | =        | =        | =        |

| KB    | -     |               | R5F101ED | R5F101FD | R5F101GD | R5F101JD | R5F101LD | =        | =        | =        |

| 32    | 4 KB  | 2 KB          | R5F100EC | R5F100FC | R5F100GC | R5F100JC | R5F100LC | -        | =        | -        |

| KB    | _     | 1             | R5F101EC | R5F101FC | R5F101GC | R5F101JC | R5F101LC | -        | -        | -        |

| 16    | 4 KB  | 2 KB          | R5F100EA | R5F100FA | R5F100GA | =        | =        | =        | =        | =        |

| KB    | _     | 1             | R5F101EA | R5F101FA | R5F101GA | -        | -        | -        | -        | =        |

Note The flash library uses RAM in self-programming and rewriting of the data flash memory.

The target products and start address of the RAM areas used by the flash library are shown below.

R5F100xD, R5F101xD (x = 6 to 8, A to C, E to G, J, L): Start address FF300H R5F100xE, R5F101xE (x = 6 to 8, A to C, E to G, J, L): Start address FEF00H R5F100xJ, R5F101xJ (x = F, G, J, L, M, P): Start address FAF00H R5F100xL, R5F101xL (x = F, G, J, L, M, P, S): Start address F7F00H

For the RAM areas used by the flash library, see **Self RAM list of Flash Self-Programming Library for RL78 Family (R20UT2944)**.

• 100-pin plastic LQFP (14 × 20 mm, 0.65 mm pitch)

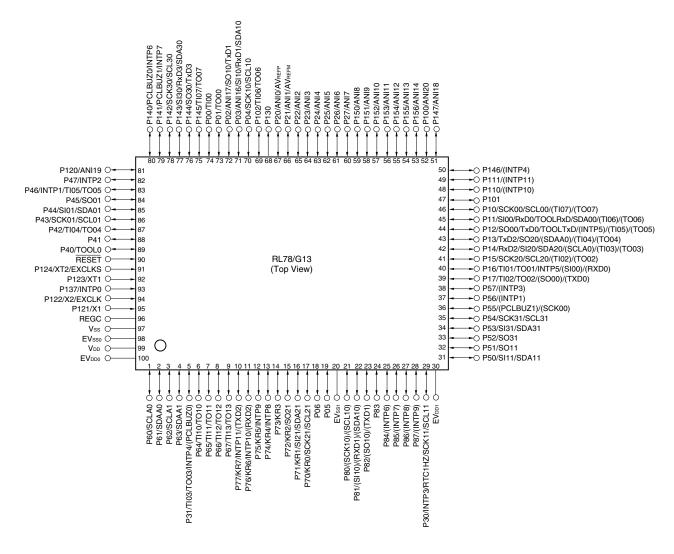

- Cautions 1. Make EVsso, EVss1 pins the same potential as Vss pin.

- 2. Make VDD pin the potential that is higher than EVDD0, EVDD1 pins (EVDD0 = EVDD1).

- 3. Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F).

- Remarks 1. For pin identification, see 1.4 Pin Identification.

- 2. When using the microcontroller for an application where the noise generated inside the microcontroller must be reduced, it is recommended to supply separate powers to the V<sub>DD</sub>, EV<sub>DD0</sub> and EV<sub>DD1</sub> pins and connect the Vss, EVsso and EVss1 pins to separate ground lines.

- 3. Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR). Refer to Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR) in the RL78/G13 User's Manual.

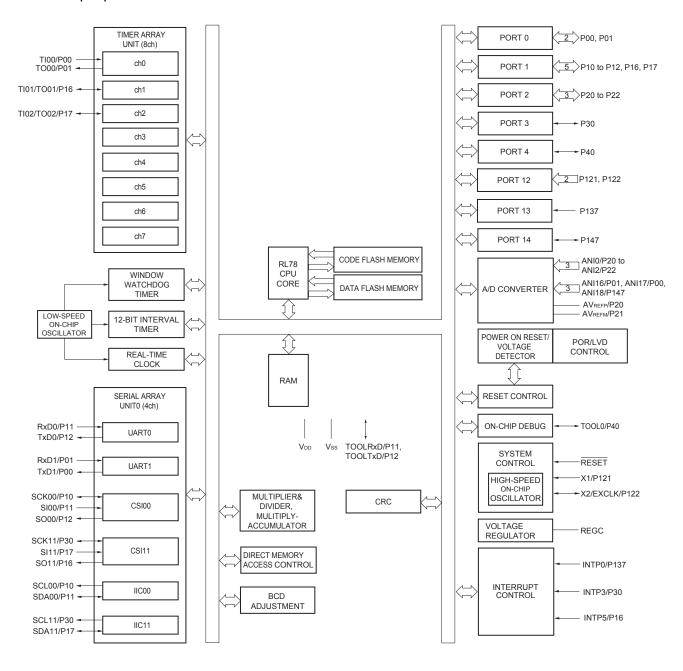

## 1.5 Block Diagram

#### 1.5.1 20-pin products

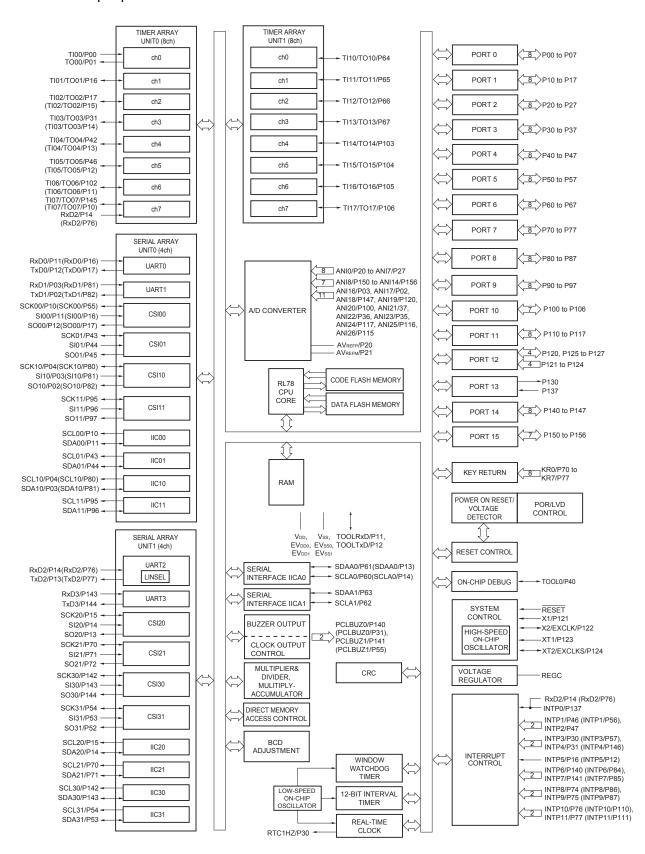

## 1.5.14 128-pin products

Remark Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR). Refer to Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR) in the RL78/G13 User's Manual.

[40-pin, 44-pin, 48-pin, 52-pin, 64-pin products]

## Caution This outline describes the functions at the time when Peripheral I/O redirection register (PIOR) is set to 00H.

(1/2)

|                   | Item                                   | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ·pin                                                                                                                                                                                                                                                                                                                                                                        | 4.4                         | -pin                                    | 40           | ·pin                                   | F0       | nin                                    |          | ·pin                                   |

|-------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------------|--------------|----------------------------------------|----------|----------------------------------------|----------|----------------------------------------|

|                   | item                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u> </u>                                                                                                                                                                                                                                                                                                                                                                    | 44                          | i                                       |              |                                        | 52-      | -pin<br>I                              |          | İ                                      |

|                   |                                        | R5F100Ex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R5F101Ex                                                                                                                                                                                                                                                                                                                                                                    | R5F100Fx                    | R5F101Fx                                | R5F100Gx     | R5F101Gx                               | R5F100Jx | R5F101Jx                               | R5F100Lx | R5F101Lx                               |

|                   |                                        | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 101                                                                                                                                                                                                                                                                                                                                                                         | 100                         | 101                                     | 100          | 101                                    | 100      | 101                                    | 100      | 101                                    |

|                   |                                        | Ex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Ex                                                                                                                                                                                                                                                                                                                                                                          | ×                           | F <sub>×</sub>                          | χ<br>Ω       | ωx                                     | ×        | ×                                      | Ž        | Ž                                      |

| Code flash me     | emory (KB)                             | 16 to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | o 192                                                                                                                                                                                                                                                                                                                                                                       | 16 t                        | o 512                                   | 16 t         | 512                                    | 32 to    | o 512                                  | 32 to    | o 512                                  |

| Data flash me     | emory (KB)                             | 4 to 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                                                                                                                                           | 4 to 8                      | _                                       | 4 to 8       | -                                      | 4 to 8   | _                                      | 4 to 8   | _                                      |

| RAM (KB)          |                                        | 2 to 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16 <sup>Note1</sup>                                                                                                                                                                                                                                                                                                                                                         | 2 to :                      | 32 <sup>Note1</sup>                     | 2 to 3       | 32 <sup>Note1</sup>                    | 2 to 3   | 32 <sup>Note1</sup>                    | 2 to 3   | 32 <sup>Note1</sup>                    |

| Address space     | e                                      | 1 MB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                             |                             |                                         |              |                                        |          |                                        |          |                                        |

| Main system clock | High-speed system clock                | HS (High<br>HS (High<br>LS (Low-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | X1 (crystal/ceramic) oscillation, external main system clock input (EXCLK) HS (High-speed main) mode: 1 to 20 MHz (V <sub>DD</sub> = 2.7 to 5.5 V), HS (High-speed main) mode: 1 to 16 MHz (V <sub>DD</sub> = 2.4 to 5.5 V), LS (Low-speed main) mode: 1 to 8 MHz (V <sub>DD</sub> = 1.8 to 5.5 V), LV (Low-voltage main) mode: 1 to 4 MHz (V <sub>DD</sub> = 1.6 to 5.5 V) |                             |                                         |              |                                        |          |                                        |          |                                        |

|                   | High-speed on-chip oscillator          | HS (High<br>LS (Low-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (High-speed main) mode: 1 to 32 MHz ( $V_{DD}$ = 2.7 to 5.5 V),<br>(High-speed main) mode: 1 to 16 MHz ( $V_{DD}$ = 2.4 to 5.5 V),<br>(Low-speed main) mode: 1 to 8 MHz ( $V_{DD}$ = 1.8 to 5.5 V),<br>(Low-voltage main) mode: 1 to 4 MHz ( $V_{DD}$ = 1.6 to 5.5 V)                                                                                                       |                             |                                         |              |                                        |          |                                        |          |                                        |

| Subsystem cl      | ock                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Γ1 (crystal) oscillation, external subsystem clock input (EXCLKS)<br>2.768 kHz                                                                                                                                                                                                                                                                                              |                             |                                         |              |                                        |          |                                        |          |                                        |

| Low-speed or      | n-chip oscillator                      | 15 kHz (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TYP.)                                                                                                                                                                                                                                                                                                                                                                       |                             |                                         |              |                                        |          |                                        |          |                                        |

| General-purp      | ose registers                          | (8-bit register $\times$ 8) $\times$ 4 banks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                             |                             |                                         |              |                                        |          |                                        |          |                                        |

| Minimum insti     | ruction execution time                 | 0.03125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | μs (High-s                                                                                                                                                                                                                                                                                                                                                                  | speed on-                   | chip oscilla                            | tor: fin = 3 | 2 MHz op                               | eration) |                                        |          |                                        |

|                   |                                        | 0.05 <i>μ</i> s (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | High-spee                                                                                                                                                                                                                                                                                                                                                                   | ed system                   | clock: fmx                              | = 20 MHz     | operation                              | )        |                                        |          |                                        |

|                   |                                        | 30.5 μs (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Subsyster                                                                                                                                                                                                                                                                                                                                                                   | n clock: fs                 | ыв = 32.76                              | 8 kHz ope    | ration)                                |          |                                        |          |                                        |

| Instruction se    | t                                      | <ul> <li>Data transfer (8/16 bits)</li> <li>Adder and subtractor/logical operation (8/16 bits)</li> <li>Multiplication (8 bits × 8 bits)</li> <li>Rotate, barrel shift, and bit manipulation (Set, reset, test, and Boolean operation), etc.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                             |                             |                                         |              |                                        |          |                                        |          |                                        |

| I/O port          | Total                                  | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 36                                                                                                                                                                                                                                                                                                                                                                          | 4                           | 40                                      | 2            | 14                                     | 4        | 18                                     | 5        | 58                                     |

|                   | CMOS I/O                               | (N-ch (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28<br>O.D. I/O<br>ithstand<br>ge]: 10)                                                                                                                                                                                                                                                                                                                                      | (N-ch<br>[V <sub>DD</sub> w | 31<br>O.D. I/O<br>rithstand<br>ge]: 10) | (N-ch (      | 34<br>O.D. I/O<br>ithstand<br>je]: 11) | (N-ch (  | 38<br>O.D. I/O<br>ithstand<br>ge]: 13) | (N-ch (  | 18<br>O.D. I/O<br>ithstand<br>ge]: 15) |

|                   | CMOS input                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                                                                                                                                                                                                                                                                                                                                                                           |                             | 5                                       |              | 5                                      |          | 5                                      |          | 5                                      |

|                   | CMOS output                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | =                                                                                                                                                                                                                                                                                                                                                                           |                             | =                                       |              | 1                                      |          | 1                                      |          | 1                                      |

|                   | N-ch O.D. I/O (withstand voltage: 6 V) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3                                                                                                                                                                                                                                                                                                                                                                           |                             | 4                                       |              | 4                                      |          | 4                                      |          | 4                                      |

| Timer             | 16-bit timer                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                             |                             |                                         | 8 cha        | nnels                                  |          |                                        |          |                                        |