Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

Ξ·ΧΕΙ

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, LINbus, UART/USART                                       |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 48                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 12K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 5.5V                                                                     |

| Data Converters            | A/D 12x8/10b                                                                    |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LFQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f101lgdfb-30 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

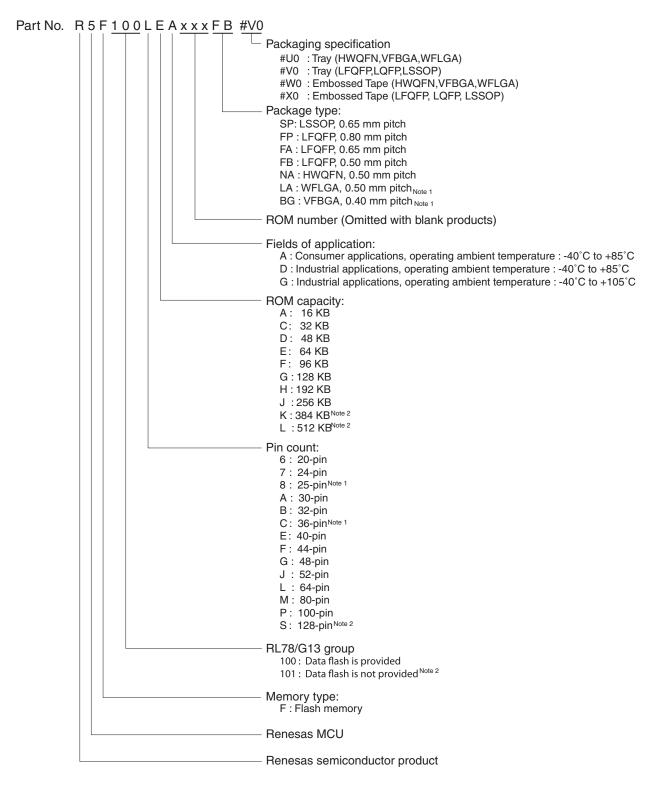

# 1.2 List of Part Numbers

- **Notes** 1. Products only for "A: Consumer applications ( $T_A = -40$  to  $+85^{\circ}C$ )", and "G: Industrial applications ( $T_A = -40$  to  $+105^{\circ}C$ )"

- **2.** Products only for "A: Consumer applications ( $T_A = -40$  to  $+85^{\circ}C$ )", and "D: Industrial applications ( $T_A = -40$  to  $+85^{\circ}C$ )"

| Table 1-1. | List of Ordering Part Numbers |

|------------|-------------------------------|

|------------|-------------------------------|

| Pin count | Package                 | Data flash | Fields of<br>Application | Ordering Part Number                                                                               |                                                 |

|-----------|-------------------------|------------|--------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------|

|           |                         |            | Note                     |                                                                                                    |                                                 |

| 48 pins   | 48-pin plastic          | Mounted    | А                        | R5F100GAANA#U0, R5F100GCANA#U0, R5F100GDANA#U0,                                                    |                                                 |

|           | HWQFN (7 $\times$ 7 mm, |            |                          |                                                                                                    | R5F100GEANA#U0, R5F100GFANA#U0, R5F100GGANA#U0, |

|           | 0.5 mm pitch)           |            |                          | R5F100GHANA#U0, R5F100GJANA#U0, R5F100GKANA#U0,                                                    |                                                 |

|           |                         |            |                          | R5F100GLANA#U0                                                                                     |                                                 |

|           |                         |            |                          | R5F100GAANA#W0, R5F100GCANA#W0,<br>R5F100GDANA#W0, R5F100GEANA#W0,                                 |                                                 |

|           |                         |            |                          | R5F100GFANA#W0, R5F100GGANA#W0,                                                                    |                                                 |

|           |                         |            |                          | R5F100GHANA#W0, R5F100GJANA#W0,                                                                    |                                                 |

|           |                         |            |                          | R5F100GKANA#W0, R5F100GLANA#W0                                                                     |                                                 |

|           |                         |            | D                        | R5F100GADNA#U0, R5F100GCDNA#U0, R5F100GDDNA#U0,                                                    |                                                 |

|           |                         |            |                          | R5F100GEDNA#U0, R5F100GFDNA#U0, R5F100GGDNA#U0,                                                    |                                                 |

|           |                         |            |                          | R5F100GHDNA#U0, R5F100GJDNA#U0, R5F100GKDNA#U0,                                                    |                                                 |

|           |                         |            |                          | R5F100GLDNA#U0                                                                                     |                                                 |

|           |                         |            |                          | R5F100GADNA#W0, R5F100GCDNA#W0,                                                                    |                                                 |

|           |                         |            |                          | R5F100GDDNA#W0, R5F100GEDNA#W0,                                                                    |                                                 |

|           |                         |            |                          | R5F100GFDNA#W0, R5F100GGDNA#W0,                                                                    |                                                 |

|           |                         |            |                          | R5F100GHDNA#W0, R5F100GJDNA#W0,                                                                    |                                                 |

|           |                         |            |                          | R5F100GKDNA#W0, R5F100GLDNA#W0                                                                     |                                                 |

|           |                         |            | G                        | R5F100GAGNA#U0, R5F100GCGNA#U0, R5F100GDGNA#U0                                                     |                                                 |

|           |                         |            |                          | R5F100GEGNA#U0, R5F100GFGNA#U0, R5F100GGGNA#U0<br>R5F100GHGNA#U0, R5F100GJGNA#U0                   |                                                 |

|           |                         |            |                          | R5F100GAGNA#W0, R5F100GCGNA#W0,                                                                    |                                                 |

|           |                         |            |                          | R5F100GDGNA#W0, R5F100GEGNA#W0,                                                                    |                                                 |

|           |                         |            |                          | R5F100GFGNA#W0, R5F100GGGNA#W0,                                                                    |                                                 |

|           |                         |            |                          | R5F100GHGNA#W0, R5F100GJGNA#W0                                                                     |                                                 |

|           |                         | Not        | А                        | R5F101GAANA#U0, R5F101GCANA#U0, R5F101GDANA#U0,                                                    |                                                 |

|           |                         | mounted    |                          | R5F101GEANA#U0, R5F101GFANA#U0, R5F101GGANA#U0,                                                    |                                                 |

|           |                         |            |                          | R5F101GHANA#U0, R5F101GJANA#U0, R5F101GKANA#U0,                                                    |                                                 |

|           |                         |            |                          | R5F101GLANA#U0                                                                                     |                                                 |

|           |                         |            |                          | R5F101GAANA#W0, R5F101GCANA#W0,                                                                    |                                                 |

|           |                         |            |                          | R5F101GDANA#W0, R5F101GEANA#W0,                                                                    |                                                 |

|           |                         |            |                          | R5F101GFANA#W0, R5F101GGANA#W0,                                                                    |                                                 |

|           |                         |            |                          | R5F101GHANA#W0, R5F101GJANA#W0,                                                                    |                                                 |

|           |                         |            | D                        | R5F101GKANA#W0, R5F101GLANA#W0                                                                     |                                                 |

|           |                         |            | D                        | R5F101GADNA#U0, R5F101GCDNA#U0, R5F101GDDNA#U0,<br>R5F101GEDNA#U0, R5F101GFDNA#U0, R5F101GGDNA#U0, |                                                 |

|           |                         |            |                          | R5F101GEDNA#00, R5F101GEDNA#00, R5F101GGDNA#00,<br>R5F101GHDNA#U0, R5F101GJDNA#U0, R5F101GKDNA#U0, |                                                 |

|           |                         |            |                          | R5F101GLDNA#U0                                                                                     |                                                 |

|           |                         |            |                          | R5F101GADNA#W0, R5F101GCDNA#W0,                                                                    |                                                 |

|           |                         |            |                          | R5F101GDDNA#W0, R5F101GEDNA#W0,                                                                    |                                                 |

|           |                         |            |                          | R5F101GFDNA#W0, R5F101GGDNA#W0,                                                                    |                                                 |

|           |                         |            |                          | R5F101GHDNA#W0, R5F101GJDNA#W0,                                                                    |                                                 |

|           |                         |            |                          | R5F101GKDNA#W0, R5F101GLDNA#W0                                                                     |                                                 |

Note For the fields of application, refer to Figure 1-1 Part Number, Memory Size, and Package of RL78/G13.

Caution The ordering part numbers represent the numbers at the time of publication. For the latest ordering part numbers, refer to the target product page of the Renesas Electronics website.

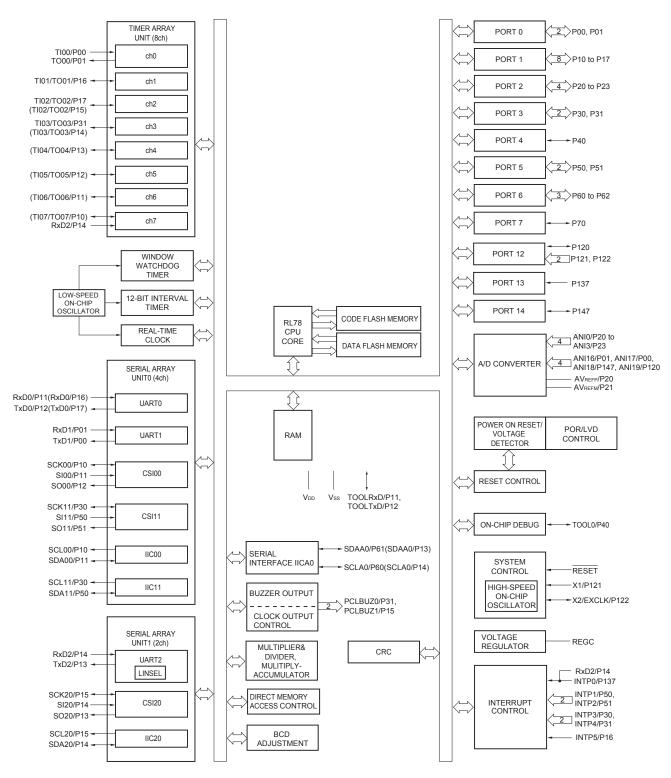

# 1.5.5 32-pin products

**Remark** Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR). Refer to Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR) in the RL78/G13 User's Manual.

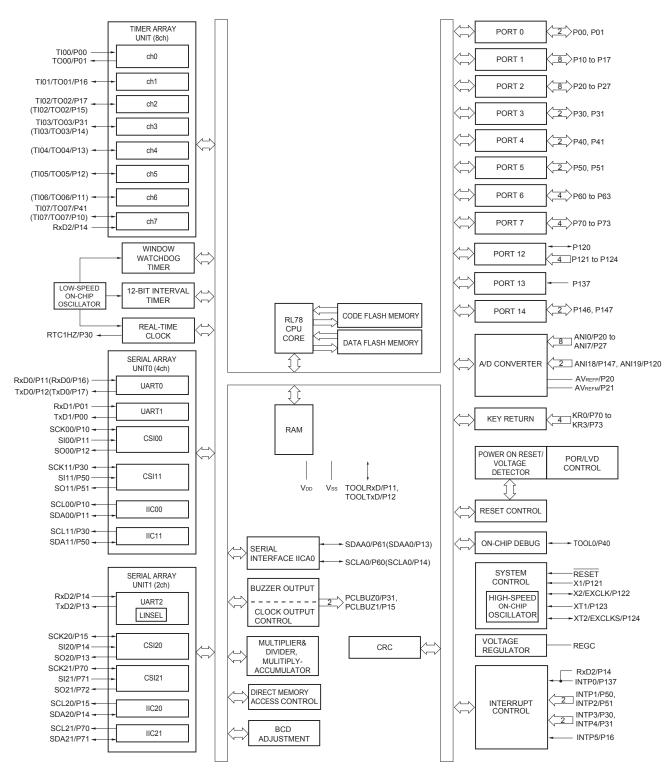

# 1.5.8 44-pin products

**Remark** Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR). Refer to **Figure 4-8 Format of Peripheral I/O Redirection Register** (**PIOR**) in the RL78/G13 User's Manual.

# 1.6 Outline of Functions

[20-pin, 24-pin, 25-pin, 30-pin, 32-pin, 36-pin products]

Caution This outline describes the functions at the time when Peripheral I/O redirection register (PIOR) is set to 00H.

|                      | Item                                                                                                                                                 | 20-p                                                                                                                                                                                                | oin                                                                                                                         | 24-                                              | pin                                      | 25                                                       | -pin                                                                    | 30-                                           | pin                     | 32-                                                        | pin                 | (1/2<br>36-                                   | pin                |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------|-------------------------|------------------------------------------------------------|---------------------|-----------------------------------------------|--------------------|

|                      | , ד                                                                                                                                                  | Ъ                                                                                                                                                                                                   | Я                                                                                                                           | גר                                               | д                                        | גר                                                       | Ъ                                                                       | דג                                            | Ъ                       | ភ្ល                                                        | Ъ                   |                                               |                    |

|                      | 5F1                                                                                                                                                  | 5F1                                                                                                                                                                                                 | 5F10                                                                                                                        | 5F10                                             | 5F10                                     | 5F10                                                     | 5F10                                                                    | 5F10                                          | 5F10                    | 5F10                                                       | 5F10                | 5F1(                                          |                    |

|                      | R5F1006x                                                                                                                                             | R5F1016x                                                                                                                                                                                            | R5F1007x                                                                                                                    | R5F1017x                                         | R5F1008x                                 | R5F1018x                                                 | R5F100Ax                                                                | R5F101Ax                                      | R5F100Bx                | R5F101Bx                                                   | R5F100Cx            | R5F101Cx                                      |                    |

| Code flash me        | emory (KB)                                                                                                                                           | 16 to                                                                                                                                                                                               | 64                                                                                                                          | 16 t                                             | o 64                                     | 161                                                      | o 64                                                                    | 16 to                                         | 128                     |                                                            | 128                 | 16 to                                         | 128                |

| Data flash me        | emory (KB)                                                                                                                                           | 4                                                                                                                                                                                                   | _                                                                                                                           | 4                                                | _                                        | 4                                                        | _                                                                       | 4 to 8                                        | _                       | 4 to 8                                                     | _                   | 4 to 8                                        | _                  |

| RAM (KB)             |                                                                                                                                                      | 2 to 4                                                                                                                                                                                              | Note1                                                                                                                       | 2 to                                             | 4 <sup>Note1</sup>                       | 2 to                                                     | 4 <sup>Note1</sup>                                                      | 2 to <sup>-</sup>                             | 12 <sup>Note1</sup>     | 2 to 1                                                     | 2 <sup>Note1</sup>  | 2 to <sup>-</sup>                             | 2 <sup>Note1</sup> |

| Address spac         | e                                                                                                                                                    | 1 MB                                                                                                                                                                                                |                                                                                                                             | •                                                |                                          | L                                                        |                                                                         |                                               |                         |                                                            |                     |                                               |                    |

| Main system<br>clock | High-speed system<br>clock                                                                                                                           | X1 (crys<br>HS (High<br>HS (High<br>LS (Low<br>LV (Low                                                                                                                                              | n-speed<br>n-speed<br>-speed                                                                                                | l main) m<br>l main) m<br>main) m                | node: 1 t<br>node: 1 t<br>ode: 1 to      | o 20 MH<br>o 16 MH<br>o 8 MHz                            | Iz (V <sub>DD</sub> =<br>Iz (V <sub>DD</sub> =<br>(V <sub>DD</sub> = 1. | 2.7 to 5.<br>2.4 to 5.<br>8 to 5.5            | .5 V),<br>.5 V),<br>V), | EXCLK)                                                     |                     |                                               |                    |

|                      | High-speed on-chip oscillator                                                                                                                        | HS (High<br>HS (High<br>LS (Low-<br>LV (Low-                                                                                                                                                        | n-speed<br>-speed                                                                                                           | l main) m<br>main) m                             | node: 1 f<br>ode: 1 f                    | to 16 MH<br>to 8 MHz                                     | Iz (Vdd =<br>2 (Vdd = 1                                                 | 2.4 to 5<br>1.8 to 5.5                        | .5 V),<br>5 V),         |                                                            |                     |                                               |                    |

| Subsystem cl         | ock                                                                                                                                                  |                                                                                                                                                                                                     |                                                                                                                             |                                                  |                                          |                                                          |                                                                         |                                               |                         |                                                            |                     |                                               |                    |

| Low-speed or         | n-chip oscillator                                                                                                                                    | 15 kHz (                                                                                                                                                                                            | TYP.)                                                                                                                       |                                                  |                                          |                                                          |                                                                         |                                               |                         |                                                            |                     |                                               |                    |

| General-purp         | ose registers                                                                                                                                        | (8-bit reg                                                                                                                                                                                          | gister ×                                                                                                                    | 8) × 4 ba                                        | anks                                     |                                                          |                                                                         |                                               |                         |                                                            |                     |                                               |                    |

| Minimum inst         | ruction execution time                                                                                                                               | 0.03125 $\mu$ s (High-speed on-chip oscillator: f <sub>IH</sub> = 32 MHz operation)                                                                                                                 |                                                                                                                             |                                                  |                                          |                                                          |                                                                         |                                               |                         |                                                            |                     |                                               |                    |

|                      |                                                                                                                                                      | 0.05 $\mu$ s (High-speed system clock: f <sub>MX</sub> = 20 MHz operation)                                                                                                                          |                                                                                                                             |                                                  |                                          |                                                          |                                                                         |                                               |                         |                                                            |                     |                                               |                    |

| Instruction set      |                                                                                                                                                      | <ul> <li>Data ti</li> <li>Adder</li> <li>Multipli</li> <li>Rotate</li> </ul>                                                                                                                        | and su<br>lication                                                                                                          | btractor/<br>(8 bits ×                           | logical o<br>8 bits)                     |                                                          |                                                                         |                                               | t, and B                | oolean o                                                   | peration            | ), etc.                                       |                    |

| I/O port             | Total                                                                                                                                                | 16                                                                                                                                                                                                  | ;                                                                                                                           | 2                                                | 0                                        | 2                                                        | 21                                                                      | 2                                             | 6                       | 2                                                          | 8                   | 3                                             | 2                  |

|                      | CMOS I/O                                                                                                                                             | 13<br>(N-ch O<br>[V₀₀ with<br>voltage                                                                                                                                                               | .D. I/O<br>nstand                                                                                                           | (N-ch C                                          | thstand                                  | (N-ch (<br>[V <sub>DD</sub> w                            | 5<br>D.D. I/O<br>thstand<br>ge]: 6)                                     | 2<br>(N-ch C<br>[V⊳⊳ wi<br>voltag             | D.D. I/O<br>thstand     | 2<br>(N-ch C<br>[V <sub>DD</sub> wi <sup>*</sup><br>voltag | D.D. I/O<br>thstand | 2<br>(N-ch C<br>[V <sub>DD</sub> wi<br>voltag | D.D. I/C           |

|                      | CMOS input                                                                                                                                           | 3                                                                                                                                                                                                   |                                                                                                                             | :                                                | 3                                        |                                                          | 3                                                                       | :                                             | 3                       | 3                                                          | 3                   | 3                                             | 3                  |

|                      | CMOS output                                                                                                                                          | -                                                                                                                                                                                                   |                                                                                                                             | -                                                | -                                        |                                                          | 1                                                                       | -                                             | -                       | -                                                          | -                   | -                                             | -                  |

|                      | N-ch O.D. I/O<br>(withstand voltage: 6 V)                                                                                                            | -                                                                                                                                                                                                   |                                                                                                                             | 2                                                | 2                                        |                                                          | 2                                                                       | 2                                             | 2                       | 3                                                          | 3                   | 3                                             | 3                  |

| Timer                | 16-bit timer                                                                                                                                         |                                                                                                                                                                                                     |                                                                                                                             |                                                  |                                          |                                                          | 8 cha                                                                   | nnels                                         |                         |                                                            |                     |                                               |                    |

|                      | Watchdog timer                                                                                                                                       | 1 channel                                                                                                                                                                                           |                                                                                                                             |                                                  |                                          |                                                          |                                                                         |                                               |                         |                                                            |                     |                                               |                    |

|                      | Real-time clock (RTC)                                                                                                                                |                                                                                                                                                                                                     |                                                                                                                             |                                                  |                                          |                                                          | 1 chan                                                                  | nel Note 2                                    |                         |                                                            |                     |                                               |                    |

|                      | 12-bit interval timer (IT)                                                                                                                           |                                                                                                                                                                                                     |                                                                                                                             |                                                  |                                          |                                                          |                                                                         |                                               |                         |                                                            |                     |                                               |                    |

|                      | Timer output                                                                                                                                         | 3 channels     4 channels     4 channels     4 channels (PWM outputs: 3 Note 3),       (PWM outputs:     (PWM outputs: 3 Note 3)     8 channels (PWM outputs: 7 Note 3)       2 Note 3)     Note 3) |                                                                                                                             |                                                  |                                          |                                                          |                                                                         |                                               |                         |                                                            |                     |                                               |                    |

|                      | RTC output                                                                                                                                           |                                                                                                                                                                                                     |                                                                                                                             | •                                                |                                          |                                                          |                                                                         | -                                             |                         |                                                            |                     |                                               |                    |

| Notes 1.             | The flash library us<br>The target products<br>R5F100xD, R5F<br>R5F100xE, R5F<br>For the RAM areas<br><b>for RL78 Family (I</b><br>Only the constant | s and sta<br>101xD (:<br>101xE ()<br>used by<br><b>R20UT29</b>                                                                                                                                      | $\begin{array}{l} \text{rt addr} \\ x = 6 \ \text{to} \\ x = 6 \ \text{to} \\ \text{the flat} \\ \textbf{944}. \end{array}$ | ress of t<br>o 8, A to<br>o 8, A to<br>ash libra | he RAN<br>o C): S<br>o C): S<br>ury, see | A areas<br>Start add<br>Start add<br>Start add<br>Self R | used by<br>dress Ff<br>dress Ff<br>AM list                              | y the fla<br>F300H<br>EF00H<br><b>of Flas</b> | sh libra<br>h Self-     | ry are s<br><b>Progra</b> i                                | hown b<br>mming     | Library                                       |                    |

<sup>2.</sup> Only the constant-period interrupt function when the low-speed on-chip oscillator clock (fiL) is selected

- **Notes 1.** Total current flowing into V<sub>DD</sub> and EV<sub>DD0</sub>, including the input leakage current flowing when the level of the input pin is fixed to V<sub>DD</sub>, EV<sub>DD0</sub> or V<sub>SS</sub>, EV<sub>SS0</sub>. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the A/D converter, LVD circuit, I/O port, and on-chip pull-up/pull-down resistors and the current flowing during data flash rewrite.

- 2. During HALT instruction execution by flash memory.

- 3. When high-speed on-chip oscillator and subsystem clock are stopped.

- 4. When high-speed system clock and subsystem clock are stopped.

- When high-speed on-chip oscillator and high-speed system clock are stopped. When RTCLPC = 1 and setting ultra-low current consumption (AMPHS1 = 1). The current flowing into the RTC is included. However, not including the current flowing into the 12-bit interval timer and watchdog timer.

- 6. Not including the current flowing into the RTC, 12-bit interval timer, and watchdog timer.

- 7. Relationship between operation voltage width, operation frequency of CPU and operation mode is as below.

- HS (high-speed main) mode: 2.7 V  $\leq$  V\_{DD}  $\leq$  5.5 V@1 MHz to 32 MHz

- 2.4 V  $\leq$  V\_{DD}  $\leq$  5.5 V@1 MHz to 16 MHz

- LS (low-speed main) mode:  $1.8 \text{ V} \le V_{\text{DD}} \le 5.5 \text{ V} @ 1 \text{ MHz}$  to 8 MHz

- LV (low-voltage main) mode: 1.6 V  $\leq$  V\_{DD}  $\leq$  5.5 V@1 MHz to 4 MHz

- 8. Regarding the value for current to operate the subsystem clock in STOP mode, refer to that in HALT mode.

- Remarks 1. fmx: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- 2. fin: High-speed on-chip oscillator clock frequency

- **3.** fsub: Subsystem clock frequency (XT1 clock oscillation frequency)

- Except subsystem clock operation and STOP mode, temperature condition of the TYP. value is T<sub>A</sub> = 25°C

- 6. Current flowing only to the A/D converter. The supply current of the RL78 microcontrollers is the sum of IDD1 or IDD2 and IADC when the A/D converter operates in an operation mode or the HALT mode.

- 7. Current flowing only to the LVD circuit. The supply current of the RL78 microcontrollers is the sum of IDD1, IDD2 or IDD3 and ILVD when the LVD circuit is in operation.

- 8. Current flowing only during data flash rewrite.

- 9. Current flowing only during self programming.

- 10. For shift time to the SNOOZE mode, see 18.3.3 SNOOZE mode.

Remarks 1. fill: Low-speed on-chip oscillator clock frequency

- **2.** fsub: Subsystem clock frequency (XT1 clock oscillation frequency)

- 3. fclk: CPU/peripheral hardware clock frequency

- 4. Temperature condition of the TYP. value is  $T_A = 25^{\circ}C$

### 2.5 Peripheral Functions Characteristics

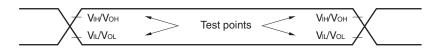

### AC Timing Test Points

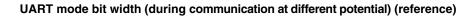

### 2.5.1 Serial array unit

### (1) During communication at same potential (UART mode) (T<sub>A</sub> = -40 to +85°C, 1.6 V $\leq$ EV<sub>DD0</sub> = EV<sub>DD1</sub> $\leq$ V<sub>DD</sub> $\leq$ 5.5 V, Vss = EV<sub>SS0</sub> = EV<sub>SS1</sub> = 0 V)

| Parameter            | Symbol |            | Conditions                                                                  |      | h-speed<br>Mode  | ``   | /-speed<br>Mode  | ``   | -voltage<br>Mode | Unit |

|----------------------|--------|------------|-----------------------------------------------------------------------------|------|------------------|------|------------------|------|------------------|------|

|                      |        |            |                                                                             | MIN. | MAX.             | MIN. | MAX.             | MIN. | MAX.             |      |

| Transfer rate Note 1 |        | 2.4 V≤ EV  | 5.5  V                                                                      |      | fMCK/6<br>Note 2 |      | fмск/6           |      | fмск/6           | bps  |

|                      |        |            | Theoretical value of the maximum transfer rate $f_{MCK} = f_{CLK}^{Note 3}$ |      | 5.3              |      | 1.3              |      | 0.6              | Mbps |

|                      |        | 1.8 V ≤ EV | $T_{\text{DD0}} \leq 5.5 \text{ V}$                                         |      | fмск/6<br>Note 2 |      | fмск/6           |      | fмск/6           | bps  |

|                      |        |            | Theoretical value of the maximum transfer rate $f_{MCK} = f_{CLK}^{Note 3}$ |      | 5.3              |      | 1.3              |      | 0.6              | Mbps |

|                      |        | 1.7 V ≤ EV | $T_{\text{DD0}} \leq 5.5 \text{ V}$                                         |      | fMCK/6<br>Note 2 |      | fмск/6<br>Note 2 |      | fмск/6           | bps  |

|                      |        |            | Theoretical value of the maximum transfer rate $f_{MCK} = f_{CLK}^{Note 3}$ |      | 5.3              |      | 1.3              |      | 0.6              | Mbps |

|                      |        | 1.6 V ≤ EV | $T_{\text{DD0}} \leq 5.5 \text{ V}$                                         | _    | _                |      | fмск/6<br>Note 2 |      | fмск/6           | bps  |

|                      |        |            | Theoretical value of the maximum transfer rate $f_{MCK} = f_{CLK}^{Note 3}$ | _    | _                |      | 1.3              |      | 0.6              | Mbps |

Notes 1. Transfer rate in the SNOOZE mode is 4800 bps only.

2. The following conditions are required for low voltage interface when  $E_{VDD0} < V_{DD}$ .

$2.4~V \leq EV_{\text{DD0}}$  < 2.7 V : MAX. 2.6 Mbps

- $1.8~\text{V} \leq \text{EV}_\text{DD0} < 2.4~\text{V}$  : MAX. 1.3 Mbps

- $1.6~V \leq EV_{\text{DD0}} < 1.8~V$  : MAX. 0.6 Mbps

- 3. The maximum operating frequencies of the CPU/peripheral hardware clock (fcLK) are:

$\begin{array}{lll} \text{HS (high-speed main) mode:} & 32 \ \text{MHz} \ (2.7 \ \text{V} \leq \text{V}_{\text{DD}} \leq 5.5 \ \text{V}) \\ & 16 \ \text{MHz} \ (2.4 \ \text{V} \leq \text{V}_{\text{DD}} \leq 5.5 \ \text{V}) \\ \text{LS (low-speed main) mode:} & 8 \ \text{MHz} \ (1.8 \ \text{V} \leq \text{V}_{\text{DD}} \leq 5.5 \ \text{V}) \\ \text{LV (low-voltage main) mode:} & 4 \ \text{MHz} \ (1.6 \ \text{V} \leq \text{V}_{\text{DD}} \leq 5.5 \ \text{V}) \\ \end{array}$

Caution Select the normal input buffer for the RxDq pin and the normal output mode for the TxDq pin by using port input mode register g (PIMg) and port output mode register g (POMg).

# (2) During communication at same potential (CSI mode) (master mode, SCKp... internal clock output, corresponding CSI00 only)

| Parameter                                                | Symbol        | Conditions                                 |                                         | 、 <b>U</b>      | h-speed<br>Mode | ``              | /-speed<br>Mode | LV (low-<br>main) | -voltage<br>Mode | Unit |

|----------------------------------------------------------|---------------|--------------------------------------------|-----------------------------------------|-----------------|-----------------|-----------------|-----------------|-------------------|------------------|------|

|                                                          |               |                                            |                                         | MIN.            | MAX.            | MIN.            | MAX.            | MIN.              | MAX.             |      |

| SCKp cycle time                                          | tkCY1         | tксү1 $\geq$ 2/fclк                        | $4.0~V \leq EV_{\text{DD0}} \leq 5.5~V$ | 62.5            |                 | 250             |                 | 500               |                  | ns   |

|                                                          |               |                                            | $2.7~V \leq EV_{\text{DD0}} \leq 5.5~V$ | 83.3            |                 | 250             |                 | 500               |                  | ns   |

| SCKp high-/low-level width                               | tĸнı,<br>tĸ∟ı | $4.0 V \le EV_{DI}$                        | $500 \leq 5.5 \text{ V}$                | tксү1/2 –<br>7  |                 | tксү1/2 –<br>50 |                 | tксү1/2 –<br>50   |                  | ns   |

|                                                          |               | 2.7 V ≤ EV <sub>D</sub>                    | $500 \leq 5.5 \text{ V}$                | tксү1/2 –<br>10 |                 | tксү1/2 –<br>50 |                 | tксү1/2 –<br>50   |                  | ns   |

| SIp setup time (to SCKp <sup>↑</sup> )                   | tsik1         | $4.0 \ V \le EV_{DI}$                      | $00 \leq 5.5 \text{ V}$                 | 23              |                 | 110             |                 | 110               |                  | ns   |

| Note 1                                                   |               | $2.7 \text{ V} \leq EV_{\text{DI}}$        | $00 \leq 5.5 \text{ V}$                 | 33              |                 | 110             |                 | 110               |                  | ns   |

| Slp hold time (from<br>SCKp↑) <sup>Note 2</sup>          | tksii         | $2.7 \text{ V} \leq \text{EV}_{\text{DI}}$ | $500 \leq 5.5 \text{ V}$                | 10              |                 | 10              |                 | 10                |                  | ns   |

| Delay time from SCKp↓ to<br>SOp output <sup>Note 3</sup> | tĸso1         | C = 20 pF <sup>Not</sup>                   | te 4                                    |                 | 10              |                 | 10              |                   | 10               | ns   |

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{EV}_{\text{DD}} = \text{EV}_{\text{DD}} \le 5.5 \text{ V}, \text{ Vss} = \text{EV}_{\text{SS}} = \text{EV}_{\text{SS}} = 0 \text{ V})$

- **Notes 1.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp setup time becomes "to  $SCKp\downarrow$ " when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 2. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp hold time becomes "from SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- **3.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The delay time to SOp output becomes "from SCKp<sup>↑</sup>" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 4. C is the load capacitance of the SCKp and SOp output lines.

# Caution Select the normal input buffer for the SIp pin and the normal output mode for the SOp pin and SCKp pin by using port input mode register g (PIMg) and port output mode register g (POMg).

- **Remarks 1.** This value is valid only when CSI00's peripheral I/O redirect function is not used.

- p: CSI number (p = 00), m: Unit number (m = 0), n: Channel number (n = 0),

g: PIM and POM numbers (g = 1)

- 3. fMCK: Serial array unit operation clock frequency

(Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn). m: Unit number,

n: Channel number (mn = 00))

| Parameter                        | Symbol  | Conditions                                                                                                                                                                                        | 、 U                                 | HS (high-speed main) Mode |                                                 | /-speed<br>Mode | `                                   | -voltage<br>Mode | Unit |

|----------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------|-------------------------------------------------|-----------------|-------------------------------------|------------------|------|

|                                  |         |                                                                                                                                                                                                   | MIN.                                | MAX.                      | MIN.                                            | MAX.            | MIN.                                | MAX.             |      |

| Data setup time (reception)      | tsu:dat | $\label{eq:constraint} \begin{array}{l} 2.7~V \leq EV_{\text{DD0}} \leq 5.5~V, \\ C_{\text{b}} = 50~pF,~R_{\text{b}} = 2.7~k\Omega \end{array}$                                                   | 1/fмск<br>+ 85<br><sub>Note2</sub>  |                           | 1/fмск<br>+ 145<br><sub>Note2</sub>             |                 | 1/fмск<br>+ 145<br><sub>Note2</sub> |                  | ns   |

|                                  |         | $\label{eq:linear} \begin{split} 1.8 \ V &\leq EV_{\text{DD0}} \leq 5.5 \ V, \\ C_{\text{b}} &= 100 \ p\text{F}, \ R_{\text{b}} = 3 \ k\Omega \end{split}$                                        | 1/fмск<br>+ 145<br><sub>Note2</sub> |                           | 1/fмск<br>+ 145<br><sub>Note2</sub>             |                 | 1/fмск<br>+ 145<br><sub>Note2</sub> |                  | ns   |

|                                  |         | $\label{eq:linear} \begin{split} 1.8 \ V &\leq EV_{\text{DD0}} < 2.7 \ V, \\ C_{\text{b}} &= 100 \ p\text{F}, \ R_{\text{b}} = 5 \ k\Omega \end{split}$                                           | 1/fмск<br>+ 230<br><sub>Note2</sub> |                           | 1/f <sub>MCK</sub><br>+ 230<br><sub>Note2</sub> |                 | 1/fмск<br>+ 230<br><sub>Note2</sub> |                  | ns   |

|                                  |         | $\label{eq:linear} \begin{array}{l} 1.7 \mbox{ V} \leq EV_{\mbox{\tiny DD0}} < 1.8 \mbox{ V}, \\ C_{\mbox{\tiny b}} = 100 \mbox{ pF}, \mbox{ R}_{\mbox{\tiny b}} = 5 \mbox{ k}\Omega \end{array}$ | 1/fмск<br>+ 290<br><sub>Note2</sub> |                           | 1/f <sub>MCK</sub><br>+ 290<br><sub>Note2</sub> |                 | 1/fмск<br>+ 290<br><sub>Note2</sub> |                  | ns   |

|                                  |         | $\label{eq:linear} \begin{array}{l} 1.6 \mbox{ V} \leq EV_{\mbox{DD0}} < 1.8 \mbox{ V}, \\ C_{\mbox{\tiny b}} = 100 \mbox{ pF}, \mbox{ R}_{\mbox{\tiny b}} = 5  k\Omega \end{array}$              | —                                   |                           | 1/f <sub>MCK</sub><br>+ 290<br><sub>Note2</sub> |                 | 1/fмск<br>+ 290<br><sub>Note2</sub> |                  | ns   |

| Data hold time<br>(transmission) | thd:dat | $\begin{array}{l} 2.7 \ \text{V} \leq \text{EV}_{\text{DD0}} \leq 5.5 \ \text{V}, \\ \text{C}_{\text{b}} = 50 \ \text{pF}, \ \text{R}_{\text{b}} = 2.7 \ \text{k}\Omega \end{array}$              | 0                                   | 305                       | 0                                               | 305             | 0                                   | 305              | ns   |

|                                  |         | $\label{eq:linear} \begin{array}{l} 1.8 \mbox{ V} \leq EV_{\mbox{DD0}} \leq 5.5 \mbox{ V}, \\ C_{\mbox{\tiny b}} = 100 \mbox{ pF}, \mbox{ R}_{\mbox{\tiny b}} = 3  k\Omega \end{array}$           | 0                                   | 355                       | 0                                               | 355             | 0                                   | 355              | ns   |

|                                  |         | $\label{eq:linear} \begin{array}{l} 1.8 \mbox{ V} \leq EV_{\mbox{DD0}} < 2.7 \mbox{ V}, \\ C_{\mbox{\tiny b}} = 100 \mbox{ pF}, \mbox{ R}_{\mbox{\tiny b}} = 5  k\Omega \end{array}$              | 0                                   | 405                       | 0                                               | 405             | 0                                   | 405              | ns   |

|                                  |         | $1.7 \text{ V} \leq \text{EV}_{\text{DD0}} < 1.8 \text{ V},$ $C_{\text{b}} = 100 \text{ pF}, \text{ R}_{\text{b}} = 5 \text{ k}\Omega$                                                            | 0                                   | 405                       | 0                                               | 405             | 0                                   | 405              | ns   |

|                                  |         | $1.6 \text{ V} \leq \text{EV}_{\text{DD0}} < 1.8 \text{ V},$ $C_{\text{b}} = 100 \text{ pF}, \text{ R}_{\text{b}} = 5 \text{ k}\Omega$                                                            | _                                   | _                         | 0                                               | 405             | 0                                   | 405              | ns   |

| (5) | During communication at same potential (simplified I <sup>2</sup> C mode) (2/2)                                                                                                                                                           |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | $(T_{A} = -40 \text{ to } +85^{\circ}\text{C}, 1.6 \text{ V} \le \text{EV}_{\text{DD0}} = \text{EV}_{\text{DD1}} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}, \text{Vss} = \text{EV}_{\text{SS0}} = \text{EV}_{\text{SS1}} = 0 \text{ V})$ |

**Notes 1.** The value must also be equal to or less than  $f_{MCK}/4$ .

**2.** Set the fMCK value to keep the hold time of SCLr = "L" and SCLr = "H".

Caution Select the normal input buffer and the N-ch open drain output (VDD tolerance (When 20- to 52-pin products)/EVDD tolerance (When 64- to 128-pin products)) mode for the SDAr pin and the normal output mode for the SCLr pin by using port input mode register g (PIMg) and port output mode register h (POMh).

(**Remarks** are listed on the next page.)

- **2.** q: UART number (q = 0 to 3), g: PIM and POM number (g = 0, 1, 8, 14)

- **3.** fMCK: Serial array unit operation clock frequency

(Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn).

m: Unit number, n: Channel number (mn = 00 to 03, 10 to 13))

- **4.** UART2 cannot communicate at different potential when bit 1 (PIOR1) of peripheral I/O redirection register (PIOR) is 1.

- **Notes 1.** Total current flowing into V<sub>DD</sub> and EV<sub>DD0</sub>, including the input leakage current flowing when the level of the input pin is fixed to V<sub>DD</sub>, EV<sub>DD0</sub> or Vss, EV<sub>SS0</sub>. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the A/D converter, LVD circuit, I/O port, and on-chip pull-up/pull-down resistors and the current flowing during data flash rewrite.

- 2. When high-speed on-chip oscillator and subsystem clock are stopped.

- 3. When high-speed system clock and subsystem clock are stopped.

- 4. When high-speed on-chip oscillator and high-speed system clock are stopped. When AMPHS1 = 1 (Ultra-low power consumption oscillation). However, not including the current flowing into the RTC, 12-bit interval timer, and watchdog timer.

- 5. Relationship between operation voltage width, operation frequency of CPU and operation mode is as below.

HS (high-speed main) mode: 2.7 V  $\leq$  V\_DD  $\leq$  5.5 V@1 MHz to 32 MHz

2.4 V

$$\leq$$

V<sub>DD</sub>  $\leq$  5.5 V@1 MHz to 16 MHz

- **Remarks 1.** f<sub>MX</sub>: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- 2. fin: High-speed on-chip oscillator clock frequency

- 3. fsub: Subsystem clock frequency (XT1 clock oscillation frequency)

- 4. Except subsystem clock operation, temperature condition of the TYP. value is TA = 25°C

- **Notes 1.** Total current flowing into VDD, EVDDD, and EVDD1, including the input leakage current flowing when the level of the input pin is fixed to VDD, EVDDD, and EVDD1, or Vss, EVsso, and EVss1. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the A/D converter, LVD circuit, I/O port, and on-chip pull-up/pull-down resistors and the current flowing during data flash rewrite.

- 2. When high-speed on-chip oscillator and subsystem clock are stopped.

- 3. When high-speed system clock and subsystem clock are stopped.

- **4.** When high-speed on-chip oscillator and high-speed system clock are stopped. When AMPHS1 = 1 (Ultra-low power consumption oscillation). However, not including the current flowing into the 12-bit interval timer and watchdog timer.

- **5.** Relationship between operation voltage width, operation frequency of CPU and operation mode is as below.

HS (high-speed main) mode: 2.7 V  $\leq$  V\_DD  $\leq$  5.5 V@1 MHz to 32 MHz

2.4 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V@1 MHz to 16 MHz

- **Remarks 1.** fMX: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- 2. fin: High-speed on-chip oscillator clock frequency

- 3. fsub: Subsystem clock frequency (XT1 clock oscillation frequency)

- 4. Except subsystem clock operation, temperature condition of the TYP. value is  $T_A = 25^{\circ}C$

- Current flowing only to the A/D converter. The supply current of the RL78 microcontrollers is the sum of IDD1 or IDD2 and IADC when the A/D converter is in operation.

- 7. Current flowing only to the LVD circuit. The supply current of the RL78 microcontrollers is the sum of IDD1, IDD2 or IDD3 and ILVD when the LVD circuit is in operation.

- 8. Current flowing only during data flash rewrite.

- **9.** Current flowing only during self programming.

- 10. For shift time to the SNOOZE mode, see 18.3.3 SNOOZE mode in the RL78/G13 User's Manual.

Remarks 1. fil: Low-speed on-chip oscillator clock frequency

- 2. fsub: Subsystem clock frequency (XT1 clock oscillation frequency)

- 3. fclk: CPU/peripheral hardware clock frequency

- 4. Temperature condition of the TYP. value is  $T_A = 25^{\circ}C$

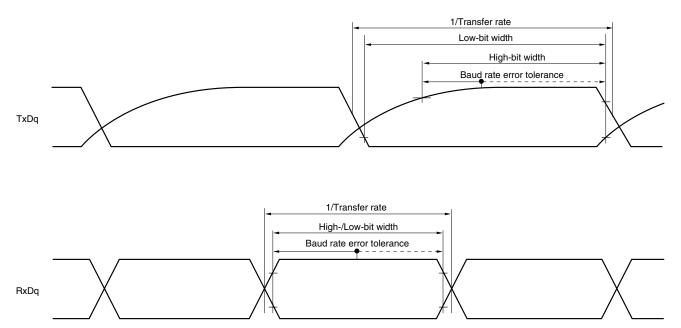

### **TI/TO Timing**

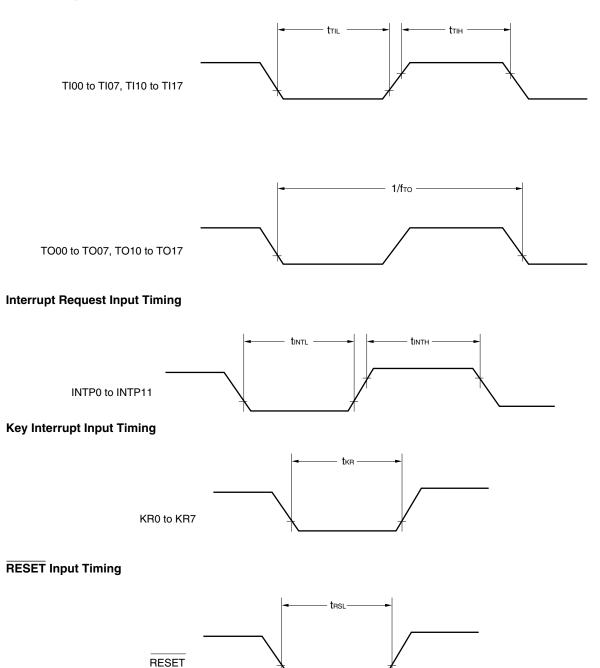

## 3.10 Timing of Entry to Flash Memory Programming Modes

| Parameter                                                                                                                                                                   | Symbol  | Conditions                                                                | MIN. | TYP. | MAX. | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------------------|------|------|------|------|

| Time to complete the<br>communication for the initial<br>setting after the external reset is<br>released                                                                    | tsuinit | POR and LVD reset must be released before the external reset is released. |      |      | 100  | ms   |

| Time to release the external reset<br>after the TOOL0 pin is set to the<br>low level                                                                                        | tsu     | POR and LVD reset must be released before the external reset is released. | 10   |      |      | μs   |

| Time to hold the TOOL0 pin at the<br>low level after the external reset is<br>released<br>(excluding the processing time of<br>the firmware to control the flash<br>memory) | tно     | POR and LVD reset must be released before the external reset is released. | 1    |      |      | ms   |

### $(T_A = -40 \text{ to } +105^{\circ}\text{C}, 2.4 \text{ V} \le \text{EV}_{\text{DD0}} = \text{EV}_{\text{DD1}} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}, \text{V}_{\text{SS}} = \text{EV}_{\text{SS0}} = \text{EV}_{\text{SS1}} = 0 \text{ V})$

- <1> The low level is input to the TOOL0 pin.

- <2> The external reset is released (POR and LVD reset must be released before the external reset is released.).

- <3> The TOOL0 pin is set to the high level.

- <4> Setting of the flash memory programming mode by UART reception and complete the baud rate setting.

- **Remark** tsuinit: Communication for the initial setting must be completed within 100 ms after the external reset is released during this period.

- $t_{\text{SU}}$ : Time to release the external reset after the TOOL0 pin is set to the low level

- thd: Time to hold the TOOL0 pin at the low level after the external reset is released (excluding the processing time of the firmware to control the flash memory)

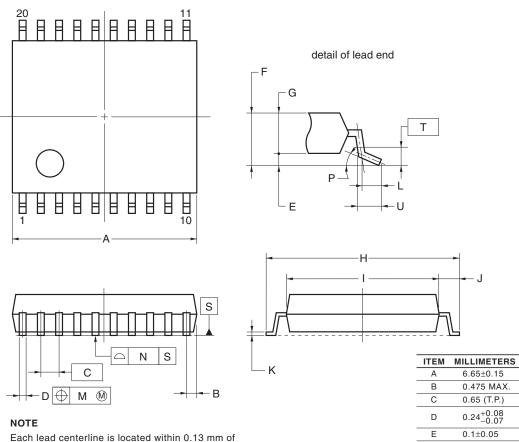

# 4. PACKAGE DRAWINGS

# 4.1 20-pin Products

R5F1006AASP, R5F1006CASP, R5F1006DASP, R5F1006EASP R5F1016AASP, R5F1016CASP, R5F1016DASP, R5F1016EASP R5F1006ADSP, R5F1006CDSP, R5F1006DDSP, R5F1006EDSP R5F1016ADSP, R5F1016CDSP, R5F1016DDSP, R5F1016EDSP R5F1006AGSP, R5F1006CGSP, R5F1006DGSP, R5F1006EGSP

| JEITA Package Code  | RENESAS Code | Previous Code  | MASS (TYP.) [g] |

|---------------------|--------------|----------------|-----------------|

| P-LSSOP20-0300-0.65 | PLSP0020JC-A | S20MC-65-5A4-3 | 0.12            |

|                     |              |                |                 |

Each lead centerline is located within 0.13 mm of its true position (T.P.) at maximum material condition.

|   | ( )                                   |

|---|---------------------------------------|

| D | $0.24^{+0.08}_{-0.07}$                |

| E | 0.1±0.05                              |

| F | 1.3±0.1                               |

| G | 1.2                                   |

| Н | 8.1±0.2                               |

| Ι | 6.1±0.2                               |

| J | 1.0±0.2                               |

| К | 0.17±0.03                             |

| L | 0.5                                   |

| Μ | 0.13                                  |

| Ν | 0.10                                  |

| Р | $3^{\circ}^{+5}_{-3^{\circ}}^{\circ}$ |

| Т | 0.25                                  |

| U | 0.6±0.15                              |

© 2012 Renesas Electronics Corporation. All rights reserved.

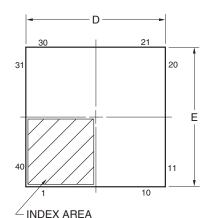

# 4.7 40-pin Products

R5F100EAANA, R5F100ECANA, R5F100EDANA, R5F100EEANA, R5F100EFANA, R5F100EGANA, R5F100EHANA R5F101EAANA, R5F101ECANA, R5F101EDANA, R5F101EEANA, R5F101EFANA, R5F101EGANA, R5F101EHANA R5F100EADNA, R5F100ECDNA, R5F100EDDNA, R5F100EEDNA, R5F100EFDNA, R5F100EGDNA, R5F100EHDNA

R5F101EADNA, R5F101ECDNA, R5F101EDDNA, R5F101EEDNA, R5F101EFDNA, R5F101EGDNA, R5F101EHDNA

R5F100EAGNA, R5F100ECGNA, R5F100EDGNA, R5F100EEGNA, R5F100EFGNA, R5F100EGGNA, R5F100EHGNA

| JEITA Package code | RENESAS code | Previous code  | MASS (TYP.) [g] |

|--------------------|--------------|----------------|-----------------|

| P-HWQFN40-6x6-0.50 | PWQN0040KC-A | P40K8-50-4B4-5 | 0.09            |

Detail of (A) Part

| Referance<br>Symbol | Dimension in Millimeters |      |      |

|---------------------|--------------------------|------|------|

|                     | Min                      | Nom  | Max  |

| D                   | 5.95                     | 6.00 | 6.05 |

| E                   | 5.95                     | 6.00 | 6.05 |

| A                   |                          |      | 0.80 |

| A <sub>1</sub>      | 0.00                     |      |      |

| b                   | 0.18                     | 0.25 | 0.30 |

| е                   |                          | 0.50 |      |

| Lp                  | 0.30                     | 0.40 | 0.50 |

| х                   |                          |      | 0.05 |

| у                   |                          |      | 0.05 |

| ZD                  |                          | 0.75 | —    |

| Z <sub>E</sub>      |                          | 0.75 | —    |

| C <sub>2</sub>      | 0.15                     | 0.20 | 0.25 |

| D <sub>2</sub>      |                          | 4.50 |      |

| E <sub>2</sub>      |                          | 4.50 |      |

©2013 Renesas Electronics Corporation. All rights reserved.

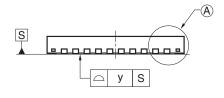

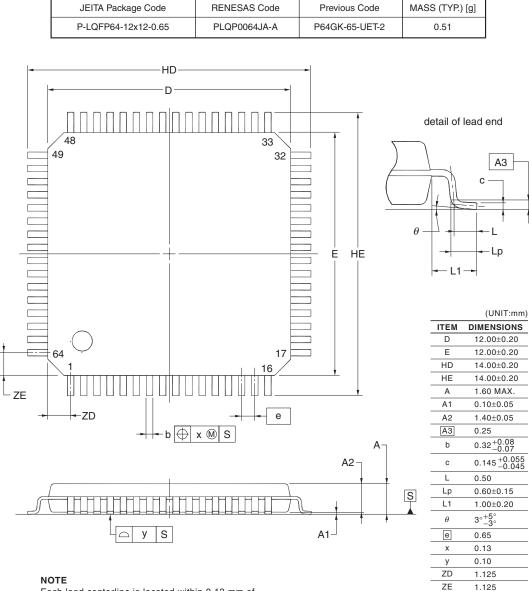

# 4.11 64-pin Products

R5F100LCAFA, R5F100LDAFA, R5F100LEAFA, R5F100LFAFA, R5F100LGAFA, R5F100LHAFA, R5F100LJAFA, R5F100LLAFA

R5F101LCAFA, R5F101LDAFA, R5F101LEAFA, R5F101LFAFA, R5F101LGAFA, R5F101LHAFA, R5F101LJAFA, R5F101LLAFA

R5F100LCDFA, R5F100LDDFA, R5F100LEDFA, R5F100LFDFA, R5F100LGDFA, R5F100LHDFA, R5F100LJDFA, R5F100LLDFA

R5F101LCDFA, R5F101LDDFA, R5F101LEDFA, R5F101LFDFA, R5F101LGDFA, R5F101LHDFA, R5F101LJDFA, R5F101LLDFA

R5F100LCGFA, R5F100LDGFA, R5F100LEGFA, R5F100LFGFA, R5F100LGGFA, R5F100LHGFA, R5F100LJGFA

Each lead centerline is located within 0.13 mm of its true position at maximum material condition.

©2012 Renesas Electronics Corporation. All rights reserved.

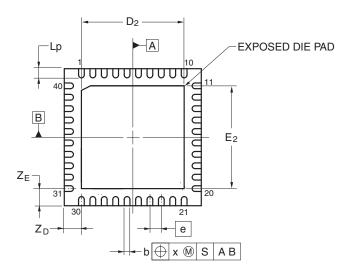

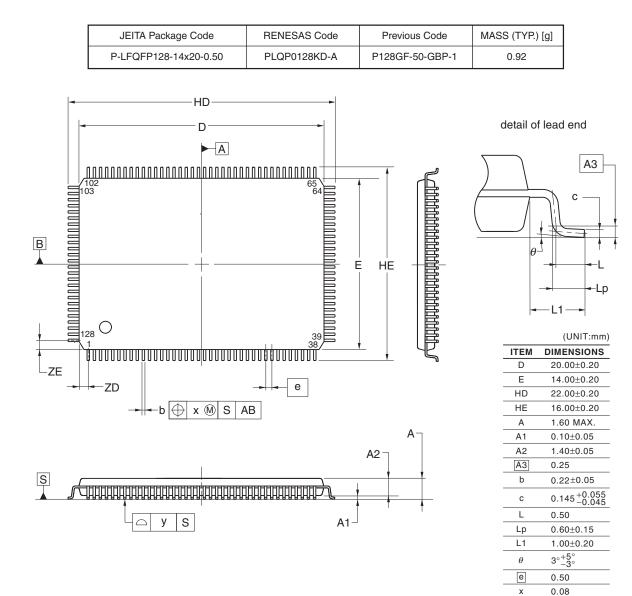

# 4.14 128-pin Products

R5F100SHAFB, R5F100SJAFB, R5F100SKAFB, R5F100SLAFB R5F101SHAFB, R5F101SJAFB, R5F101SKAFB, R5F101SLAFB R5F100SHDFB, R5F100SJDFB, R5F100SKDFB, R5F100SLDFB R5F101SHDFB, R5F101SJDFB, R5F101SKDFB, R5F101SLDFB

©2012 Renesas Electronics Corporation. All rights reserved.

х

y ZD

ZE

0.08

0.75

0.75